| [1] |

LIANG Huaguo, XU Xiumin, HUANG Zhengfeng, et al. A methodology for characterization of SET propagation in SRAM-based FPGAs[J]. IEEE Transactions on Nuclear Science, 2016, 63(6): 2985–2992. doi: 10.1109/TNS.2016.2620165.

|

| [2] |

WANG Ke and LOURI A. CURE: A high-performance, low-power, and reliable network-on-chip design using reinforcement learning[J]. IEEE Transactions on Parallel and Distributed Systems, 2020, 31(9): 2125–2138. doi: 10.1109/TPDS.2020.2986297.

|

| [3] |

BHOWMIK B. Maximal connectivity test with channel-open faults in on-chip communication networks[J]. Journal of Electronic Testing, 2020, 36(3): 385–408. doi: 10.1007/S10836-020-05878-1.

|

| [4] |

DITOMASO D, BORATEN T, KODI A, et al. Dynamic error mitigation in NoCs using intelligent prediction techniques[C]. 2016 49th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), Taipei, China, 2016: 1–12. doi: 10.1109/MICRO.2016.7783734.

|

| [5] |

CHANG Y C, GONG C S A, and CHIU C T. Fault-tolerant mesh-based NoC with router-level redundancy[J]. Journal of Signal Processing Systems, 2020, 92(4): 345–355. doi: 10.1007/S11265-019-01476-3.

|

| [6] |

GUO Pengxing, HOU Weigang, GUO Lei, et al. Fault-tolerant routing mechanism in 3D optical network-on-chip based on node reuse[J]. IEEE Transactions on Parallel and Distributed Systems, 2020, 31(3): 547–564. doi: 10.1109/TPDS.2019.2939240.

|

| [7] |

NARAYANASAMY P and GOPALAKRISHNAN S. Novel fault tolerance topology using corvus seek algorithm for application specific NoC[J]. Integration, 2023, 89: 146–154. doi: 10.1016/J.VLSI.2022.11.011.

|

| [8] |

SLEEBA S Z, JOSE J, and MINI M G. Energy-efficient fault tolerant technique for deflection routers in two-dimensional mesh Network-on-Chips[J]. IET Computers & Digital Techniques, 2018, 12(3): 69–79. doi: 10.1049/IET-CDT.2017.0006.

|

| [9] |

SAMALA J, TAKAWALE H, CHOKHANI Y, et al. Fault-tolerant routing algorithm for mesh based NoC using reinforcement learning[C]. 2020 24th International Symposium on VLSI Design and Test (VDAT), Bhubaneswar, India, 2020: 1–6. doi: 10.1109/VDAT50263.2020.9190340.

|

| [10] |

LIU Yi, GUO Rujia, XU Changqing, et al. A Q-learning-based fault-tolerant and congestion-aware adaptive routing algorithm for networks-on-chip[J]. IEEE Embedded Systems Letters, 2022, 14(4): 203–206. doi: 10.1109/LES.2022.3176233.

|

| [11] |

JAIN A, LAXMI V, TRIPATHI M, et al. TRACK: An algorithm for fault-Tolerant, dynamic and scalable 2D mesh network-on-chip routing reconfiguration[J]. Integration, 2020, 72: 92–110. doi: 10.1016/J.VLSI.2020.01.005.

|

| [12] |

ZHANG Ying, HONG Xinpeng, CHEN Zhongsheng, et al. A deterministic-path routing algorithm for tolerating many faults on very-large-scale network-on-chip[J]. ACM Transactions on Design Automation of Electronic Systems (TODAES), 2021, 26(1): 8. doi: 10.1145/3414060.

|

| [13] |

LI Jiao, QIN Chaoqun, and SUN Xuecheng. An efficient adaptive routing algorithm for the Co-optimization of fault tolerance and congestion awareness based on 3D NoC[J]. Microelectronics Journal, 2023, 142: 105989. doi: 10.1016/J.MEJO.2023.105989.

|

| [14] |

RIZK M, MARTIN K J M, and DIGUET J P. Run-time remapping algorithm of dataflow actors on NoC-based heterogeneous MPSoCs[J]. IEEE Transactions on Parallel and Distributed Systems, 2022, 33(12): 3959–3976. doi: 10.1109/TPDS.2022.3177957.

|

| [15] |

WANG K, LOURI A, KARANTH A, et al. IntelliNoC: A holistic design framework for energy-efficient and reliable on-chip communication for manycores[C]. Proceedings of the 46th International Symposium on Computer Architecture, Phoenix, USA, 2019: 589–600. doi: 10.1145/3307650.3322274.

|

| [16] |

ZHENG Hao and LOURI A. Agile: A learning-enabled power and performance-efficient network-on-chip design[J]. IEEE Transactions on Emerging Topics in Computing, 2022, 10(1): 223–236. doi: 10.1109/TETC.2020.3003496.

|

| [17] |

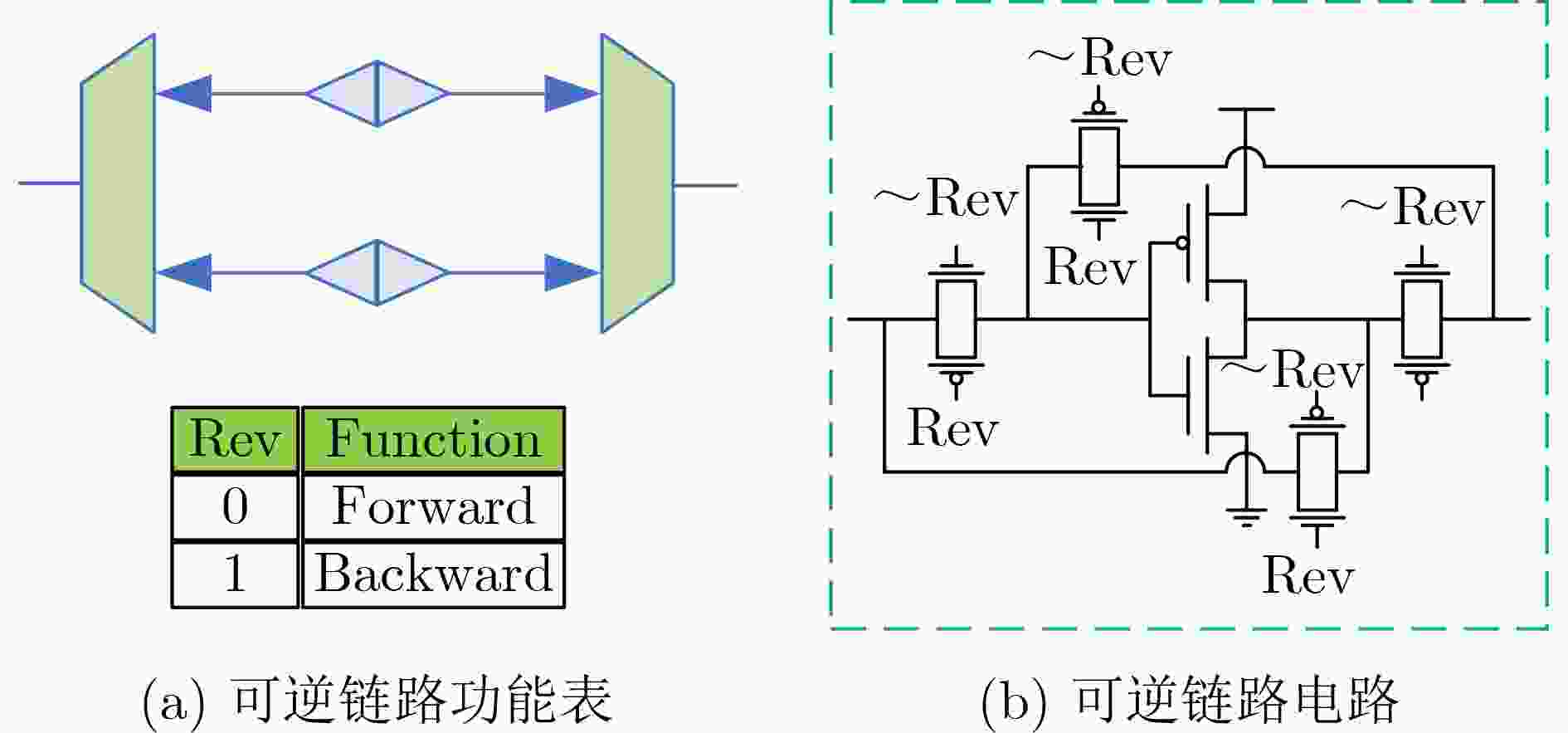

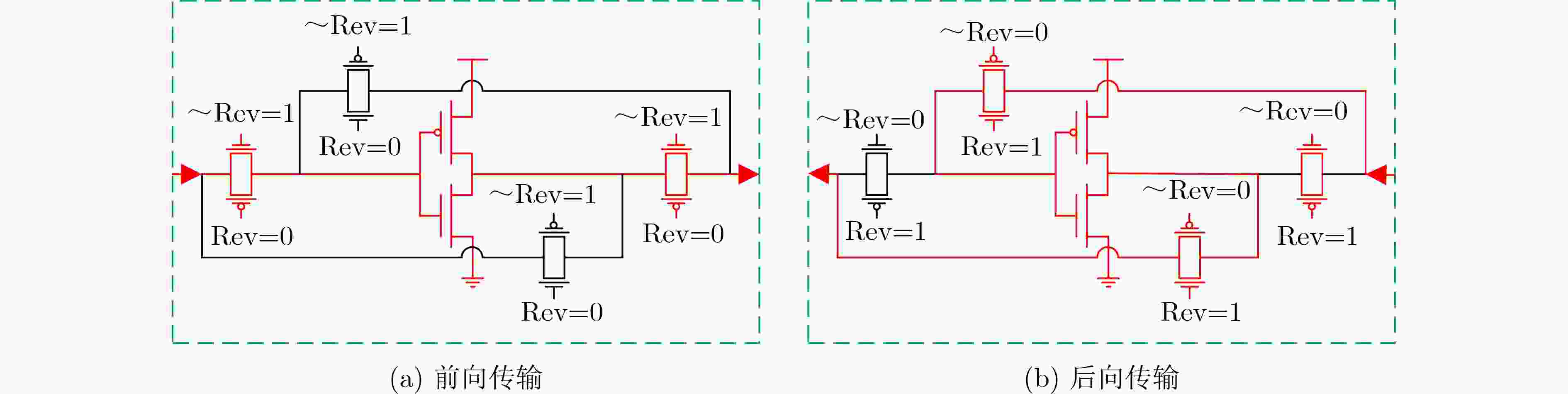

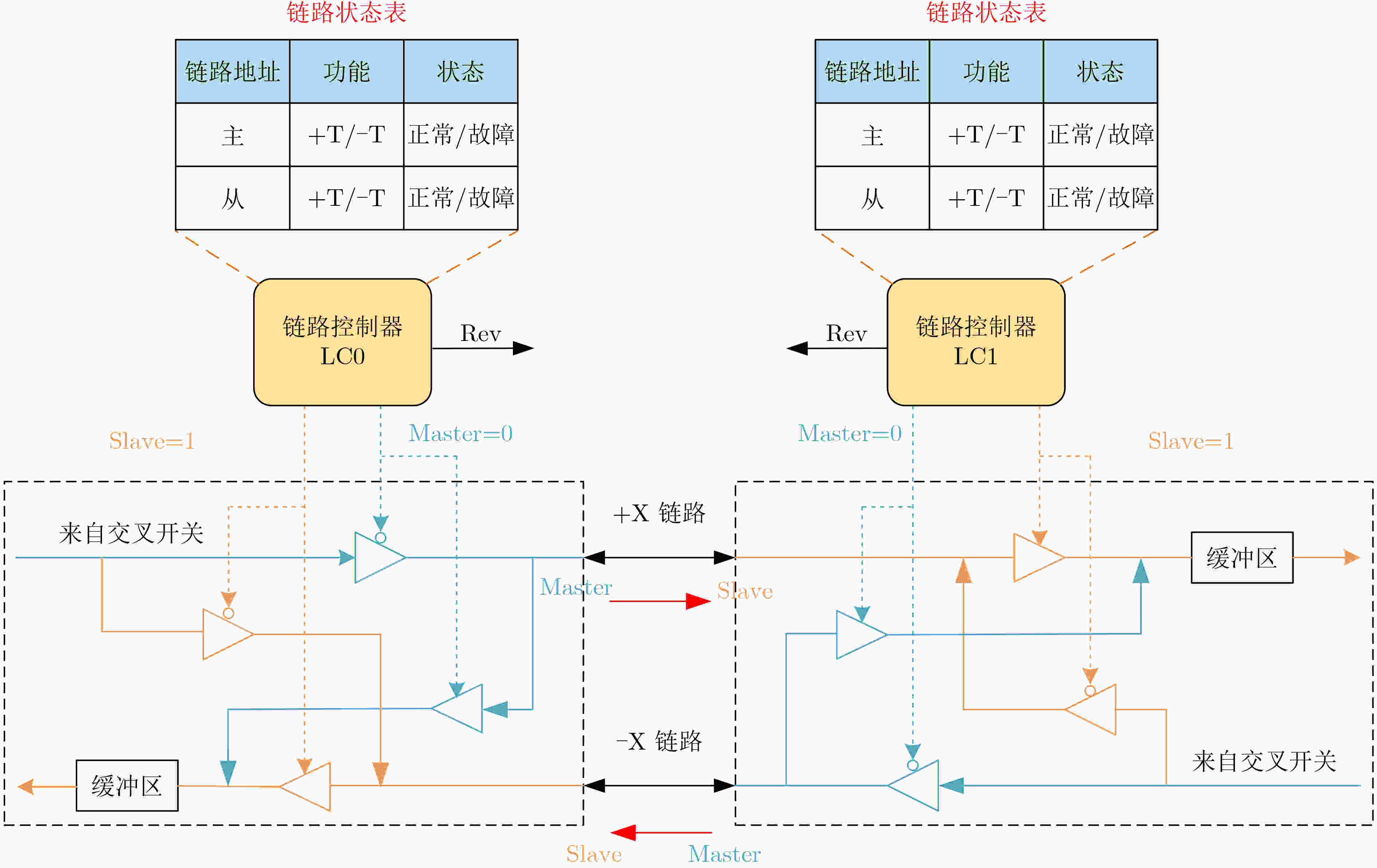

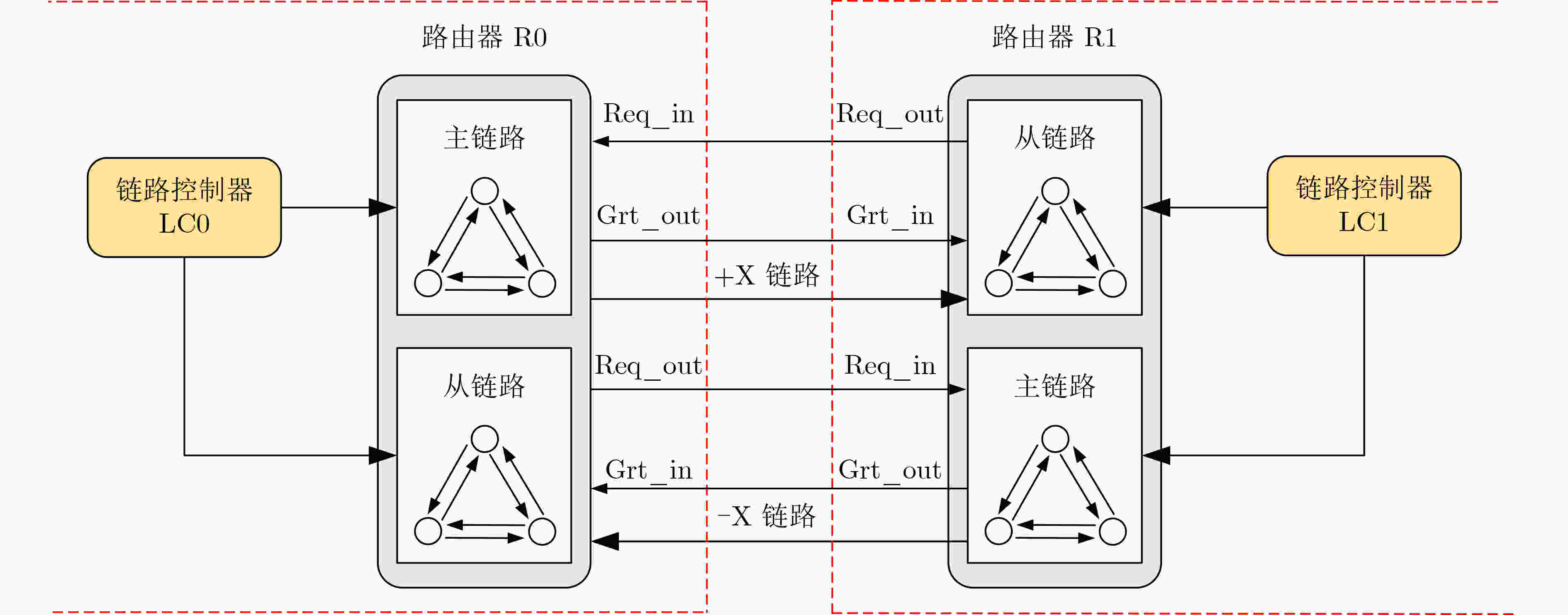

LAN Y C, LIN H A, LO S H, et al. A bidirectional NoC (BiNoC) architecture with dynamic self-reconfigurable channel[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2011, 30(3): 427–440. doi: 10.1109/TCAD.2010.2086930.

|

| [18] |

FARROKHBAKHT H, KAO H, HASAN K, et al. Pitstop: Enabling a virtual network free network-on-chip[C]. 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA), Seoul, Korea (South), 2021: 682–695. doi: 10.1109/HPCA51647.2021.00063.

|

| [19] |

SUN Chen, CHEN C H O, KURIAN G, et al. DSENT-a tool connecting emerging photonics with electronics for opto-electronic networks-on-chip modeling[C]. 2012 IEEE/ACM Sixth International Symposium on Networks-on-Chip, Lyngby, Denmark, 2012: 201–210. doi: 10.1109/NOCS.2012.31.

|

| [20] |

ZHOU Wu, OUYANG Yiming, XU Dongyu, et al. Energy-efficient multiple network-on-chip architecture with bandwidth expansion[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2023, 31(4): 442–455. doi: 10.1109/TVLSI.2023.3244859.

|

下载:

下载:

下载:

下载: