Design Method of Ferroelectric Field Effect Transistor Polymorphic Gate Based on Immune Algorithm

-

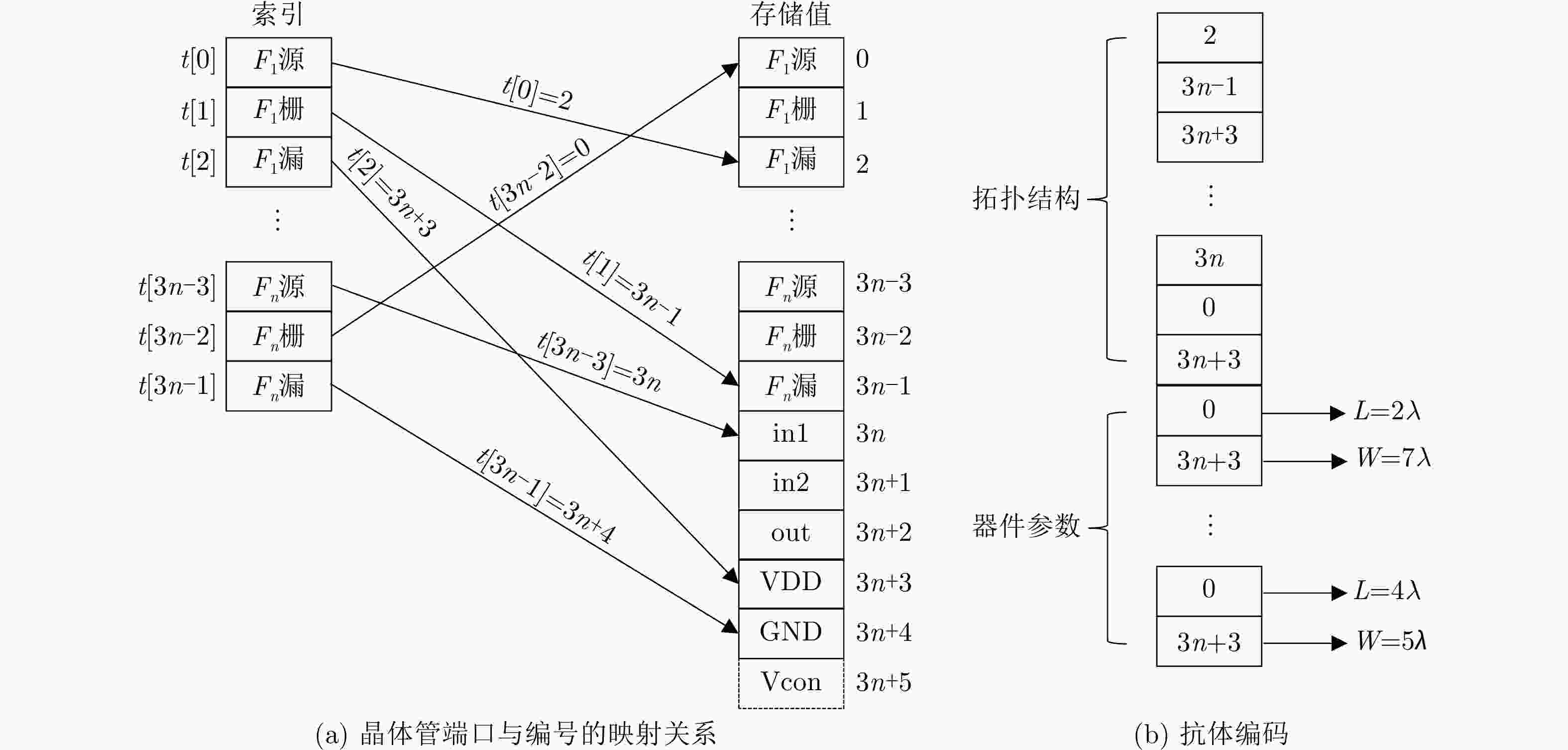

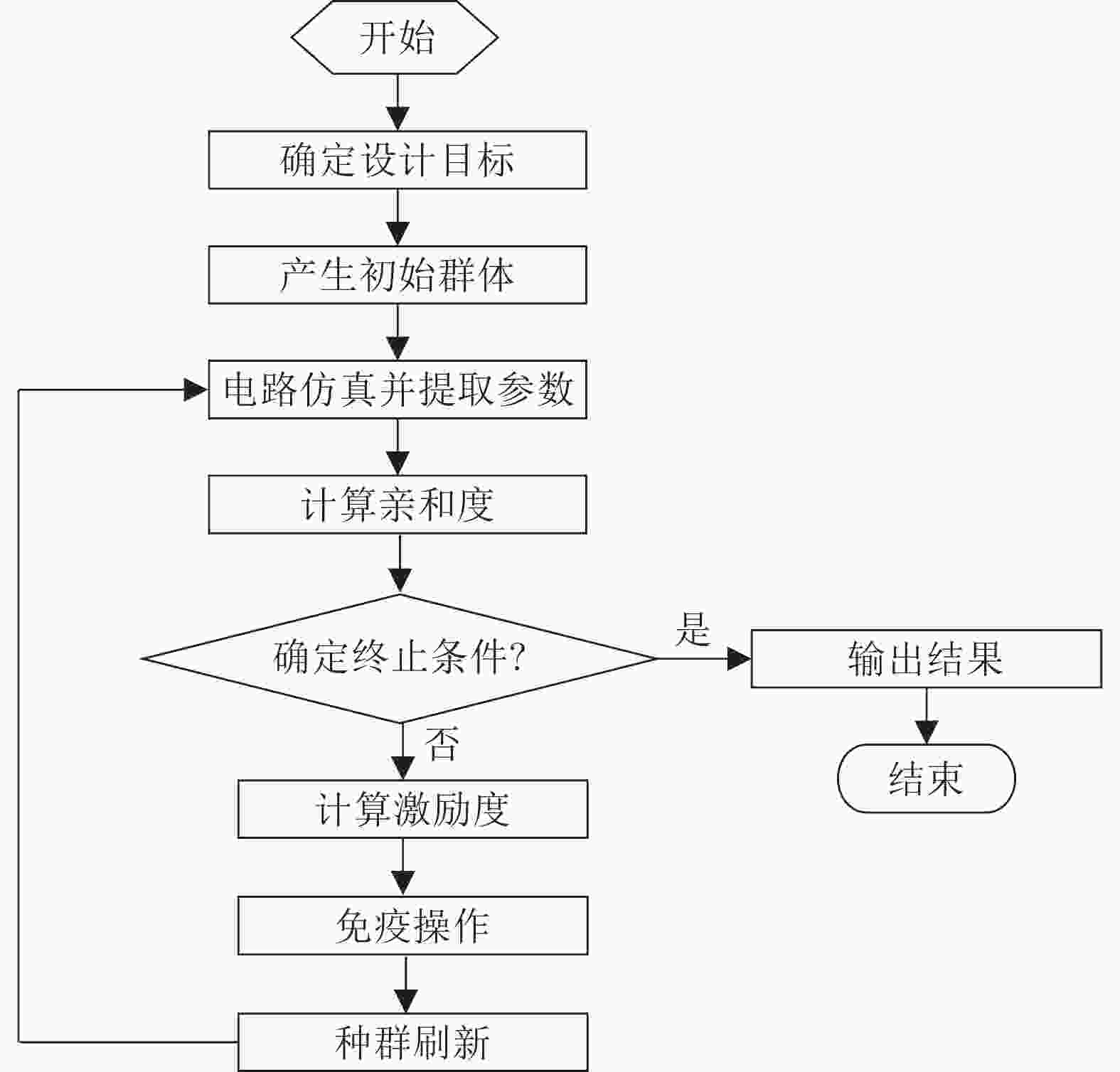

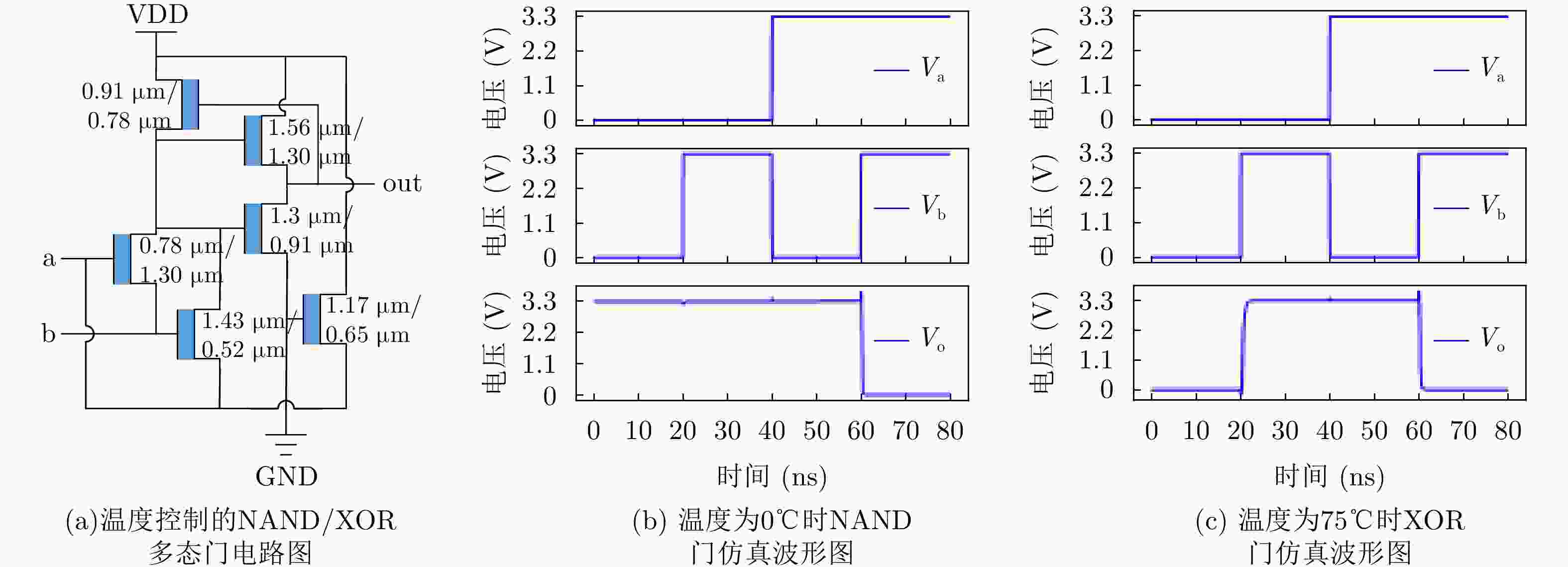

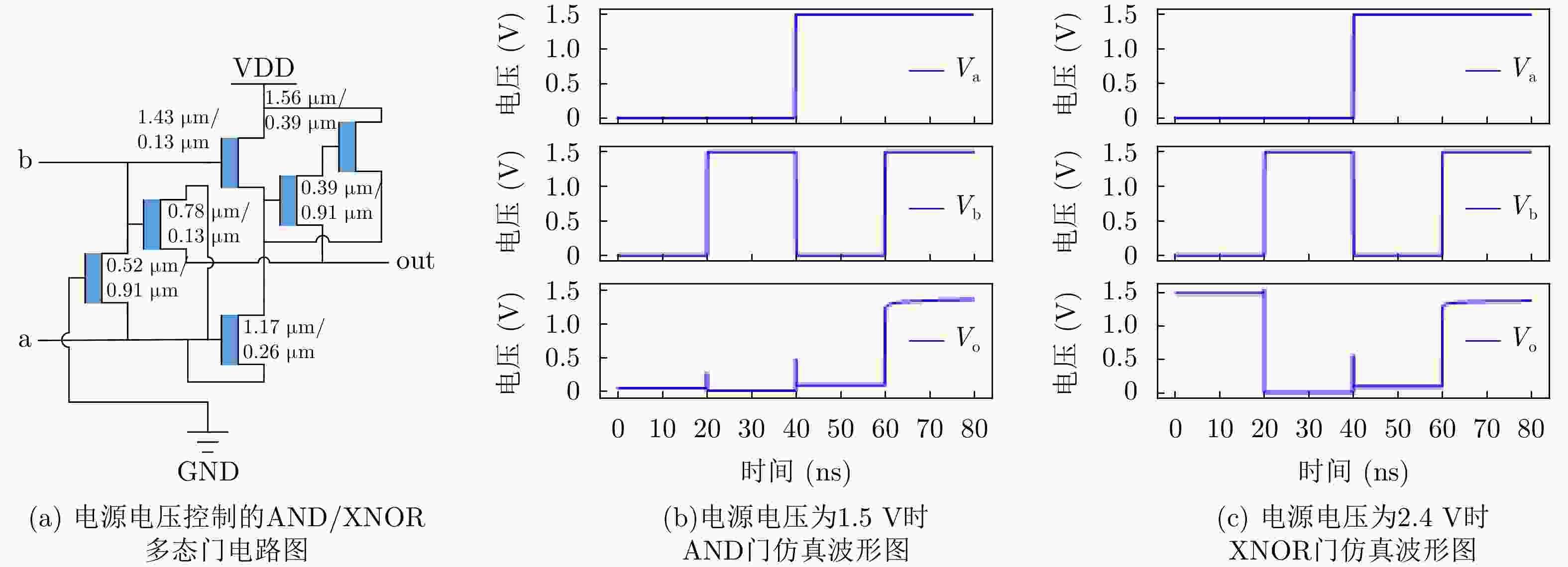

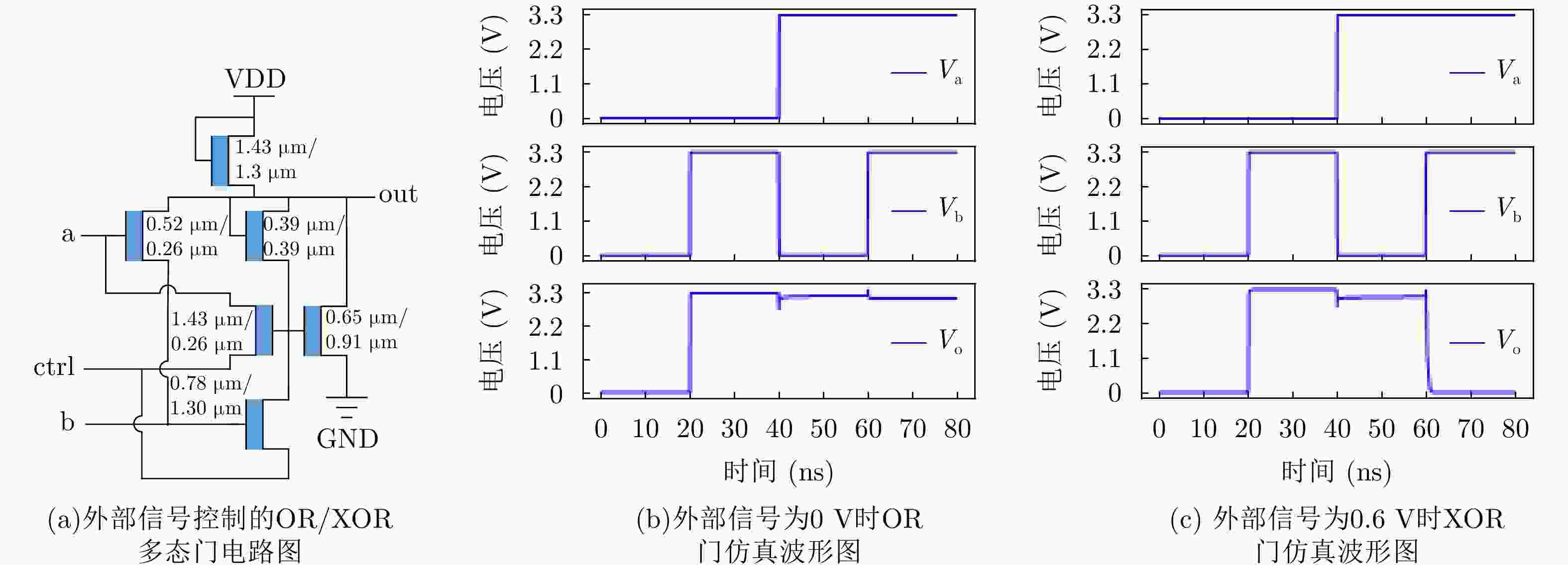

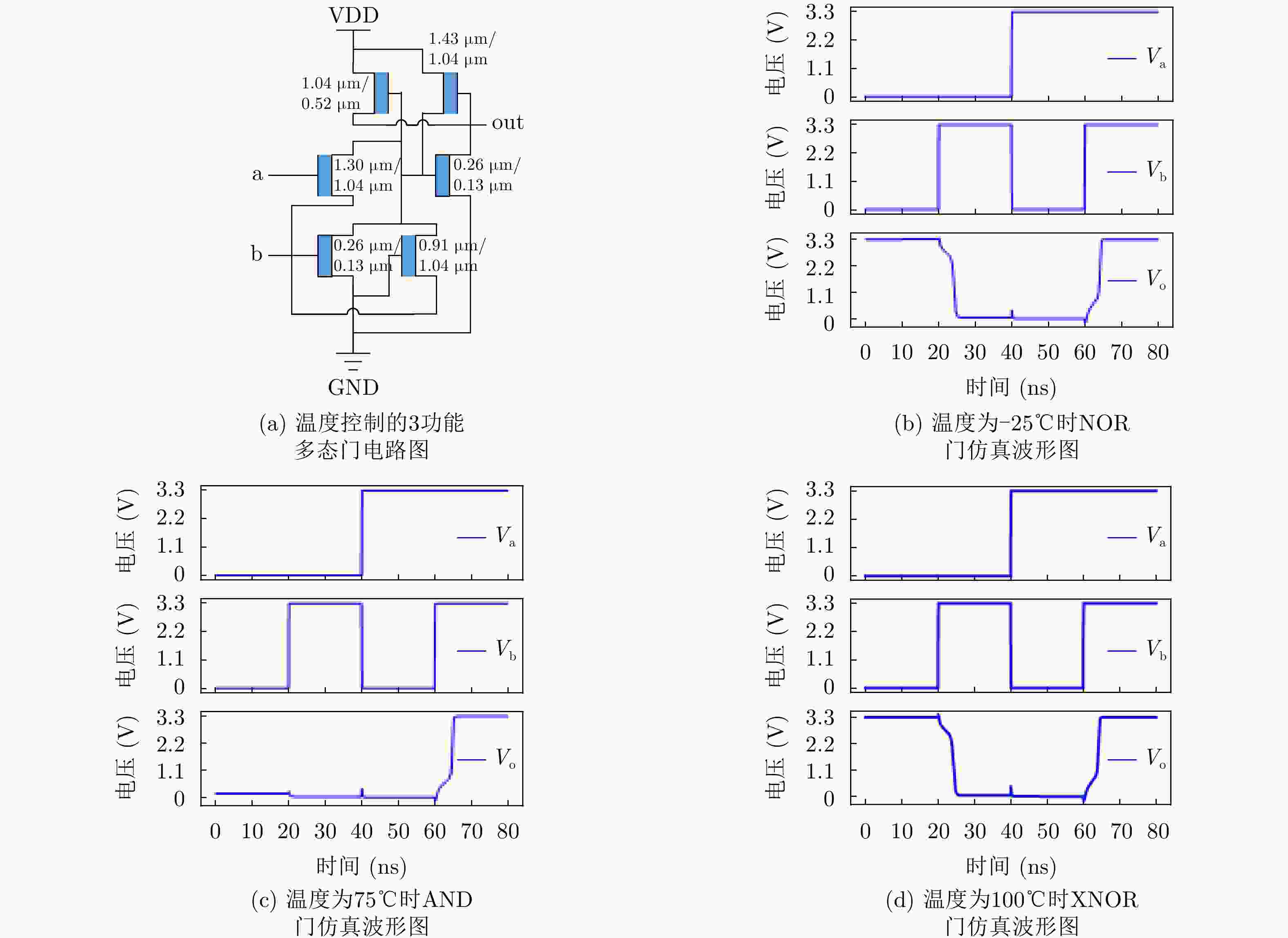

摘要: 应用于硬件安全领域的多态电路对于除金属氧化物半导体场效应晶体管(MOSFET)外的新器件的研究较少,往往只有少数几个设计实例,缺乏一般化的研究方法和多态门设计平台。面向铁电场效应晶体管(FeFET)器件,该文提出一种多态门设计方法。该方法利用免疫算法,将基于FeFET的多态门电路生成问题归结为生物代际演化过程。该文利用C++语言平台和Hspice仿真工具实现了完整的FeFET多态门设计算法,结合具体的工艺和电路模型搭建了多态门的设计平台。实验结果表明,该设计方法可有效地生成出基于FeFET的多态电路,其所生成的多态门电路可实现温度、电源电压和外部信号多种控制方式。Abstract: The research on polymorphic circuits applied to the field of hardware security for new devices other than Metal Oxide Semiconductor Field-Effect Transistors (MOSFET) is relatively limited, often with only a few design examples, lacking general research methods and polymorphic gate design platforms. A polymorphic gate design method based on Ferroelectric Field Effect Transistor (FeFET) devices is proposed. Immune algorithms are used to attribute the generation problem of polymorphic gate circuits based on FeFET to the process of biological intergenerational evolution. A complete FeFET polymorphic gate design algorithm is implemented by combining the C++language platform with the Hspice simulation tool. Combining specific process and circuit models, a design platform for three types of polymorphic gates controlled by temperature, power supply voltage, and external signals is constructed. The results indicate that this design method can effectively generate FeFET based polymorphic circuits, and the generated polymorphic gate circuits can achieve multiple control methods for temperature, power supply voltage, and external signals.

-

算法1 用于FeFET多态门设计的免疫算法 输入:电路的拓扑结构和器件参数、控制条件、器件模型和工艺 输出:符合设计目标的混合多态门电路 (1) 参数设置 Pop_num:每一个父代生成的个体数目 Gen_Max:最大免疫代数,即当进化的代数达到此值时,算法停止运行 Function_affinity:亲和度函数 r%:变异率 ncl:克隆个数 detas:相似度阈值 Num_FeFET:FeFET器件个数 Control:多态门的功能切换的控制条件 fi <i, a, b, ···>:控制条件为i,输入值为a, b, ···时设计目标的真值表 (2) 初始群体生成 Gen_now = 0; Survival_pop = ø; 生成包含Sur_num个初始电路网表的集合; for (n=0; n < Sur_num; n++) do 初始电路网表编码为初始个体chromo[n]; //对初始的电路网表进

行编码Survival_pop = Survival_pop ∪ chromo[n]; //生成初始群体 end for (3) 网表仿真并提取仿真结果 for (n=0; n < Pop_num×sur_num; n++) do 将Pop_chromo[n]译码为netlist[n]; for 不同的控制条件i do Simulate (i, a, b, ···netlist[n]); end for end for for (n=0; n < Pop_num×Sur_num; n++) do 提取仿真结果; 将仿真结果映射为不同控制条件下的真值表f’; end for (4) 亲和度计算 for (n = 0; n < Pop_num×Sur_num; n++) do ${\text{aff} }({f_i},f'_i){\text{ = } }\displaystyle\sum\nolimits_{i = 1}^{ {2^n} } { {\partial _k} }$//计算每个个体的亲和度 end for (5) 激励度计算 for (n = 0; n < Pop_num×Sur_num; n++) do ${\text{sim} }({{\rm{ab}}_i}) = {\text{a} } \times {\text{aff} }({f_i},f'_i) - {\text{b} } \times {\text{den} }({\text{a} }{ {\text{b} }_i})$ //计算每个个体的激

励度end for (6) 免疫操作 for (n = 0; n < Pop_num×Sur_num; n++) do Selection();// 进行选择操作 Clone();// 进行克隆操作 Mutation();// 进行选择操作 Cloneinhibition();// 进行克隆抑制操作 end for (7) 种群刷新 for (n = 0; n < Pop_num×Sur_num; n++) do 得到当前代群体chromo[Pop_num×Sur_num]; Current_check();//电路结构检测 end for Gen_now ++; (8) 停止条件判断 while (Gen_now < Gen_Max || ${\text{aff} }({f_i},f'_i) \ne {2^n}$)//进化代数未达到设定最大值或未出现满足预期目标的多态门结构 跳到步骤3 end while 表 1 利用免疫算法得到的FeFET多态门

序号 功能 控制条件 数值 器件数量 1 NAND/NOR T –25°C/100°C 6 2 NAND/AND T 75°C/125°C 6 3 XNOR/AND T 50°C/150°C 6 4 XOR/NAND VDD 1.2 V/1.8 V 6 5 NOR/AND VDD 1.2 V/2.1 V 6 6 XNOR/NOR VDD 2.7 V/3.3 V 6 7 NAND/NOR VCONTROL 1.2 V/2.1 V 6 8 XNOR/NOR VCONTROL 0.6 V/1.2 V 6 9 OR/XNOR/NOR VCONTROL 0 V/1.5 V/3.0 V 6 10 OR/NAND/XOR VCONTROL 0 V/0.9 V/1.2 V 6 -

[1] STOICA A, ZEBULUM R, and KEYMEULEN D. Polymorphic electronics[C]. 4th International Conference on Evolvable Systems: From Biology to Hardware, Tokyo, Japan, 2001: 291–302. [2] RUZICKA R, SEKANINA L, and PROKOP R. Physical demonstration of polymorphic self-checking circuits[C]. 2008 14th IEEE International On-Line Testing Symposium, Rhodes, Greece, 2008: 31–36. [3] SEKANINA L, RUZICKA R, and GAJDA Z. Polymorphic FIR filters with backup mode enabling power savings[C]. 2009 NASA/ESA Conference on Adaptive Hardware and Systems, San Francisco, USA, 2009: 43–50. [4] STARECEK L, SEKANINA L, and KOTASEK Z. Reduction of test vectors volume by means of gate-level reconfiguration[C]. 2008 11th IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems, Bratislava, Slovakia, 2008: 1–4. [5] SUAREZ A, ORO H, PEÑAREDONDA L, et al. Design of a new external signal controlled polymorphic gates[C]. 2016 7th International Conference on Intelligent Systems, Modelling and Simulation (ISMS), Bangkok, Thailand, 2016: 413–418. [6] WANG Tian, CUI Xiaoxin, YU Dunshan, et al. Polymorphic gate based IC watermarking techniques[C]. 2018 23rd Asia and South Pacific Design Automation Conference (ASP-DAC), Jeju, Korea (South), 2018: 90–96. [7] NEVORAL J, RUZICKA R, and SIMEK V. CMOS gates with second function[C]. 2018 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Hong Kong, China, 2018: 82–87. [8] BI Yu, GAILLARDON P E, HU X S, et al. Leveraging emerging technology for hardware security-case study on silicon nanowire FETs and graphene symfets[C]. 2014 IEEE 23rd Asian Test Symposium, Hangzhou, China, 2014: 342–347. [9] PARVEEN F, HE Zhezhi, ANGIZI S, et al. Hybrid polymorphic logic gate with 5-terminal magnetic domain wall motion device[C]. 2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Bochum, Germany, 2017: 152–157. [10] REZAEI A, SHEN Yuanqi, KONG Shuyu, et al. Cyclic locking and memristor-based obfuscation against CycSAT and inside foundry attacks[C]. 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 2018: 85–90. [11] MACHA N, GEEDIPALLY S, REPALLE B, et al. Crosstalk based fine-grained reconfiguration techniques for polymorphic circuits[C]. The 14th IEEE/ACM International Symposium on Nanoscale Architectures, Athens, Greece, 2018: 114–120. [12] MACHA N K, REPALLE B T, IQBAL M A, et al. Crosstalk-computing-based gate-level reconfigurable circuits[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2022, 30(8): 1073–1083. doi: 10.1109/TVLSI.2022.3173344 [13] KAREMPUDI V S P, VATSAVAI S S, THAKKAR I, et al. A polymorphic electro-optic logic gate for high-speed reconfigurable computing circuits[C]. 2023 24th International Symposium on Quality Electronic Design (ISQED), San Francisco, USA, 2023: 1–8. [14] ZHANG Xiaoyu, LIU Rui, SONG Tao, et al. Re-FeMAT: A reconfigurable multifunctional FeFET-based memory architecture[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41(11): 5071–5084. doi: 10.1109/TCAD.2021.3140194 [15] SAITO D, KOBAYASHI T, KOGA H, et al. Analog in-memory computing in FeFET-based 1T1R array for edge AI applications[C]. 2021 Symposium on VLSI Circuits, Kyoto, Japan, 2021: 1–2. [16] FENG Ning, LI Hao, SU Chang, et al. A dynamic compact model for ferroelectric capacitance[J]. IEEE Electron Device Letters, 2022, 43(3): 390–393. doi: 10.1109/LED.2022.3141413 [17] SU Yuchao, LUO Naili, LIN Qiuzhen, et al. Many-objective optimization by using an immune algorithm[J]. Swarm and Evolutionary Computation, 2022, 69: 101026. doi: 10.1016/j.swevo.2021.101026 -

下载:

下载:

下载:

下载: