A Survey for Electronic Design Automation Based on Graph Neural Network

-

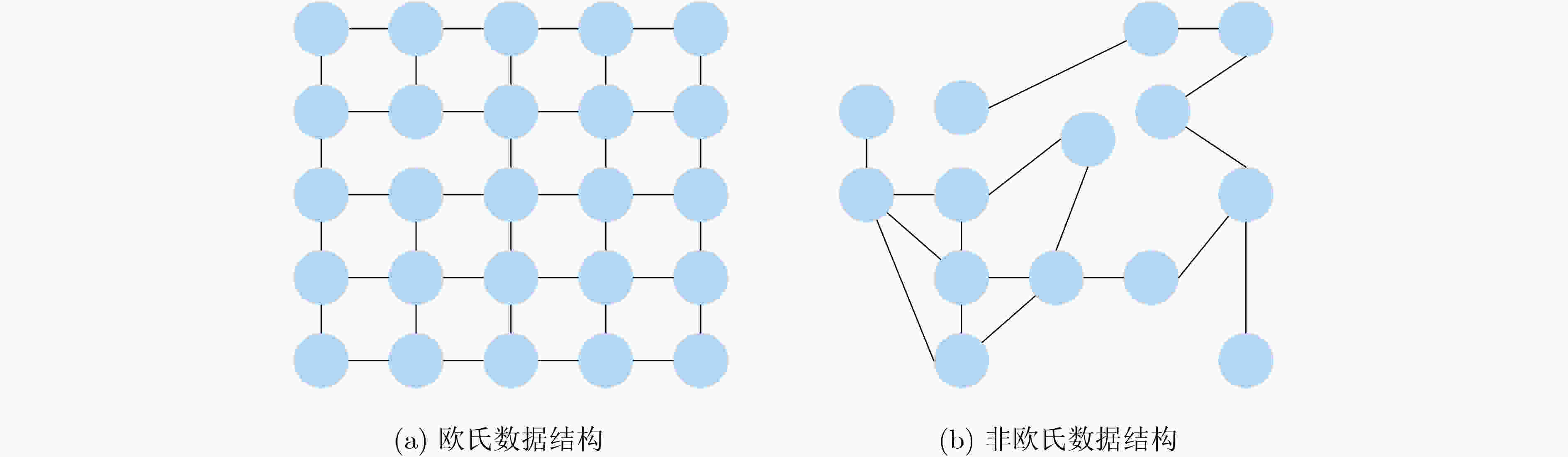

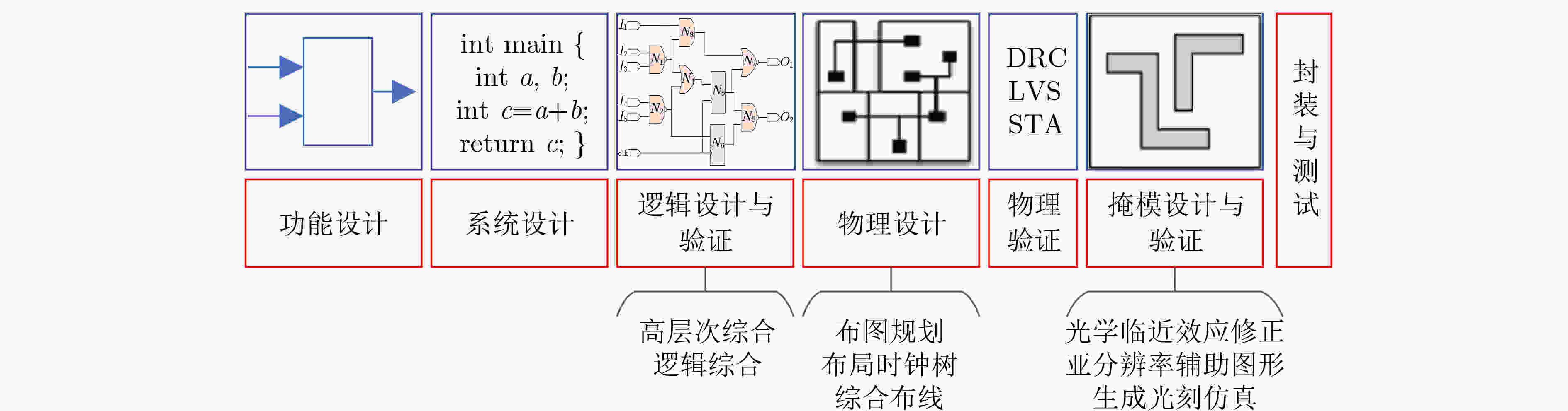

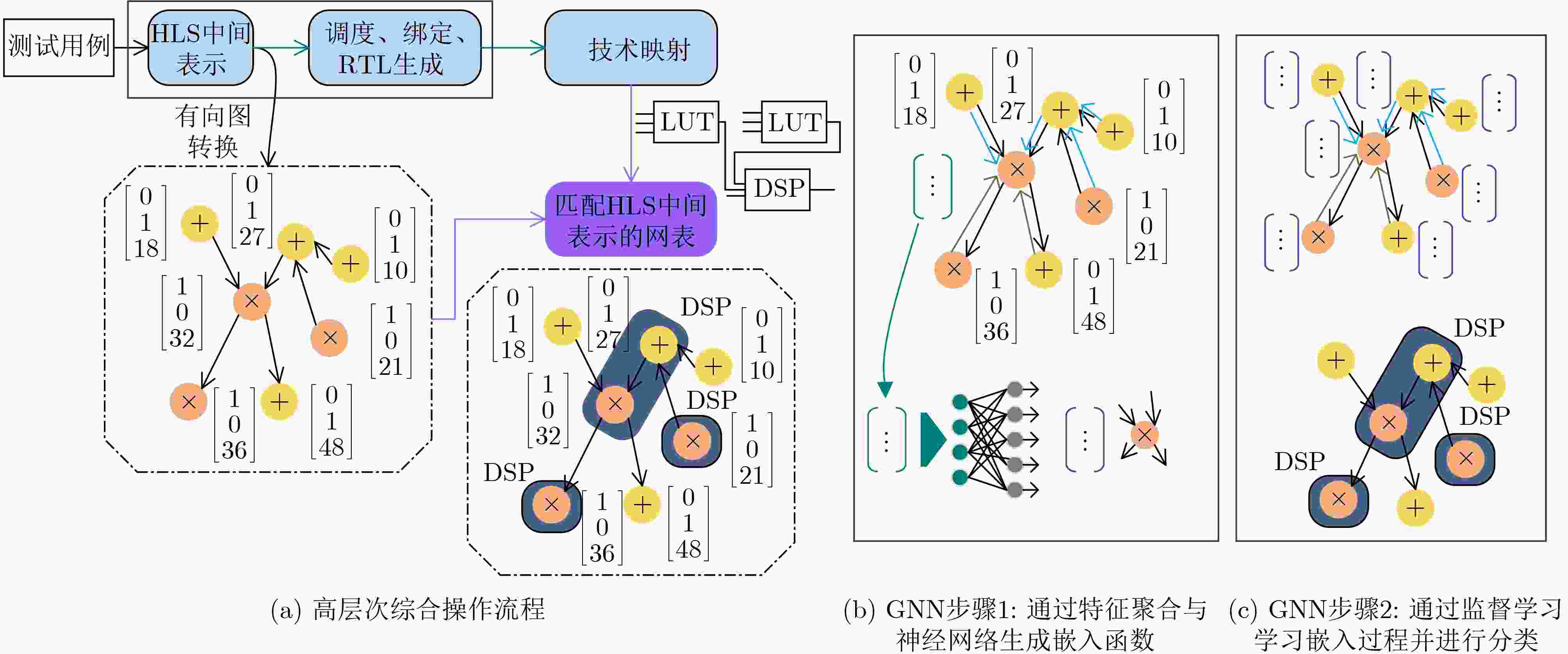

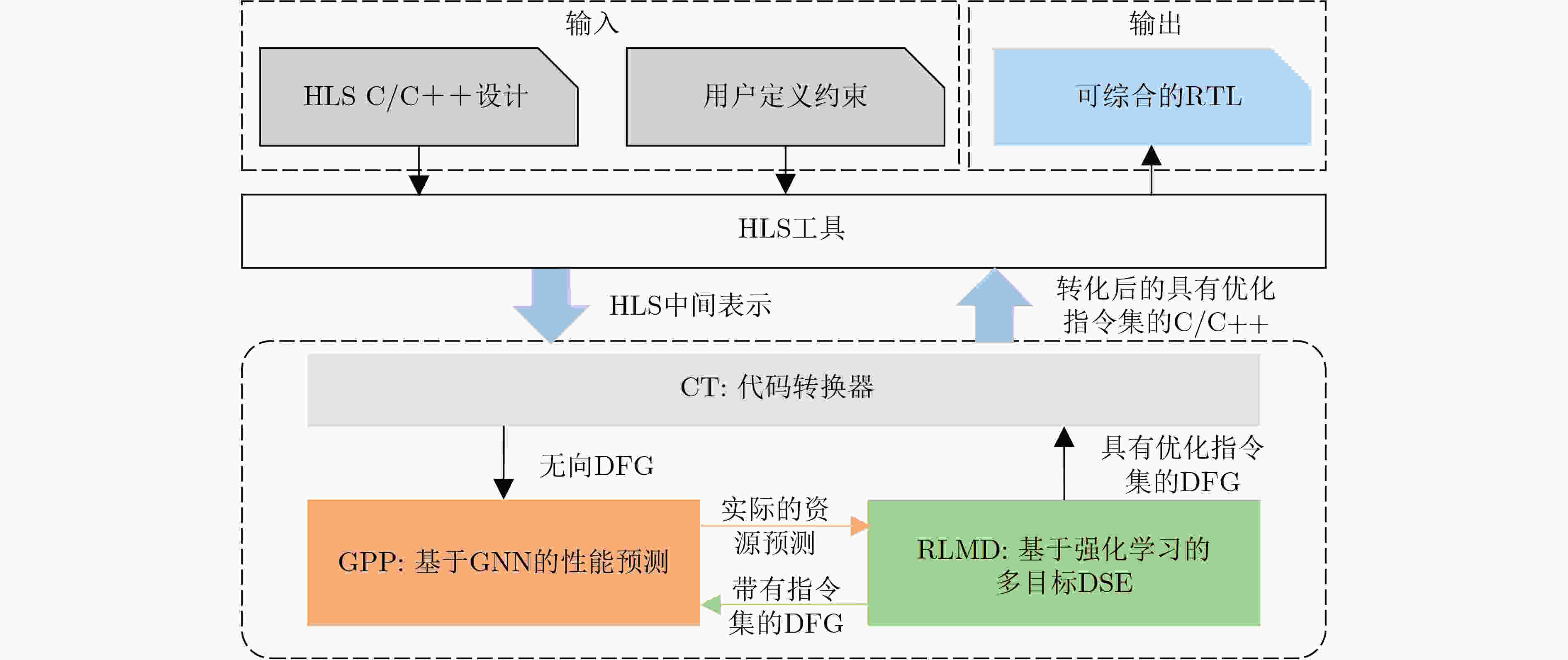

摘要: 在摩尔定律的推动下,工艺节点在不断演进,集成电路设计复杂度也在不断增加,电子设计自动化(EDA)技术面临着来自运行时间与计算资源等诸多方面的挑战。为了缓解这些挑战,机器学习方法已被纳入EDA工具的设计流程中。与此同时,鉴于电路网表作为图形数据的本质,图神经网络(GNN)在EDA流程中的应用正变得越来越普遍,为复杂问题的建模以及最优问题的求解带来了新思路。该文首先对GNN与EDA技术的概念内涵进行了简要的概述,详细地梳理了GNN在高层次综合(HLS)、逻辑综合、布图规划与布局、布线、反向工程、硬件木马检测以及测试点插入等不同EDA设计流程中的主要作用,以及当前基于GNN的EDA技术的一些重要探索。以希望为集成电路设计自动化以及相关领域的研究人员提供参考,为我国先进集成电路产业的发展提供技术支持。Abstract: Driven by Moore’s law, the aggressive shrinking of feature sizes, and the complexity of the chip design is also steadily increasing. Electronic Design Automation (EDA) technology faces challenges from many aspects such as runtime and computing resources. To alleviate these challenges, machine learning methods are incorporated into the design process of EDA tools. At the same time, given the nature of circuit netlist as graphical data, the application of Graph Neural Network (GNN) in the EDA is becoming more and more common, bring new ideas for modeling complex problems and solving optimal problems. A brief overview of the concept GNN and EDA is presented. The main role of GNN in different EDA stages such as High Level Synthesis (HLS), logic synthesis, floorplan and placement, routing, reverse engineering, hardware trojan detection and test point insertion is summarized. The main role of GNN in the EDA design process is sorted out in detail, as well as some important explorations of current GNN-based EDA technology. It is hoped to provide reference for researchers in integrated circuit design automation and related fields, and provide technical support for China’s advanced integrated circuit industry.

-

表 1 基于GNN的EDA技术

EDA技术分类 GNN模型 具体描述 参考文献 逻辑综合 GraphSAGE HLS阶段学习如何将算术运算映射为实际的FPGA资源 文献[26]: D-SAGE GCN 在尽可能早的阶段快速完成对HLS设计关于资源使用和时序性能的预测评估 文献[27] GCN HLS阶段进行性能的预测评估,同时进行设计空间探索,提供不同目标间的帕累托最优解决方案 文献[28]: IRONMAN

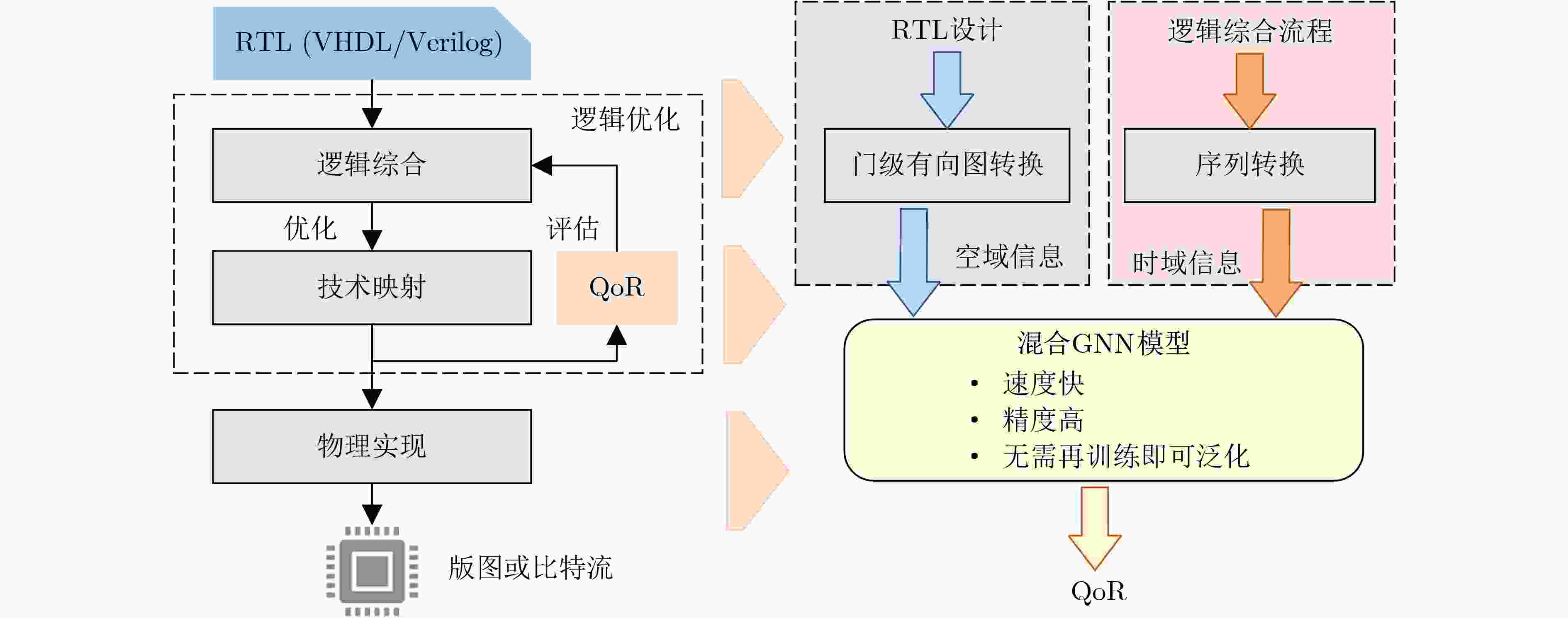

文献[29]: IRONMAN-PROGCN 利用来自硬件设计和逻辑综合流程的空时信息完成不同设计在各种逻辑综合流程中关于延时及面积信息的预测 文献[30]: LOSTIN 布图规划

与布局Edge-GNN

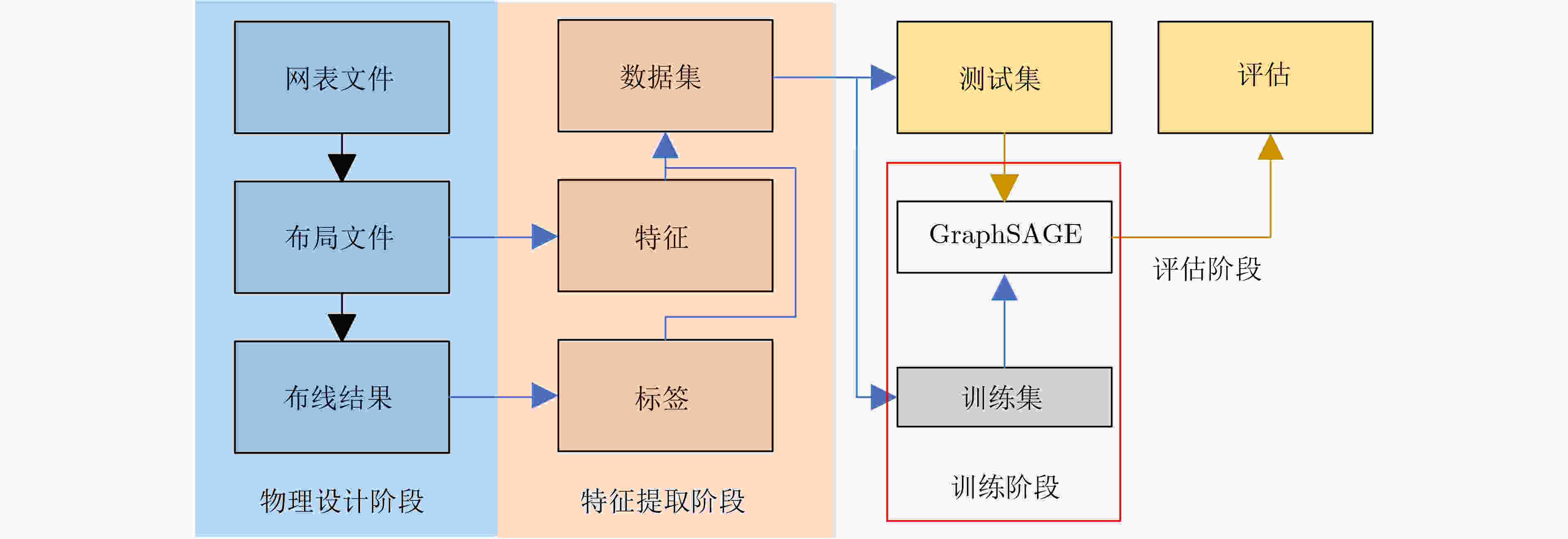

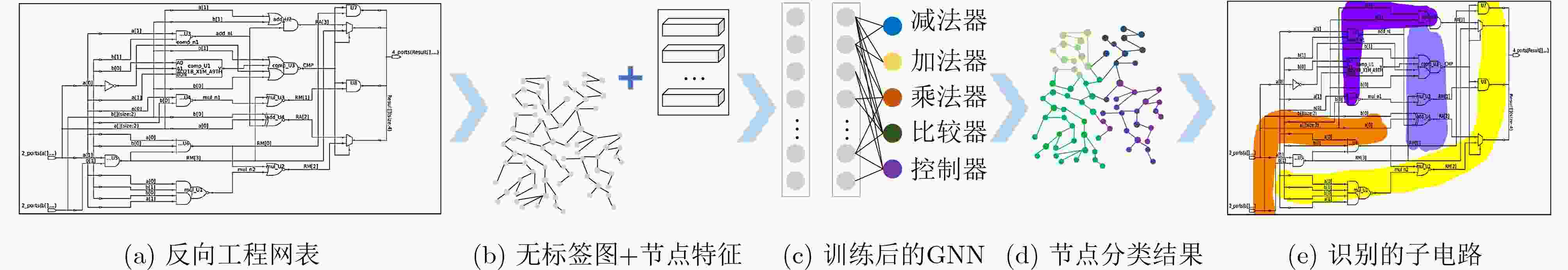

图强化学习将数字集成电路宏模块布图规划问题转化为强化学习问题,进一步进行求解 文献[31] GraphSAGE 将逻辑单元进行聚类,从而优化布局流程,加速布局流程收敛 文献[32]、文献[33] GCN 同时考虑了宏模块与标准单元的布局求解问题 文献[34]: DeepPlace GCN 布局阶段完成拥塞预测 文献[35] GCN 布局阶段完成拥塞预测 文献[36] GraphSAGE 通过提取完整的能够反映短路违例的特征参数,在布局阶段利用GraphSAGE模型完成短路违例的预测 文献[37] 布线 GCN 利用GCN的详细节点嵌入作为强化学习的策略网络指导布线流程的优化 文献[34]: DeepPR 反向工程与硬件木马检测 GAT/GraphSAINT 门级网表中进行子电路的分类与提取 文献[43]: GNN-RE ABGNN 提升GNN在门级网表算数块识别过程中的可扩展性,并利用开源RISC-V处理器的门级网表进行验证 文献[44] GCN 在事先不了解设计IP或硬件木马结构的前提下完成对RTL设计中硬件木马的快速检测与识别 文献[45]: GNN4TJ

文献[46-49]测试点的选取 GCN 快速进行测试点的插入以及时序模型的选择 文献[20] GCNNs 快速处理数字逻辑电路中不规则的图表示,提高故障覆盖率 文献[51] -

[1] 田春生, 陈雷, 王源, 等. 基于机器学习的FPGA电子设计自动化技术研究综述[J]. 电子与信息学报, 2023, 45(1): 1–13. doi: 10.11999/JEIT220183TIAN Chunsheng, CHEN Lei, WANG Yuan, et al. A survey on FPGA electronic design automation technology based on machine learning[J]. Journal of Electronics &Information Technology, 2023, 45(1): 1–13. doi: 10.11999/JEIT220183 [2] 贺旭, 王耀, 傅智勇, 等. 敏捷设计中基于机器学习的静态时序分析方法综述[J]. 计算机辅助设计与图形学学报, 2023, 35(4): 640–652. doi: 10.3724/SP.J.1089.2023.19557HE Xu, WANG Yao, FU Zhiyong, et al. A survey on machine learning-based technology for static timing analysis in agile design[J]. Journal of Computer-Aided Design &Computer Graphics, 2023, 35(4): 640–652. doi: 10.3724/SP.J.1089.2023.19557 [3] KAHNG A B, LIENIG J, MARKOV I L, et al. VLSI Physical Design: From Graph Partitioning to Timing Closure[M]. Dordrecht: Springer, 2011. [4] ITRS. International technology roadmap for semiconductors 2.0 publication[EB/OL]. http://www.itrs2.net/itrs-reports.html. [5] 殷佳琪, 潘涛. 集成电路产业综述[J]. 科技资讯, 2021, 19(28): 54–58,63. doi: 10.16661/j.cnki.1672-3791.2110-5042-8981YIN Jiaqi and PAN Tao. Overview of integrated circuit industry[J]. Science &Technology Information, 2021, 19(28): 54–58,63. doi: 10.16661/j.cnki.1672-3791.2110-5042-8981 [6] CHEN T. An ANN approach for modeling the multisource yield learning process with semiconductor manufacturing as an example[J]. Computers & Industrial Engineering, 2017, 103: 98–104. doi: 10.1016/j.cie.2016.11.021 [7] DING Duo, TORRES J A, and PAN D Z. High performance lithography hotspot detection with successively refined pattern identifications and machine learning[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2011, 30(11): 1621–1634. doi: 10.1109/TCAD.2011.2164537 [8] WARD S, DING D, and PAN D Z. PADE: A high-performance placer with automatic datapath extraction and evaluation through high-dimensional data learning[C]. DAC Design Automation Conference 2012, San Francisco, USA, 2012: 756–761. [9] WANG Fanchao, ZHU Hanbin, POPLI P, et al. Accelerating coverage directed test generation for functional verification: A neural network-based framework[C]. The 2018 on Great Lakes Symposium on VLSI, Chicago, USA, 2018: 207–212. [10] KIELY T and GIELEN G. Performance modeling of analog integrated circuits using least-squares support vector machines[C]. Design, Automation and Test in Europe Conference and Exhibition, Paris, France, 2004: 448–453. [11] KAHNG A B, LIN B, and NATH S. ORION 3.0: A comprehensive NoC router estimation tool[J]. IEEE Embedded Systems Letters, 2015, 7(2): 41–45. doi: 10.1109/LES.2015.2402197 [12] YU Bei, PAN D Z, MATSUNAWA T, et al. Machine learning and pattern matching in physical design[C]. The 20th Asia and South Pacific Design Automation Conference, Chiba, Japan, 2015: 286–293. [13] HUANG Guyue, HU Jingbo, HE Yifan, et al. Machine learning for electronic design automation: A survey[J]. ACM Transactions on Design Automation of Electronic Systems, 2021, 26(5): 40. doi: 10.1145/3451179 [14] 田春生, 陈雷, 王源, 等. 面向FPGA的布局与布线技术研究综述[J]. 电子学报, 2022, 50(5): 1243–1254. doi: 10.12263/DZXB.20210637TIAN Chunsheng, CHEN Lei, WANG Yuan, et al. Review on technology of placement and routing for the FPGA[J]. Acta Electronica Sinica, 2022, 50(5): 1243–1254. doi: 10.12263/DZXB.20210637 [15] YIN Xiaoyan, LIN Wanyu, SUN Kexin, et al. A2S2-GNN: Rigging GNN-based social status by adversarial attacks in signed social networks[J]. IEEE Transactions on Information Forensics and Security, 2023, 18: 206–220. doi: 10.1109/TIFS.2022.3219342 [16] LI Jianxin, PENG Hao, CAO Yuwei, et al. Higher-order attribute-enhancing heterogeneous graph neural networks[J]. IEEE Transactions on Knowledge and Data Engineering, 2023, 35(1): 560–574. doi: 10.1109/TKDE.2021.3074654 [17] KIM M, KIM J, QU J, et al. Interpretable temporal graph neural network for prognostic prediction of Alzheimer’s disease using longitudinal neuroimaging data[C]. 2021 IEEE International Conference on Bioinformatics and Biomedicine (BIBM), Houston, USA, 2021: 1381–1384. [18] REN Haoxiang, NATH S, ZHANG Yanqing, et al. Why are graph neural networks effective for EDA problems[C]. 2022 IEEE/ACM International Conference On Computer Aided Design (ICCAD), San Diego, USA, 2022: 1–8. [19] LU Y C and LIM S K. On advancing physical design using graph neural networks[C]. The 41st IEEE/ACM International Conference on Computer-Aided Design, San Diego, USA, 2022: 2. [20] MA Yuzhe, HE Zhuolun, LI Wei, et al. Understanding graphs in EDA: From shallow to deep learning[C]. The 2020 International Symposium on Physical Design, Taipei, China, 2020: 119–126. [21] KHAILANY B. Accelerating chip design with machine learning[C]. The 2020 ACM/IEEE Workshop on Machine Learning for CAD, Iceland, 2020: 33. [22] 李甜甜, 张荣梅, 张佳慧. 图神经网络技术研究综述[J]. 河北省科学院学报, 2022, 39(2): 1–13. doi: 10.16191/j.cnki.hbkx.2022.02.007LI Tiantian, ZHANG Rongmei, and ZHANG Jiahui. Research review of graph neural network technology[J]. Journal of the Hebei Academy of Sciences, 2022, 39(2): 1–13. doi: 10.16191/j.cnki.hbkx.2022.02.007 [23] 马帅, 刘建伟, 左信. 图神经网络综述[J]. 计算机研究与发展, 2022, 59(1): 47–80. doi: 10.7544/issn1000-1239.20201055MA Shuai, LIU Jianwei, and ZUO Xin. Survey on graph neural network[J]. Journal of Computer Research and Development, 2022, 59(1): 47–80. doi: 10.7544/issn1000-1239.20201055 [24] SÁNCHEZ D, SERVADEI L KIPRIT G N, et al. A comprehensive survey on electronic design automation and graph neural networks: Theory and applications[J]. ACM Transactions on Design Automation of Electronic Systems, 2023, 28(2): 15. doi: 10.1145/3543853 [25] 林亦波, 高笑涵, 陈廷欢, 等. 机器学习辅助数字集成电路后端设计方法[J]. 微纳电子与智能制造, 2021, 3(2): 11–20. doi: 10.19816/j.cnki.10-1594/tn.2021.02.011LIN Y B, GAO X H, CHEN T H, et al. Machine learning for digital circuit backend design[J]. Micro/Nano Electronics and Intelligent Manufacturing, 2021, 3(2): 11–20. doi: 10.19816/j.cnki.10-1594/tn.2021.02.011 [26] USTUN E, DENG Chenhui, PAL D, et al. Accurate operation delay prediction for FPGA HLS using graph neural networks[C]. The 39th International Conference on Computer-Aided Design, New York, USA, 2020: 87. [27] WU Nan, YANG Hang, XIE Yuan, et al. High-level synthesis performance prediction using GNNs: Benchmarking, modeling, and advancing[C]. The 59th ACM/IEEE Design Automation Conference, San Francisco California, USA, 2022: 49–54. [28] WU Nan, XIE Huan, and HAO Cang. IronMan: GNN-assisted design space exploration in high-level synthesis via reinforcement learning[C]. 2021 on Great Lakes Symposium on VLSI, New York, USA, 2021: 39–44. [29] WU Nan, XIE Yuan, and HAO Cong. IRONMAN-PRO: Multiobjective design space exploration in HLS via reinforcement learning and graph neural network-based modeling[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2023, 42(3): 900–913. doi: 10.1109/TCAD.2022.3185540 [30] WU Nan, LEE J, XIE Yuan, et al. LOSTIN: Logic optimization via spatio-temporal information with hybrid graph models[C]. 2022 IEEE 33rd International Conference on Application-specific Systems, Architectures and Processors (ASAP), Gothenburg, Sweden, 2022: 11–18. [31] MIRHOSEINI A, GOLDIE A, YAZGAN M, et al. A graph placement methodology for fast chip design[J]. Nature, 2021, 594(7862): 207–212. doi: 10.1038/s41586–021-03544-w [32] AGNESINA A, PENTAPATI S, and LIM S K. A general framework for VLSI tool parameter optimization with deep reinforcement learning[C/OL]. The NeurIPS 2020 Workshop on Machine Learning for Systems, 2020: 6–12. [33] LU Yichen, PENTAPATI S, and LIM S K. The law of attraction: Affinity-aware placement optimization using graph neural networks[C/OL]. The 2021 International Symposium on Physical Design, 2021: 7–14. [34] CHENG Ruoyu and YAN Junchi. On joint Learning for solving placement and routing in chip design[C/OL]. 35th Conference on Neural Information Processing Systems, 2021: 16508–16519. [35] KIRBY R, GODIL S, ROY R, et al. CongestionNet: Routing congestion prediction using deep graph neural networks[C]. 2019 IFIP/IEEE 27th International Conference on Very Large Scale Integration (VLSI-SoC), Cuzco, Peru, 2019: 217–222. [36] GHOSE A, ZHANG V, ZHANG Yingxue, et al. Generalizable cross-graph embedding for GNN-based congestion prediction[C]. 2021 IEEE/ACM International Conference on Computer Aided Design (ICCAD), Munich, Germany, 2021: 1–9. [37] CHEN Xuan, DI Zhixiong, WU Wei, et al. Detailed routing short violation prediction using graph-based deep learning model[J]. IEEE Transactions on Circuits and Systems II:Express Briefs, 2022, 69(2): 564–568. doi: 10.1109/TCSII.2021.3093420 [38] TABRIZI A F, RAKAI L, DARAV N K, et al. A machine learning Framework to identify detailed routing short violations from a placed netlist[C]. 2018 55th ACM/ESDA/IEEE Design Automation Conference (DAC), San Francisco, USA, 2018: 1–6. [39] LI Wenchao, GASCOM A, SUBRAMANYAN P, et al. WordRev: Finding word-level structures in a sea of bit-level gates[C]. 2013 IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), Austin, USA, 2013: 67–74. [40] LI Wenchao, WASSON Z, and SESHIA S A. Reverse engineering circuits using behavioral pattern mining[C]. 2012 IEEE International Symposium on Hardware-Oriented Security and Trust, San Francisco, USA, 2012: 83–88. [41] SUBRAMANYAN P, TSISKARIDZE N, LI Wenchao, et al. Reverse engineering digital circuits using structural and functional analyses[J]. IEEE Transactions on Emerging Topics in Computing, 2014, 2(1): 63–80. doi: 10.1109/TETC.2013.2294918 [42] GASCÓM A, SUBRAMANYAN P, DUTERTRE B, et al. Template-based circuit understanding[C]. 2014 Formal Methods in Computer-Aided Design (FMCAD), Lausanne, Switzerland, 2014: 83–90. [43] ALRAHIS L, SENGUPTA A, KNECHTEL J, et al. GNN-RE: Graph neural networks for reverse engineering of gate-level netlists[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41(8): 2435–2448. doi: 10.1109/TCAD.2021.3110807 [44] HE Zhuolun, WANG Ziyi, BAIL C, et al. Graph learning-based arithmetic block identification[C]. 2021 IEEE/ACM International Conference On Computer Aided Design (ICCAD), Munich, Germany, 2021: 1–8. [45] YASAEI R, YU S Y, and AI FARUQUE M A. GNN4TJ: Graph neural networks for hardware Trojan detection at register transfer level[C]. 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2021: 1504–1509. [46] HASEGAWA K, YAMASHITA K, HIDANO S, et al. Node-wise hardware trojan detection based on graph learning[J]. IEEE Transactions on Computers. To be published. [47] MURALIDHAR N, ZUBAIR A, WEIDLER N, et al. Contrastive graph convolutional networks for hardware Trojan detection in third party IP cores[C]. 2021 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Tysons Corner, USA, 2021: 181–191. [48] CHENG Dong, DONG Chen, HE Wenwu, et al. GNN4Gate: A bi-directional graph neural network for gate-level hardware Trojan detection[C/OL]. 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2022: 1315–1320. [49] YASAEI R, YU S Y, NAEINI E K, et al. GNN4IP: Graph neural network for hardware intellectual property piracy detection[C]. 2021 58th ACM/IEEE Design Automation Conference (DAC), San Francisco, USA, 2021: 217–222. [50] ZHANG Yanqing, REN Haoxing, and KHAILANY B. GRANNITE: Graph neural network inference for transferable power estimation[C]. 2020 57th ACM/IEEE Design Automation Conference (DAC), San Francisco, USA, 2020: 1–6. [51] MA Yuzhe, REN Haoxing, KHAILANY B, et al. High performance graph convolutional networks with applications in testability analysis[C]. The 56th Annual Design Automation Conference 2019, Las Vegas, USA, 2019: 18. [52] CHAI Zhuomin, ZHAO Yuxiang, LIN Yibo, et al. CircuitNet: An open-source dataset for machine learning applications in electronic design automation (EDA)[J]. Science China Information Sciences, 2022, 65(12): 227401. doi: 10.1007/s11432-022-3571-8 [53] YU Yunxuan, ZHAO Tiandong, WANG Mingyu, et al. Uni-OPU: An FPGA-based uniform accelerator for convolutional and transposed convolutional networks[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2020, 28(7): 1545–1556. doi: 10.1109/TVLSI.2020.2995741 -

下载:

下载:

下载:

下载: