Chip Collaborative Protection Design Method Based on Piecewise Linear Model for Transmission Line Pulse Transient Interference Signal

-

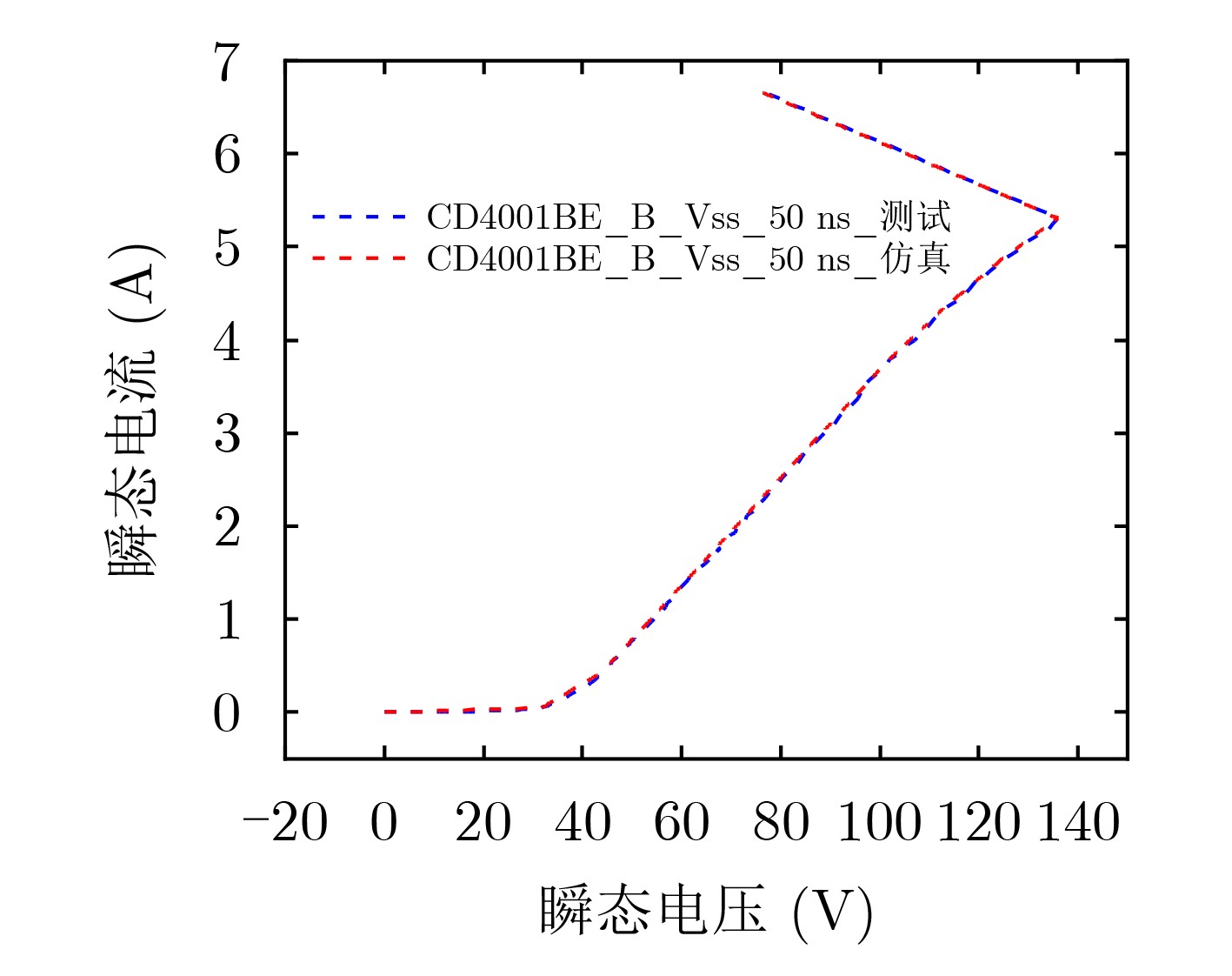

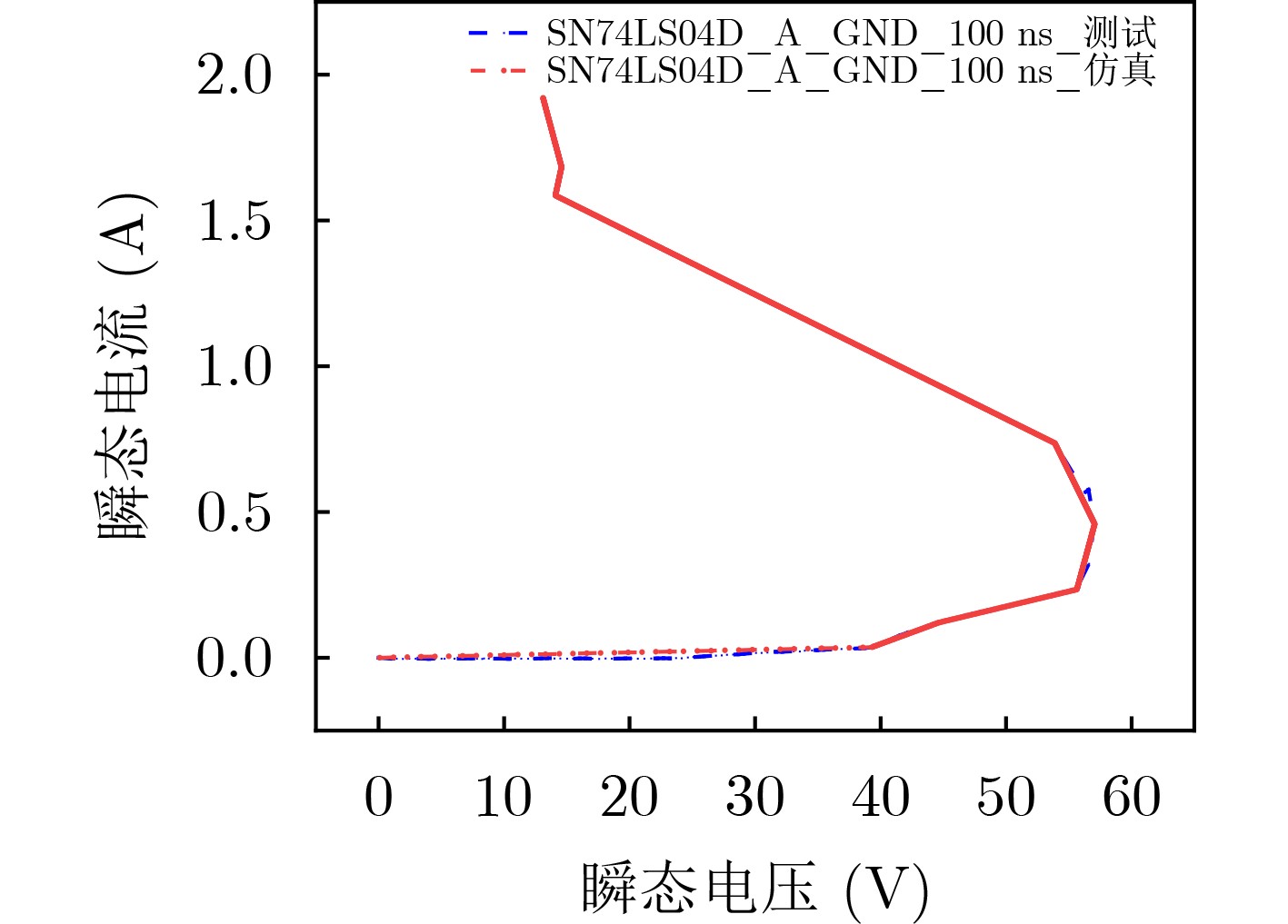

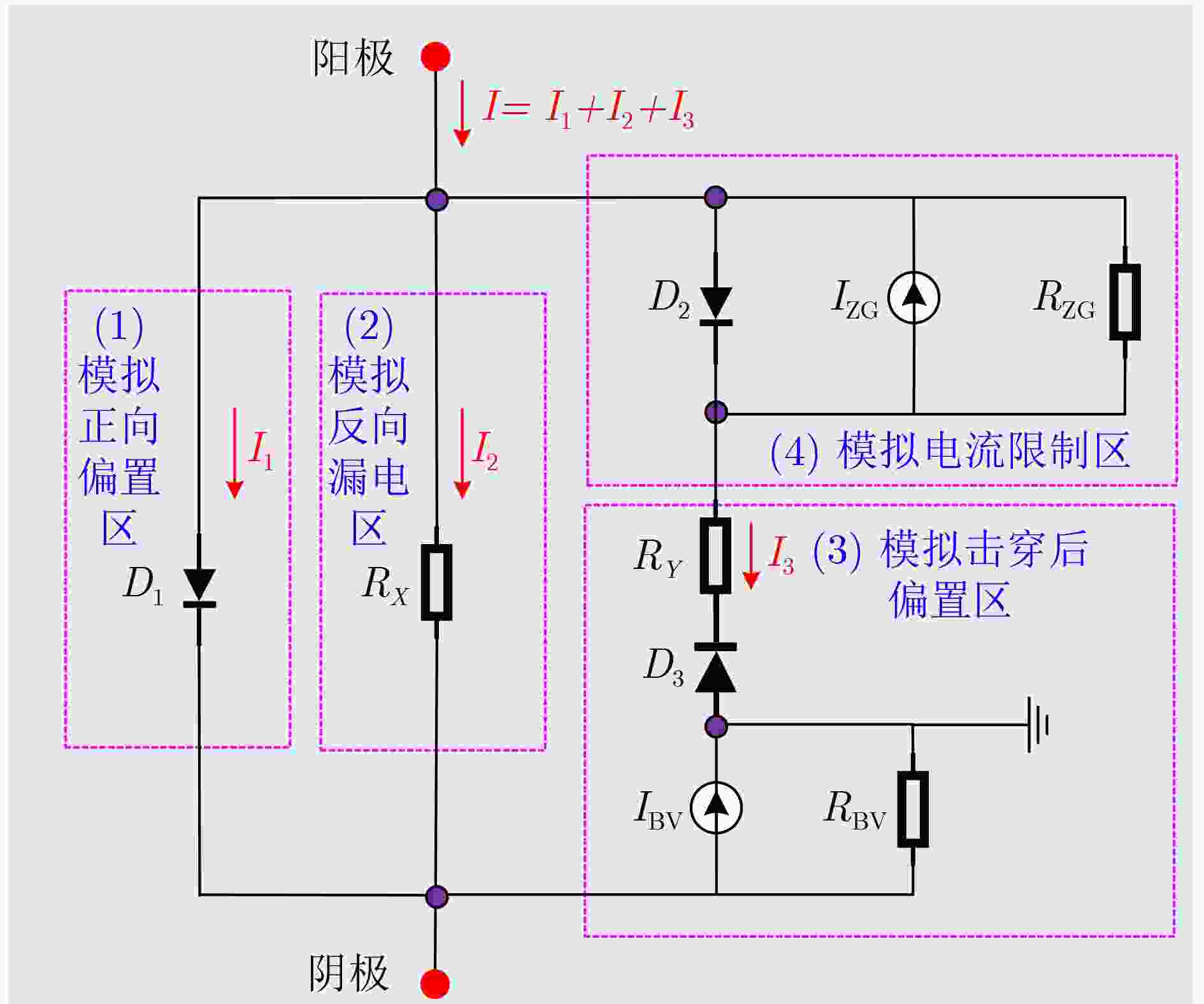

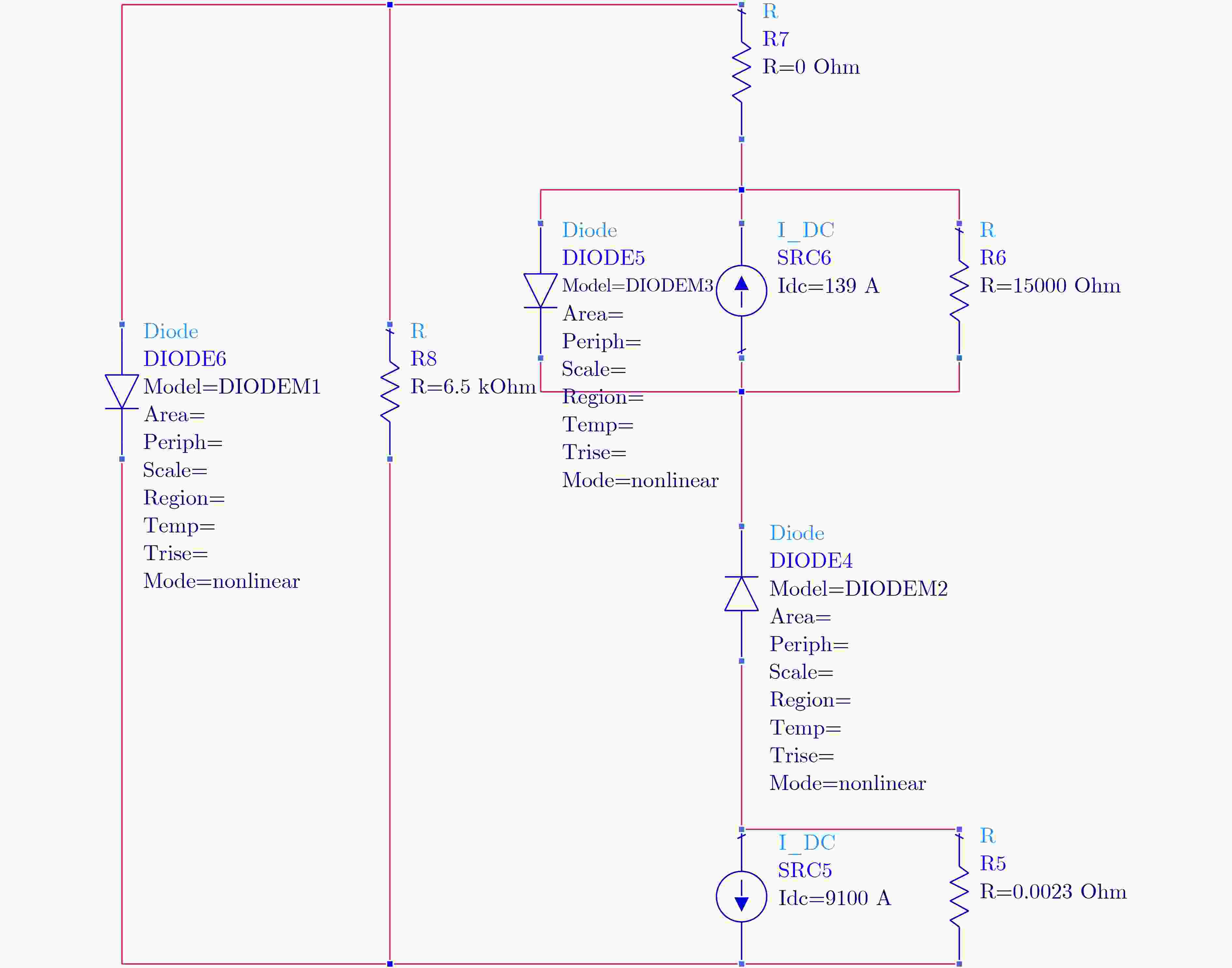

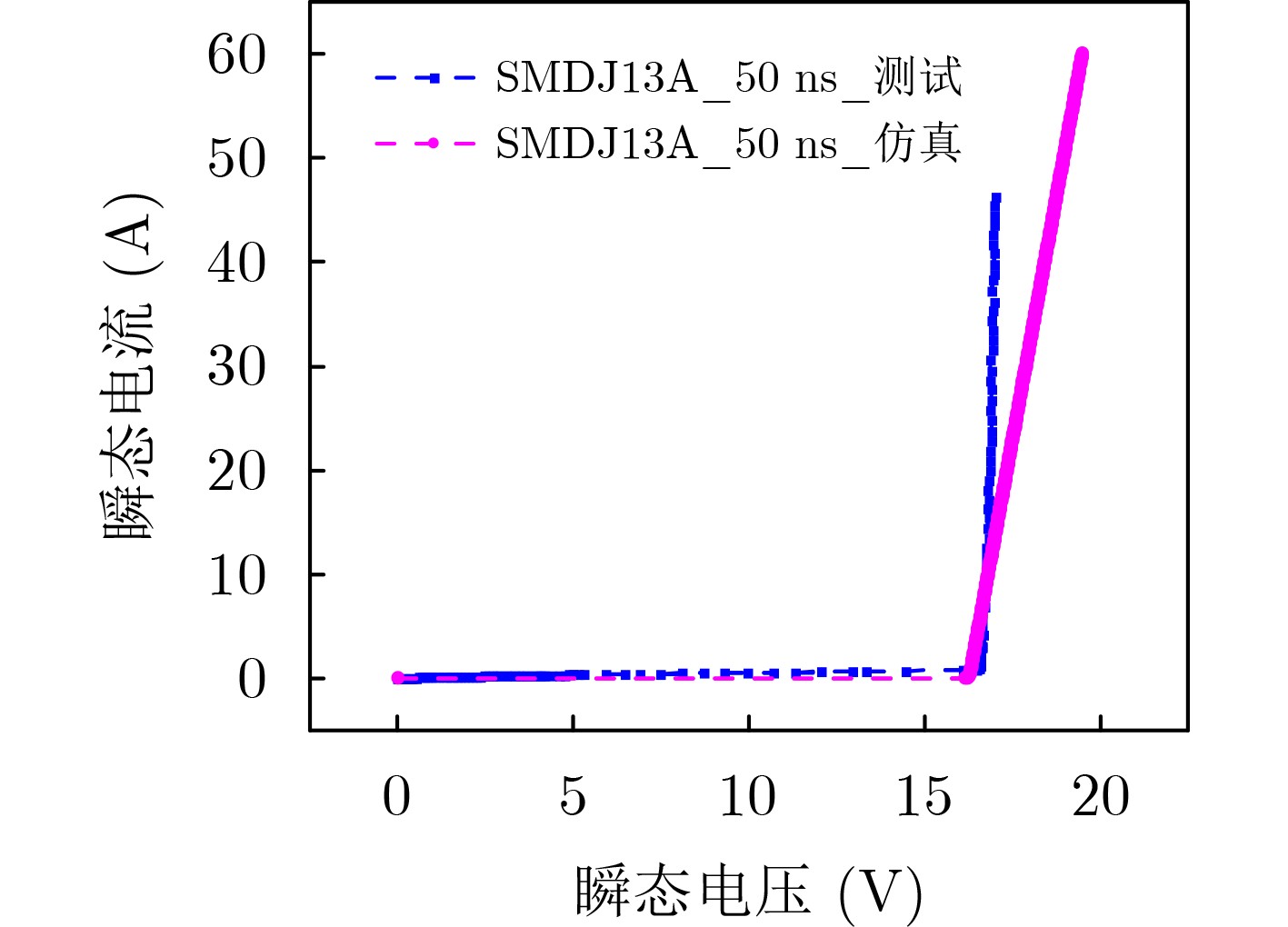

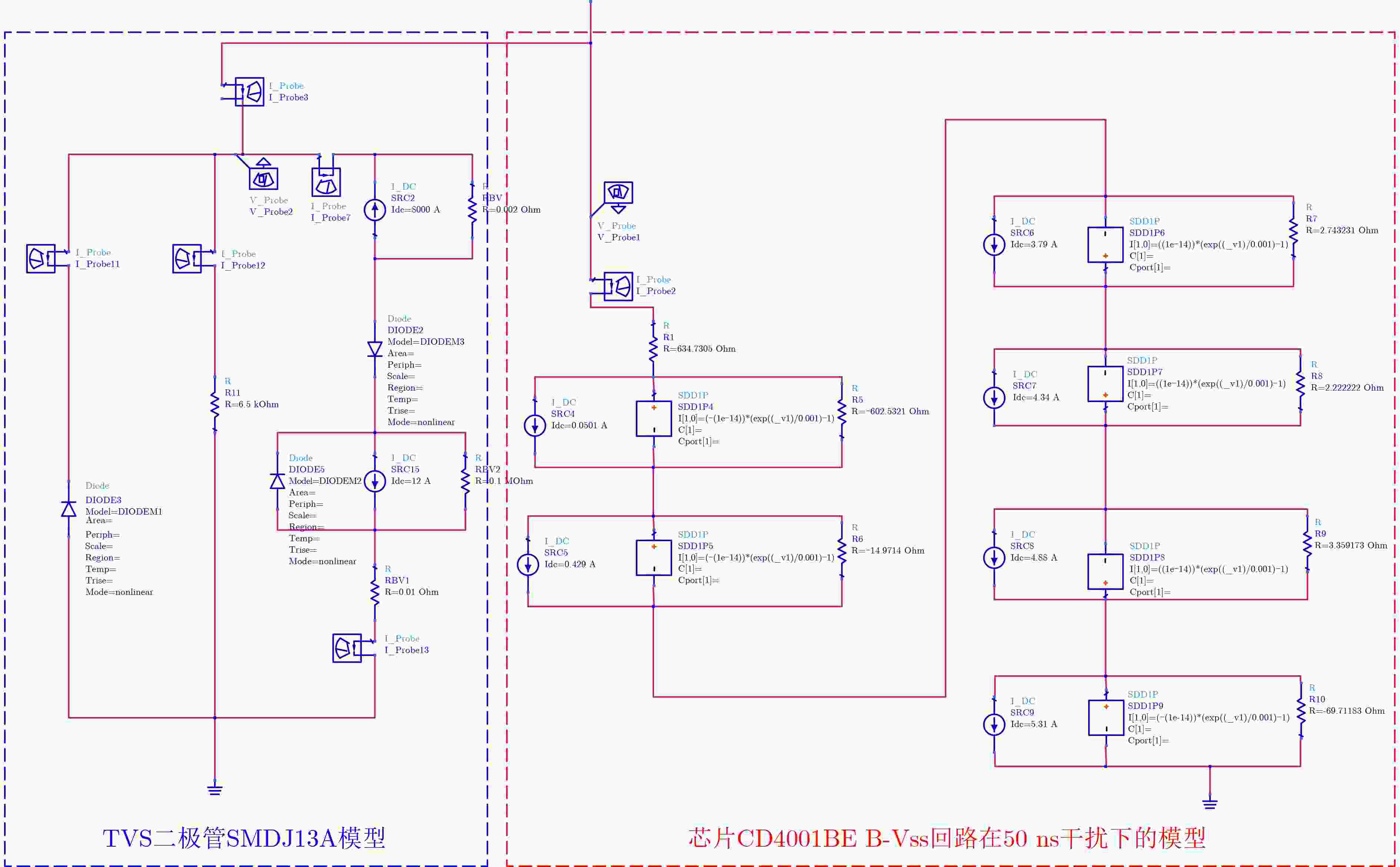

摘要: 随着电子设备向小型化、高密度和高速的趋势发展,集成电路作为电子设备的基本核心单元也朝着这一方向发展,由此带来了越来越严重的电磁兼容问题。其中静电放电问题越来越引起设计者、制作者和使用者的重视。该文利用传输线脉冲(TLP)方法对芯片进行测试,获取了器件在应对静电放电干扰时的伏安特性数据。基于TLP测试数据应用分段线性建模方法构建了芯片应对静电放电干扰的模型。该文还根据二极管的等效电路及其数据手册的伏安特性数据构建了瞬态电压抑制(TVS)二极管模型,并通过TLP测试进行验证。同时,结合上述两个模型,开展了芯片静电放电干扰的协同防护设计方法研究,并应用实例验证了芯片的协同防护设计方法的可行性。该方法实现了用仿真模拟的方式进行芯片的协同防护设计,能够节约设计成本和时间。Abstract: With the development trend of miniaturization, high density and high speed of electronic equipment, integrated circuit, as the basic core unit of electronic equipment, is also developing in this direction, which brings more and more serious problems of electromagnetic compatibility. Among them, the problem of electrostatic discharge has attracted more and more attention of designers, producers and users. In this paper, the chip is tested by Transmission Line Pulse (TLP) method, and the volt ampere characteristic data of the device in response to electrostatic discharge interference are obtained. Based on the TLP test data, the piecewise linear modeling method is applied to build the model of the chip to deal with the electrostatic discharge interference. Based on the equivalent circuit of the diode and the volt ampere characteristic data in its data book, the Transient Voltage Suppression (TVS) diode model is constructed and verified by TLP test. At the same time, combined with the above two models, this paper carries out the research on the collaborative protection design method of chip electrostatic discharge interference, and obtains the collaborative protection design process and examples of the chip. This method realizes the collaborative protection design of the chip by simulation, which can save the design cost and time.

-

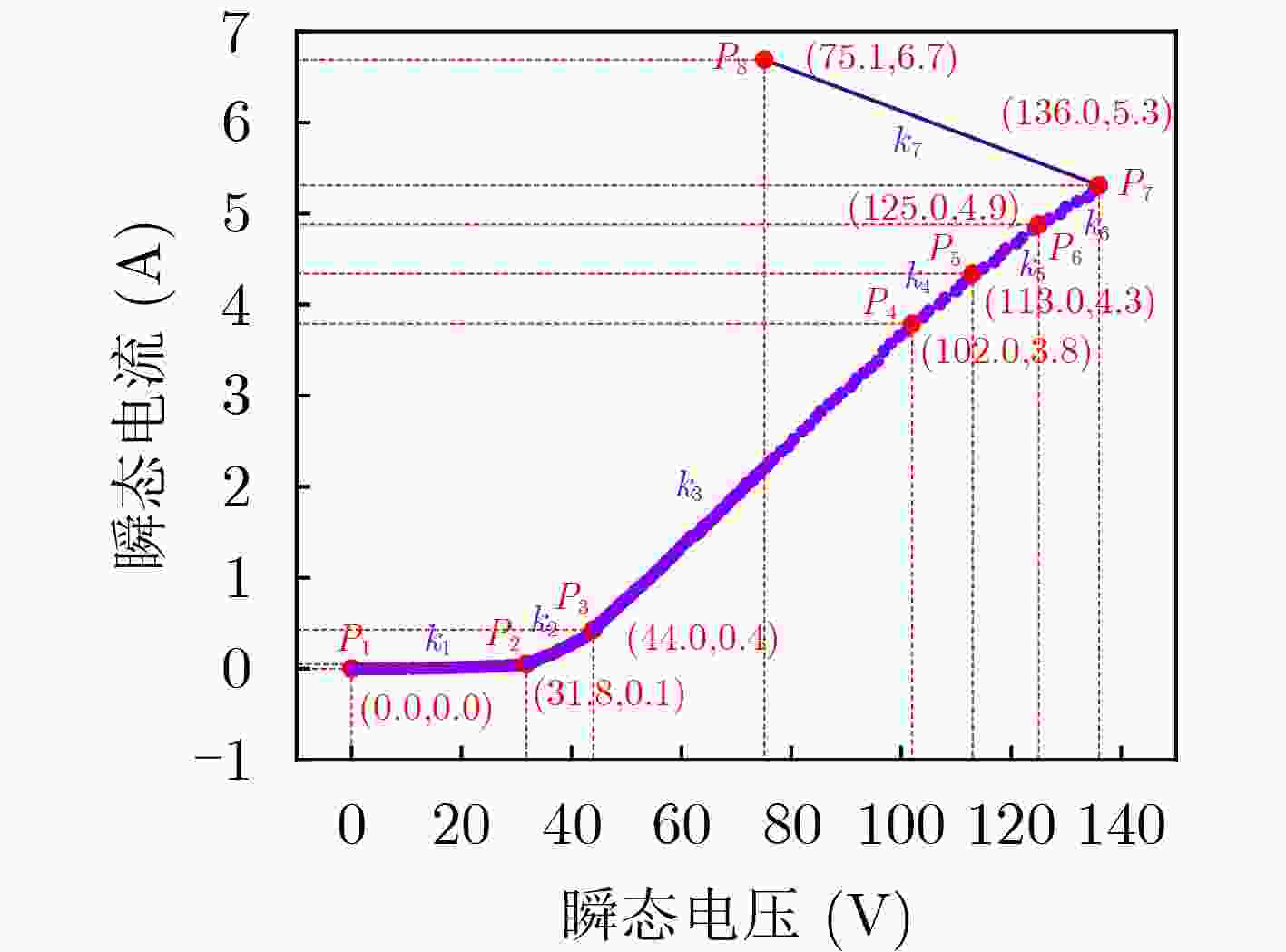

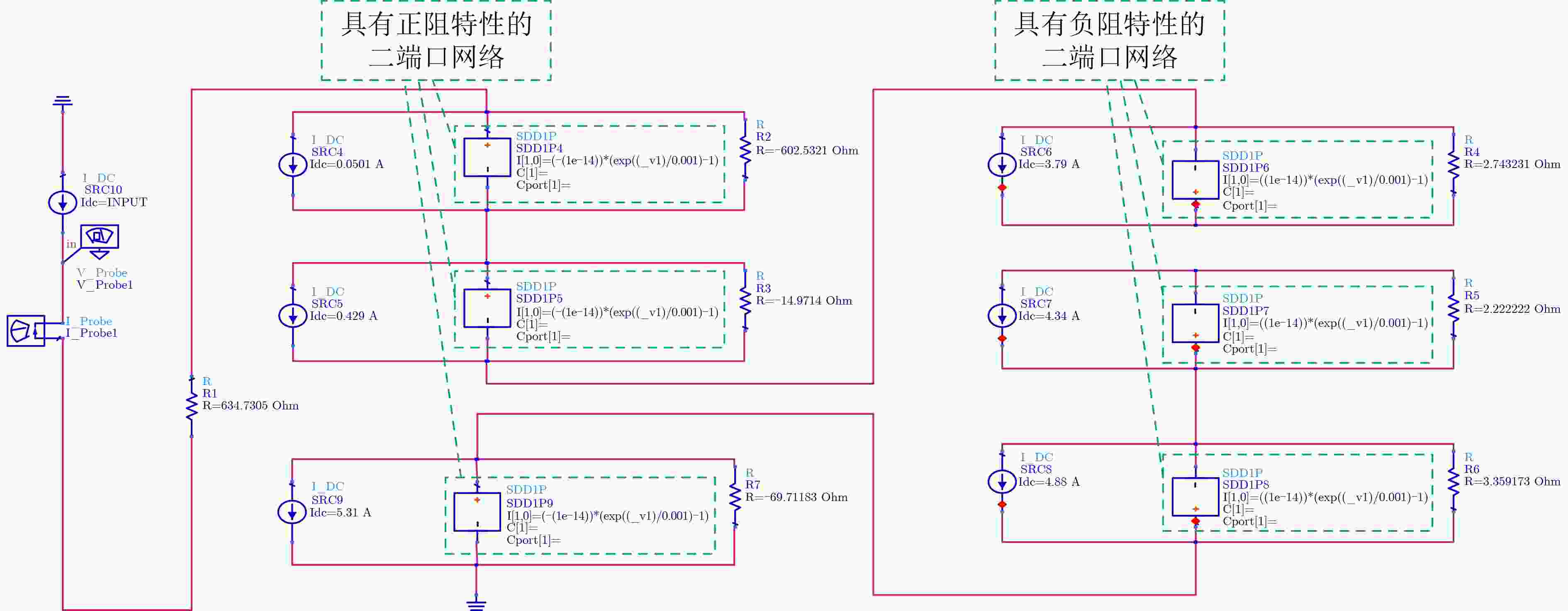

表 1 模型中的参数

拐点 瞬态电压(V) 瞬态电流(A) 电阻(Ω) 0 0 0 – 1 31.8 0.050 1 634.730 5 2 44 0.429 –602.532 1 3 102 3.79 –14.941 7 4 113 4.34 2.743 231 5 125 4.88 2.222 222 6 136 5.31 3.359 173 7 75.1 6.69 –69.711 83 表 2 TVS 二极管击穿电压参数对比(V)

序号 TVS型号 数据手册的击穿

电压实测击穿

电压仿真击穿

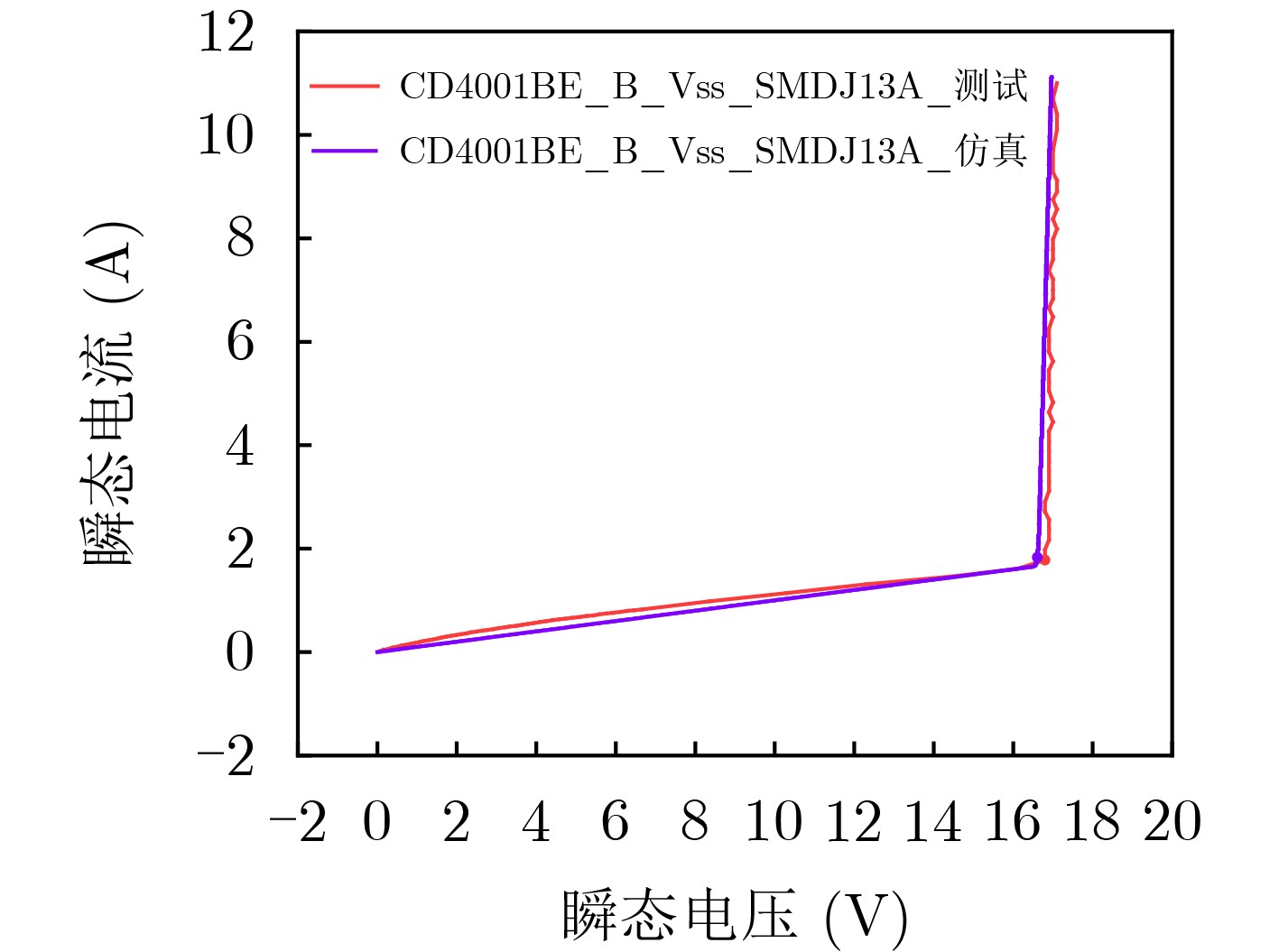

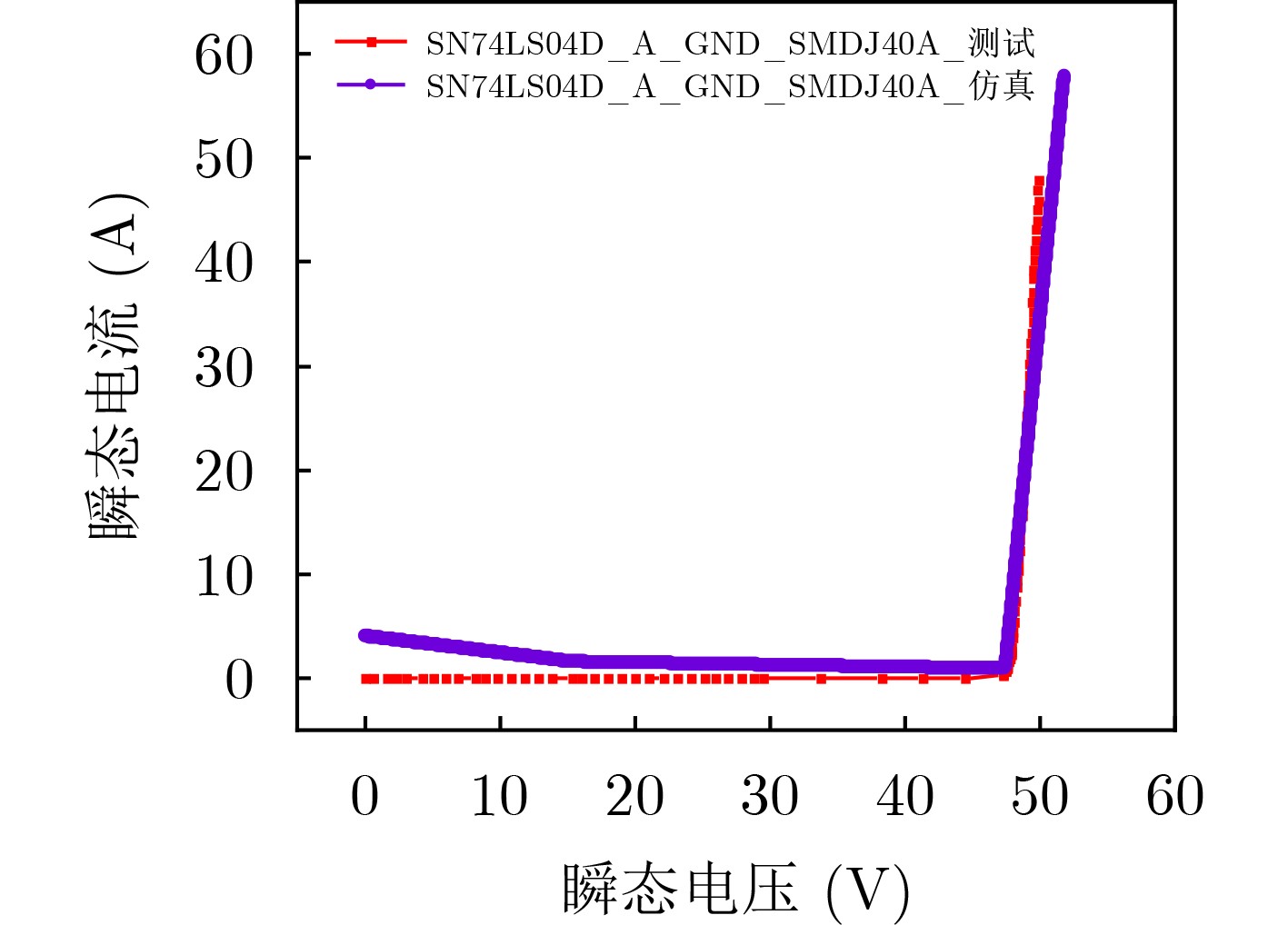

电压1 SMDJ13A 14.4~15.9 16.31 16.57 2 SMDJ40A 44.1~49.1 47.8 47.52 表 3 TVS 二极管最大钳位电压参数对比(V)

序号 TVS型号 数据手册的

钳位电压实测钳位电压 仿真钳位电压 1 SMDJ13A 21.5 17.0 19.5 2 SMDJ40A 64.5 50.3 52.0 -

[1] 付蕊. 基于场路协同仿真的电子设备电磁敏感性研究[D]. [硕士论文], 西安电子科技大学, 2020.FU Rui. Research on electromagnetic susceptibility of electronic equipment based on field-circuit cooperated simulation[D]. [Master dissertation], Xidian University, 2020. [2] JEON C, LIM H, JIN J, et al. A new method of component-level ESD test to assess system-level ESD risk for ICs[C]. 2019 Joint International Symposium on Electromagnetic Compatibility, Sapporo and Asia-Pacific International Symposium on Electromagnetic Compatibility (EMC Sapporo/APEMC), Sapporo, Japan, 2019: 681–684. [3] BOUANGEUNE D, HONG W K, CHOI S S, et al. ESD robustness of low-voltage/high-speed TVS devices with epitaxial grown films[C]. The 1st IEEE Global Conference on Consumer Electronics 2012, Tokyo, Japan, 2012: 189–192. [4] KHURANA N, MALONEY T, and YEH W. ESD on CHMOS devices - equivalent circuits, physical models and failure mechanisms[C]. The 23rd International Reliability Physics Symposium, Orlando, USA, 1985: 212–223. [5] MAAS J S, PRATT D J, and BOXLEITNER W. Furniture ESD-the forgotten parameter in ESD testing[C]. IEEE 1991 International Symposium on Electromagnetic Compatibility, Cherry Hill, USA, 1991: 248–252. [6] TS EN 60749–28-2008. Semiconductor devices - Mechanical and climatic test methods - Part 28: ElectroStatic Discharge (ESD) sensitivity testing - Direct contact charged device model (DC - CDM)[S]. 2018. [7] ESD. ANSI/ESD STM5.5. 1-2016 ESD association standard test method for elcetrostatic discharge sensitivity testing-Transmission Line Pulse (TLP) - device level[S]. Rome: EOS/ESD Association, 2016. [8] WANG A Z H. On-Chip ESD Protection for Integrated Circuits[M]. Boston: Kluwer Academic Publishers, 2002. [9] MUHONEN K, GRUND E, and ASHTON R. High-Speed TLP and ESD Characterization of ICs[C]. 2021 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, USA, 2021: 1–6. [10] BSI. IEC 62615: 2010 Electrostatic discharge sensitivity testing - Transmission Line Pulse (TLP)-Component level[S]. London: BSI, 2010. [11] DI BICCARI L, CERATI L, ZULLINO L, et al. HV ESD diodes investigation under vf-TLP stresses: TCAD approach[C]. 2016 38th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Garden Grove, USA, 2016: 1–10. [12] CHEN Qi, LI Cheng, LU Fei, et al. TLP measurement and analysis of graphene NEMS switches for on-chip ESD protection[C]. 2017 IEEE 12th International Conference on Nano/Micro Engineered and Molecular Systems (NEMS), Los Angeles, USA, 2017: 370–374. [13] HUANG Shaochang, LI C H, CHEN Lifan, et al. The correlations between ESD and TLP in large array devices[C]. 2020 IEEE International Conference on Consumer Electronics - Taiwan (ICCE-Taiwan), Taoyuan, China, 2020: 1–2. [14] MA Rui, WANG Li, ZHANG Chen, et al. TLP and HBM ESD test correlation for power ICs[C]. 2013 IEEE International Conference of Electron Devices and Solid-state Circuits, Hong Kong, China, 2013: 1–2. [15] XI Yunfeng, MALOBABIC S, VASHCHENKO V, et al. Correlation between TLP, HMM, and system-level ESD pulses for Cu metallization[J]. IEEE Transactions on Device and Materials Reliability, 2014, 14(1): 446–450. doi: 10.1109/TDMR.2013.2292039 [16] SANTORO R P. Piecewise-linear modeling of I-V characteristics with SPICE[J]. IEEE Transactions on Education, 1995, 38(2): 107–117. doi: 10.1109/13.387211 [17] AUSTERMANN C, SCHEIER S, FREI S, et al. Modellierung von ESD schutzelementen mit snapback-verhalten[J]. Tagungsband 14. ESD-Forum, 2015: 115–120. [18] 王志明. 应用于CAN总线静电保护的低电容TVS二极管设计[D]. [硕士论文], 电子科技大学, 2021.WANG Zhiming. Design of low capacitance TVS diodes for CAN bus electrostatic protection[D]. [Master dissertation], University of Electronic Science and Technology of China, 2021. [19] KASHYAP A S, SANDVIK P, MCMAHON J, et al. Silicon carbide transient voltage suppressor for next generation lightning protection[C]. 2014 IEEE Workshop on Wide Bandgap Power Devices and Applications, Knoxville, USA, 2014: 147–150. [20] 黄薇, 罗启元, 蒋同全, 等. 瞬态电压抑制二极管的建模及仿真[J]. 太赫兹科学与电子信息学报, 2014, 12(6): 927–931,936. doi: 10.11805/TKYDA201406.0927HUANG Wei, LUO Qiyuan, JIANG Tongquan, et al. Modeling and simulation of the transient voltage suppression diode[J]. Journal of Terahertz Science and Electronic Information Technology, 2014, 12(6): 927–931,936. doi: 10.11805/TKYDA201406.0927 [21] 周月宾, 饶宏, 许树楷, 等. 一种二极管箝位型MMC的高效等值建模方法[J]. 中国电机工程学报, 2016, 36(7): 1925–1932. doi: 10.13334/j.0258-8013.pcsee.2016.07.020ZHOU Yuebin, RAO Hong, XU Shukai, et al. An equivalent efficient modeling approach for diode clamp sub-module based MMC[J]. Proceedings of the CSEE, 2016, 36(7): 1925–1932. doi: 10.13334/j.0258-8013.pcsee.2016.07.020 [22] SHEN Yushu, KER M D, and JIANG H C. Transient Voltage Suppressor (TVS) on signal integrity of microelectronics system with CMOS ICs under system-level ESD test[C]. 2020 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 2020: 1–4. [23] SHEN Yushu and KER M D. The impact of holding voltage of Transient Voltage Suppressor (TVS) on signal integrity of microelectronics system with CMOS ICs under system-level ESD and EFT/burst tests[J]. IEEE Transactions on Electron Devices, 2021, 68(5): 2152–2159. doi: 10.1109/TED.2021.3063208 [24] MAGHLAKELIDZE G, MARATHE S, HUANG Wei, et al. Effect of RF signals on TVS diode trigger voltage for ESD protection[C]. 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI), Reno, USA, 2020: 194–199. [25] ZENG Xun, ZHOU Liang, and ZHANG Chengrui. Investigation of protection effects using transient voltage suppressor diodes-based circuits under high power microwave pulses[C]. 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, Raleigh, USA, 2021: 524–527. [26] 张杨. 基于ESD的TVS冲击电压特性机理研究[J]. 电子质量, 2022(6): 188–193. doi: 10.3969/j.issn.1003-0107.2022.06.046ZHANG Yang. Research on impulse voltage characteristic of TVS based on ESD[J]. Electronics Quality, 2022(6): 188–193. doi: 10.3969/j.issn.1003-0107.2022.06.046 [27] 陈强, 徐可, 陈真真, 等. 基于TLP建模的系统级静电放电效应仿真[J]. 强激光与粒子束, 2019, 31(10): 103208. doi: 10.11884/HPLPB201931.190113CHEN Qiang, XU Ke, CHEN Zhenzhen, et al. System-level electrostatic discharge simulation based on transmission line pulse modeling[J]. High Power Laser and Particle Beams, 2019, 31(10): 103208. doi: 10.11884/HPLPB201931.190113 [28] 李景钦. 二极管电磁兼容模型建立方法研究[D]. [硕士论文], 电子科技大学, 2021.LI Jingqin. Research on establishing method of diode electromagnetic compatibility model[D]. [Master dissertation], University of Electronic Science and Technology of China, 2021. -

下载:

下载:

下载:

下载: