Flexible Network Modal Packet Processing Pipeline Construction Mechanism for Cloud-Network Convergence Environment

-

摘要: 随着云网融合技术的发展,多样化的网络业务需求催生了对多模态网络报文柔性化处理的需求。该文提出一种基于多模态网元抽象模型与前-中-后端三段式编译架构的协议报文柔性化处理编译机制,通过中间表示切片算法将多种网络模态混合的处理逻辑拆解并映射至ASIC, FPGA和CPU等异构硬件资源上,构建支持自定义配置的柔性流水线以适应不同的网络业务传输要求。该文详细介绍该架构的设计理念、中间表示结构及中间表示切片算法,并验证所提出的柔性流水线在构造效果和功能满足方面的优越性。实验表明,该机制能构建从1段到5段等多种流水线样式,在原型系统上实现的多模态处理流水线平均延迟最低可达15.48 μs。因此,该机制能够有效提升网络服务的灵活性和效率,为超融合云网环境下的网络报文处理提供了新的思路。Abstract:

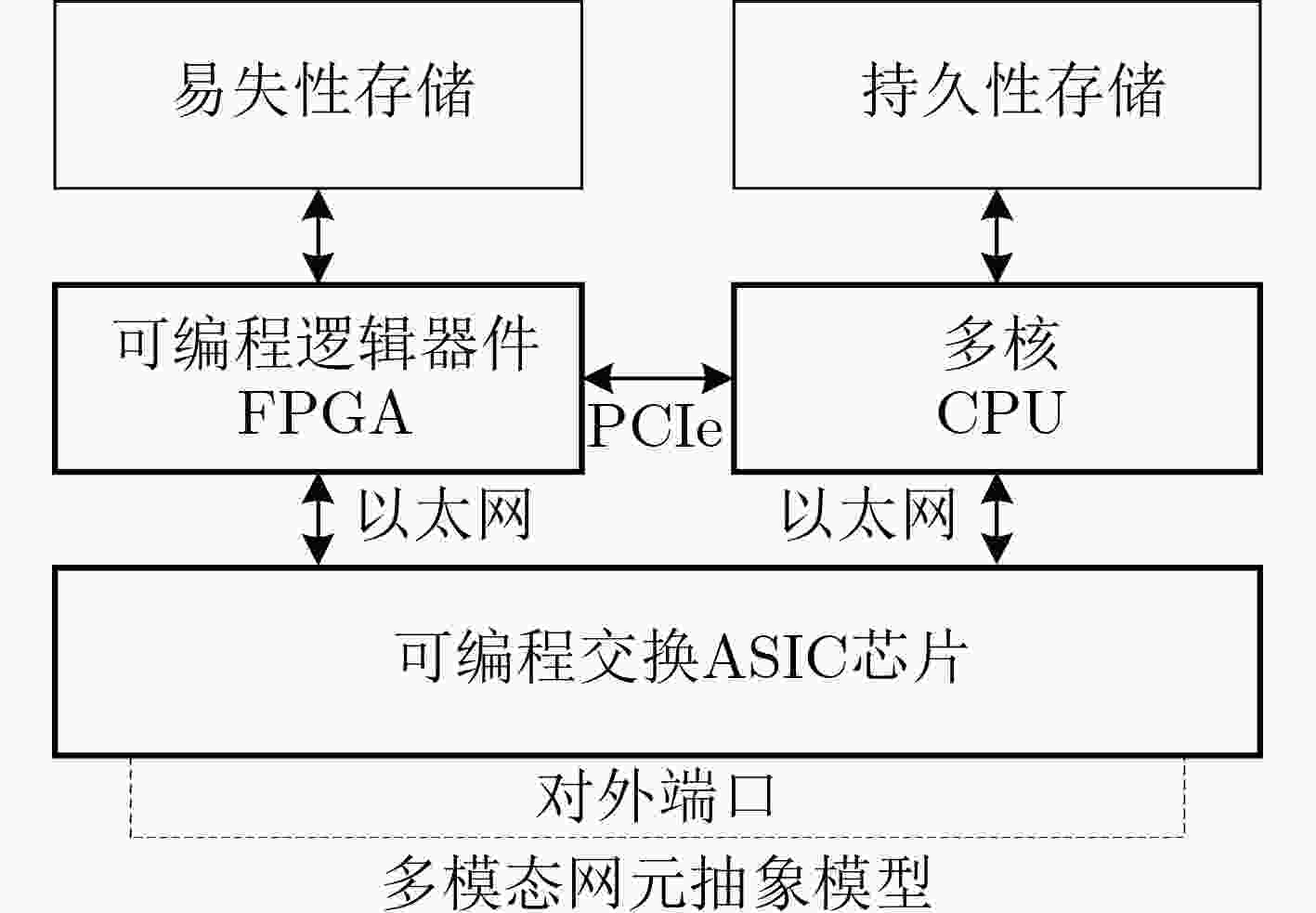

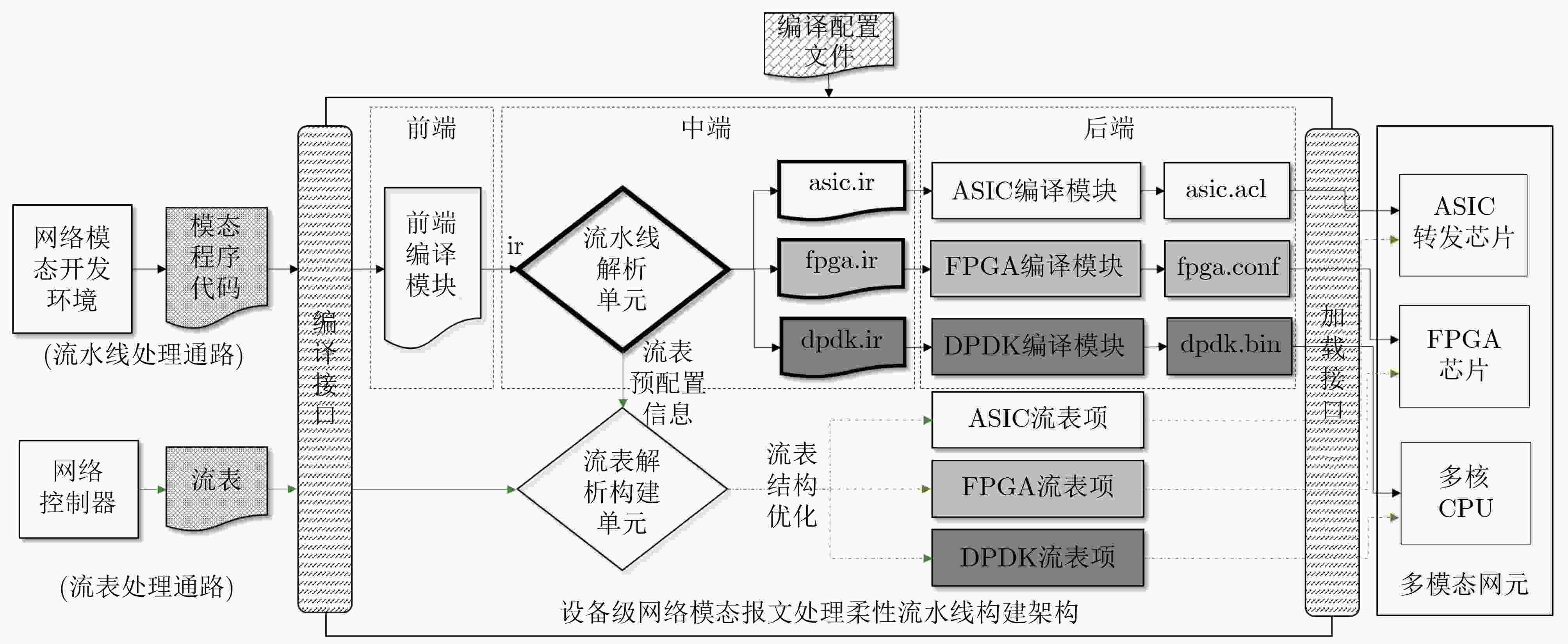

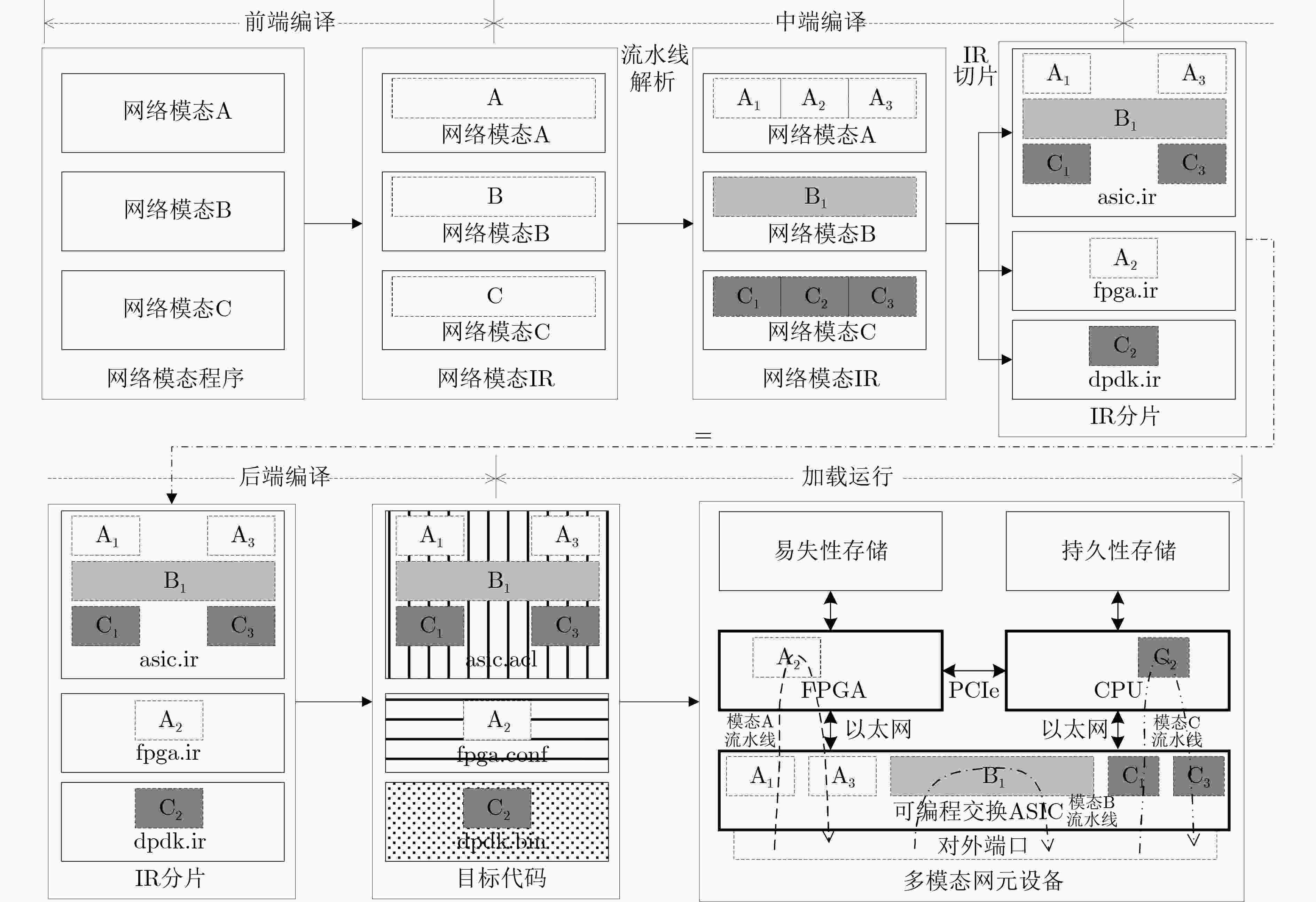

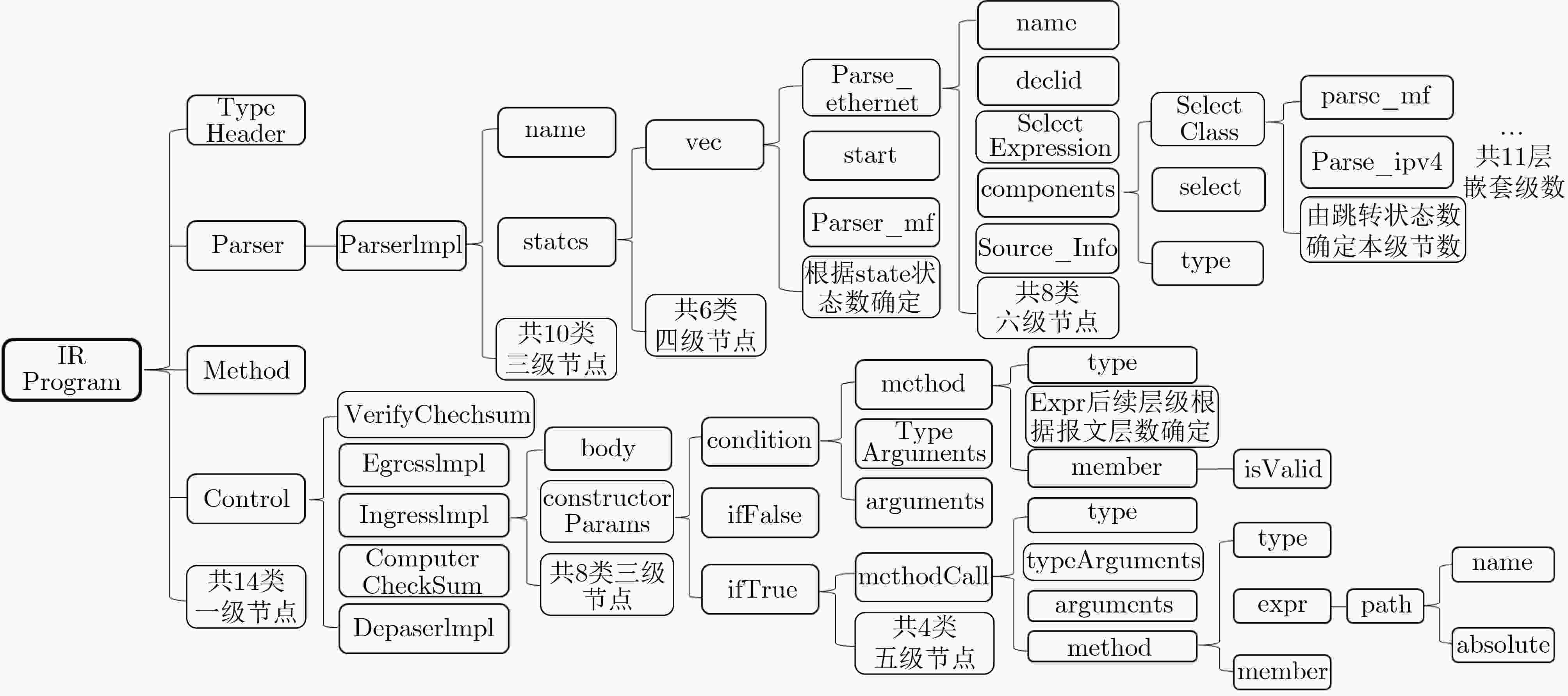

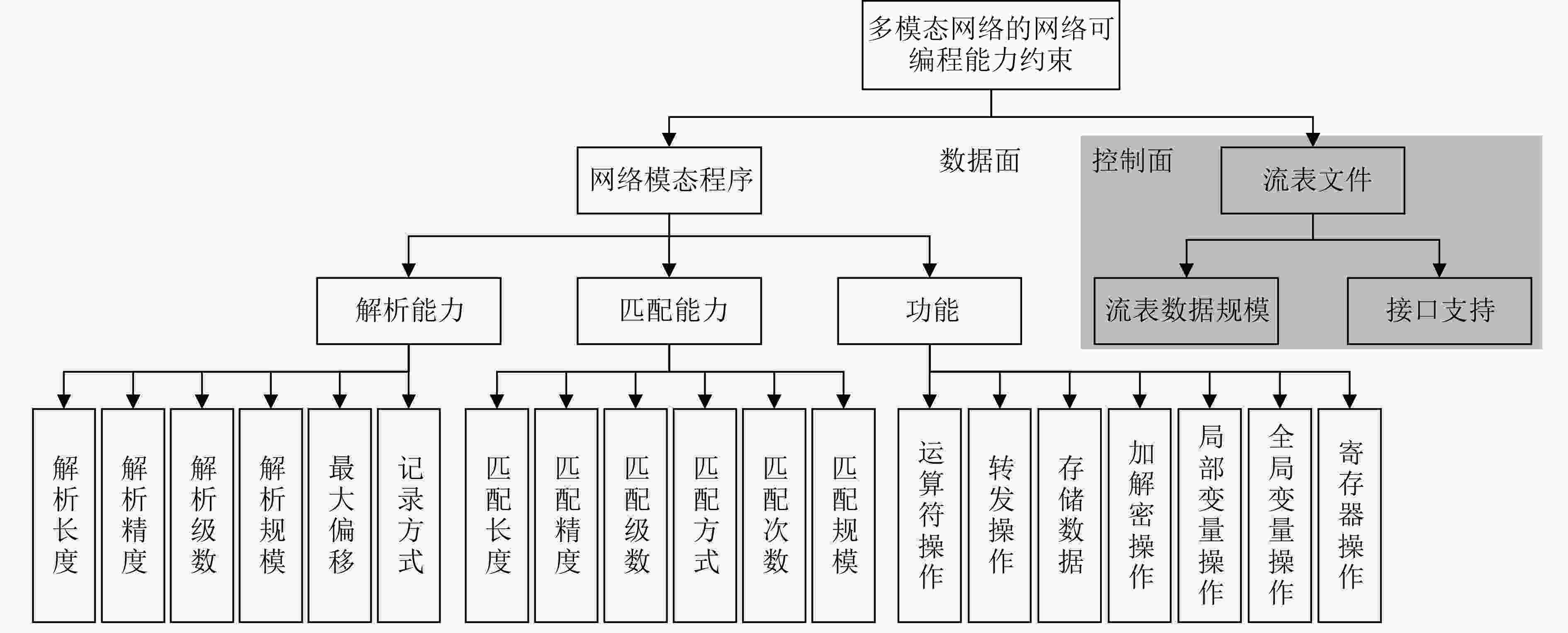

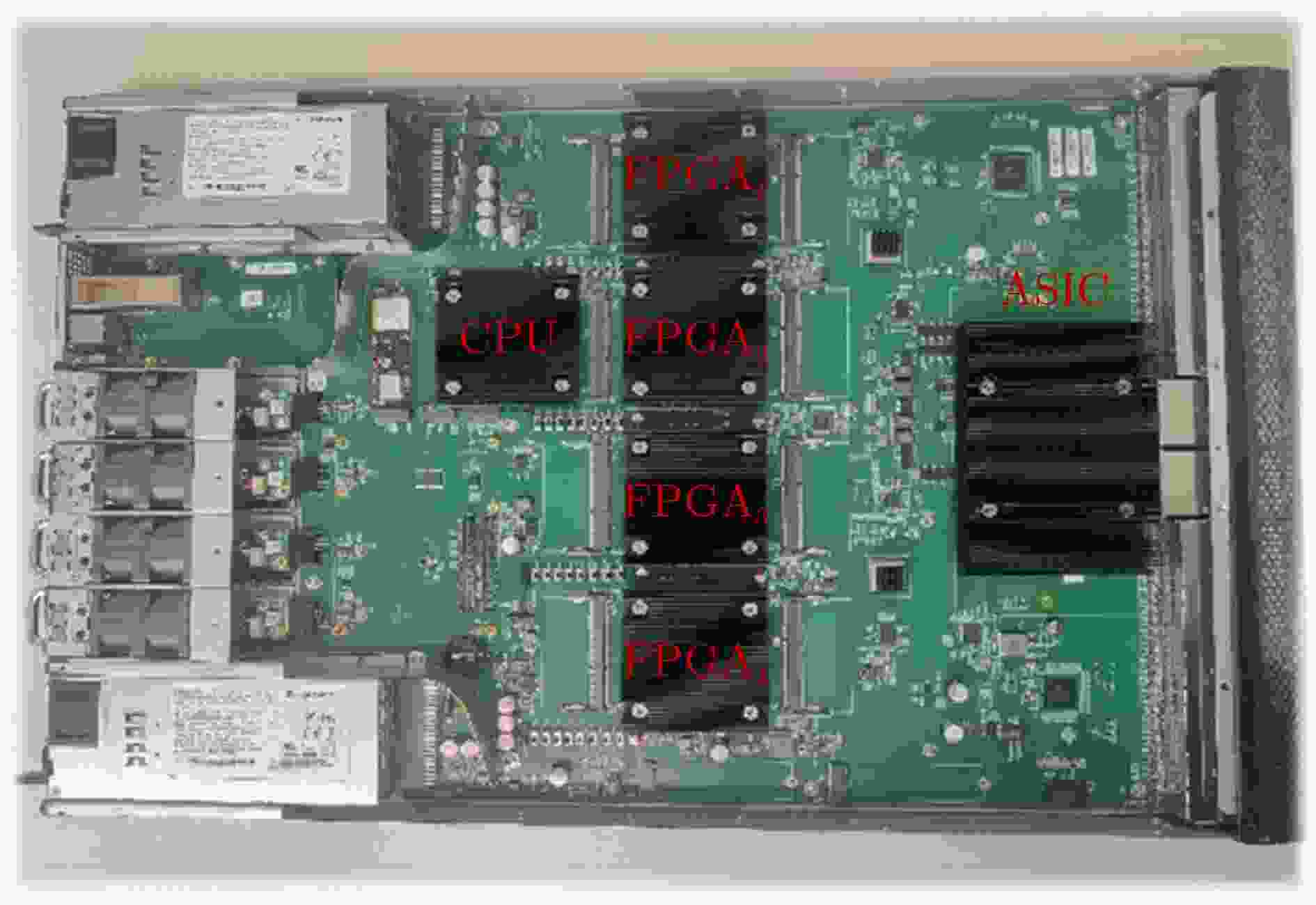

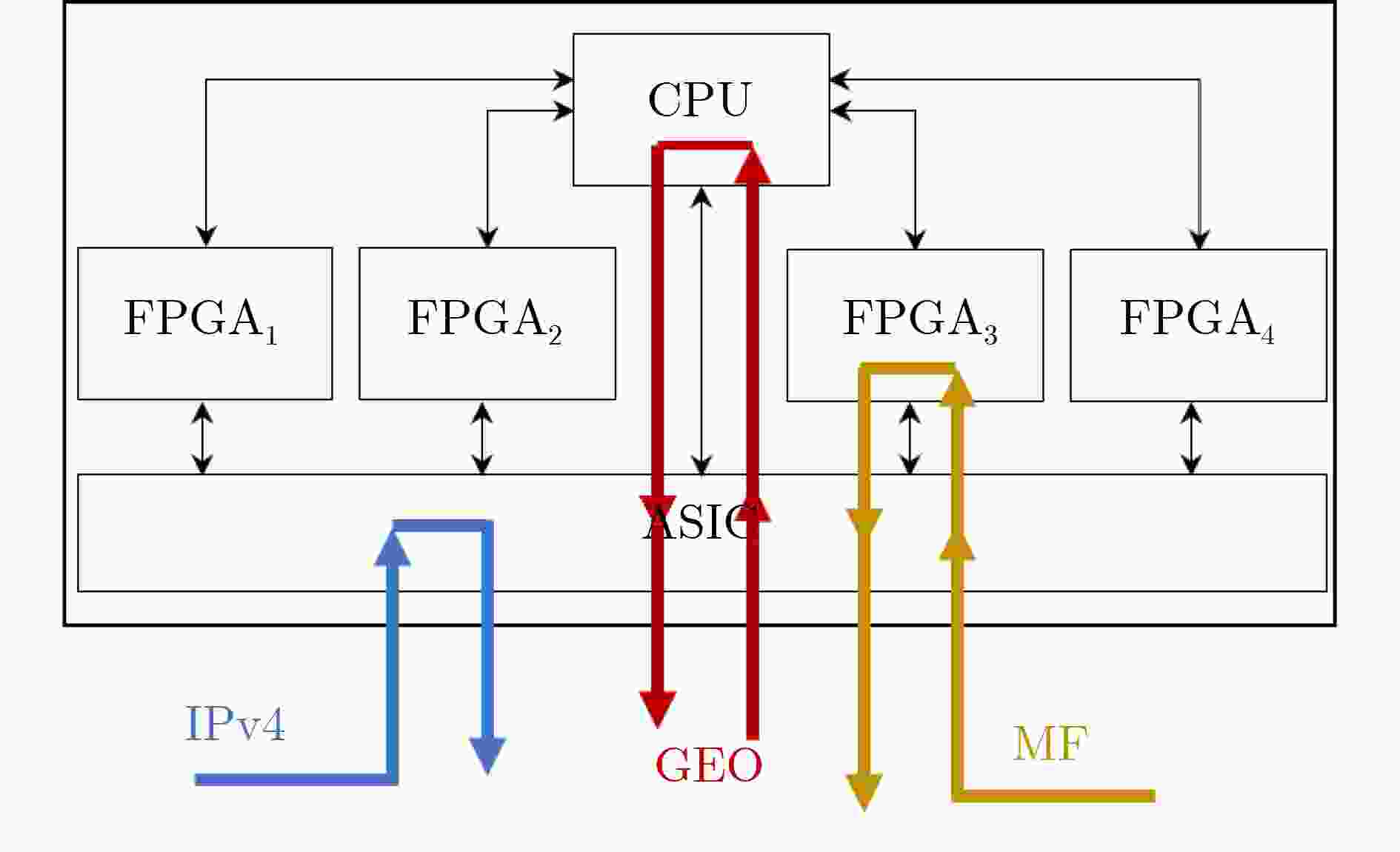

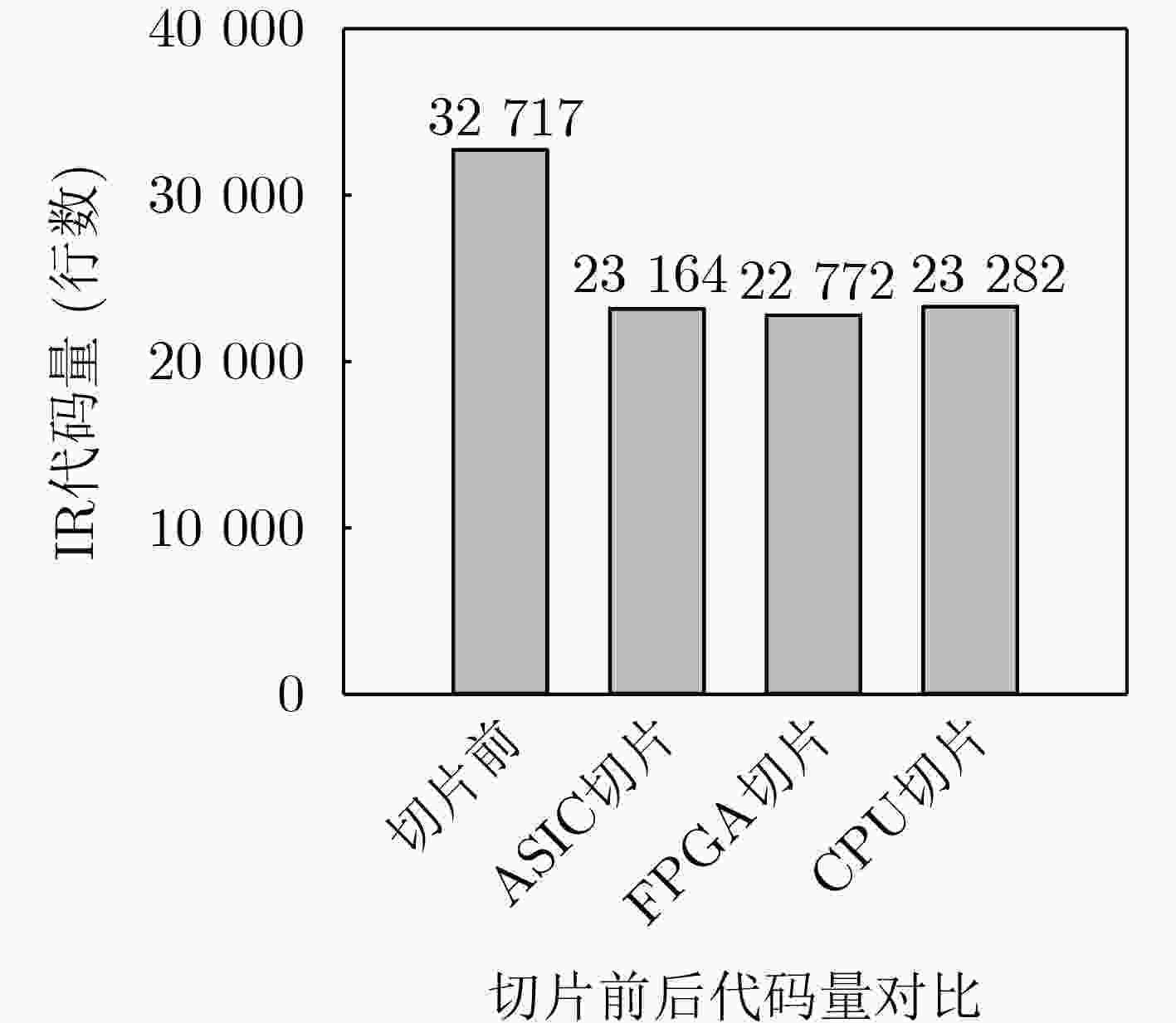

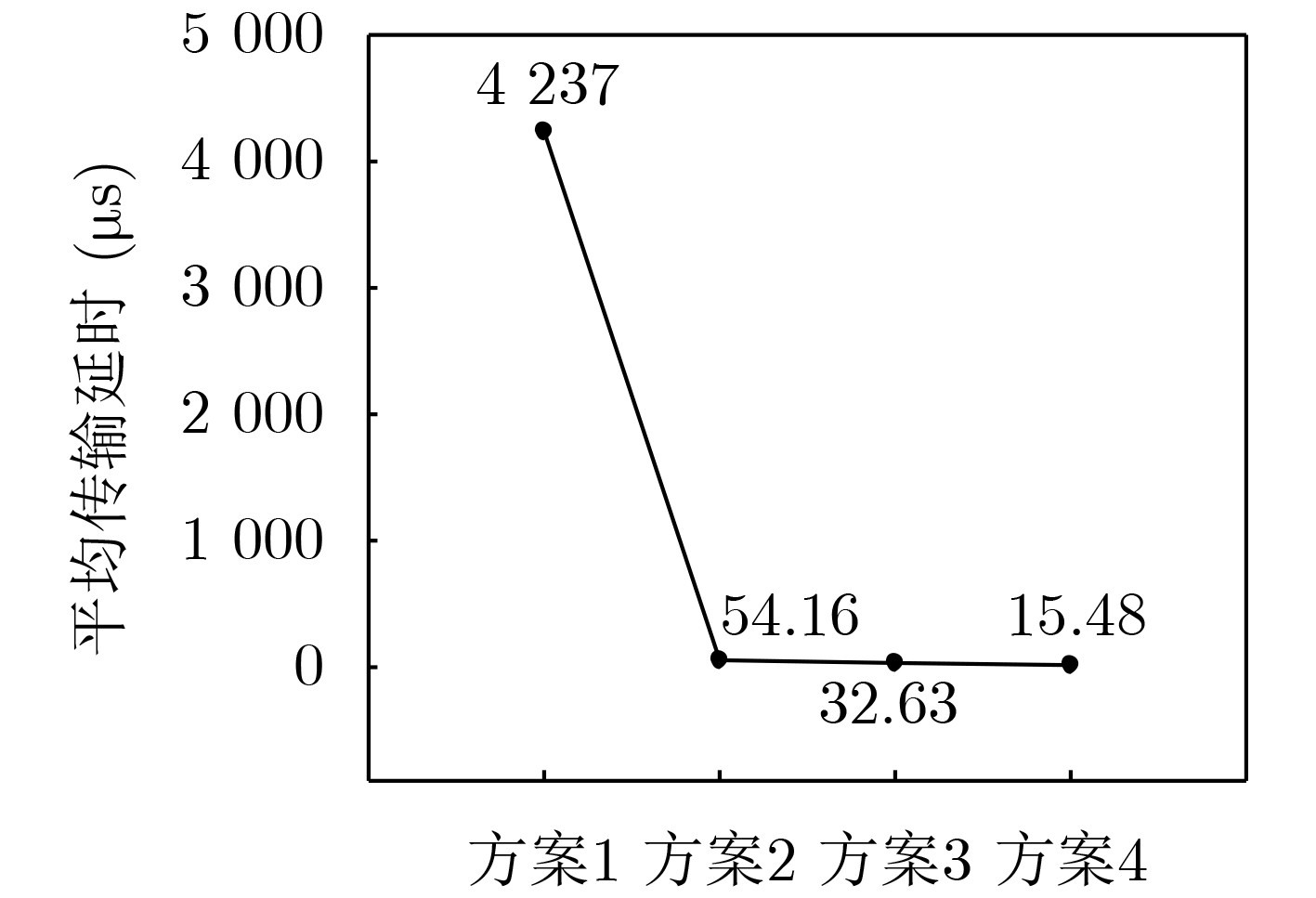

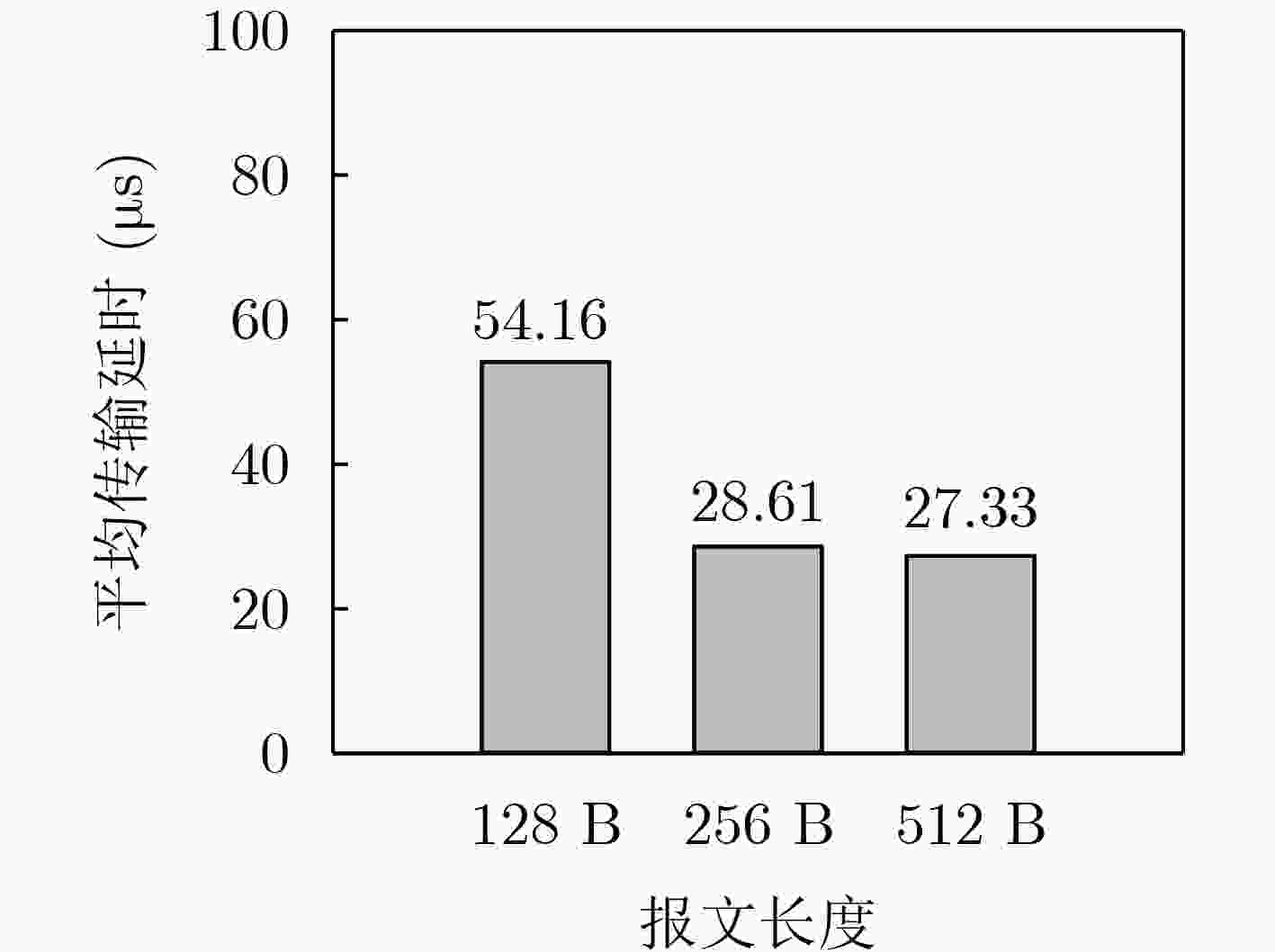

Objective With the deep integration of information network technologies and vertical application domains, the demand for cloud-network convergence infrastructure becomes increasingly significant, and the boundaries between cloud computing and network technologies are gradually fading. The advancement of cloud-network convergence technologies gives rise to diverse network service requirements, creating new challenges for the flexible processing of multimodal network packets. The device-level network modal packet processing flexible pipeline construction mechanism is essential for realizing an integrated environment that supports multiple network technologies. This mechanism establishes a flexible protocol packet processing pipeline architecture that customizes a sequence of operations such as packet parsing, packet editing, and packet forwarding according to different network modalities and service demands. By enabling dynamic configuration and adjustment of the processing flow, the proposed design enhances network adaptability and meets both functional and performance requirements across heterogeneous transmission scenarios. Methods Constructing a device-level flexible pipeline faces two primary challenges: (1) it must flexibly process diverse network modal packet protocols across polymorphic network element devices. This requires coordination of heterogeneous resources to enable rapid identification, accurate parsing, and correct handling of packets in various formats; (2) the pipeline construction must remain flexible, offering a mechanism to dynamically generate and configure pipeline structures that can adjust not only the number of stages but also the specific functions of each stage. To address these challenges, this study proposes a polymorphic network element abstraction model that integrates heterogeneous resources. The model adopts a hyper-converged hardware architecture that combines high-performance switching ASIC chips with more programmable but less computationally powerful FPGA and CPU devices. The coordinated operation of hardware and software ensures unified and flexible support for custom network protocols. Building upon the abstraction model, a protocol packet flexible processing compilation mechanism is designed to construct a configurable pipeline architecture that meets diverse network service transmission requirements. This mechanism adopts a three-stage compilation structure consisting of front-end, mid-end, and back-end processes. In response to adaptation issues between heterogeneous resources and differentiated network modal demands, a flexible pipeline technology based on Intermediate Representation (IR) slicing is further proposed. This technology decomposes and reconstructs the integrated IR of multiple network modalities into several IR subsets according to specific optimization methods, preserving original functionality and semantics. By applying the IR slicing algorithm, the mechanism decomposes and maps the hybrid processing logic of multimodal networks onto heterogeneous hardware resources, including ASICs, FPGAs, and CPUs. This process enables flexible customization of network modal processing pipelines and supports adaptive pipeline construction for different transmission scenarios. Results and Discussions To demonstrate the construction effectiveness of the proposed flexible pipeline, a prototype verification system for polymorphic network elements is developed. As shown in Fig. 6, the system is equipped with Centec CTC8180 switch chips, multiple domestic FPGA chips, and domestic multi-core CPU chips. On this polymorphic network element prototype platform, protocol processing pipelines for IPv4, GEO, and MF network modalities are constructed, compiled, and deployed. As illustrated in Fig. 7, packet capture tests verify that different network modalities operate through distinct packet processing pipelines. To further validate the core mechanism of network modal flexible pipeline construction, the IR code size before and after slicing is compared across the three network modalities and allocation strategies described in Section 6.2. The integrated P4 code for the three modalities, after front-end compilation, produces an unsliced intermediate code containing 32,717 lines. During middle-end compilation, slicing is performed according to the modal allocation scheme, generating IR subsets for ASIC, CPU, and FPGA with code sizes of 23,164, 23,282, and 22,772 lines, respectively. The performance of multimodal protocol packet processing is then assessed, focusing on the effects of different traffic allocation strategies on network protocol processing performance. As shown in Fig. 9, the average packet processing delay in Scheme 1 is significantly higher than in the other schemes, reaching 4.237 milliseconds. In contrast, the average forwarding delays in Schemes 2, 3, and 4 decrease to 54.16 microseconds, 32.63 microseconds, and 15.48 microseconds, respectively. These results demonstrate that adjusting the traffic allocation strategy, particularly the distribution of CPU resources for GEO and MF modalities, effectively mitigates processing bottlenecks and markedly improves the efficiency of multimodal network communication. Conclusions Experimental evaluations verify the superiority of the proposed flexible pipeline in construction effectiveness and functional capability. The results indicate that the method effectively addresses complex network environments and diverse service demands, demonstrating stable and high performance. Future work focuses on further optimizing the architecture and expanding its applicability to provide more robust and flexible technical support for protocol packet processing in hyper-converged cloud-network environments. -

表 1 多段式网络模态报文处理柔性流水线设计

序号 流水线段数 流水线通路 优缺点分析 1 1 ASIC 速度快,报文解析转发功能相对固定 2 3 ASIC→FPGAm→ASIC 速度较快,具备一定灵活性 3 3 ASIC→CPUn→ASIC 速度较慢,灵活性高 4 4 ASIC→FPGAm→CPUn→ASIC 速度较慢,灵活性高 5 4 ASIC→CPUn→FPGAm→ASIC 速度较慢,灵活性高 6 5 ASIC→FPGAm→CPUn→FPGAm→ASIC 速度慢,灵活性较高 7 5 ASIC→FPGAm→CPUn→FPGAm’→ASIC 速度慢,灵活性较高,可利用资源更多 8 5 ASIC→CPUn→FPGAm→CPUn→ASIC 速度慢,灵活性较高 9 5 ASIC→CPUn→FPGAm→CPUn’→ASIC 速度慢,灵活性较高,可利用资源更多 10 1+2i或1+3i(i≥1) ASIC→i·(CPUn|FPGAm|(CPUn→FPGAm)|(FPGAm→ CPUn) → ASIC →) 更一般化的流水线阶段表示 1 模态中间表示IR中的control单元切片处理模块算法

1 control单元切片处理模块() 2 { 3 for (auto i : 模态条件判断模块集合){ 4 ···. 5 auto cond = new

IR::IndexedVector<IR::StatOrDecl>;6 element = element_extract(); //模态条件判断模块,

模态标识要素提取7 if (true == check_element(element)) //模态标识要素

校验8 ans = element_match(element) //模态标识要素匹配 9 if (true == ans) 10 cond = push_back(i); //保留此模态条件判断模块 11 else 12 切片删除此模态条件判断模块 13 else 14 continue; //要素不合法,跳出循环 15 ···. 16 } 17 refresh_node(cond); //模态条件判断模块集更新 18 return; 19 } 表 2 IR切片测试和代码量情况

网络

模态模态

分配

策略切片前网络模态

IR代码量

(multimodal_mix.ir)切片后各个芯片IR

切片代码量ASIC

切片

(asic.ir)FPGA

切片

(fpga.ir)CPU

切片

(cpu.ir)IPv4 ASIC 32717 23164 22772 23282 GEO CPU MF FPGA 表 3 多模态协议报文处理性能评估(128B报文长度)

模态组合 切片策略 流量分配方案 方案1 方案2 方案3 方案4 IPv4 ASIC 100 Mbps 200 Mbps 300 Mbps 400 Mbps GEO CPU 200 Mbps 150 Mbps 100 Mbps 50 Mbps MF CPU 200 Mbps 150 Mbps 100 Mbps 50 Mbps 平均报文处理延迟时间(μs) 4 237 54.16 32.63 15.48 -

[1] WANG Guohui and NG T S E. The impact of virtualization on network performance of amazon EC2 data center[C]. 2010 Proceedings IEEE INFOCOM, San Diego, USA, 2010: 1–9. doi: 10.1109/INFCOM.2010.5461931. [2] DUAN Qiang, YAN Yuhong, and VASILAKOS A V. A survey on service-oriented network virtualization toward convergence of networking and cloud computing[J]. IEEE Transactions on Network and Service Management, 2012, 9(4): 373–392. doi: 10.1109/TNSM.2012.113012.120310. [3] 胡宇翔, 伊鹏, 孙鹏浩, 等. 全维可定义的多模态智慧网络体系研究[J]. 通信学报, 2019, 40(8): 1–12. doi: 10.11959/j.issn.1000-436x.2019192.HU Yuxiang, YI Peng, SUN Penghao, et al. Research on the full-dimensional defined polymorphic smart network[J]. Journal on Communications, 2019, 40(8): 1–12. doi: 10.11959/j.issn.1000-436x.2019192. [4] HU Yuxiang, LI Dan, SUN Penghao, et al. Polymorphic smart network: An open, flexible and universal architecture for future heterogeneous networks[J]. IEEE Transactions on Network Science and Engineering, 2020, 7(4): 2515–2525. doi: 10.1109/tnse.2020.3006249. [5] 支婷, 刘颖, 周华春, 等. 智慧标识网络服务机理研究进展及安全性分析[J]. 电子学报, 2021, 49(8): 1653–1664. doi: 10.12263/DZXB.20200416.ZHI Ting, LIU Ying, ZHOU Huachun, et al. Research progress and security analysis of the service mechanism in smart identifier network[J]. Acta Electronica Sinica, 2021, 49(8): 1653–1664. doi: 10.12263/DZXB.20200416. [6] WU Jiangxing. Thoughts on the development of novel network technology[J]. Science China Information Sciences, 2018, 61(10): 101301. doi: 10.1007/s11432-018-9456-x. [7] 邬江兴. 论网络技术体制发展范式的变革——网络之网络[J]. 电信科学, 2022, 38(6): 3–12. doi: 10.11959/j.issn.1000-0801.2022140.WU Jiangxing. Revolution of the development paradigm of network technology system—network of networks[J]. Telecommunications Science, 2022, 38(6): 3–12. doi: 10.11959/j.issn.1000-0801.2022140. [8] BRANDINO B and GRAMPÍN E. Network data plane programming languages: A survey[J]. Computers, 2024, 13(12): 314. doi: 10.3390/computers13120314. [9] 胡宇翔, 崔子熙, 田乐, 等. 面向垂直行业定制的多模态网络编程技术[J]. 信息通信技术, 2024, 18(4): 51–56. doi: 10.3969/j.issn.1674-1285.2024.04.008.HU Yuxiang, CUI Zixi, TIAN Le, et al. Polymorphic network programming technologies customized for vertical industries[J]. Information and Communications Technologies, 2024, 18(4): 51–56. doi: 10.3969/j.issn.1674-1285.2024.04.008. [10] 崔子熙, 田乐, 崔鹏帅, 等. 支持增量式编程的多模态网络环境[J]. 电子学报, 2024, 52(4): 1230–1238. doi: 10.12263/DZXB.20230852.CUI Zixi, TIAN Le, CUI Pengshuai, et al. Enabling incremental programming in PINet environment[J]. Acta Electronica Sinica, 2024, 52(4): 1230–1238. doi: 10.12263/DZXB.20230852. [11] 王劲林, 井丽南, 陈晓, 等. 面向多模态网络的可编程数据处理方法及系统设计[J]. 通信学报, 2022, 43(4): 14–25. doi: 10.11959/j.issn.1000−436x.2022070.WANG Jinlin, JING Linan, CHEN Xiao, et al. Programmable data processing method and system design for polymorphic network[J]. Journal on Communications, 2022, 43(4): 14–25. doi: 10.11959/j.issn.1000−436x.2022070. [12] SONI H, RIFAI M, KUMAR P, et al. Composing dataplane programs with μP4[C]. Proceedings of the Annual Conference of the ACM Special Interest Group on Data Communication on the Applications, Technologies, Architectures, and Protocols for Computer Communication, USA, 2020: 329–343. doi: 10.1145/3387514.3405872. [13] GAO Jiaqi, ZHAI Ennan, LIU H H, et al. Lyra: A cross-platform language and compiler for data plane programming on heterogeneous ASICs[C]. Proceedings of the Annual Conference of the ACM Special Interest Group on Data Communication on the Applications, Technologies, Architectures, and Protocols for Computer Communication, USA, 2020: 435–450. doi: 10.1145/3387514.3405879. [14] KUMAZOE K, KAWAHARA K, and TSURU M. Evaluation of essential functions for data-plane programming on P4 hardware switch[M]. BAROLLI L. Advances in Internet, Data and Web Technologies: Proceedings of the 13th International Conference on Emerging Internet, Data and Web Technologies (EIDWT 2025). Cham: Springer, 2025: 398–408. doi: 10.1007/978-3-031-86149-9_38. -

下载:

下载:

下载:

下载: