Bit-configurable Physical Unclonable Function Circuit Based on Self-detection and Repair Method

-

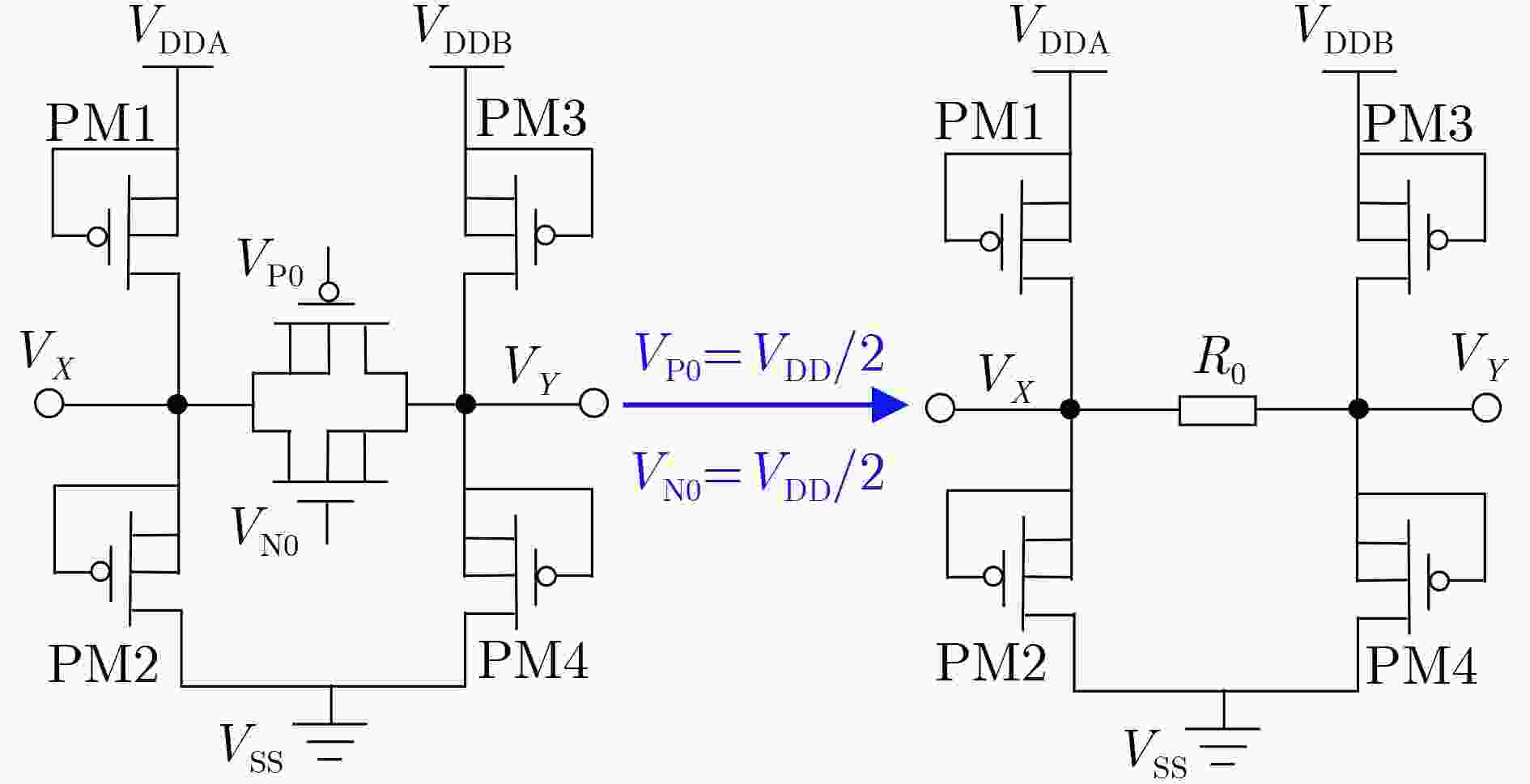

摘要: 物理不可克隆函数(PUF)作为硬件安全原语,为资源受限的物联网设备提供低成本的密钥生成与设备身份认证。然而,PUF电路的可靠性问题已经成为大规模部署的瓶颈。为此,该文提出一种基于自检测修复的比特配置高可靠PUF电路方案。该方案首先研究电桥失衡效应和亚阈值电流特性,利用亚阈值指数级电流特性放大随机工艺偏差,提升输出熵源随机性。其次,构建可配置位单元拓扑结构,结合比特配置策略,在不增加额外硬件开销的情况下,可灵活切换电桥PUF与分压PUF模式。最后,提出一种自检测与修复机制以提升PUF电路的可靠性,并结合掩蔽操作进一步降低误码率(BER)。在TSMC 28 nm工艺下实现64×64位PUF电路设计,全定制版图面积为

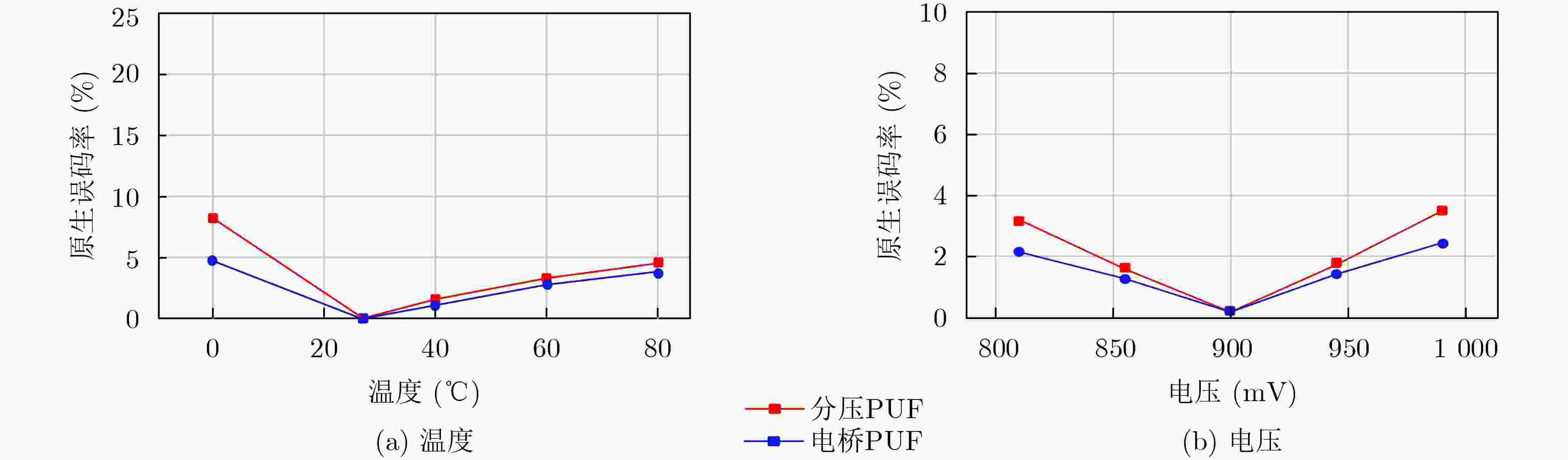

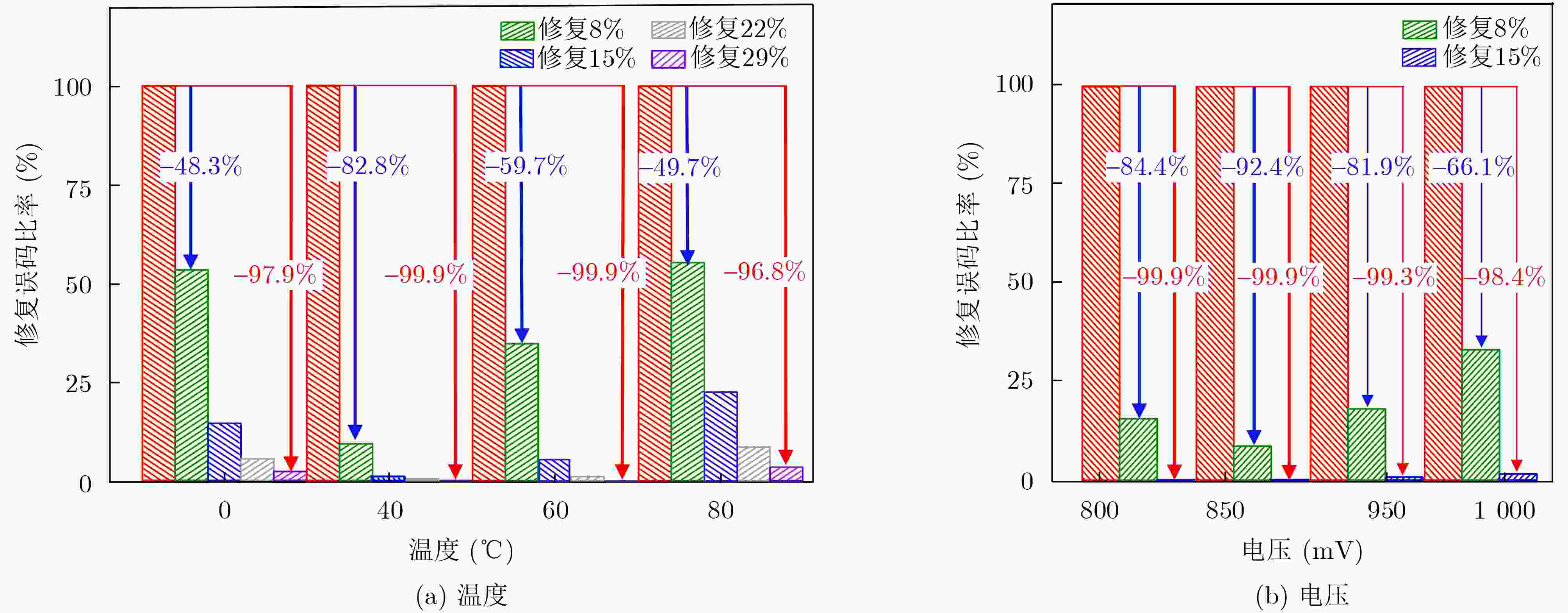

3283.3 μm2。实验结果表明,电桥PUF和分压PUF唯一性和自相关性分别为50.03%/50.08%和0.027 3/0.027 7,且通过NIST800-22随机性测试。此外,在0 °C~80 °C的温度范围和0.81~0.99 V的电压范围内,对29%的不稳定位进行修复或掩蔽处理,最终误码率为1.62E–9。Abstract:Objective The proliferation of Internet of Things (IoT) devices has intensified the need for robust, hardware-level security. Among hardware-based security primitives, Physical Unclonable Functions (PUFs) serve a critical role in lightweight authentication and dynamic key generation by leveraging inherent process variations to produce unique, unclonable responses. Achieving reliable PUF performance under environmental fluctuations—such as temperature and supply voltage variation, requires balancing sensitivity to process variations with environmental robustness. Conventional approaches, including circuit-level stabilization and architecture-level error correction, can improve reliability but often increase area, power, and test complexity. To overcome these drawbacks, recent work has explored voltage or bias perturbation for unstable response correction. However, entropy degradation during mode transitions in dual-mode PUFs remains a major concern, compromising both reliability and energy efficiency. This study proposes a bit-configurable bistable electric bridge-divider PUF that addresses these challenges by maintaining entropy independence between operational modes, reducing error correlation, and limiting repair and masking overhead. The proposed solution improves randomness, reliability, and energy efficiency, making it suitable for secure, cost-effective authentication in IoT edge devices operating under dynamic conditions. Methods Hardware overhead and testing complexity associated with conventional PUF stabilization techniques are reduced by introducing a bit-configurable bistable electric bridge-divider PUF architecture. Entropy generation is enhanced by amplifying process-induced variations through electric bridge imbalance and the exponential behavior of subthreshold current. A reconfigurable bit-cell is employed to enable seamless switching between electric bridge mode and voltage divider mode without additional layout cost; dual-mode operation is thus supported while preserving area efficiency. A voltage-skew-based self-detection and repair mechanism is integrated to dynamically identify and mitigate unstable responses, thereby improving reliability under varying environmental conditions. The PUF circuit is fully custom-designed and fabricated in the TSMC 28 nm CMOS process. Post-layout simulations confirm the robustness of the architecture, demonstrating effective self-repair capabilities and consistent performance under temperature and voltage fluctuations. Results and Discussions The proposed design is fabricated using the TSMC 28 nm CMOS process. The total layout area measures 3 283.3 μm2, and each PUF cell occupies 0.7888 μm2 (Fig. 11 ). Simulation waveforms of the self-detection, repair, and masking operations are presented in (Fig. 12 ). Inter-chip Hamming distance histograms and fitted curves for both electric bridge mode and voltage divider mode are shown in (Fig. 13a ,Fig. 14a ). Autocorrelation results of the 40,960-bit output are illustrated in (Fig. 13b ,Fig. 14b ). The randomness of the responses is evaluated using the NIST test suite provided by the U.S. National Institute of Standards and Technology, with the results summarized in (Table 1 ). The native Bit Error Rate (BER), measured before repair or masking, is analyzed under various temperature and supply voltage conditions (Fig. 15 ). By dynamically adjusting the voltage skew, precise control of the error correction rate is achieved, leading to a substantial reduction in BER across different environments (Fig. 16 ). A performance comparison with previously reported designs is provided in (Table 2 ). After applying the entropy source repair and masking mechanism, the BER converges to below 1.62 × 10–9, approaching the ideal “zero” BER.Conclusions A bit-configurable PUF architecture is proposed to address environmental variability and hardware constraints in IoT edge devices. A reconfigurable bit-cell is employed to support dynamic switching between electric bridge mode and voltage divider mode without incurring additional layout cost. Process-induced variations are amplified through bridge imbalance and the exponential behavior of subthreshold current, which enhances the randomness and uniqueness of the PUF responses. A voltage-skew-based self-detection and repair mechanism is integrated to identify and correct unstable responses, effectively reducing the BER under varying environmental conditions. The proposed design, fabricated using the TSMC 28 nm CMOS process, demonstrates high entropy, robustness, and low overhead in terms of area and power consumption. These characteristics make it suitable for secure and lightweight authentication and key generation in resource-constrained IoT systems. -

表 1 NIST随机性测试

测试项目 比特流长度 P-Value I P-Value II 通过/不通过 近似熵 1 024 0.999 83 0.795 61 通过 块内频率 1 024 0.877 29 0.839 12 通过 累加和 1 024 0.741 40 0.834 10 通过 离散傅里叶变换 1 024 0.327 66 0.427 92 通过 频率 1 024 0.592 16 0.521 88 通过 线性复杂度 1 024 0.561 34 0.638 17 通过 块内最长游程 1 024 0.775 82 0.793 70 通过 非重叠模块匹配 1 024 0.718 99 0.460 11 通过 2元矩阵秩 1 024 0.538 69 0.324 15 通过 序列 1 024 0.693 72 0.586 71 通过 游程 1 024 0.530 80 0.443 76 通过 表 2 与相关文献性能对比

INV PUF[15] SRAM PUF[17] NOR PUF[19] NAND PUF[20] 本文 工艺尺寸(nm) 65 65 65 14 28 单位面积(F2/bit) 594 3 001 266 1 065 1 006 温度范围(°C) –40~125 –10~85 –20~125 25~110 0~80 电压范围(V) 0.7~1.4 0.8~1.2 0.8~1.2 0.55~75 0.8~1 原生不稳定位(%) 4.2 19.6 2.74 2.55 5.4/8.2 稳定前误码率(%) 4.2 2.24 4.64 1.46 - 稳定后误码率(%e) <5.99E–7 <1.4E–9 <4.88E–8 - <1.62E–9 掩蔽率(%) 31/35 59 - 20 29 唯一性(%) 0.499 5 - 0.499/0.5 0.497 8 50.3%/50.8% 芯片能耗(fJ/bit) 0.057 15.39 0.063 4 0.104 -

[1] AL-MEER A and AL-KUWARI S. Physical Unclonable Functions (PUF) for IoT devices[J]. ACM Computing Surveys, 2023, 55(14s): 314. doi: 10.1145/3591464. [2] XU Chongyao, ZHANG Litao, MAK P I, et al. Fully symmetrical obfuscated interconnection and weak-PUF-assisted challenge obfuscation strong PUFs against machine-learning modeling attacks[J]. IEEE Transactions on Information Forensics and Security, 2024, 19: 3927–3942. doi: 10.1109/tifs.2024.3372801. [3] 夏卓群, 苏潮, 徐梓桑, 等. 基于物理不可克隆函数的轻量级可证明安全车联网认证协议[J]. 电子与信息学报, 2024, 46(9): 3788–3796. doi: 10.11999/jeit240141.XIA Zhuoqun, SU Chao, XU Zisang, et al. A lightweight and provably secure authentication protocol for internet of vehicles using physical unclonable function[J]. Journal of Electronics & Information Technology, 2024, 46(9): 3788–3796. doi: 10.11999/jeit240141. [4] ZHOU Ziyu, LI Gang, ZHANG Yuejun, et al. A strong PUF-based security protocol to protect AI model parameters against privacy information leakage[J]. IEEE Internet of Things Journal, 2025, 12(12): 20815–20827. doi: 10.1109/jiot.2025.3544555. [5] CHIU Y C, KHWA W S, YANG C S, et al. A CMOS-integrated spintronic compute-in-memory macro for secure AI edge devices[J]. Nature Electronics, 2023, 6(7): 534–543. doi: 10.1038/s41928-023-00994-0. [6] WANG Ziyu, WU Yuting, PARK Y, et al. Safe, secure and trustworthy compute-in-memory accelerators[J]. Nature Electronics, 2024, 7(12): 1086–1097. doi: 10.1038/s41928-024-01312-y. [7] SHAO Hanyong, FU Boyi, YANG Jinghao, et al. IMCE: An in-memory computing and encrypting hardware architecture for robust edge security[C]. 2024 Design, Automation & Test in Europe Conference & Exhibition (DATE), Valencia, Spain, 2024: 1–6. doi: 10.23919/DATE58400.2024.10546703. [8] HUANG Shanshi, JIANG Hongwu, PENG Xiaochen, et al. Secure XOR-CIM engine: Compute-in-memory SRAM architecture with embedded XOR encryption[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2021, 29(12): 2027–2039. doi: 10.1109/tvlsi.2021.3120296. [9] LEE J, KIM M, JEONG M, et al. A 20F2/bit current-integration-based differential nand-structured PUF for stable and V/T variation-tolerant low-cost IoT security[J]. IEEE Journal of Solid-State Circuits, 2022, 57(10): 2957–2968. doi: 10.1109/jssc.2022.3192903. [10] LIU Kunyang, CHEN Xinpeng, PU Hongliang, et al. A 0.5-V hybrid SRAM physically unclonable function using hot carrier injection burn-in for stability reinforcement[J]. IEEE Journal of Solid-State Circuits, 2021, 56(7): 2193–2204. doi: 10.1109/jssc.2020.3035207. [11] KARPINSKYY B, LEE Y, CHOI Y, et al. 8.7 physically unclonable function for secure key generation with a key error rate of 2E-38 in 45nm smart-card chips[C]. 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA, 2016: 158–160. doi: 10.1109/isscc.2016.7417955. [12] TANEJA S and ALIOTO M. PUF architecture with run-time adaptation for resilient and energy-efficient key generation via sensor fusion[J]. IEEE Journal of Solid-State Circuits, 2021, 56(7): 2182–2192. doi: 10.1109/jssc.2021.3050959. [13] CHUANG K H, BURY E, DEGRAEVE R, et al. A physically unclonable function using soft oxide breakdown featuring 0% native BER and 51.8 fJ/bit in 40-nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2019, 54(10): 2765–2776. doi: 10.1109/jssc.2019.2920714. [14] SARAZA-CANFLANCA P, FODOR F, DIAZ-FORTUNY J, et al. Unveiling the vulnerability of oxide-breakdown-based PUF[J]. IEEE Electron Device Letters, 2024, 45(5): 750–753. doi: 10.1109/led.2024.3369860. [15] HE Yan, LI Dai, YU Zhanghao, et al. ASCH-PUF: A “Zero” bit error rate CMOS physically unclonable function with dual-mode low-cost stabilization[J]. IEEE Journal of Solid-State Circuits, 2023, 58(7): 2087–2097. doi: 10.1109/jssc.2022.3233373. [16] LIU Kunyang, MIN Yue, YANG Xuan, et al. A 373-F2 0.21%-native-BER EE SRAM physically unclonable function with 2-D power-gated bit cells and VSS bias-based dark-bit detection[J]. IEEE Journal of Solid-State Circuits, 2020, 55(6): 1719–1732. doi: 10.1109/jssc.2019.2963002. [17] SHIFMAN Y, MILLER A, KEREN O, et al. An SRAM-based PUF with a capacitive digital preselection for a 1E-9 key error probability[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2020, 67(12): 4855–4868. doi: 10.1109/tcsi.2020.2996772. [18] VATALARO M, DE ROSE R, LANUZZA M, et al. Static CMOS physically unclonable function based on 4T voltage divider with 0.6%–1.5% bit instability at 0.4–1.8 V operation in 180 nm[J]. IEEE Journal of Solid-State Circuits, 2022, 57(8): 2509–2520. doi: 10.1109/jssc.2022.3151229. [19] ZHANG Haoyi, SONG Jiahao, LUO Haoyang, et al. A 266F2 ultra stable differential NOR-structured physically unclonable function with <6×10–9 bit error rate through efficient redundancy strategy[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2024, 71(12): 4979–4983. doi: 10.1109/tcsii.2024.3433543. [20] SATPATHY S, MATHEW S K, SURESH V, et al. A 4-fJ/b delay-hardened physically unclonable function circuit with selective bit destabilization in 14-nm trigate CMOS[J]. IEEE Journal of Solid-State Circuits, 2017, 52(4): 940–949. doi: 10.1109/jssc.2016.2636859. -

下载:

下载:

下载:

下载: