Integrated Design Techniques of Physical Unclonable Function and Multi-bit Parallel Exclusive OR Operations

-

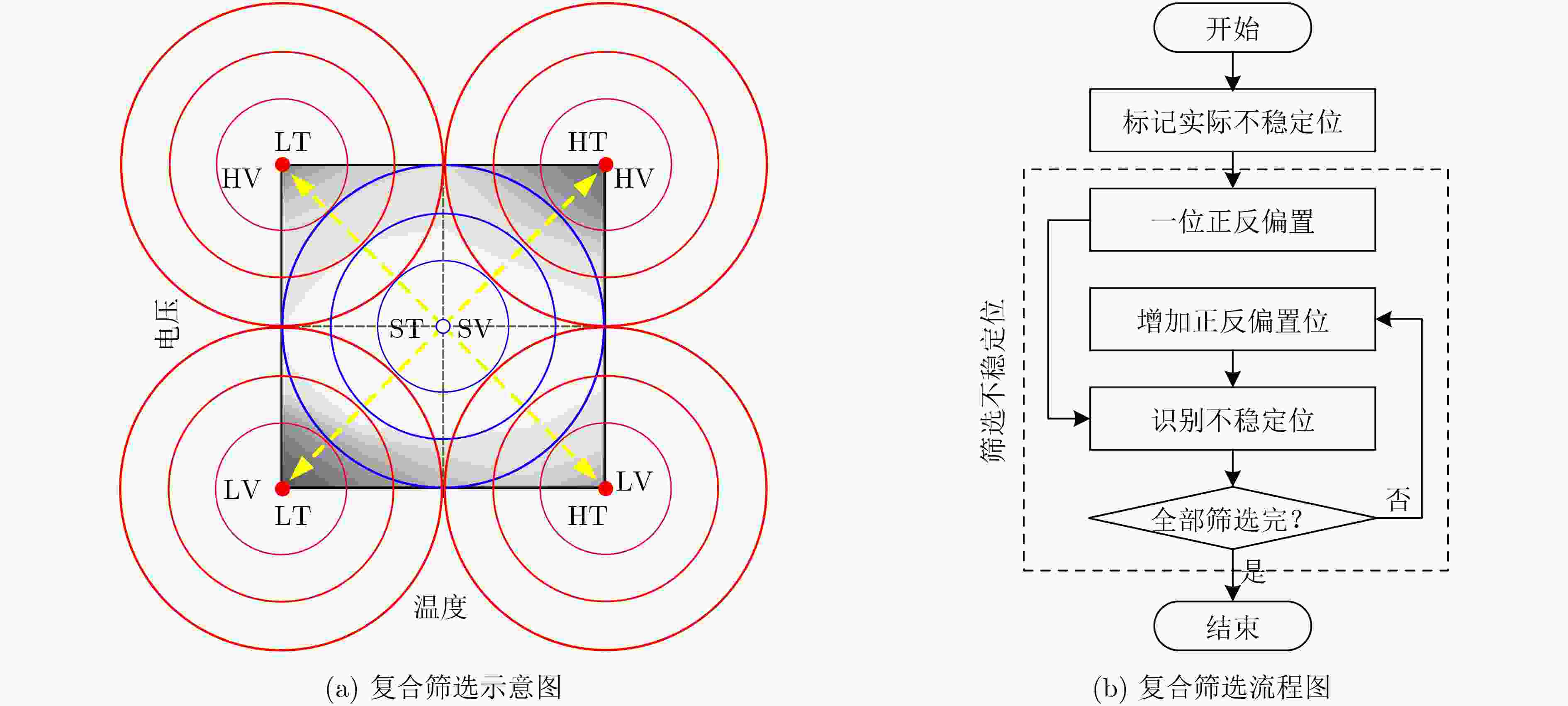

摘要: 物理不可克隆函数(PUF)和异或(XOR)运算在信息安全领域均发挥着重要作用。为突破PUF与逻辑运算之间的功能壁垒,通过对PUF工作机理和差分串联电压开关逻辑(DCVSL)的研究,该文提出一种基于DCVSL异或门级联单元随机工艺偏差的PUF和多位并行异或运算电路一体化设计方案。通过在DCVSL异或门差分输出端增加预充电管并在对地端设置管控门,可实现PUF特征信息提取、异或/同或(XOR/XNOR)运算和功率控制3种工作模式自由切换。此外,针对PUF响应稳定性问题,提出极端工作点和黄金工作点共同参与标记的不稳定位混合筛选技术。基于TSMC 65 nm工艺,对输入位宽为10位的电路进行全定制版图设计,面积为38.76 μm2。实验结果表明,PUF模式下,可产生1 024位输出响应,混合筛选后可获得超过512位稳定的密钥,且具有良好的随机性和唯一性;运算模式下,可同时实现10位并行异或和同或运算,功耗和延时分别为2.67 μW和593.52 ps。功控模式下,待机功耗仅70.5 nW。所提方法为突破PUF“功能墙”提供了一种新的设计思路。Abstract: Physical Unclonable Functions (PUFs), as well as Exclusive OR (XOR) operations, play an important role in the field of information security. In order to break through the functional barrier between PUF and logic operation, an integrated design scheme of PUF and multi-bit parallel XOR operation circuit based on the random process deviation of Differential Cascode Voltage Switch Logic (DCVSL) XOR gate cascade unit is proposed by studying the working mechanism of PUF and DCVSL. By adding a pre-charge tube at the differential output of the DCVSL XOR gate and setting a control gate at the ground end, three operating modes of the PUF feature information extraction, XOR/ Negated Exclusive OR (XNOR) operation and power control can be switched freely. Meanwhile, for the PUF response stability problem, the unstable bit hybrid screening technique with extreme and golden operating point participation labeling was proposed. Based on TSMC process of 65 nm, a fully customized layout design for a 10-bit input bit-wide circuit with an area of 38.76 μm2 was carried out. The experimental results show that the

1024 -bit output response can be generated in PUF mode, and a stable key of more than 512 bit can be obtained after hybrid screening, which has good randomness and uniqueness; In the operation mode, 10-bit parallel XOR and XNOR operations can be achieved simultaneously, with power consumption and delay of 2.67 μW and 593.52 ps, respectively. In power control mode, the standby power consumption is only 70.5 nW. The proposed method provides a novel way to break the function-wall of PUF. -

1 标记实际不稳定位

standard_response = PUF_at (SV, ST), unstable_bits = 0 for each voltage∈ [LV, ···, SV, ···, HV] do for each temperature ∈ [LT, ···, ST, ···, HT] do if measured_response[i] != standard_response[i] unstable_bits[i] = 1 end if end for end for 2 筛选不稳定位

Filter_bits=1; for each (voltage, temperature)∈ [(SV,ST), (LV,LT),

(LV,HT), (HV,LT), (HV,HT)] dofor i from 1 to 2n do if left_response[i] != right_response [i] filter[i] = 1; end if end for end for for i from 1 to 2n do if filter[i] ==0 and unstable_bits==1 Filter_bits++ break end if end for 表 1 与相关文献性能对比

VLSI’20[16] TCASI’22[17] JSSC’22[13] ISCAS’23[18] 本文 工艺尺寸(nm) 65 65 28 65 65 比特特征尺寸(F2) 215 – 1125 – 8.95 电压范围(V) 1.0~1.4 0.5~1.0 0.75~1.05 0.7~1.5 1.0~1.4 温度范围(°C) –40~125 –10~80 –25~100 0~120 –40~85 原始误码率(%) 2.12* 3.00 3.78 5.025* 3.82 随机性(%) 49.30 50.11 – 50.59 49.87 唯一性 0.500 0 0.494 7 0.5030 0.499 8 0.502 8 逻辑运算 无 无 无 无 有 功率控制 无 无 无 无 有 不稳定位筛选 无 无 无 无 有 *最大误码率 -

[1] GAO Yansong, AL-SARAWI S F, and ABBOTT D. Physical unclonable functions[J]. Nature Electronics, 2020, 3(2): 81–91. doi: 10.1038/s41928-020-0372-5. [2] ZHANG Jiliang, SHEN Chaoqun, GUO Zhiyang, et al. CT PUF: Configurable Tristate PUF against machine learning attacks for IoT security[J]. IEEE Internet of Things Journal, 2022, 9(16): 14452–14462. doi: 10.1109/JIOT.2021.3090475. [3] ZHOU Ziyu, WANG Pengjun, and LI Gang. Bagua protocol: A whole-process configurable protocol for IoT sensing devices security based on strong PUF[J]. IEEE Internet of Things Journal, 2024, 11(1): 805–819. doi: 10.1109/JIOT.2023.3285930. [4] 郭昕婕, 王光燿, 王绍迪. 存内计算芯片研究进展及应用[J]. 电子与信息学报, 2023, 45(5): 1888–1898. doi: 10.11999/JEIT220420.GUO Xinjie, WANG Guangyao, and WANG Shaodi. Technology developments and applications of in-memory computing processors[J]. Journal of Electronics & Information Technology, 2023, 45(5): 1888–1898. doi: 10.11999/JEIT220420. [5] HONG Qinghui, MAN Shen, SUN Jingru, et al. Programmable in-memory computing circuit for solving combinatorial matrix operation in one step[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2023, 70(7): 2916–2928. doi: 10.1109/TCSI.2023.3263217. [6] GUAJARDO J, KUMAR S S, SCHRIJEN G J, et al. FPGA Intrinsic PUFs and their use for IP protection[C]. 9th International Workshop on Cryptographic Hardware and Embedded Systems - CHES 2007, Vienna, Austria, 2007: 63–80. doi: 10.1007/978-3-540-74735-2_5. [7] KASSEM M, MANSOUR M, CHEHAB A, et al. A sub-threshold SRAM based PUF[C]. 2010 International Conference on Energy Aware Computing, Cairo, Egypt, 2010: 1–4. doi: 10.1109/ICEAC.2010.5702285. [8] ZHENG Yu, HASHEMIAN M S, and BHUNIA S. RESP: A robust physical unclonable function retrofitted into embedded SRAM array[C]. 2013 50th ACM/EDAC/IEEE Design Automation Conference (DAC), Austin, USA, 2013: 1–9. doi: 10.1145/2463209.2488807. [9] SUTAR S, RAHA A, and RAGHUNATHAN V. D-PUF: An intrinsically reconfigurable DRAM PUF for device authentication in embedded systems[C]. 2016 International Conference on Compliers, Architectures, and Sythesis of Embedded Systems (CASES), Pittsburgh, USA, 2016: 1–10. doi: 10.1145/2968455.2968519. [10] ZHAO Xiaojin, ZHAO Qiang, LIU Yongpan, et al. An ultracompact switching-voltage-based fully reconfigurable RRAM PUF with low native instability[J]. IEEE Transactions on Electron Devices, 2020, 67(7): 3010–3013. doi: 10.1109/TED.2020.2996181. [11] VATAJELU E I, DI NATALE G, and PRINETTO P. Security primitives (PUF and TRNG) with STT-MRAM[C]. 2016 IEEE 34th VLSI Test Symposium (VTS), Las Vegas, USA, 2016: 1–4. doi: 10.1109/VTS.2016.7477292. [12] SATPATHY S K, MATHEW S K, KUMAR R, et al. An all-digital unified physically unclonable function and true random number generator featuring self-calibrating hierarchical von Neumann extraction in 14-nm tri-gate CMOS[J]. IEEE Journal of Solid-State Circuits, 2019, 54(4): 1074–1085. doi: 10.1109/JSSC.2018.2886350. [13] TANEJA S, RAJANNA V K, and ALIOTO M. In-memory unified TRNG and multi-bit PUF for ubiquitous hardware security[J]. IEEE Journal of Solid-State Circuits, 2022, 57(1): 153–166. doi: 10.1109/JSSC.2021.3125255. [14] BATURONE I, ROMÁN R, and CORBACHO Á. A unified multibit PUF and TRNG based on ring oscillators for secure IoT devices[J]. IEEE Internet of Things Journal, 2023, 10(7): 6182–6192. doi: 10.1109/JIOT.2022.3224298. [15] PRATIHAR K, CHATTERJEE U, ALAM M, et al. Birds of the same feather flock together: A dual-mode circuit candidate for strong PUF-TRNG functionalities[J]. IEEE Transactions on Computers, 2023, 72(6): 1636–1651. doi: 10.1109/TC.2022.3218986. [16] LI Gang, WANG Pengjun, MA Xuejiao, et al. A 215-F² bistable physically unclonable function with an ACF of <0.005 and a native bit instability of 2.05% in 65-nm CMOS process[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2020, 28(11): 2290–2299. doi: 10.1109/TVLSI.2020.3014892. [17] LU Lu, YOO T, and KIM T T H. A 6T SRAM based two-dimensional configurable challenge-response PUF for portable devices[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2022, 69(6): 2542–2552. doi: 10.1109/TCSI.2022.3156983. [18] PENG Qiaozhou, ZUO Haibiao, HAO Jiacheng, et al. A subthreshold-inverter-based strong PUF with high reliability and energy efficiency[C]. 2023 IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, USA, 2023: 1–5. doi: 10.1109/ISCAS46773.2023.10181580. -

下载:

下载:

下载:

下载: