Review of the Application and Funding Statistics of the NationalNatural Science Foundation of China in the Electronics and Technology Area for 2023

-

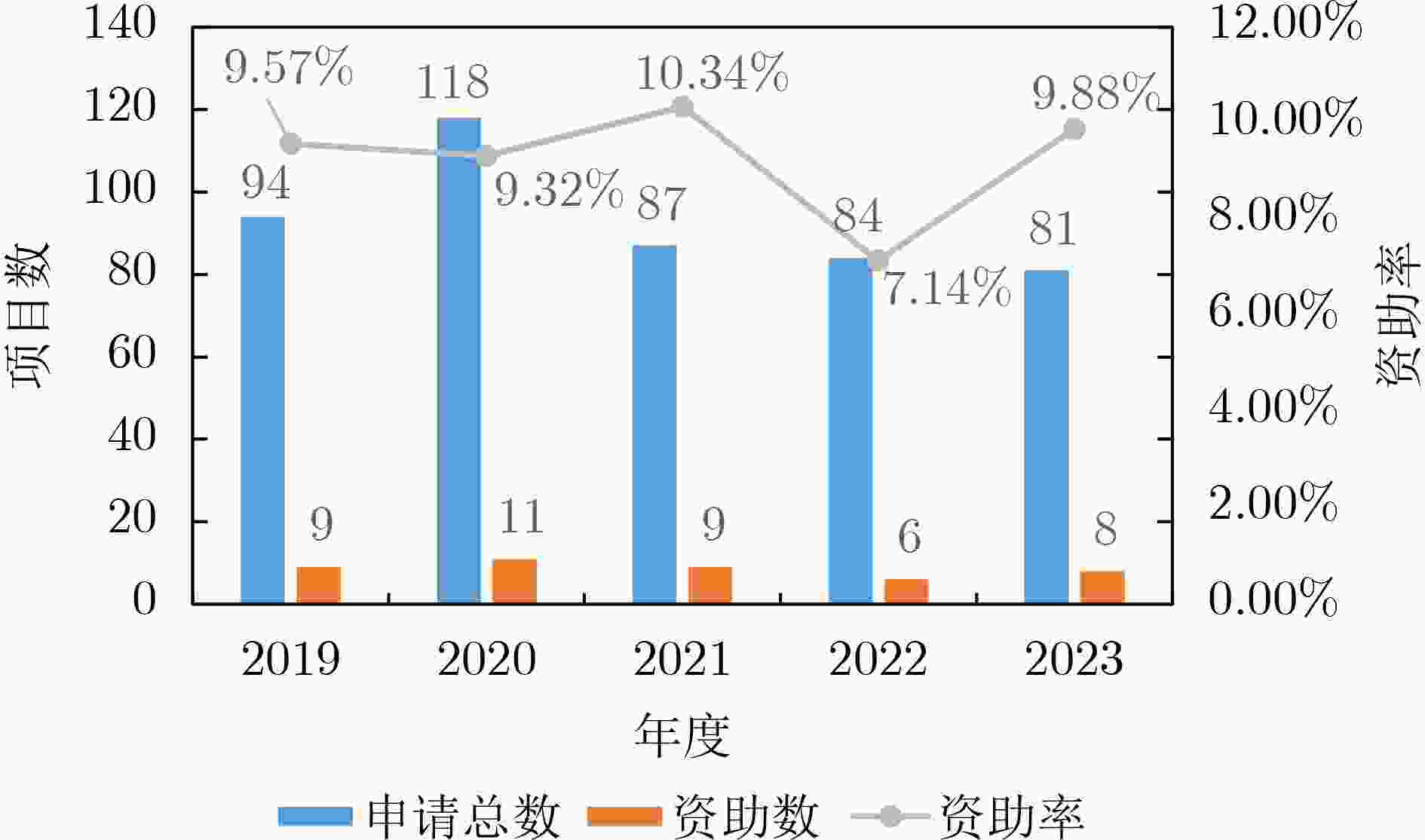

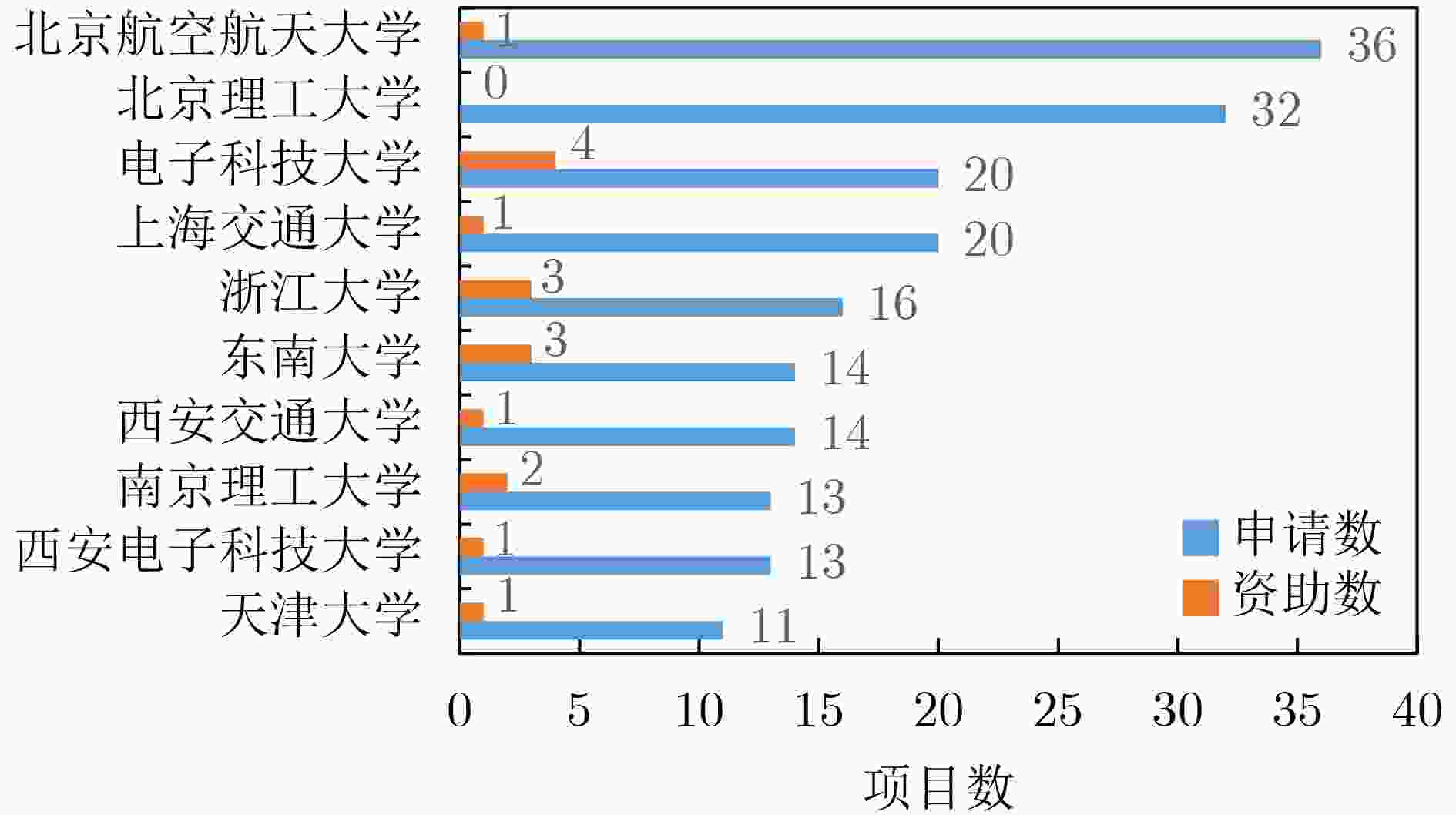

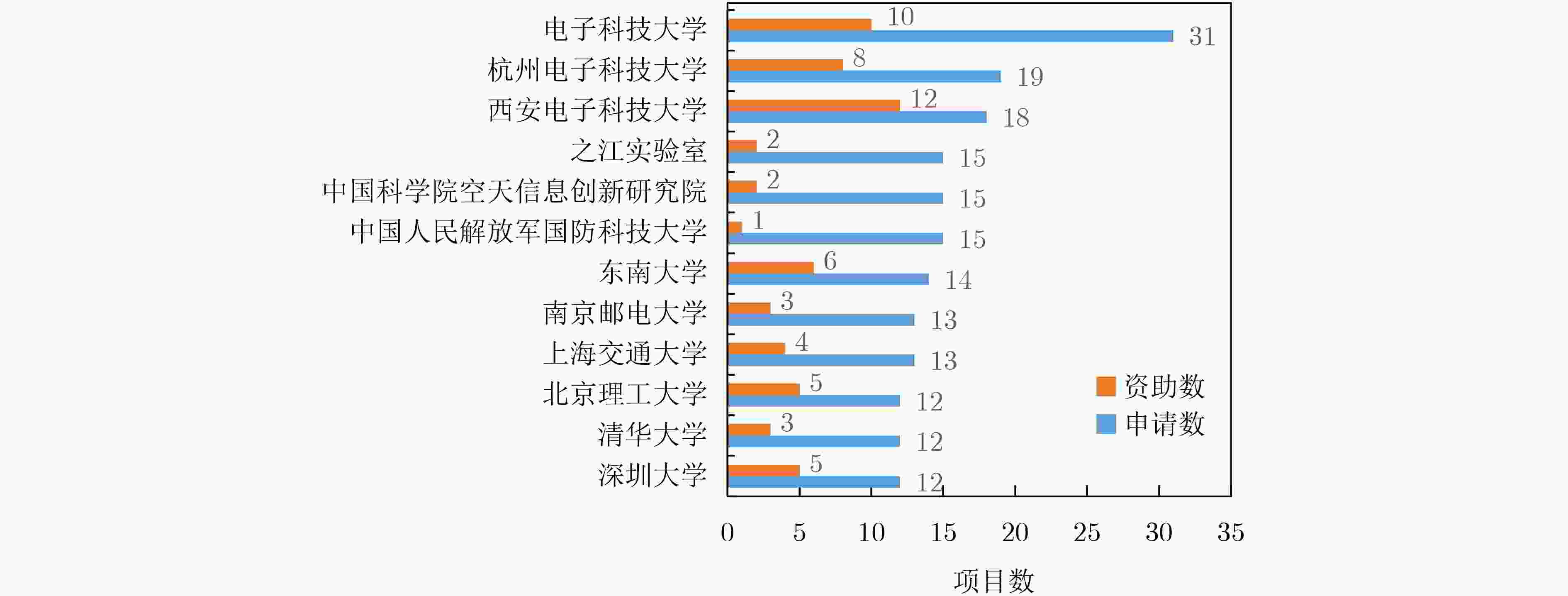

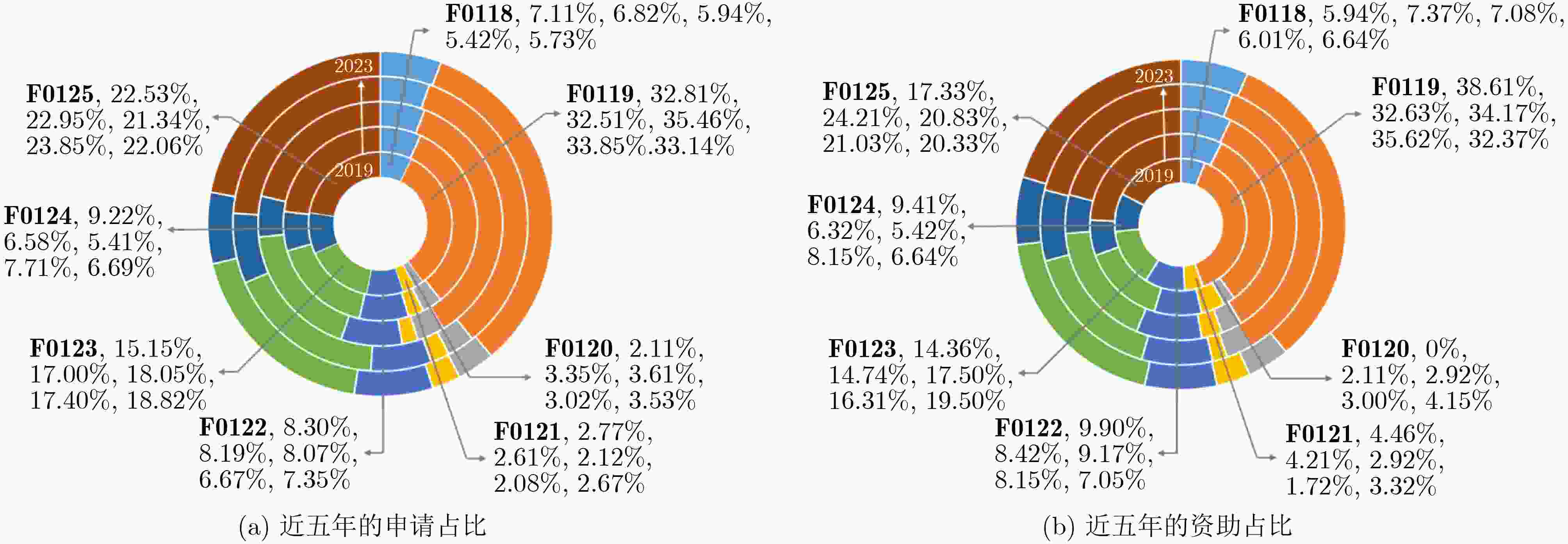

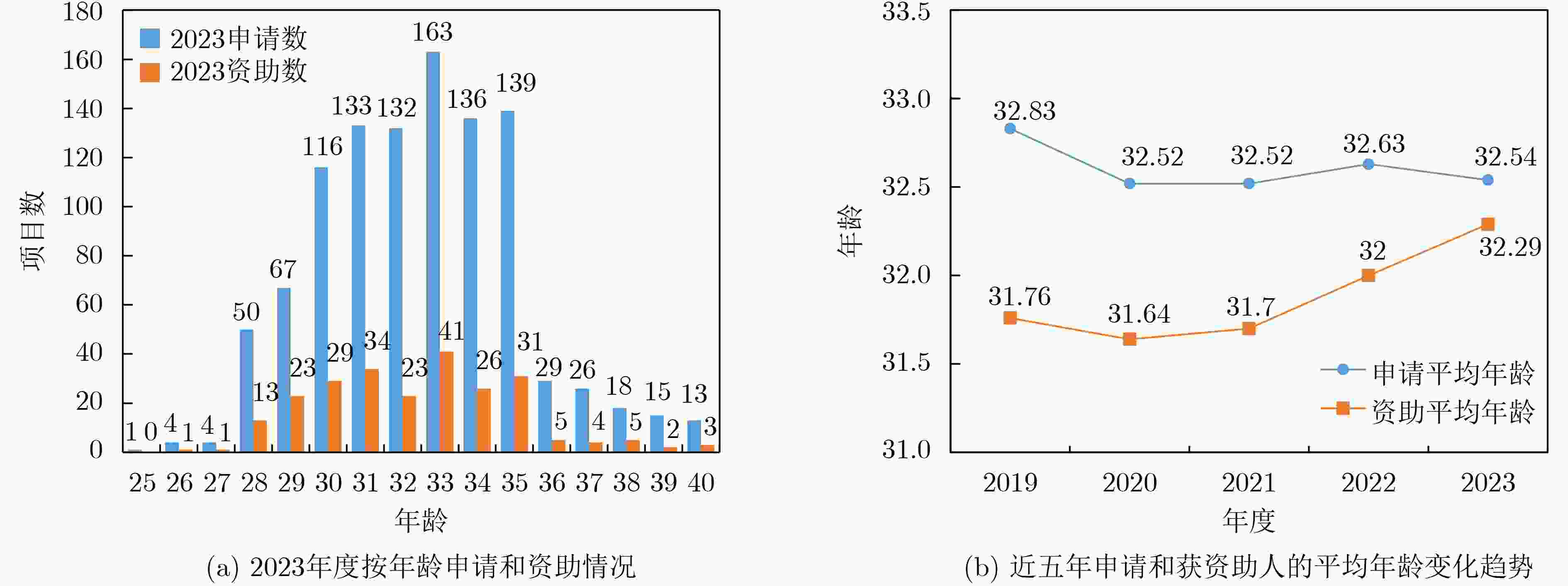

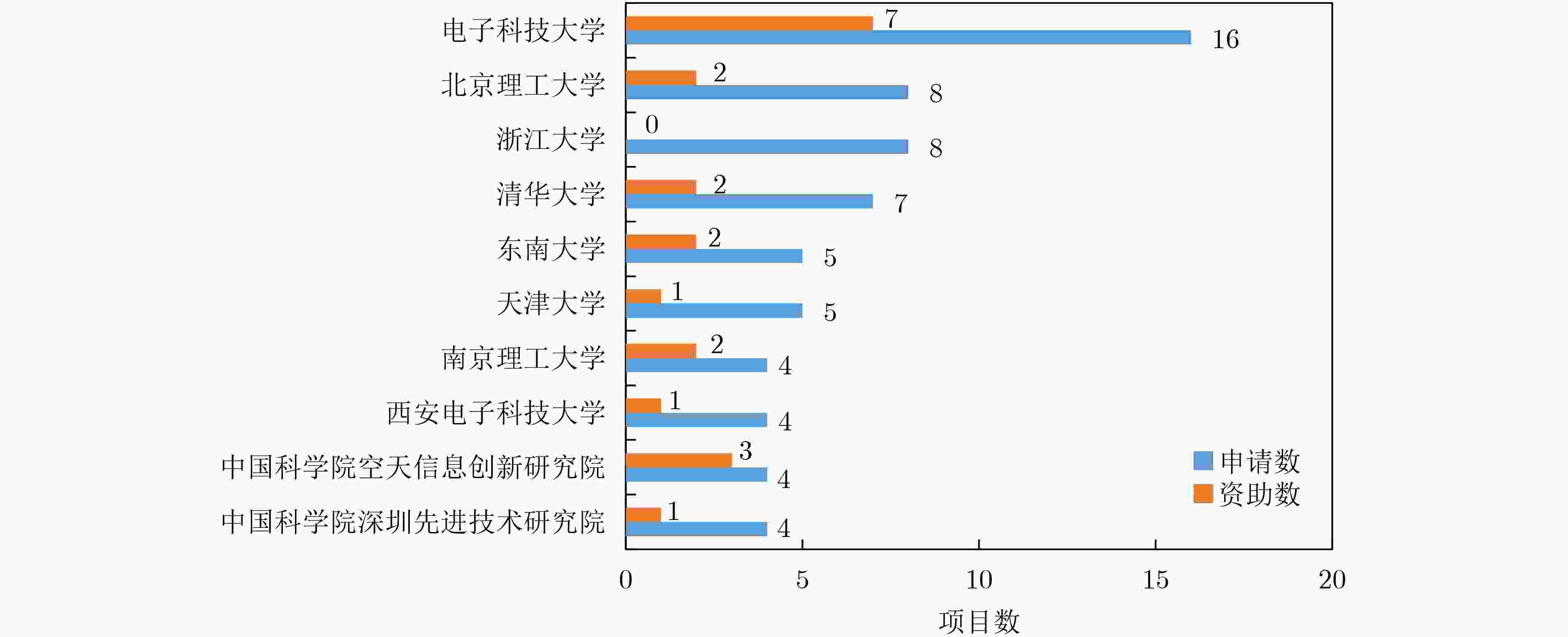

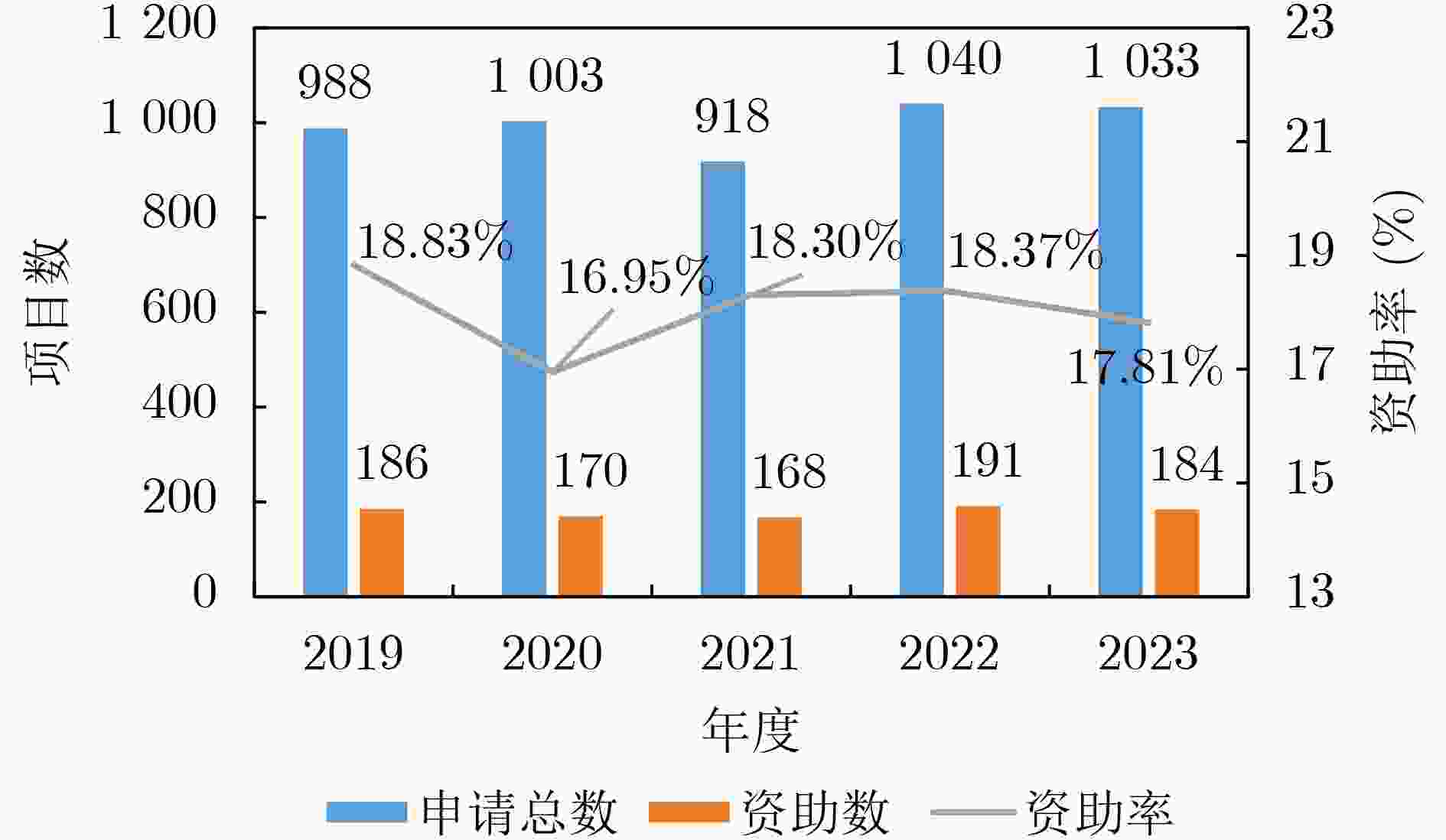

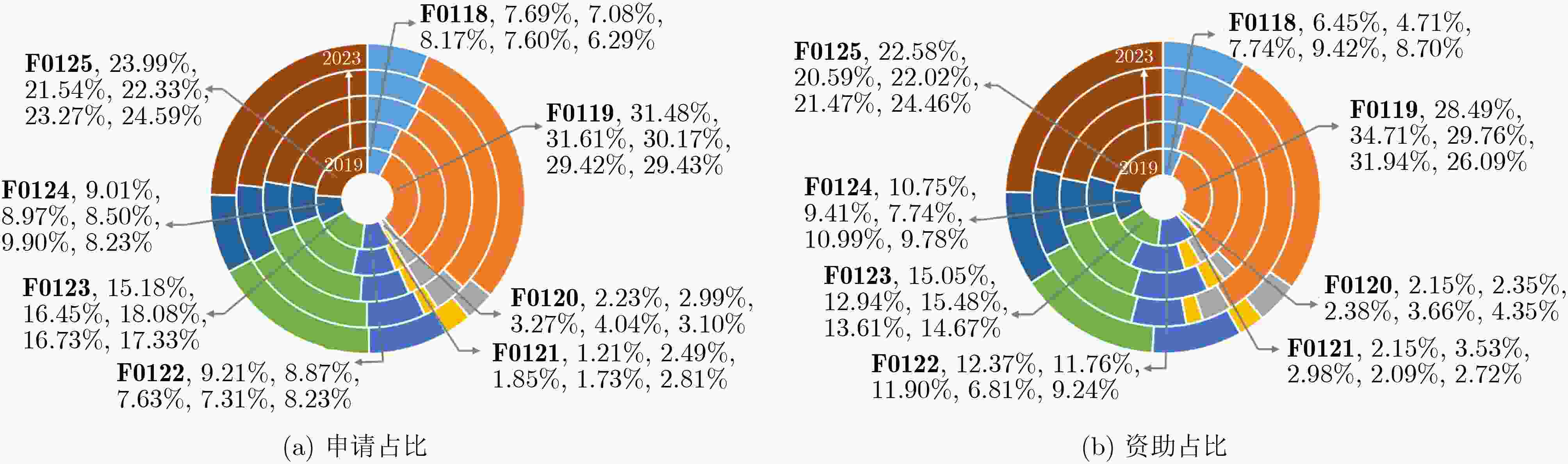

摘要: 国家自然科学基金委员会信息科学部一处“电子科学与技术”领域涉及电路与系统、电磁场与波、电子学及应用等相关研究。本文介绍了2023年度该领域“人才”和“研究”两大项目系列中部分项目的申请与资助情况,并从申请代码、申请人年龄、依托单位分布及其近五年的变化趋势等角度进行了分析,旨在为广大科研人员了解该领域的研究热点和未来发展方向提供参考。Abstract: The electronics and technology area in Division I of Information Science Department of National Natural Science Foundation of China covers the research fields of electrical circuits and systems, electromagnetic fields and waves, electronics and applications. This report introduces the application and funding statistics of several types of projects that are classified into the talent and exploratory funding categories. The analysis is from various aspects, including application codes, age of applicants, host institutions and the trend in recent five years. It aims to provide a general guidance for the scientific researchers about the hot topics and future development directions in this area.

-

表 1 2021—2023年度领域青年项目按科学问题属性申请与资助情况

科学问题属性 2021年 2022年 2023年 申请数 资助率(%) 申请数 资助率(%) 申请数 资助率(%) A 24 4.17 32 18.75 13 7.69 B 323 23.22 345 24.94 352 23.30 C 509 29.67 513 24.56 622 22.99 D 86 15.12 70 21.43 60 21.43 表 2 2023年度领域地区项目所在省份分布情况

省份 依托单位数 申请数 资助数 江西 15 31 4 广西 11 25 7 云南 9 16 1 贵州 5 12 1 甘肃 6 9 3 内蒙古 5 9 1 海南 2 6 0 宁夏 2 5 2 陕西 2 4 1 新疆 3 3 0 青海 1 2 0 四川 1 1 0 合计 62 123 20 表 3 2019—2023 年度领域各二级代码重点项目立项、申请与资助情况

二级代码 立项数 申请数 资助数 F0118 3 8 3 F0119 17 51 17 F0120 3 6 3 F0121 1 1 0 F0122 5 16 4 F0123 9 24 8 F0124 4 10 5 F0125 10 37 10 合计 52 153 50 表 4 2020-2023年度领域面上项目按科学问题属性申请与资助情况

年份 科学问题属性A 科学问题属性B 科学问题属性C 科学问题属性D 申请数 资助数 资助率(%) 申请数 资助数 资助率(%) 申请数 资助数 资助率(%) 申请数 资助数 资助率(%) 2020 62 5 8.06 327 62 18.96 479 83 17.33 135 20 14.81 2021 29 4 13.79 295 66 22.37 491 82 16.70 103 16 15.53 2022 34 8 23.53 342 60 17.54 567 103 18.17 97 20 20.62 2023 21 2 9.52 324 62 19.14 574 99 17.25 114 21 18.42 表 5 领域近两年面上项目RCC反馈情况统计

申请人对专家意见评价 申请人项目是否获资助 未资助项目(份) 资助项目(份) 2022年 2023年 2022年 2023年 很有帮助 476 434 225 229 有帮助 498 385 55 41 帮助不大 149 112 9 6 没有帮助 125 120 6 4 尚未反馈 2977 3189 660 640 总计 4225 4240 955 920 表 6 领域近两年青年项目RCC反馈情况统计

申请人对专家意见评价 申请人项目是否获资助 未资助项目(份) 资助项目(份) 2022年 2023年 2022年 2023年 很有帮助 329 255 240 269 有帮助 180 141 40 26 帮助不大 57 38 0 5 没有帮助 46 46 1 0 尚未反馈 1560 1929 418 423 总计 2172 2409 699 723 -

[1] 窦贤康. 推动基础研究高质量发展为建设世界科技强国夯实根基[J]. 中国科学基金, 2023, 37(5): 709–712. doi: 10.16262/j.cnki.1000-8217.2023.05.001DOU Xiankang. Boost the high-quality development of basic research, consolidate the foundation for building a world leader in science and technology[J]. Bulletin of National Natural Science Foundation of China, 2023, 37(5): 709–712. doi: 10.16262/j.cnki.1000-8217.2023.05.001 [2] 刘晶, 孙玲, 何杰, 等. “电子科学与技术”领域2022年度国家自然科学基金项目受理与资助情况综述[J]. 电子学报, 2023, 51(3): 757–764. doi: 10.12263/DZXB.20230053LIU Jing, SUN Ling, HE Jie, et al. Review of the application and funding statistics of national natural science foundation of china in electronics and technology area for 2022[J]. Acta Electronica Sinica, 2023, 51(3): 757–764. doi: 10.12263/DZXB.20230053 [3] 国家自然科学基金委员会. 2023年度国家自然科学基金项目指南[M]. 北京: 科学出版社, 2023: 1. [4] 国家自然科学基金委员会. 国家自然科学基金创新研究群体项目管理办法[EB/OL]. https://www.nsfc.gov.cn/publish/portal0/tab475/info70245.htm, 2015. [5] 国家自然科学基金委员会. 关于发布2023年度国家自然科学基金原创探索计划项目申请指南的通告[EB/OL]. https://www.nsfc.gov.cn/publish/portal0/tab442/info88482.htm, 2023. [6] 国家自然科学基金委员会. “十四五”发展规划[EB/OL]. https://www.nsfc.gov.cn/publish/portal0/tab1392/. -

下载:

下载:

下载:

下载: