Wafer-Level Adaptive Testing Method with Low Test Escape

-

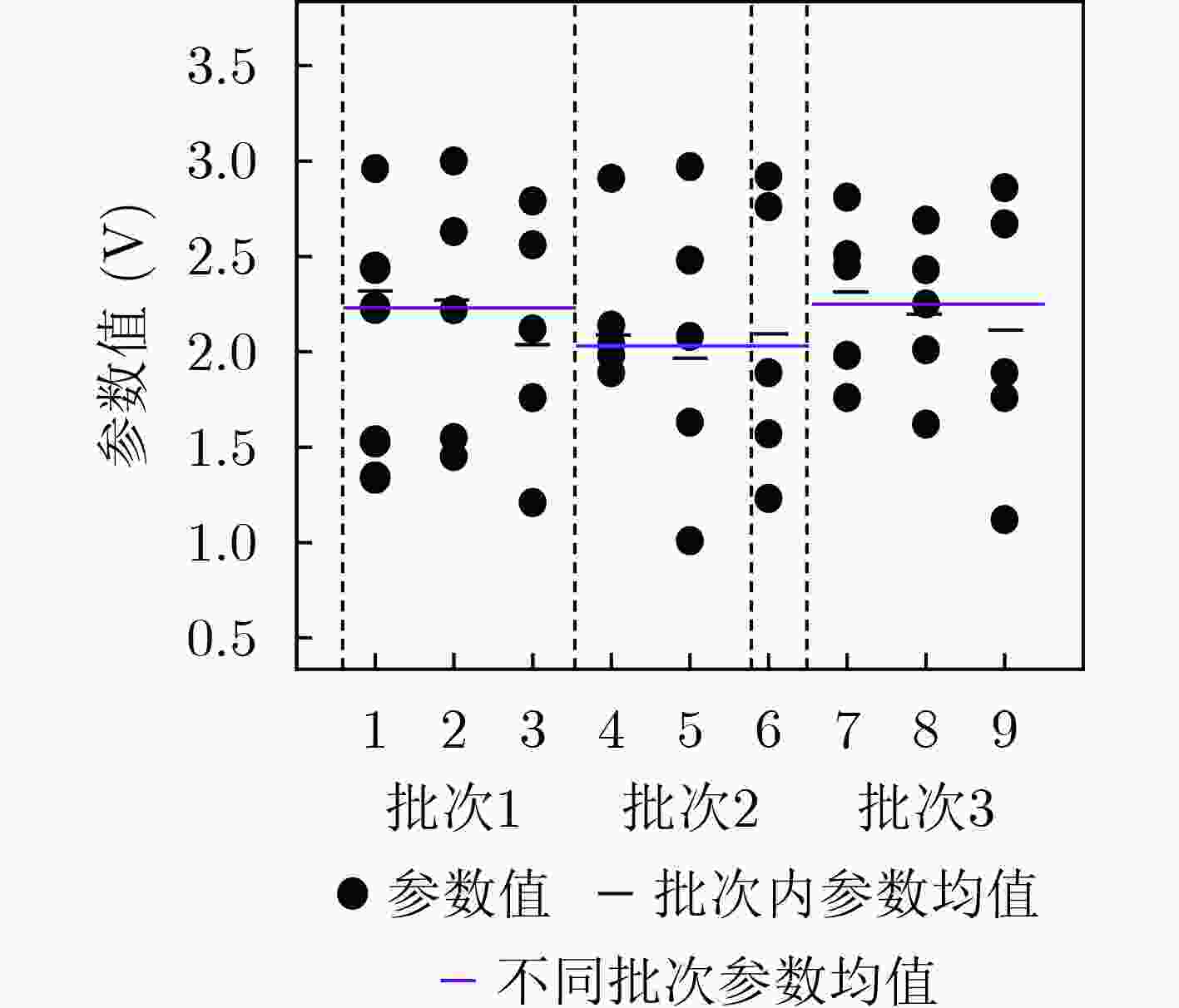

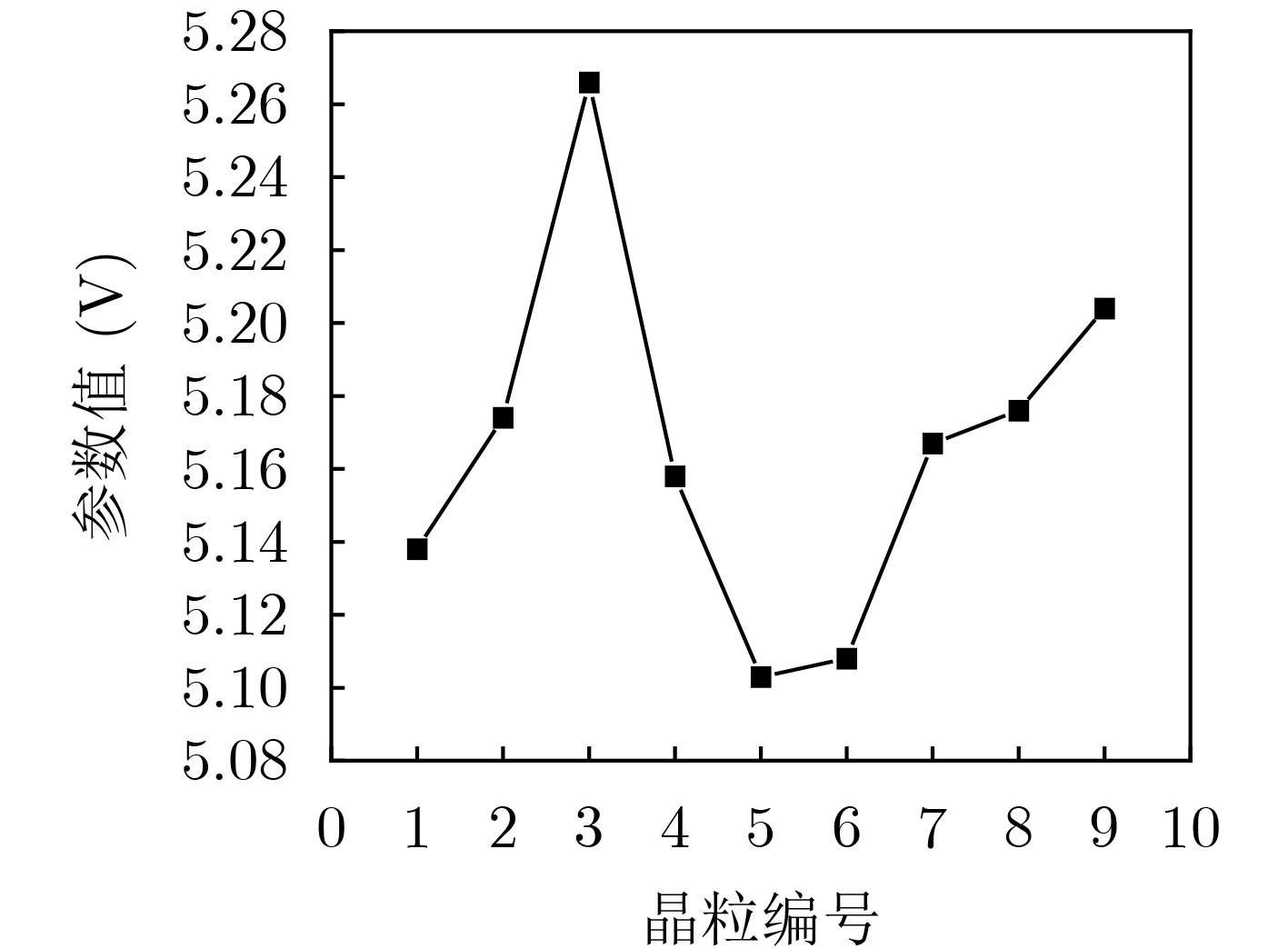

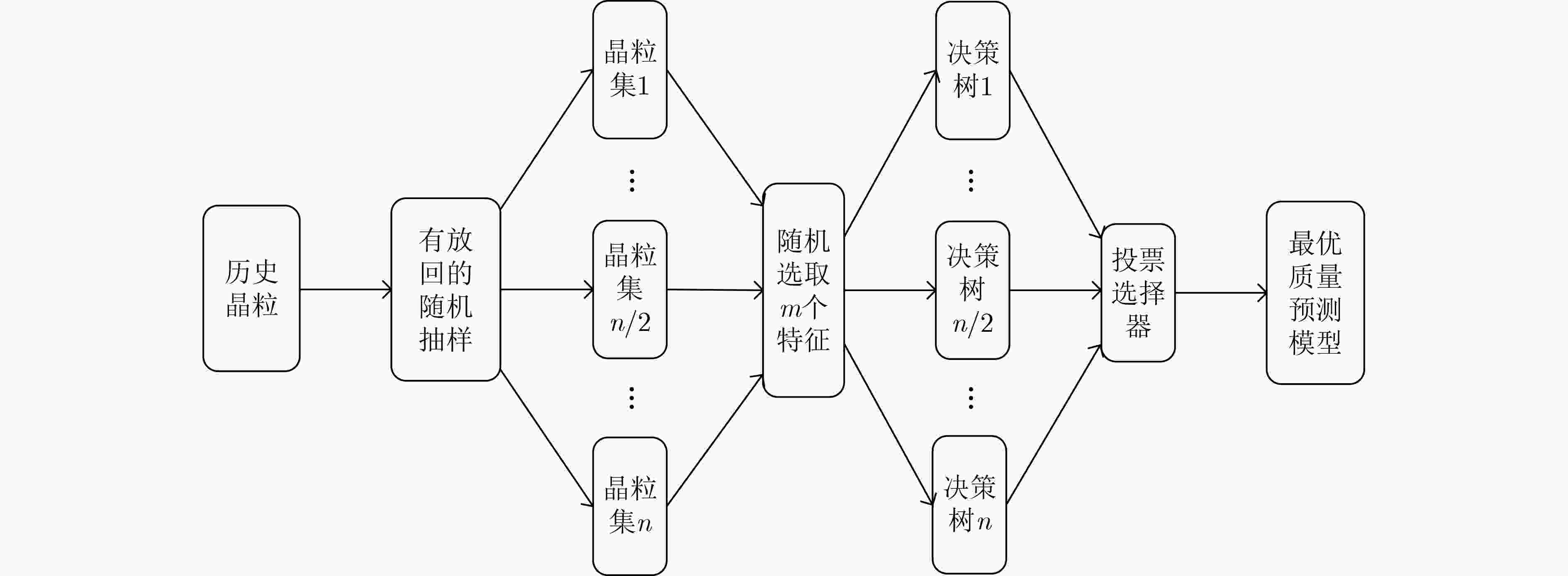

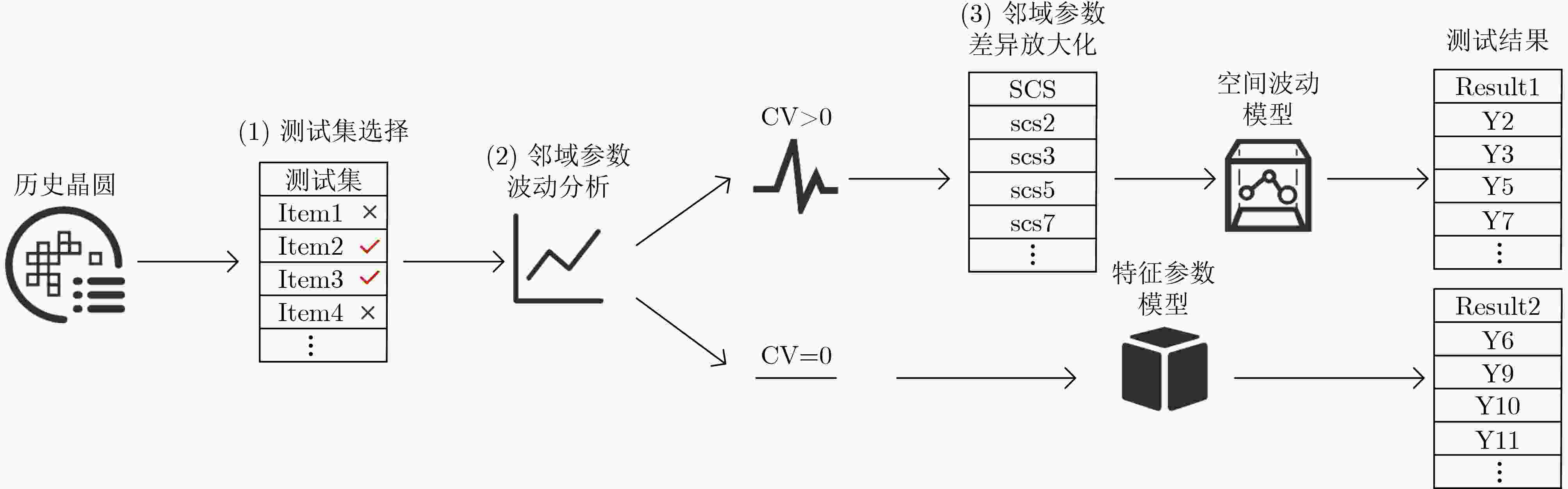

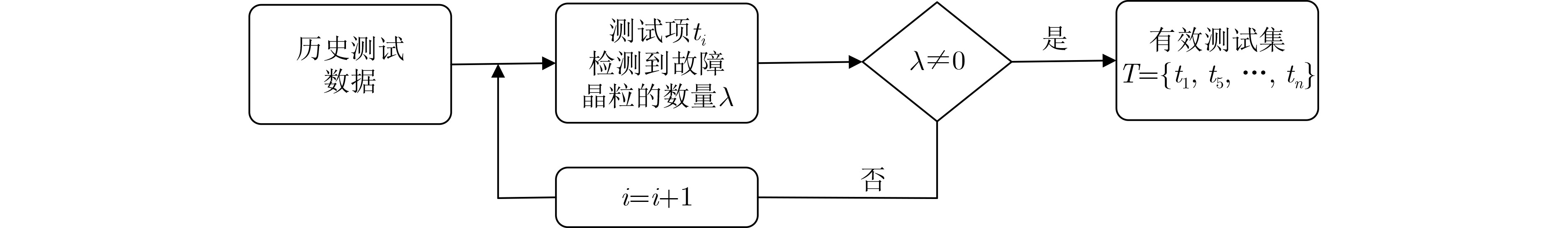

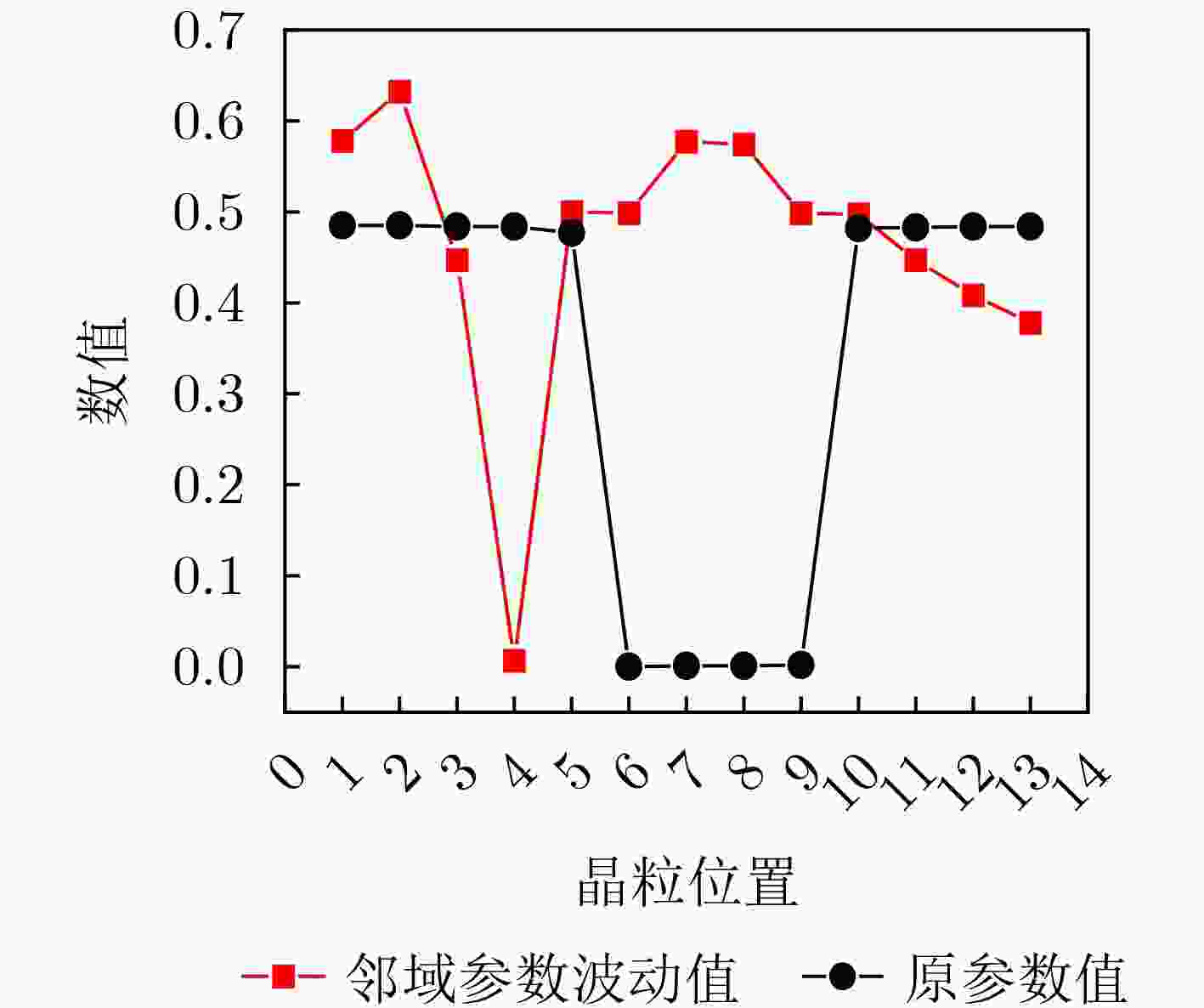

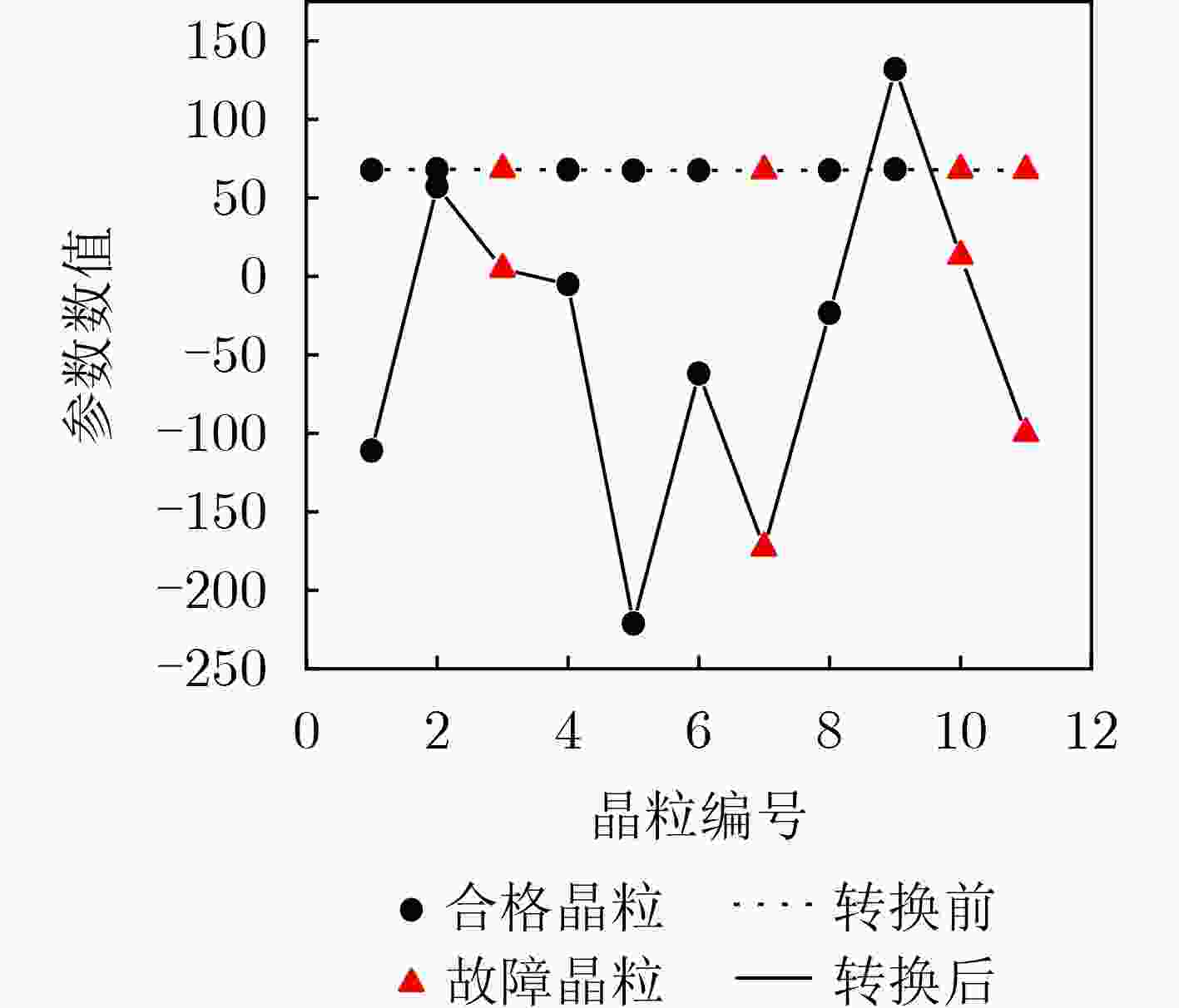

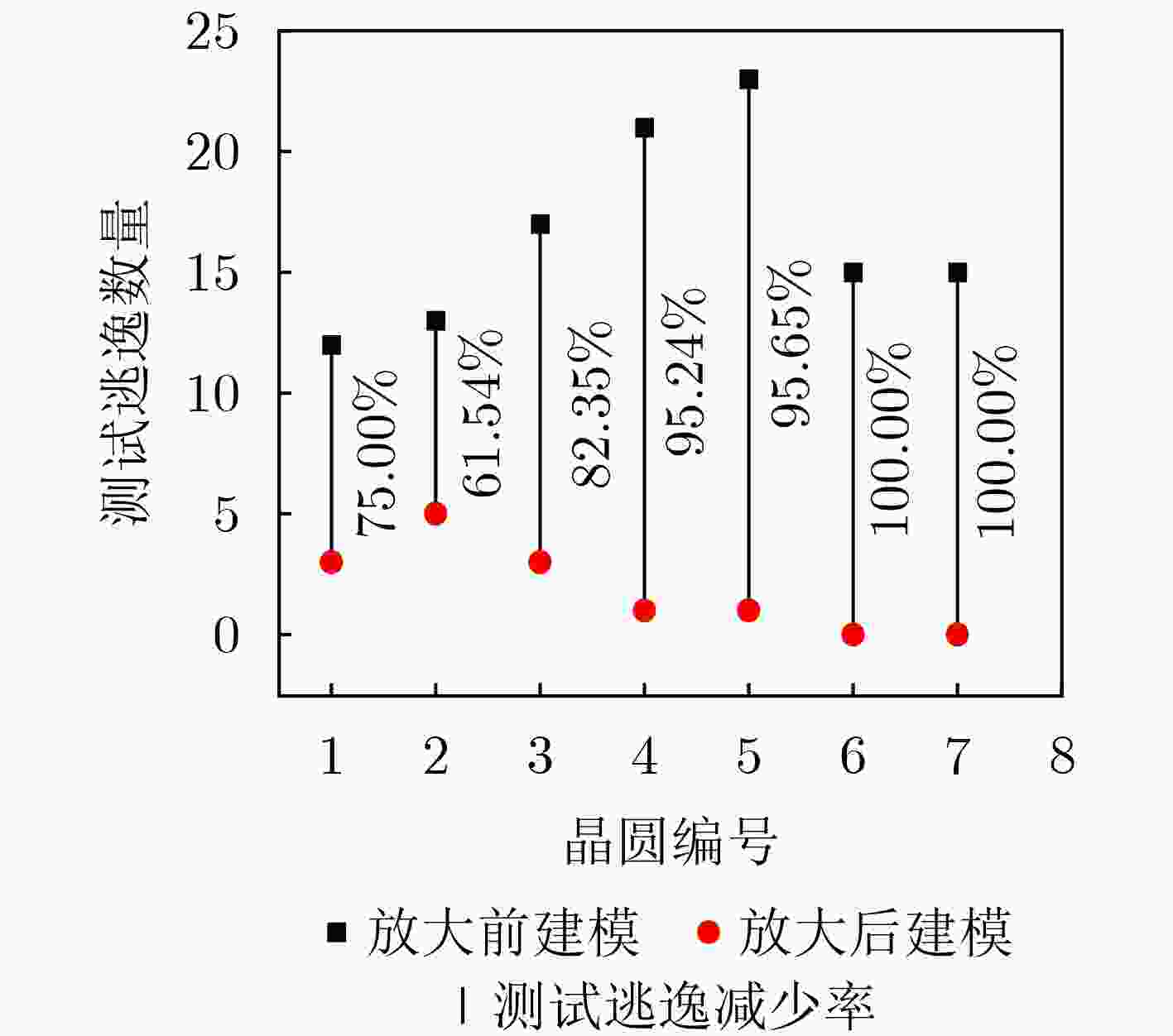

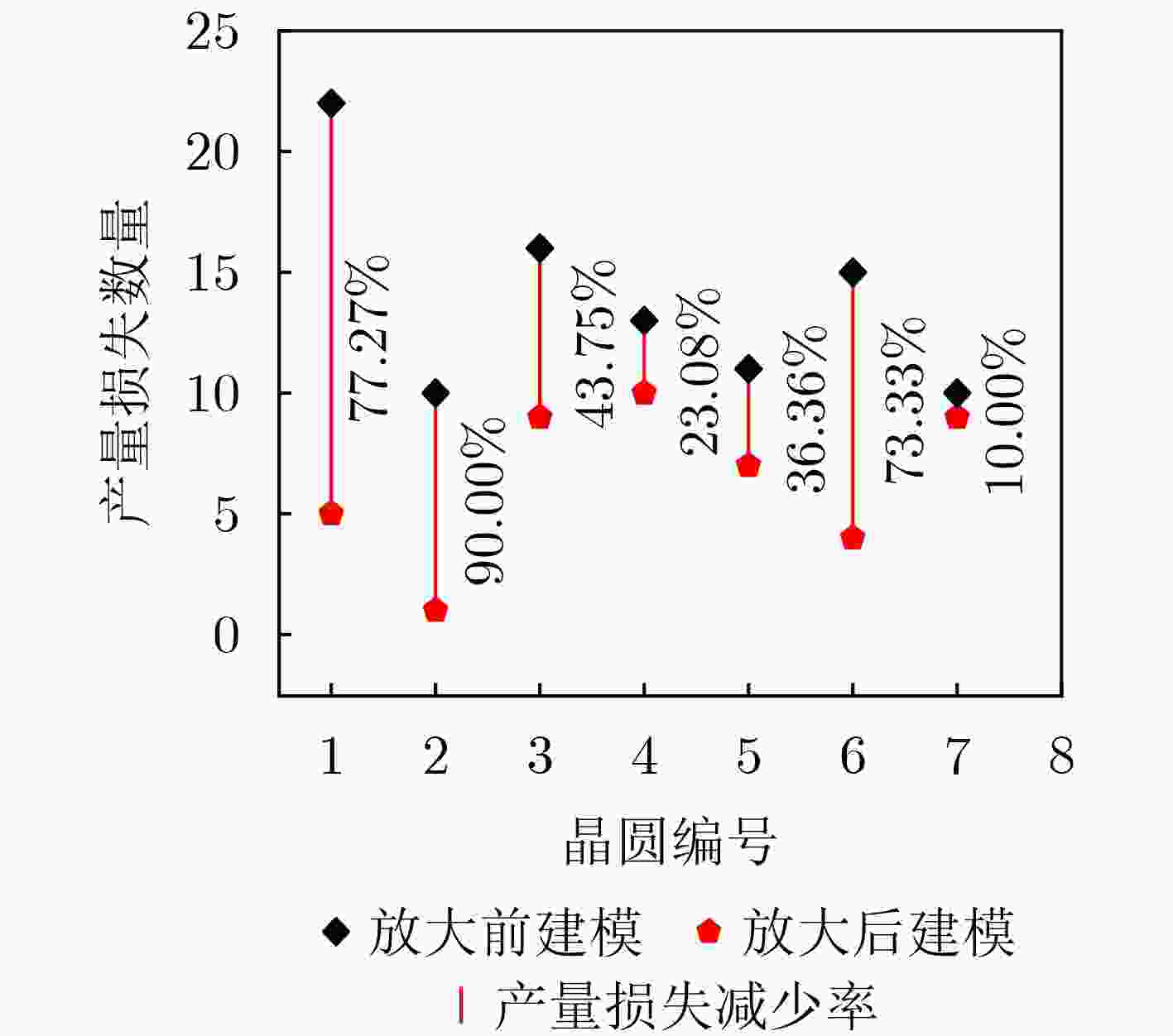

摘要: 为了降低集成电路中测试成本,提高测试质量,该文提出一种低测试逃逸率的晶圆级适应性测试方法。该方法根据历史测试数据中测试项检测故障晶粒的有效性筛选测试集,降低待测晶圆的测试成本。同时,分析晶粒邻域参数波动程度,将存在波动晶粒的参数差异进行放大并建模,提高该类晶粒质量预测模型的分类准确率;无波动的晶粒使用有效测试集建模的方法进行质量预测,减少测试逃逸的风险。根据实际晶圆生产数据的实验结果表明,该方法可以明显降低晶圆的测试项成本40.13%,并保持较低的测试逃逸率0.0091%。Abstract: In order to reduce the test cost and improve the test quality in ICs. A wafer-level adaptive test method with low test escapes is proposed. The method reduces the test cost of wafers to be tested by filtering the test set based on the effectiveness of the test item to detect faulty die in historical test data. At the same time, the degree of fluctuation of the parameters in the neighborhood of the die is analyzed, and the parameter differences of the die with fluctuations are amplified and modeled to improve the classification accuracy of the quality prediction model for this type of dies; The dies without fluctuations are used for quality prediction using the valid test set modeling method to reduce the risk of test escapes. Experimental results based on actual wafer production data show that the method can significantly reduce the test item cost of wafers by 40.13% and maintain a low test escape rate of 0.0091%.

-

表 1 实验数据分布

批次 晶粒总数 平均良率(%) 测试项数 1 383640 98.55 67 2 312312 98.96 39 3 789276 99.76 25 表 2 对比实验结果(%)

方案 TIRR TER YLR 本文方法 40.13 0.0091 0.0137 方法1 45.23 0.0570 0.0337 方法2 35.85 0.0188 0.0274 -

[1] LIU Mengyun, PAN Renjian, YE Fangming, et al. Fine-grained adaptive testing based on quality prediction[J]. ACM Transactions on Design Automation of Electronic Systems, 2020, 25(5): 38. doi: 10.1145/3385261 [2] YILMAZ E, OZEV S, SINANOGLU O, et al. Adaptive testing: Conquering process variations[C]. 2012 17th IEEE European Test Symposium, Annecy, France, 2012: 1–6. [3] WANG Rui, ZHANG Linmiao, and CHEN Nan. Spatial correlated data monitoring in semiconductor manufacturing using gaussian process model[J]. IEEE Transactions on Semiconductor Manufacturing, 2019, 32(1): 104–111. doi: 10.1109/TSM.2018.2883763 [4] XUE Cheng and SHAWN R D. A one-pass test-selection method for maximizing test coverage[C]. 2015 33rd IEEE International Conference on Computer Design, New York, USA, 2015: 621–628. [5] PAN Renjian, ZHANG Zhaobo, LI Xin, et al. Black-box test-cost reduction based on Bayesian network models[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2021, 40(2): 386–399. doi: 10.1109/TCAD.2020.2994257 [6] LIU Mengyun, LI Xin, CHAKRABARTY K, et al. Knowledge transfer in board-level functional fault diagnosis enabled by domain adaptation[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41(3): 762–775. doi: 10.1109/TCAD.2021.3065919 [7] XU Hongwei, ZHANG Jie, LV Youlong, et al. Hybrid feature selection for wafer acceptance test parameters in semiconductor manufacturing[J]. IEEE Access, 2020, 8: 17320–17330. doi: 10.1109/ACCESS.2020.2966520 [8] LIN Fan, HSU C K, and CHENG K T. AdaTest: An efficient statistical test framework for test escape screening[C]. 2015 IEEE International Test Conference, Anaheim, USA, 2015: 1–8. [9] LIN Fan, HSU C K, and CHENG K T. Learning from production test data: Correlation exploration and feature engineering[C]. 2014 IEEE 23rd Asian Test Symposium, Hangzhou, China, 2014: 236–241. [10] LIN Fan, HSU C K, and CHENG K T. Feature engineering with canonical analysis for effective statistical tests screening test escapes[C]. 2014 International Test Conference, Seattle, USA, 2014: 1–10. [11] SHINTANI M, MIAN R U H, INOUE M, et al. Wafer-level variation modeling for multi-site RF IC testing via hierarchical Gaussian process[C]. 2021 IEEE International Test Conference, Anaheim, USA, 2021: 103–112. [12] ZHANG Jinli, YOU Hailong, JIA Renxu, et al. The research on screening method to reduce chip test escapes by using multi-correlation analysis of parameters[J]. IEEE Transactions on Semiconductor Manufacturing, 2022, 35(2): 266–271. doi: 10.1109/TSM.2022.3144283 [13] KATRAGADDA V, MUTHEE M, GASASIRA A, et al. Algorithm based adaptive parametric testing for outlier detection and test time reduction[C]. 2018 IEEE International Conference on Microelectronic Test Structures, Austin, USA, 2018: 142–146. [14] KUO Y T, LIN Weichen, CHEN Chun, et al. Minimum operating voltage prediction in production test using accumulative learning[C]. 2021 IEEE International Test Conference, Anaheim, USA, 2021: 47–52. [15] DAASCH W R, COTA K, MCNAMES J, et al. Neighbor selection for variance reduction in I/sub DDQ/ and other parametric data[C]. The International Test Conference, Baltimore, USA, 2002: 1240–1248. [16] ZHANG Jinli, YOU Hailong, and JIA Renxu. Reliability hazard characterization of wafer-level spatial metrology parameters based on LOF-KNN method[C]. 2019 IEEE 26th International Symposium on Physical and Failure Analysis of Integrated Circuits, Hangzhou, China, 2019: 1–4. [17] YANG Chenghao, YEN C H, WANG Tingrui, et al. Identifying good-dice-in-bad-neighborhoods using artificial neural networks[C]. 2021 IEEE 39th VLSI Test Symposium, San Diego, USA, 2021: 1–7. -

下载:

下载:

下载:

下载: