Design of an Process In-Memory Full Adder Based on Voltage-Controlled Spin Orbit Torque Magnetic Random Access Memory

-

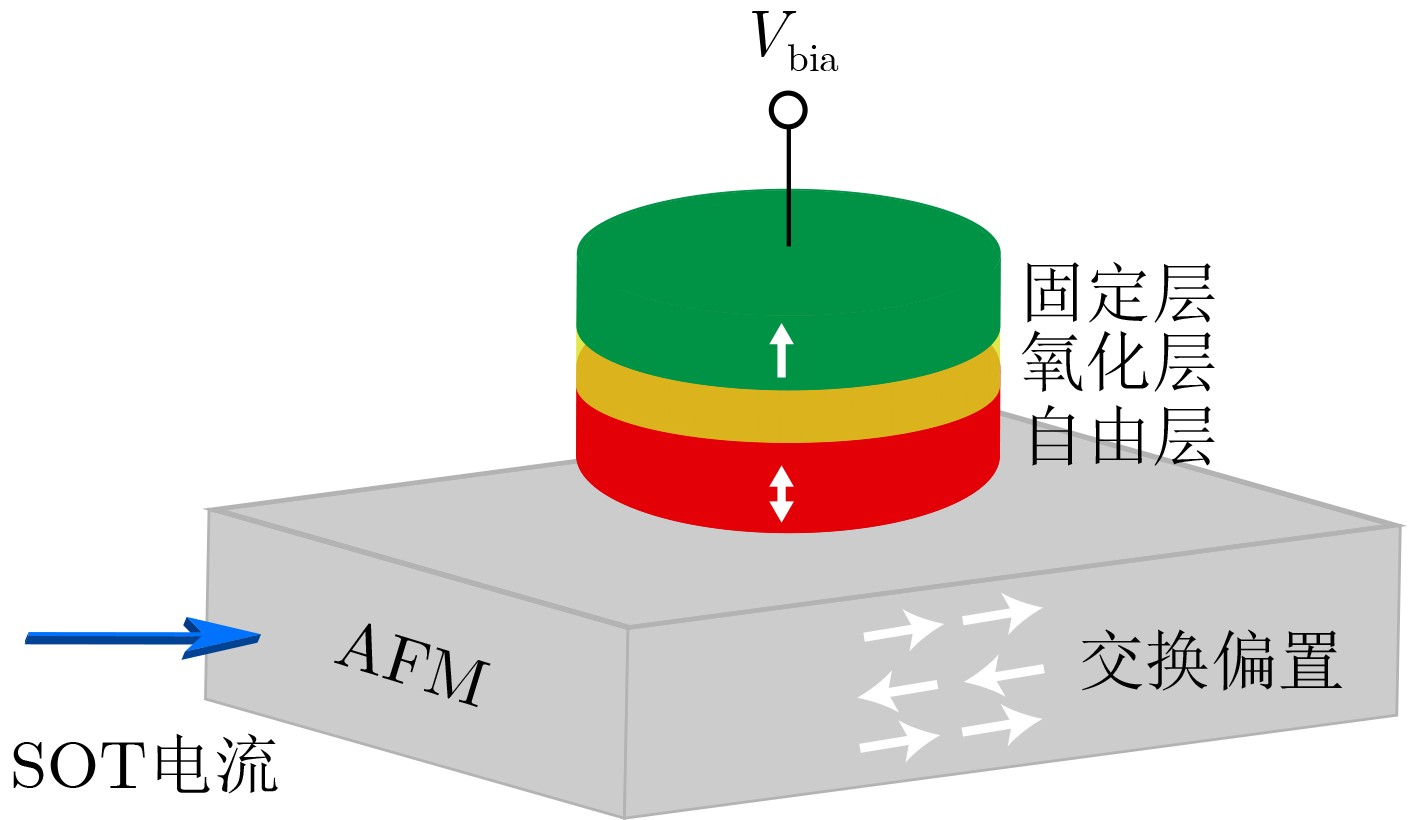

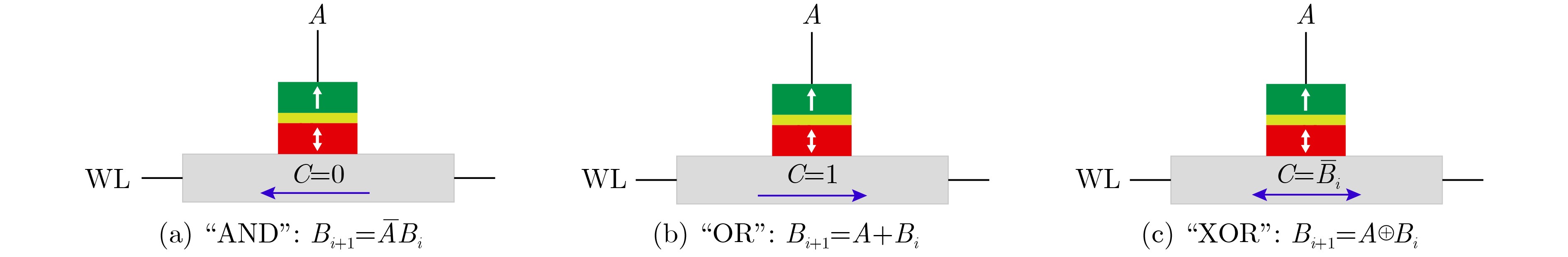

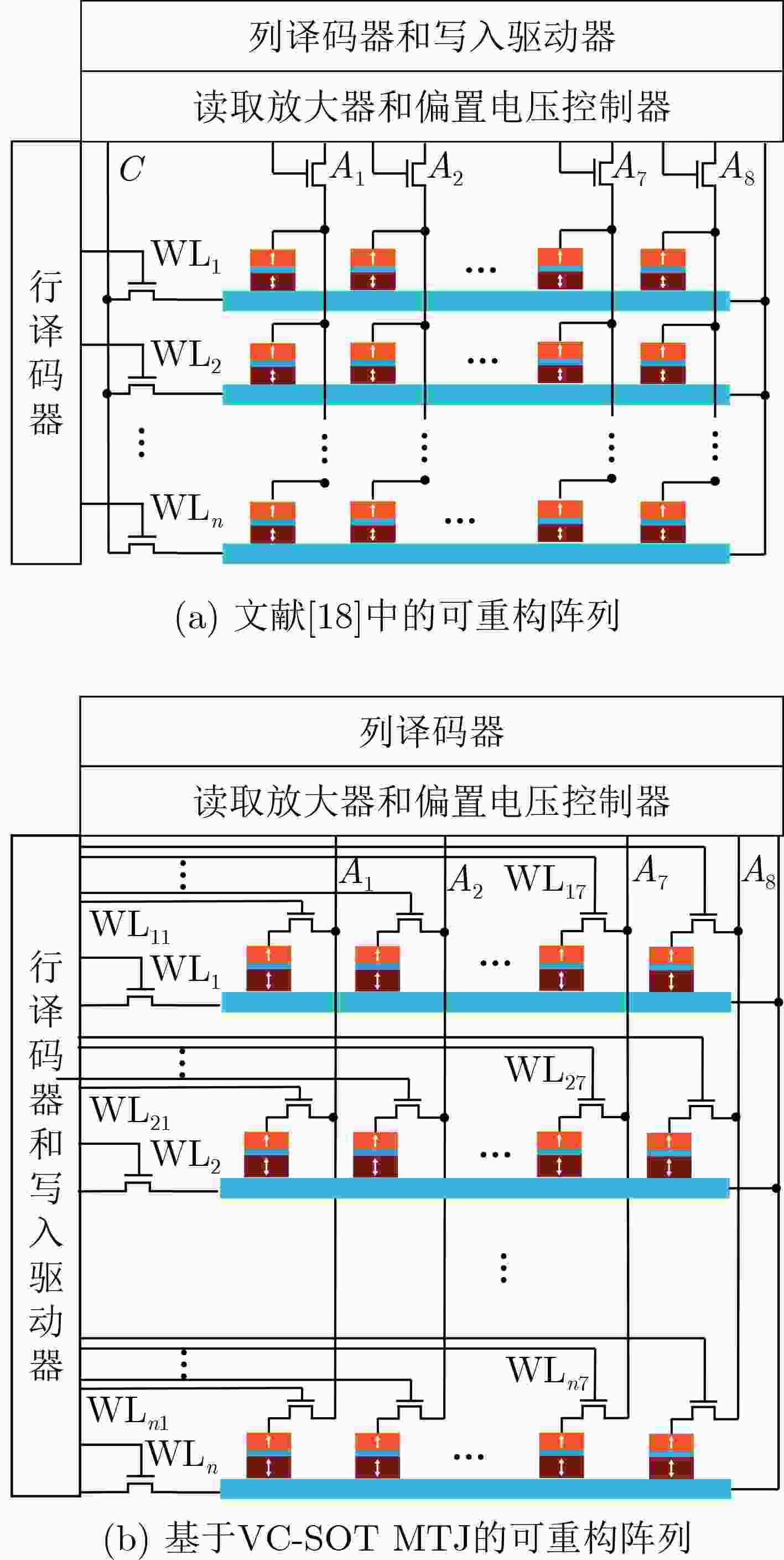

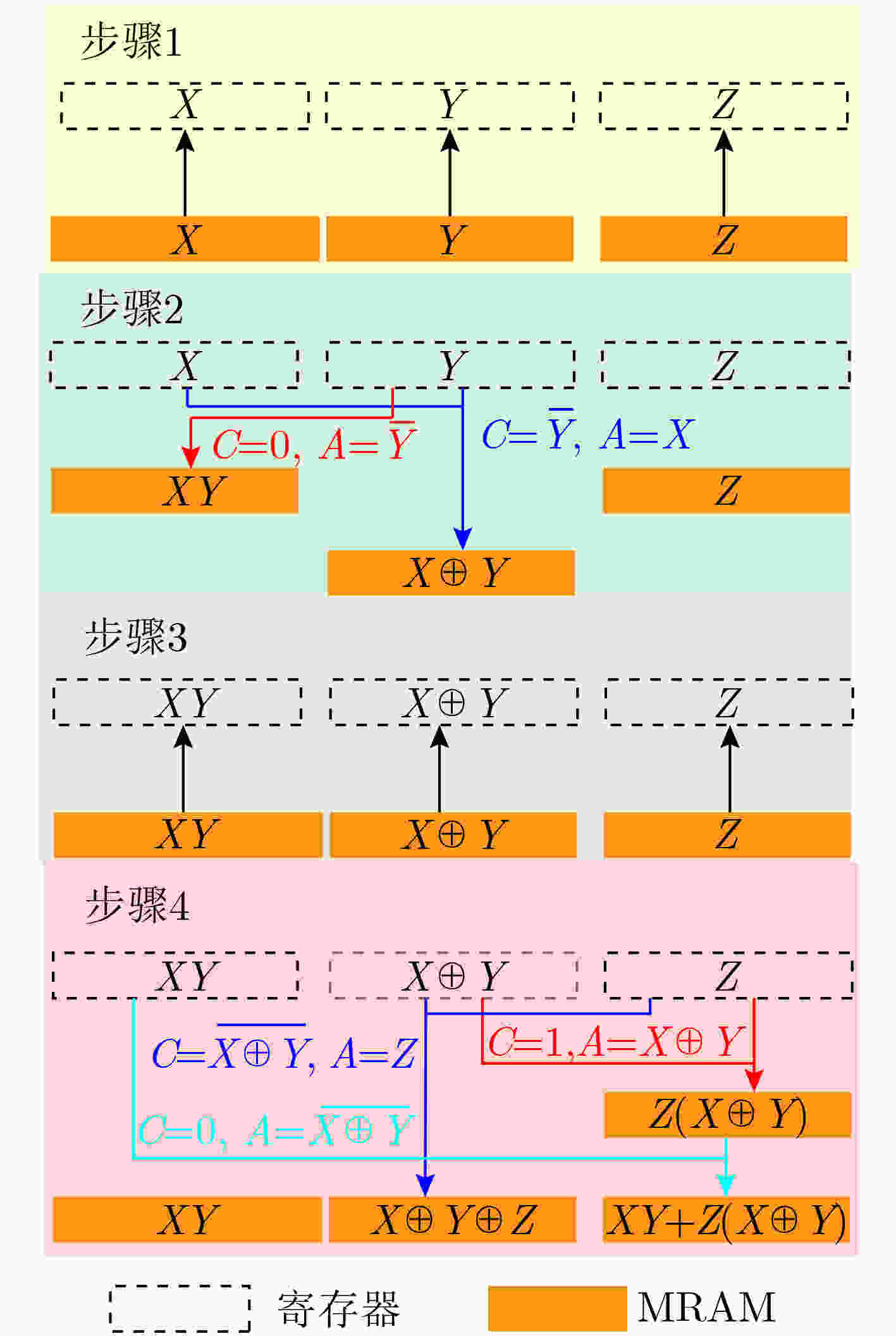

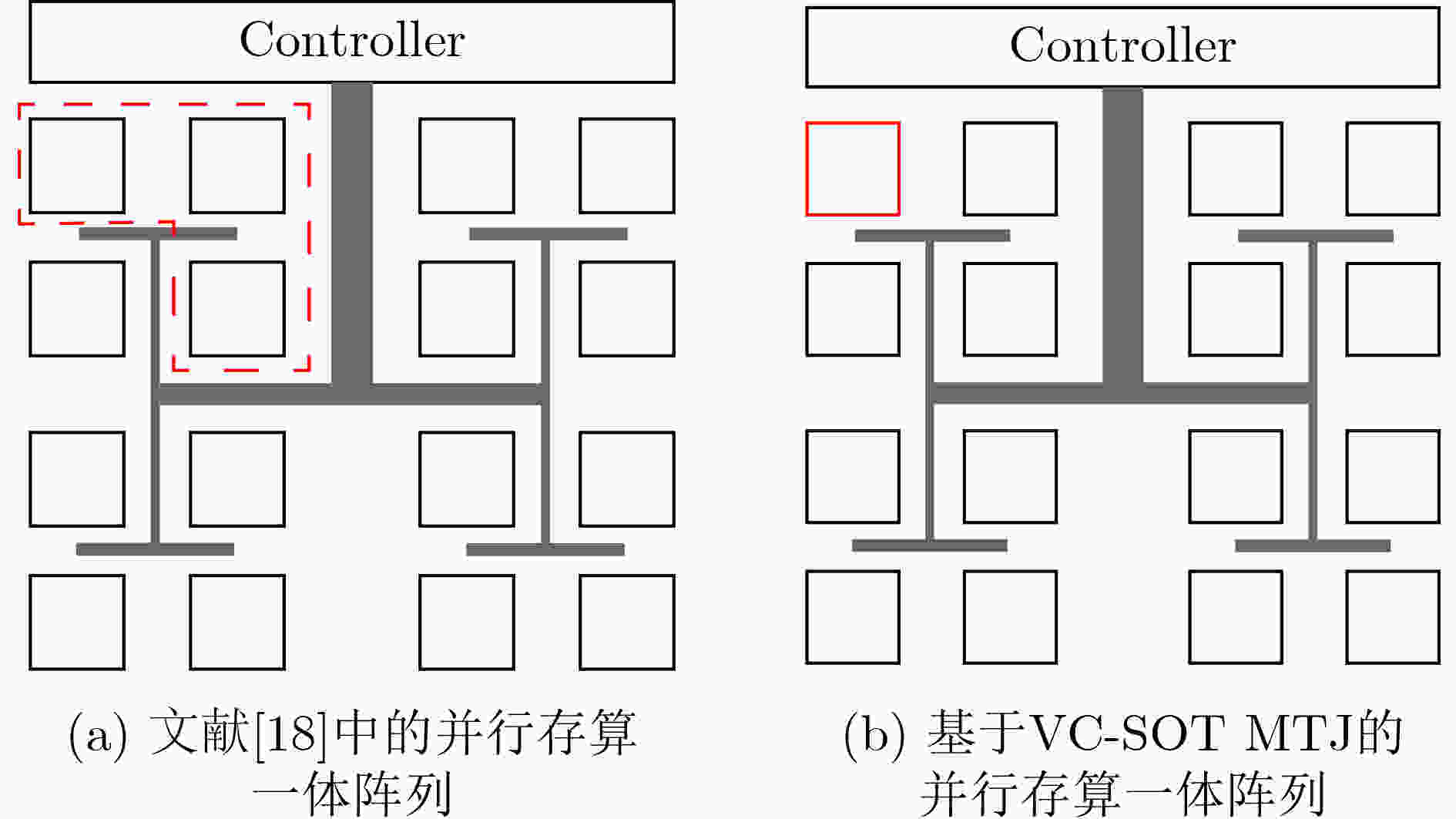

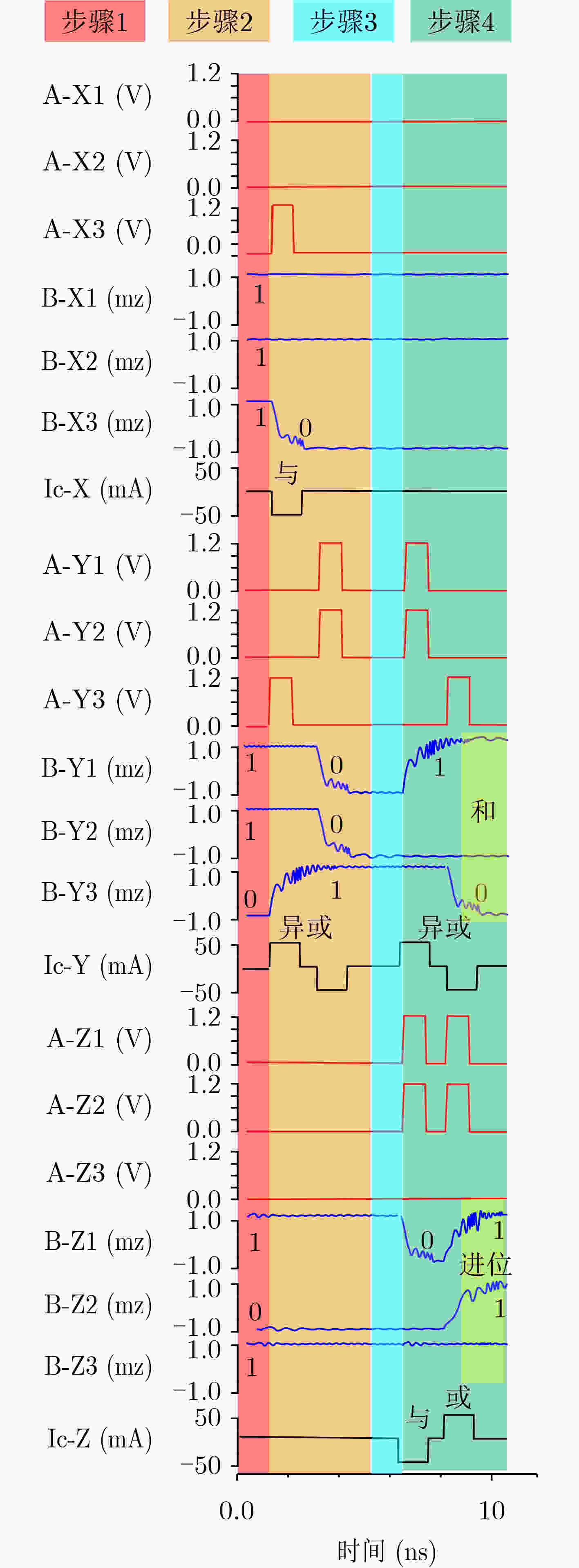

摘要: 随着互补金属氧化物半导体技术的特征尺寸的不断缩小,其面临的静态功耗问题缩越来越突出。自旋磁随机存储器(MRAM)由于其非易失性、高速读写能力、高集成密度和CMOS兼容性等良好特性,受到了学术界的广泛关注和研究。该文采用电压调控的自旋轨道矩随机存储器设计了一个存内计算可重构逻辑阵列,能够实现全部布尔逻辑功能和高度并行计算。在此基础上设计了存内计算全加器并在40 nm工艺下进行了仿真验证。结果表明,与当前先进研究相比,该文提出的全加器具有更高的并行度,能够实现更快的计算速度(约1.11 ns/bit)和更低的计算功耗(约5.07 fJ/bit)。Abstract: With the feature size of complementary metal oxide semiconductor technology decreasing, the problem of static power consumption becomes more and more serious. Spin Magnetic Random Access Memory (MRAM) has been widely studied because of its nonvolatile, high-speed read-write ability, high integration density and CMOS compatibility. In this paper, a reconfigurable memory logic array is designed using a novel Voltage-Controlled Spin-Orbit Torque(VC-SOT) random access memory. It can implement all of Boolean Logic functions and highly parallel computing. On this basis, an in-memory computing Full Adder (FA) is designed and simulated in 40 nm process. The results show that the proposed full adder has higher parallelism, faster computation speed (~1.11 ns/bit) and lower computation power consumption (~5.07 fJ/bit).

-

Key words:

- Full adder /

- Process In-Memory /

- Spin orbital torque /

- Magnetic tunnel junction /

- Reconfigurable

-

表 1 VC-SOT MTJ模型的参数和变量

参数 描述 默认值 tOX (nm) 氧化层高度 1.50~2.50 tFL (nm) 自由层厚度 1.10 l,w,d (nm) 重金属尺寸 100, 100, 3 α 磁阻尼常数 0.02 TMR(0) 零偏置电压下的隧穿磁电阻比率 100% -

[1] KIM N S, AUSTIN T, BAAUW D, et al. Leakage current: Moore's law meets static power[J]. Computer, 2003, 36(12): 68–75. doi: 10.1109/MC.2003.1250885 [2] MUSELLO A, GARZÓN E, LANUZZA M, et al. XNOR-bitcount operation exploiting computing-in-memory with STT-MRAMs[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 70(3): 1259–1263. [3] WONG H S P and SALAHUDDIN S. Memory leads the way to better computing[J]. Nature Nanotechnology, 2015, 10(3): 191–194. doi: 10.1038/nnano.2015.29 [4] KANG Wang, ZHANG Yue, WANG Zhaohao, et al. Spintronics: Emerging ultra-low-power circuits and systems beyond MOS technology[J]. ACM Journal on Emerging Technologies in Computing Systems, 2015, 12(2): 16. doi: 10.1145/2663351 [5] SHARMA V, KIM H, and KIM T T H. A 64 Kb reconfigurable full-precision digital ReRAM-based compute-in-memory for artificial intelligence applications[J]. IEEE Transactions on Circuits and Systems I:Regular Papers, 2022, 69(8): 3284–3296. doi: 10.1109/TCSI.2022.3168053 [6] YOON J H, CHANG Muya, KHWA W S, et al. A 40-nm, 64-Kb, 56.67 TOPS/W voltage-sensing computing-in-memory/digital RRAM macro supporting iterative write with verification and online read-disturb detection[J]. IEEE Journal of Solid-State Circuits, 2022, 57(1): 68–79. doi: 10.1109/JSSC.2021.3101209 [7] GUO Zongxia, YIN Jialiang, BAI Yue, et al. Spintronics for energy- efficient computing: An overview and outlook[J]. Proceedings of the IEEE, 2021, 109(8): 1398–1417. doi: 10.1109/JPROC.2021.3084997 [8] SAFRANSKI C, HU Guohan, SUN J Z, et al. Reliable sub-nanosecond switching in magnetic tunnel junctions for MRAM applications[J]. IEEE Transactions on Electron Devices, 2022, 69(12): 7180–7183. doi: 10.1109/TED.2022.3214168 [9] DONG Xiangyu, WU Xiaoxia, SUN Guangyu, et al. Circuit and microarchitecture evaluation of 3D stacking magnetic RAM (MRAM) as a universal memory replacement[C]. The 45th Annual Design Automation Conference, Anaheim, USA, 2008. [10] ZAND R, ROOHI A, SALEHI S, et al. Scalable adaptive spintronic reconfigurable logic using area-matched MTJ design[J]. IEEE Transactions on Circuits and Systems II:Express Briefs, 2016, 63(7): 678–682. doi: 10.1109/TCSII.2016.2532099 [11] FONG Xuanyao, KIM Y, YOGENDRA K, et al. Spin-transfer torque devices for logic and memory: Prospects and perspectives[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2016, 35(1): 1–22. doi: 10.1109/TCAD.2015.2481793 [12] ROOHI A, ZAND R, and DEMARA R F. A tunable majority gate-based full adder using current-induced domain wall nanomagnets[J]. IEEE Transactions on Magnetics, 2016, 52(8): 1–7. doi: 10.1109/TMAG.2016.2540600 [13] RAJAEI R. Highly reliable and low-power magnetic full-adder designs for nanoscale technologies[J]. Microelectronics Reliability, 2017, 73: 129–135. doi: 10.1016/j.microrel.2017.04.033 [14] DENG Erya, YUE Zue, KLEIN J O, et al. Low power magnetic full-adder based on spin transfer torque MRAM[J]. IEEE Transactions on Magnetics, 2013, 49(9): 4982–4987. doi: 10.1109/TMAG.2013.2245911 [15] ZHONG Xingwei, CAI Kui, and SONG Guanghui. Union bound analysis for Spin-Torque Transfer Magnetic Random Access Memory (STT-MRAM) with channel quantization[J]. IEEE Transactions on Magnetics, 2022, 58(2): 3400105. doi: 10.1109/TMAG.2021.3084210 [16] SHAO Qiming, LI Peng, LIU Luqiao, et al. Roadmap of spin-orbit torques[J]. IEEE Transactions on Magnetics, 2021, 57(7): 800439. doi: 10.1109/TMAG.2021.3078583 [17] PENG Shouzhong, LU Jiaqi, LI Weixiang, et al. Field-free switching of perpendicular magnetization through voltage-gated spin-orbit torque[C]. 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, USA, 2019. [18] ZHANG He, KANG Wang, WU Bi, et al. Spintronic processing unit within voltage-gated spin hall effect MRAMs[J]. IEEE Transactions on Nanotechnology, 2019, 18: 473–483. doi: 10.1109/TNANO.2019.2914009 -

下载:

下载:

下载:

下载: