Design of Highly Robust Glitch-Physical Uunclonable Functions Based on ZnO Memristor

-

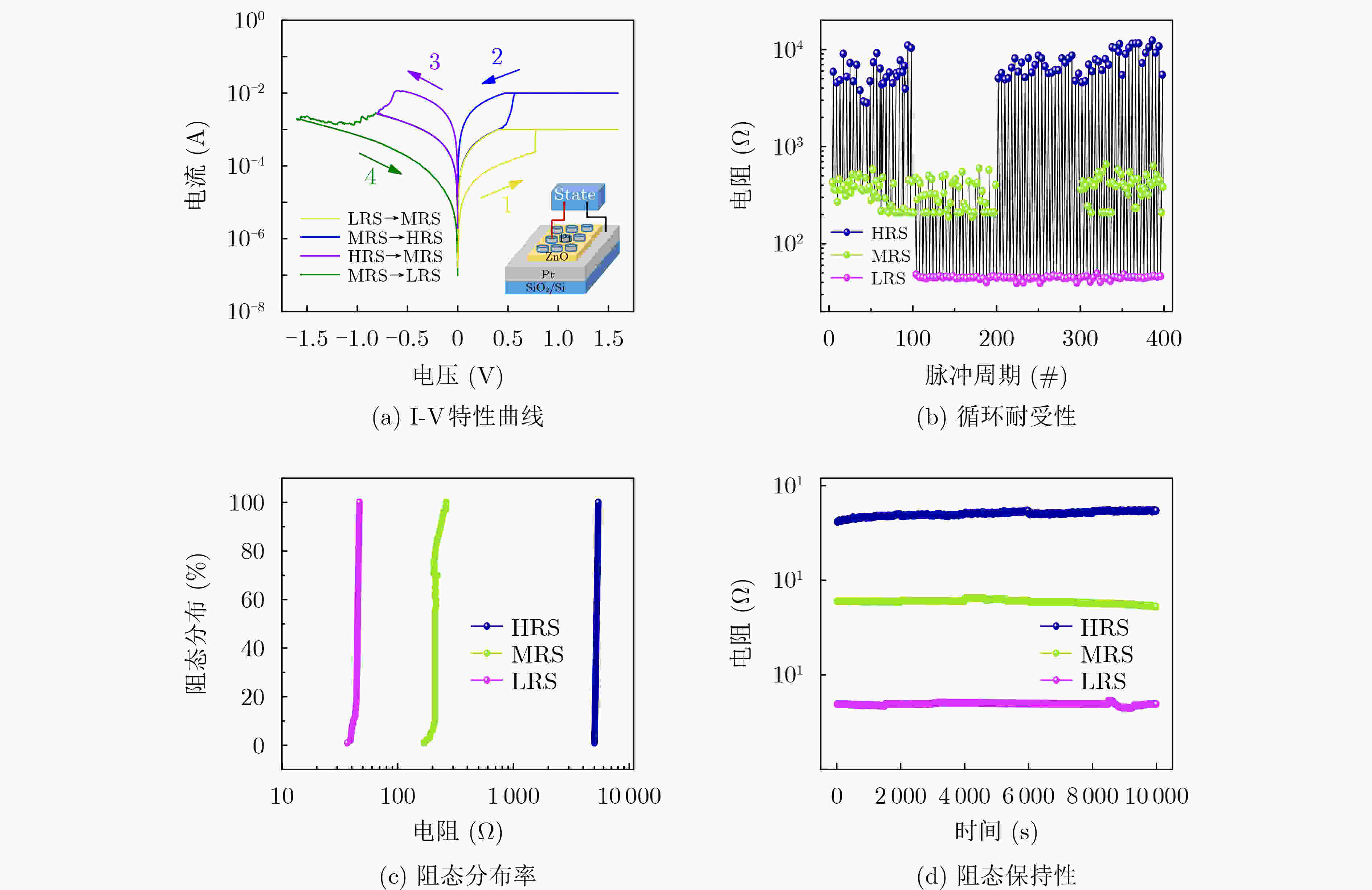

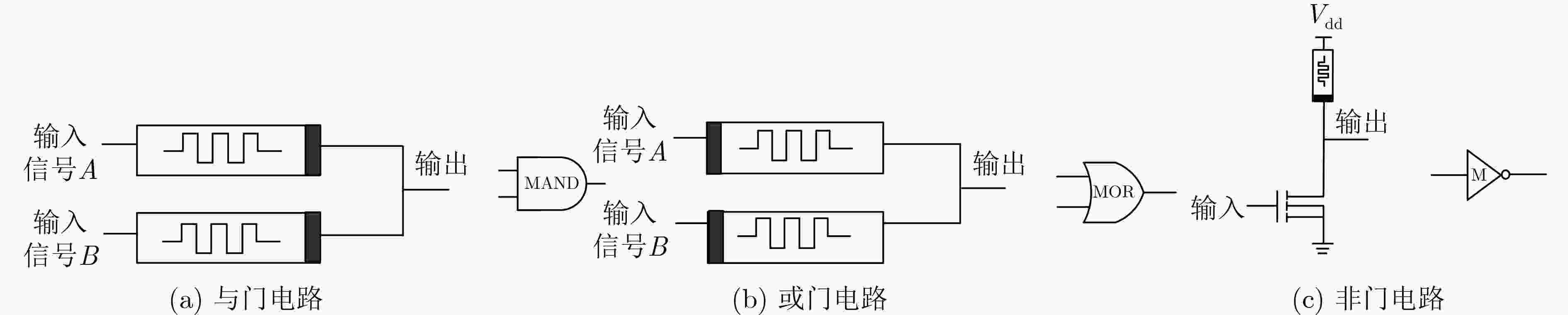

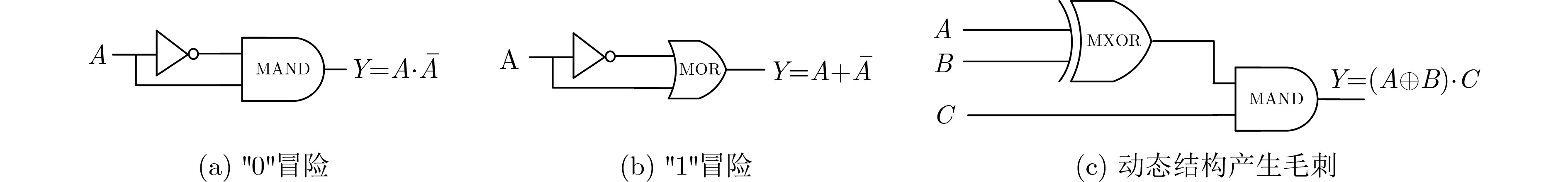

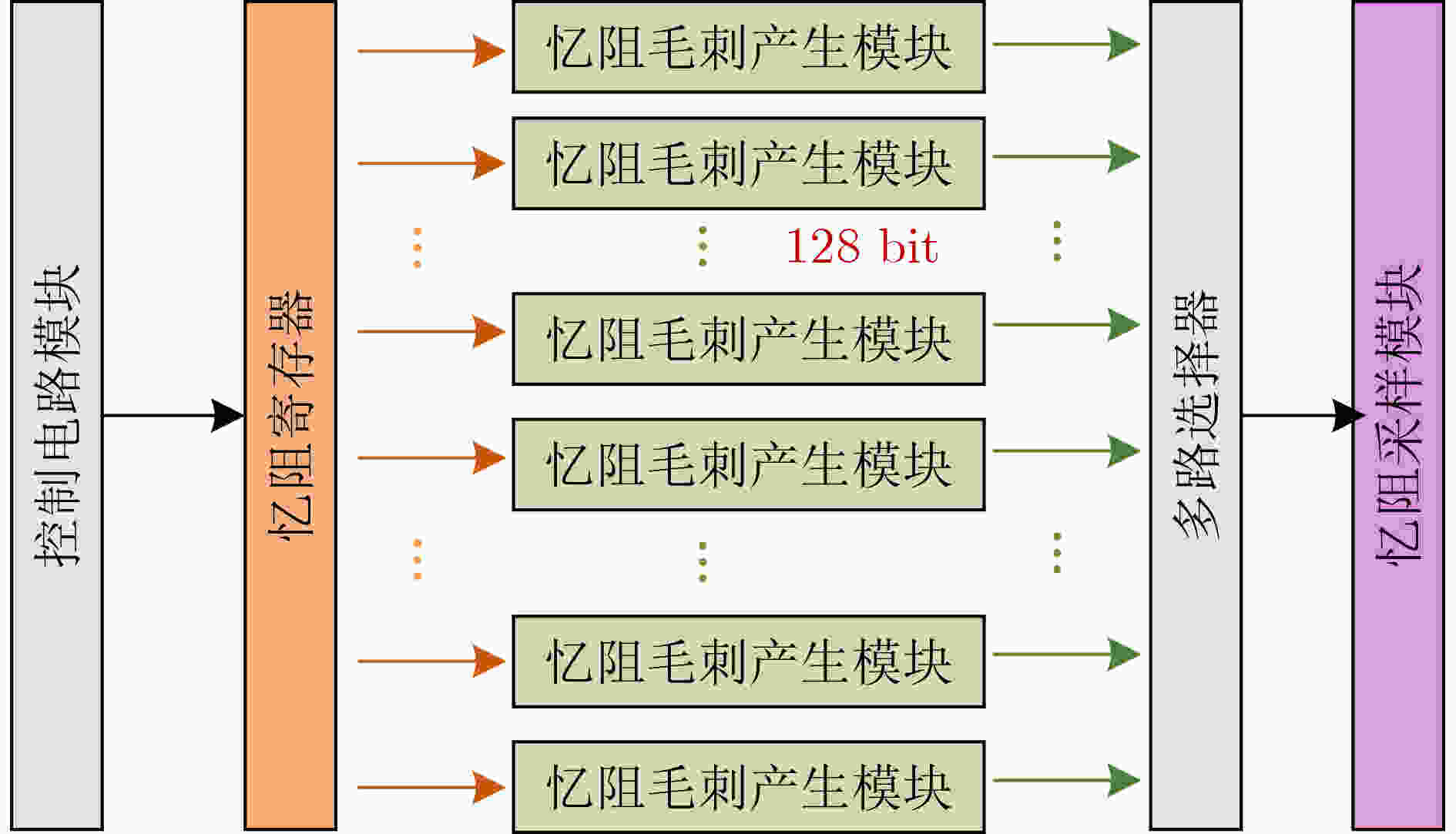

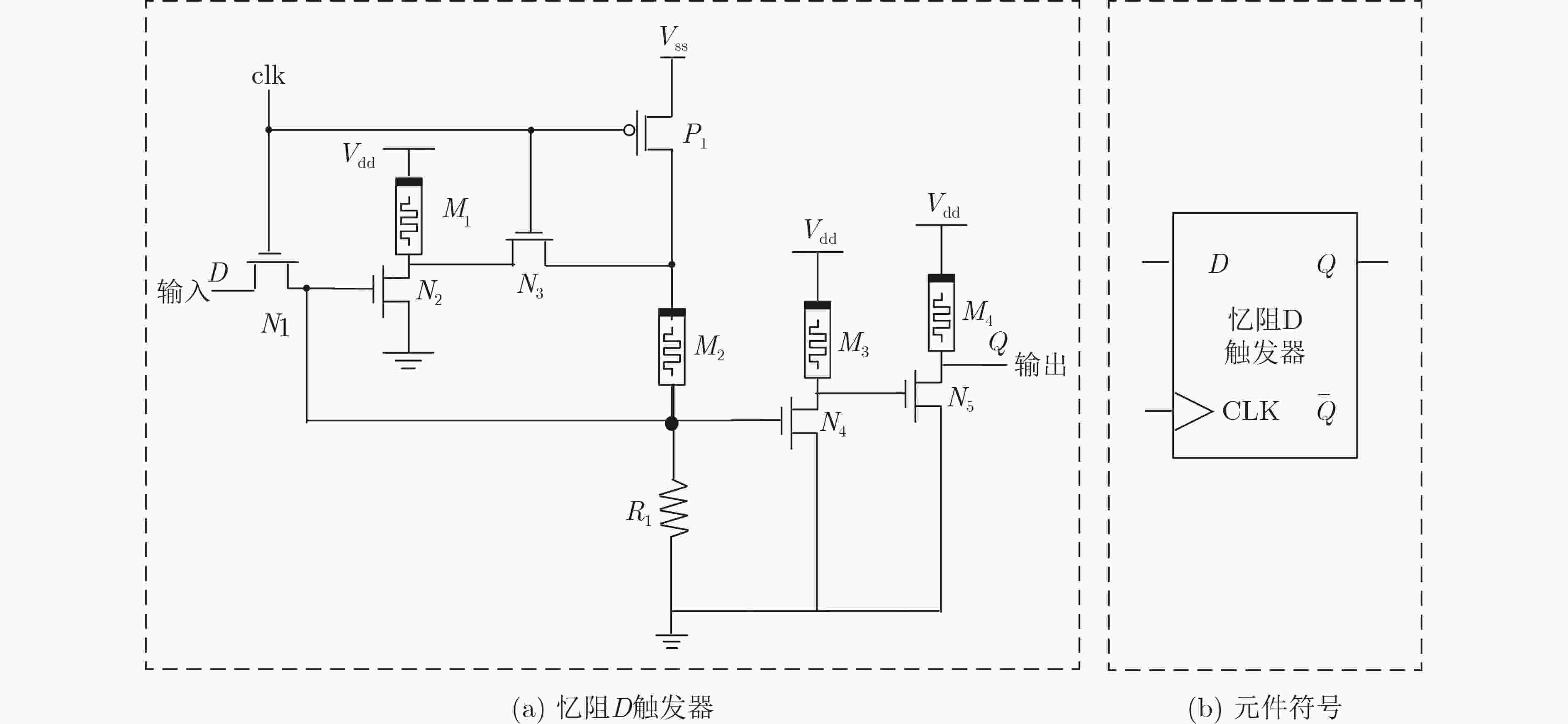

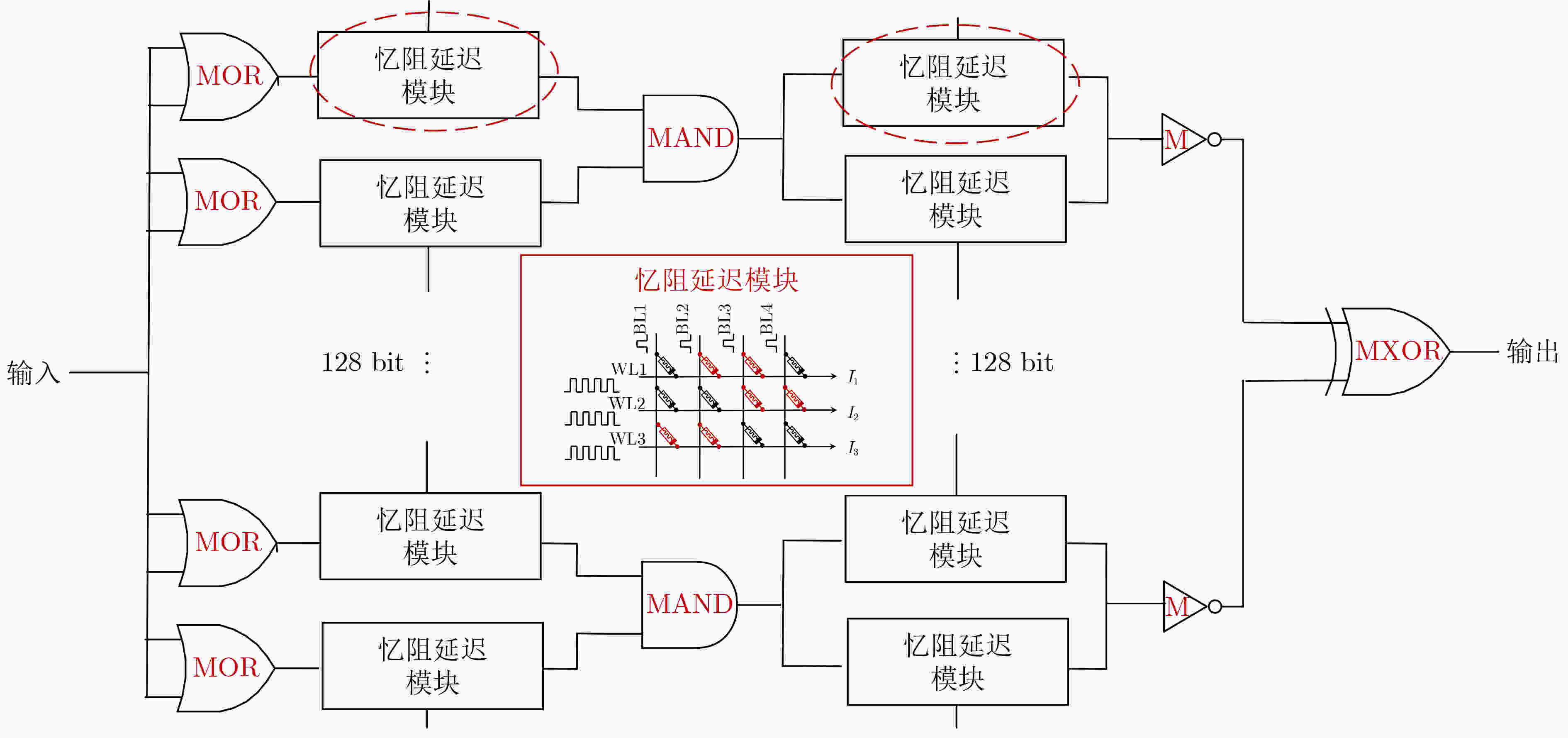

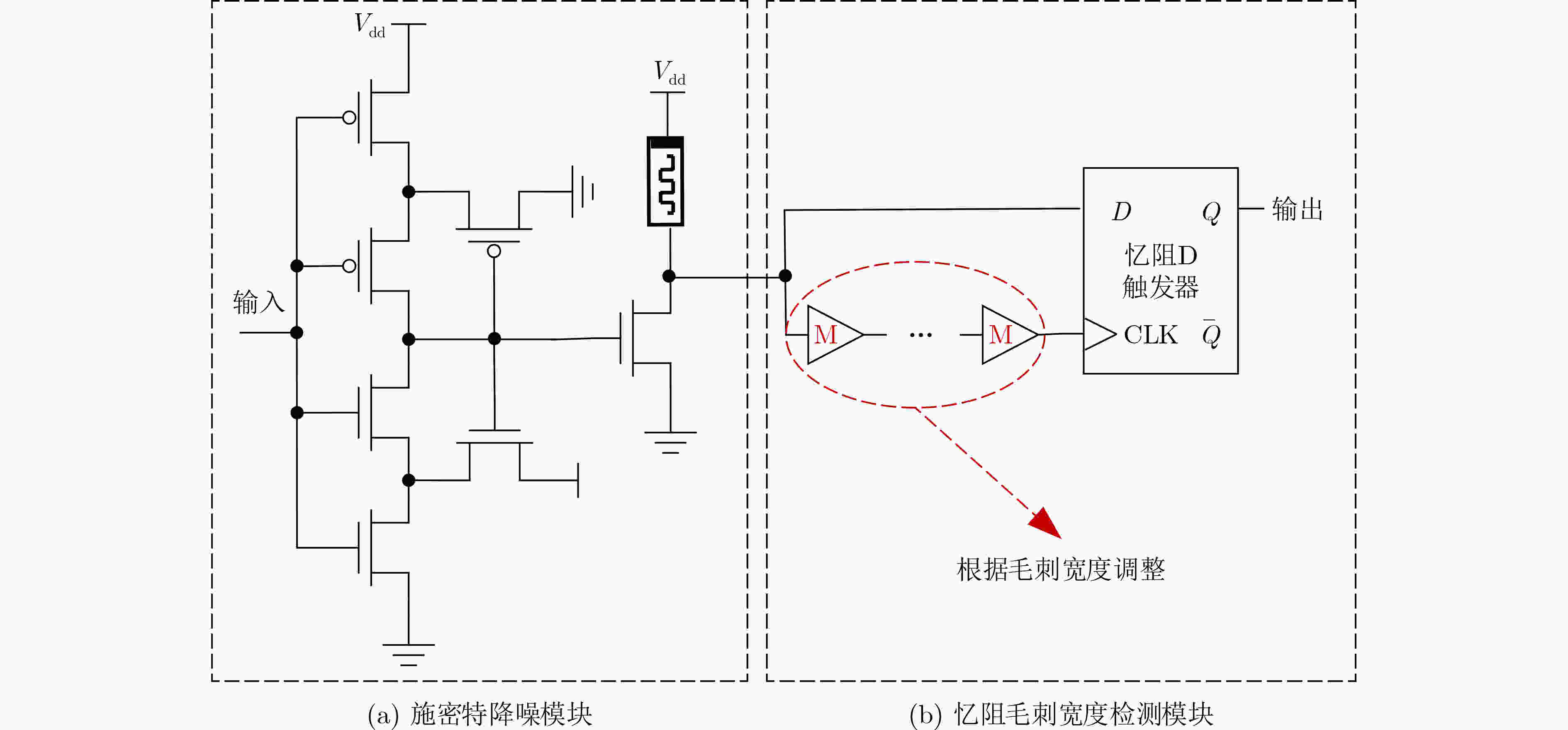

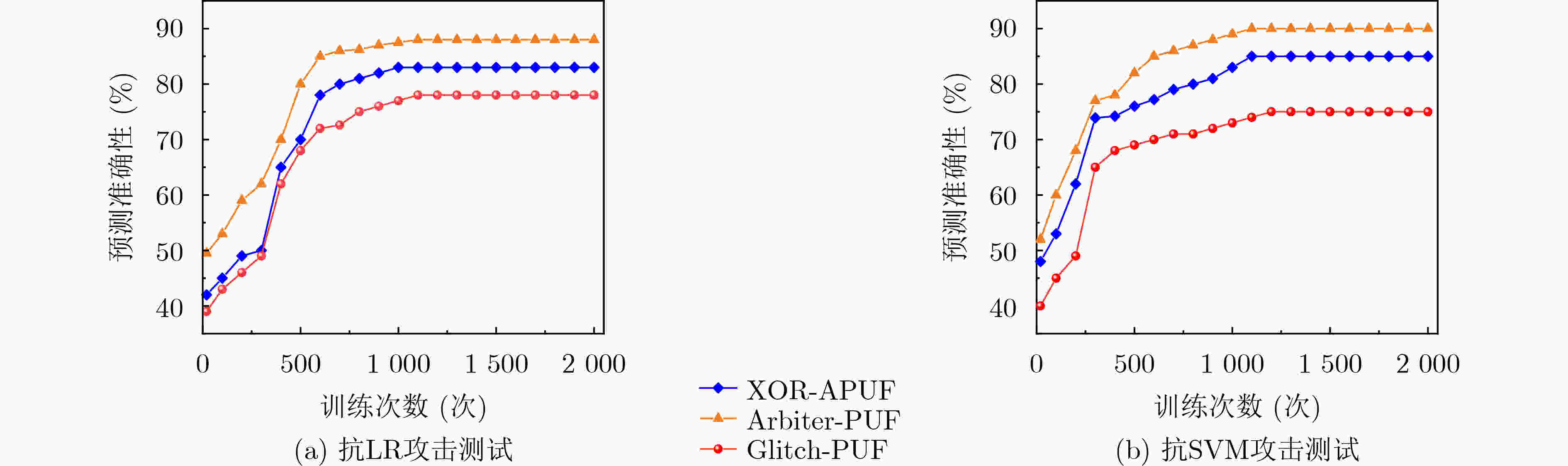

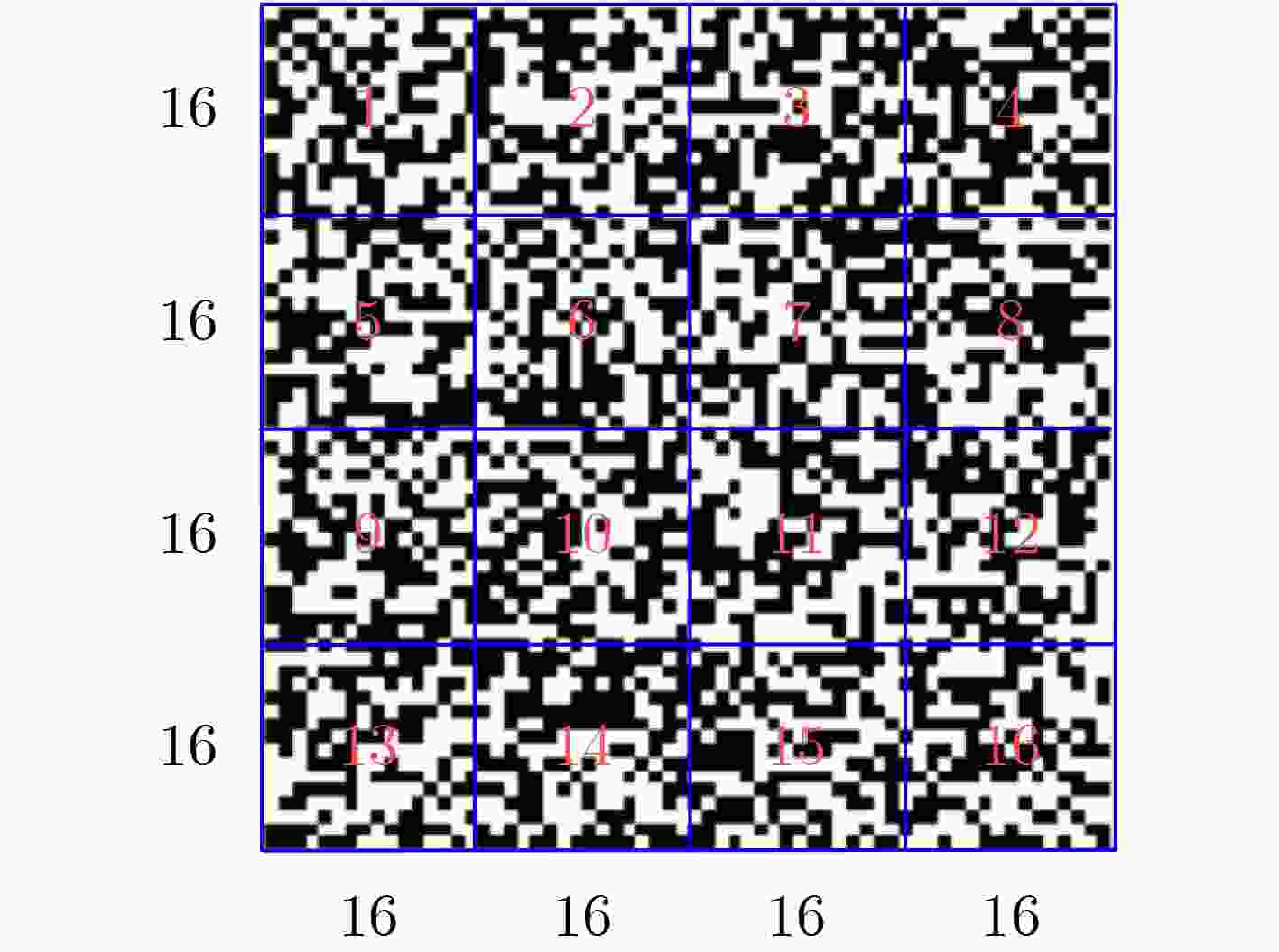

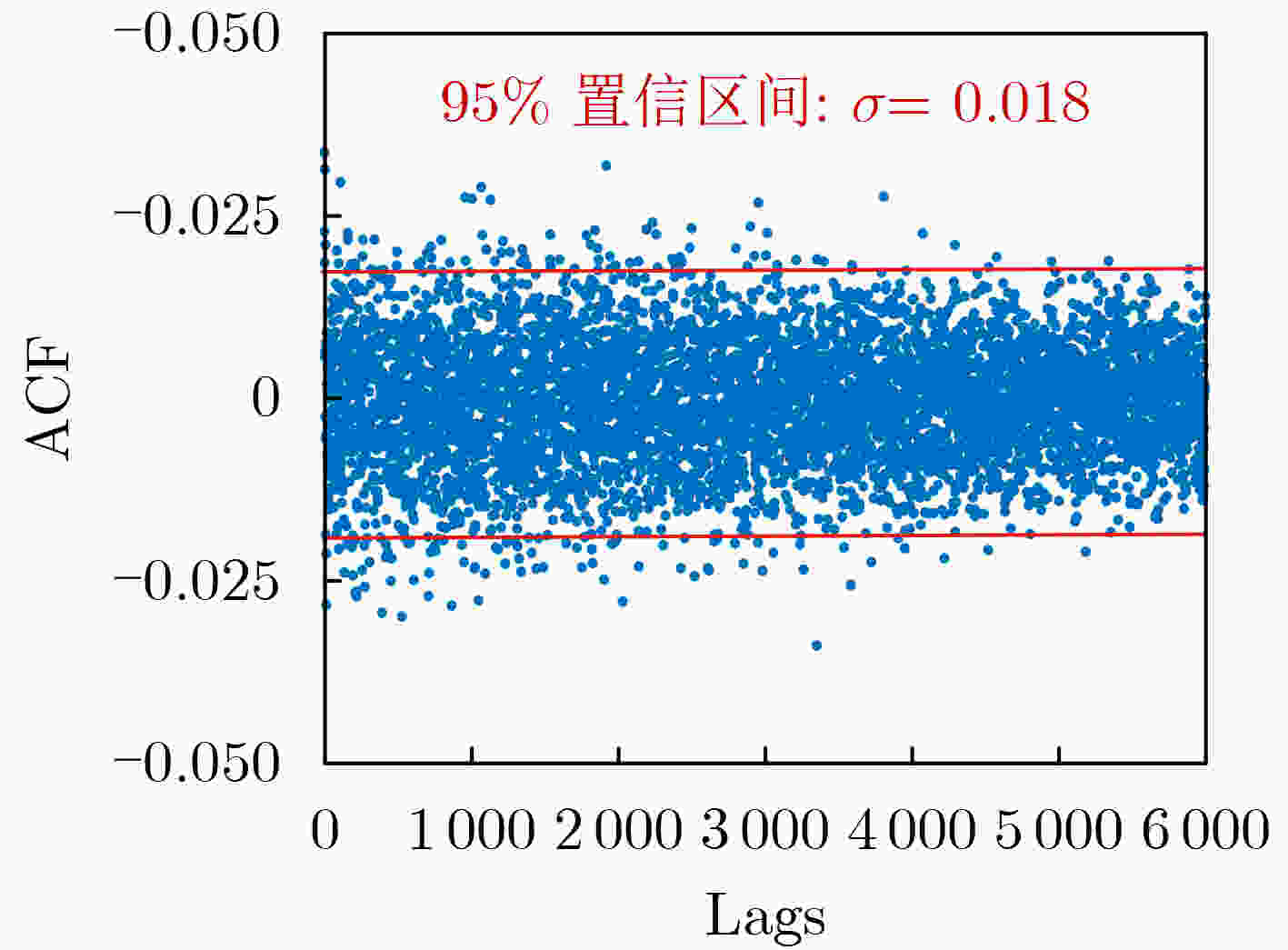

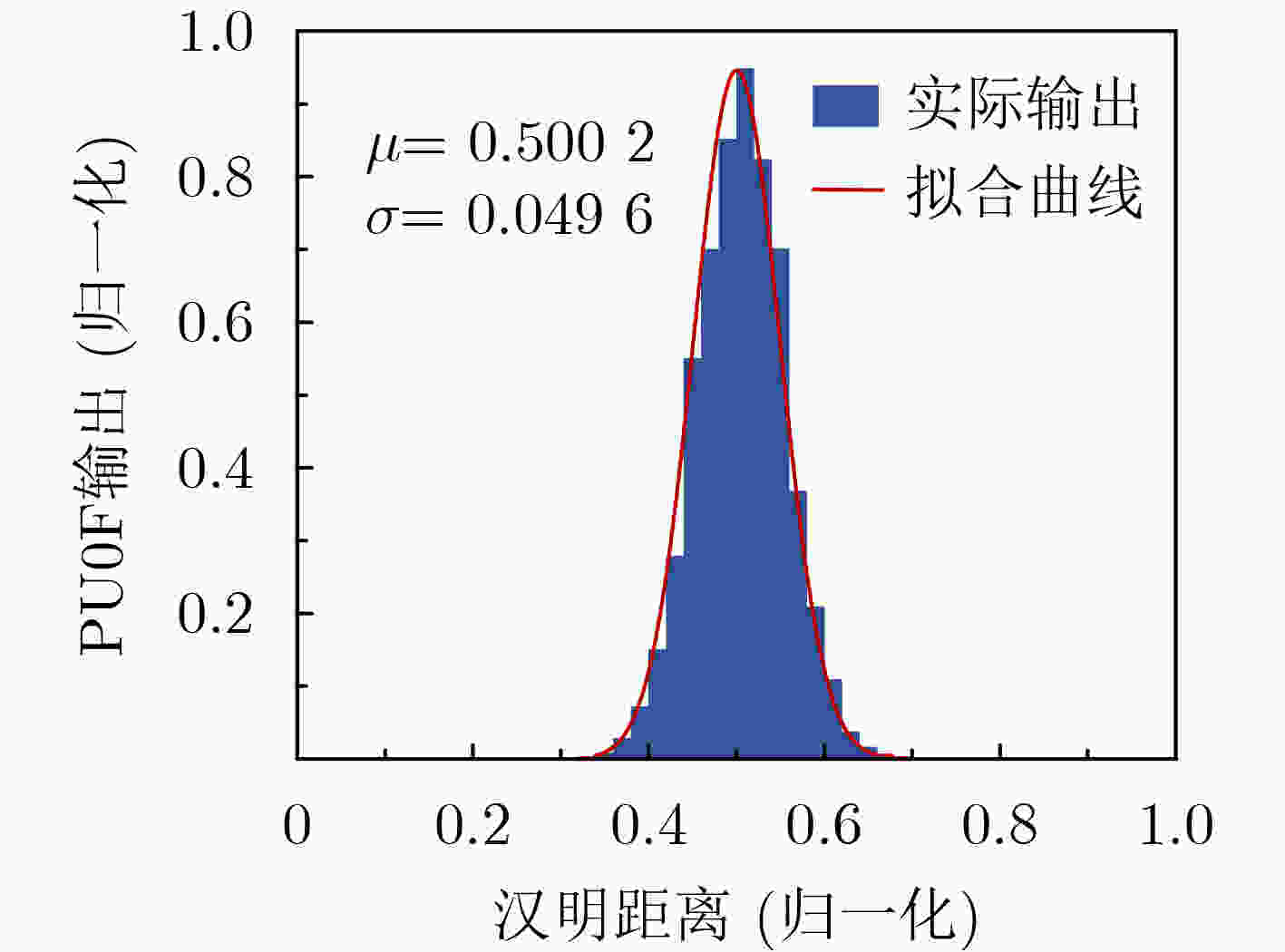

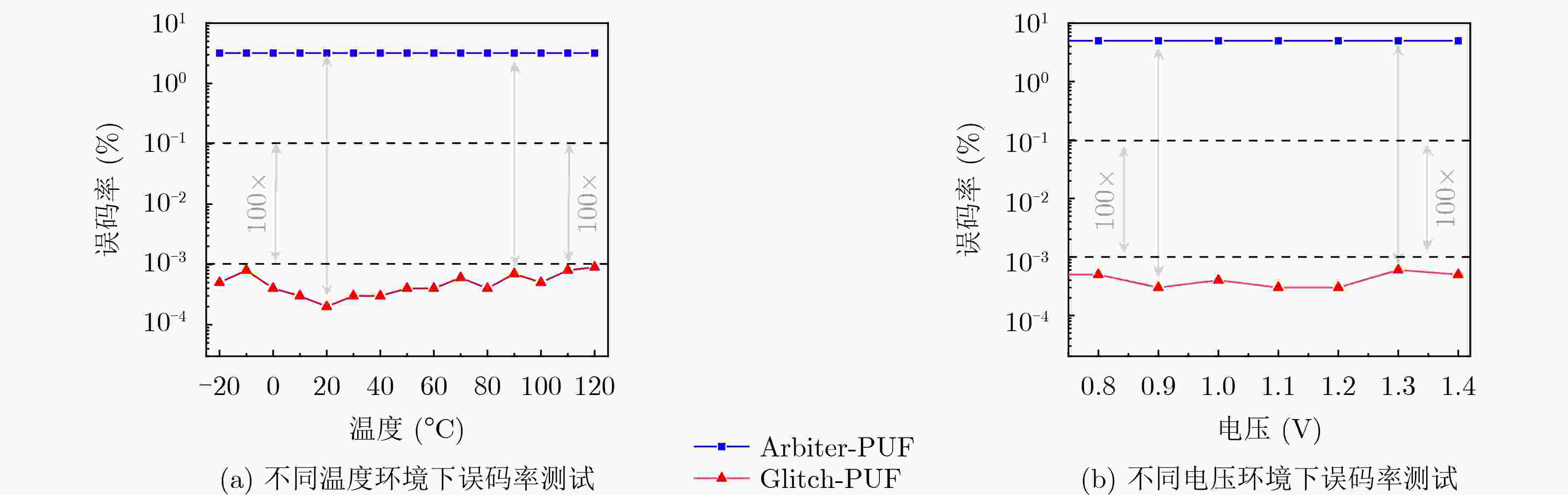

摘要: 物理不可克隆函数(PUF)作为硬件安全原语,广泛应用于众多领域。针对传统硅基类PUF电路可靠性差和易受建模攻击等问题,该文提出一种基于忆阻器的“毛刺”型物理不可克隆函数电路(Glitch-PUF)。该方案首先利用忆阻器的非易失性和阻变效应,实现二值逻辑完备集;然后,利用完备集和竞争冒险现象设计忆阻毛刺产生模块,通过选通信号控制流经忆阻交叉阵列路径的延时大小,改变“毛刺”宽度获得稳定“毛刺”输出;最后,利用忆阻器的存算一体特性和施密特回滞效应设计忆阻采样模块,并测试Glitch-PUF性能。实验结果表明,所设计的Glitch-PUF电路相比文献,抗攻击性提高4.9%~14.3%,随机性达到98.2%,误码率(BER)为0.08%,具有优异的鲁棒性和稳定性。Abstract: Physical Unclonable Functions(PUF) are widely used in various fields as hardware security primitives. Considering the problems of vulnerability to modeling attacks and low stability of traditional CMOS-based PUF, a memristive Glitch-PUF circuit is proposed in this paper. The non-volatility and resistive effect of memristor are used to achieve the complete set of binary logic circuit. Then, the glitch generation circuit is designed based on the logic complete sets and competition and risk taking phenomenon, the stable glitch is obtained by varying the delay time, which is controlled by the path of the current flowing through crossbar array. Finally, the sampling circuit is designed according to the computing in memory characteristics of the memristor and Schmidt hysteresis effect, and the Glitch-PUF is verified. The experimental results show that the anti-modeling attack of designed Glitch-PUF is improved about 4.9%~14.3%, the randomness reaches 98.2%, and the Bit Error Rate(BER) is 0.08%, showing excellent robustness and stability.

-

Key words:

- Physical Unclonable Functions(PUF) /

- Memristor /

- Hardware security /

- Stability

-

算法1 忆阻器伪代码程序描述 (1)RON=100 ROFF=5 000 VON=0.8 VOFF=0.8 L0=3e-9 Eh=0.6 XT=0.4e-9 (2)f=1e13 I0=1e13 WCF=5e-9 weff=0.5e-9 Rth= 5e5 Ei=1.45 T0=300 (3)alpha=0.75e-9 TAU=0.000 1 k=1.380 649e-23 e=1.6e–19 w=0.5e-9 (3)Kb=8.617 33e–5 pi = 3.141 592 6 a=0.25e-9 Ea=0.489 9 rou=1.9e-5 (4)G(v)=V/RON+(1–V)/ROFF (5)Temp=T0+abs(Itb×Vtb×Rth) (6)dx=–a×f×exp(–(Ea-Vg×alpha×2/x)/(Kb×Temp)) (7)dw=(weff+pow(weff,2)/(2×w))×f×exp(–(Ea–Vtb×alpha×2/L0)/(Kb×Temp)) (8)I1=I0×pi×(WCF×WCF/4-w×w/4)×exp(–L0/XT)×sinh(Vtb/VT) (9)RCF=rou×(L0-x)/(pi×w×w/4) (10)Vg=Vtb–(Itb–I1)×RCF (11)dx/dt =(1/TAU)×((1/(1+exp(–1/(T×k/e)×(Vtb–Von))))×(1–Vtb)–(1–(1/(1+exp(–1/(T×k/e)×(Vtb+Voff)))))×V2 (12)IVRel(V1,V2)=V1×G(V2) 表 1 NIST测试

测试项目 长度(bit) 测试次数(次) 通过率(%) P值 测试通过 单比特频数 6400 10 100 0.589 是 块内频数 6400 10 90 0.436 是 累加和 6400 10 100 0.825 是 近似熵 6400 10 100 0.371 是 游程 6400 10 100 0.328 是 最大游程 6400 10 100 0.682 是 离散傅里叶变换 6400 10 100 0.737 是 序列 6400 10 100 0.253 是 通用统计 6400 10 100 0.375 是 二进制矩阵秩 6400 10 100 0.411 是 表 2 与相关文献的比较结果

比较文献 工艺(nm) NIST测试 电压(V) 温度(℃) 汉明距离(归一化) 误码率(%) VLSI[15] 130 – 1.08~1.3 –20~80 0.499 9 9.000 ISSCC[16] 65 PASS 0.7~1.0 25~85 0.501 4 1.730 IEDM[17] – PASS 0.8~1.2 25~85 0.499 5 11.500 VLSI[18] 200 – 1.0~1.3 25~100 0.500 1 5.300 ISSCC[19] 130 PASS 0.9~1.8 25~125 0.498 9 1.730 TCASI[20] 65 PASS 0.5~1.0 –10~80 0.494 7 3.000 JSSC[21] 180 PASS 0.4~1.8 10~80 0.493 0 0.130 本文 65 PASS 0.8~1.4 –20~120 0.500 2 0.008 -

[1] GENKIN D, PIPMAN I, and TROMER E. Get your hands off my laptop: Physical side-channel key-extraction attacks on PCs[J]. Journal of Cryptographic Engineering, 2015, 5(2): 95–112. doi: 10.1007/s13389-015-0100-7 [2] WANG Xiaoxiao and TEHRANIPOOR M. Novel physical unclonable function with process and environmental variations[C]. 2010 Design, Automation & Test in Europe Conference & Exhibition, Dresden, Germany, 2010: 1065–1070. [3] ZHAO Qiang, WU Yiheng, ZHAO Xiao, et al. A 1036-F2/bit high reliability temperature compensated cross-coupled comparator-based PUF[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2020, 28(6): 1449–1460. doi: 10.1109/TVLSI.2020.2980306 [4] HE Zhangqing, WAN Meilin, DENG Jie, et al. A reliable strong PUF based on switched-capacitor circuit[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018, 26(6): 1073–1083. doi: 10.1109/TVLSI.2018.2806041 [5] GOVINDARAJ R, GHOSH S, and KATKOORI S. Design, analysis and application of embedded resistive RAM based strong arbiter PUF[J]. IEEE Transactions on Dependable and Secure Computing, 2020, 17(6): 1232–1242. doi: 10.1109/TDSC.2018.2866425 [6] AVVARU S V S, ZENG Ziqing, and PARHI K K. Homogeneous and heterogeneous feed-forward XOR physical unclonable functions[J]. IEEE Transactions on Information Forensics and Security, 2020, 15: 2485–2498. doi: 10.1109/TIFS.2020.2968113 [7] MANDRY H, HERKLE A, MÜELICH S, et al. Normalization and multi-valued symbol extraction from RO-PUFs for enhanced uniform probability distribution[J]. IEEE Transactions on Circuits and Systems II:Express Briefs, 2020, 67(12): 3372–3376. doi: 10.1109/TCSII.2020.2980748 [8] YE Jing, GUO Qingli, HU Yu, et al. Modeling attacks on strong physical unclonable functions strengthened by random number and weak PUF[C]. 2018 IEEE 36th VLSI Test Symposium (VTS), San Francisco, USA, 2018: 1–6, [9] 张跃军, 汪鹏君, 李刚, 等. 基于信号传输理论的Glitch物理不可克隆函数电路设计[J]. 电子与信息学报, 2016, 38(9): 2391–2396. doi: 10.11999/JEIT151312ZHANG Yuejun, WANG Pengjun, LI Gang, et al. Design of glitch physical unclonable functions circuit based on signal transmission theory[J]. Journal of Electronics &Information Technology, 2016, 38(9): 2391–2396. doi: 10.11999/JEIT151312 [10] NOZAKI Y, TAKEMOTO S, IKEZAKI Y, et al. Performance evaluation of unrolled cipher based Glitch PUF implemented on Virtex-7[C]. 2021 International Symposium on Devices, Circuits and Systems (ISDCS), Higashihiroshima, Japan, 2021: 1–4. [11] NI Li, WANG Pengjun, ZHANG Yuejun, et al. A reliable multi-information entropy Glitch PUF using schmitt trigger sampling method for IoT security[C]. 2021 IEEE 14th International Conference on ASIC (ASICON), Kunming, China, 2021: 1–4. [12] 董永兴, 徐金甫, 李军伟. 基于延时控制的Glitch PUF电路设计[J]. 计算机应用与软件, 2020, 37(11): 311–315,333. doi: 10.3969/j.issn.1000-386x.2020.11.050DONG Yongxing, XU Jinfu, and LI Junwei. Design of Glitch PUF based on delay control[J]. Computer Applications and Software, 2020, 37(11): 311–315,333. doi: 10.3969/j.issn.1000-386x.2020.11.050 [13] 张章, 李超, 韩婷婷, 等. 基于忆阻器的感存算一体技术综述[J]. 电子与信息学报, 2021, 43(6): 1498–1509. doi: 10.11999/JEIT201102ZHANG Zhang, LI Chao, HAN Tingting, et al. Review of the fused technology of sensing, storage and computing based on memristor[J]. Journal of Electronics &Information Technology, 2021, 43(6): 1498–1509. doi: 10.11999/JEIT201102 [14] NI Li, WANG Penjun, ZHANG Yuejun, et al. An ACF<0.03 low-power software PUF based on the RISC-V processor for IoT security[J]. Microelectronics Journal, 2022, 121: 105362. doi: 10.1016/j.mejo.2022.105362 [15] XI Xiaodan, ZHUANG Haoyu, SUN Nan, et al. Strong subthreshold current array PUF with 265 challenge-response pairs resilient to machine learning attacks in 130nm CMOS[C]. 2017 Symposium on VLSI Circuits, Kyoto, Japan, 2017: C268–C269. [16] ALVAREZ A, ZHAO Wenfeng, and ALIOTO M. 15fJ/b static physically unclonable functions for secure chip identification with <2% native bit instability and 140× Inter/Intra PUF hamming distance separation in 65nm[C]. 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, San Francisco, USA, 2015: 1–3. [17] MAHMOODI M R, NILI H, FAHIMI Z, et al. Ultra-low power physical unclonable function with nonlinear fixed-resistance crossbar circuits[C]. 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, USA, 2019: 30.1. 1–30.1. 4. [18] MAHMOODI M R, NILI H, and STRUKOV D B. RX-PUF: Low power, dense, reliable, and resilient physically unclonable functions based on analog passive RRAM crossbar arrays[C]. 2018 IEEE Symposium on VLSI Technology, Honolulu, USA, 2018: 99–100. [19] YANG Kaiyuan, DONG Qing, BLAAUW D, et al. A 553F2 2-transistor amplifier-based physically unclonable function (PUF) with 1.67% native instability[C]. 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA, 2017: 146–147. [20] LU Lu, YOO T, and KIM T T H. A 6T SRAM based two-dimensional configurable challenge-response PUF for portable devices[J]. IEEE Transactions on Circuits and Systems I:Regular Papers, 2022, 69(6): 2542–2552. doi: 10.1109/TCSI.2022.3156983 [21] VATALARO M, DE ROSE R, LANUZZA M, et al. Static CMOS physically unclonable function based on 4T voltage divider with 0.6%–1.5% bit instability at 0.4–1.8V operation in 180 nm[J]. IEEE Journal of Solid-State Circuits, 2022, 57(8): 2509–2520. doi: 10.1109/JSSC.2022.3151229 -

下载:

下载:

下载:

下载: