Design of Novel Dynamic March Algorithm Based on Memory Built-in Self-test

-

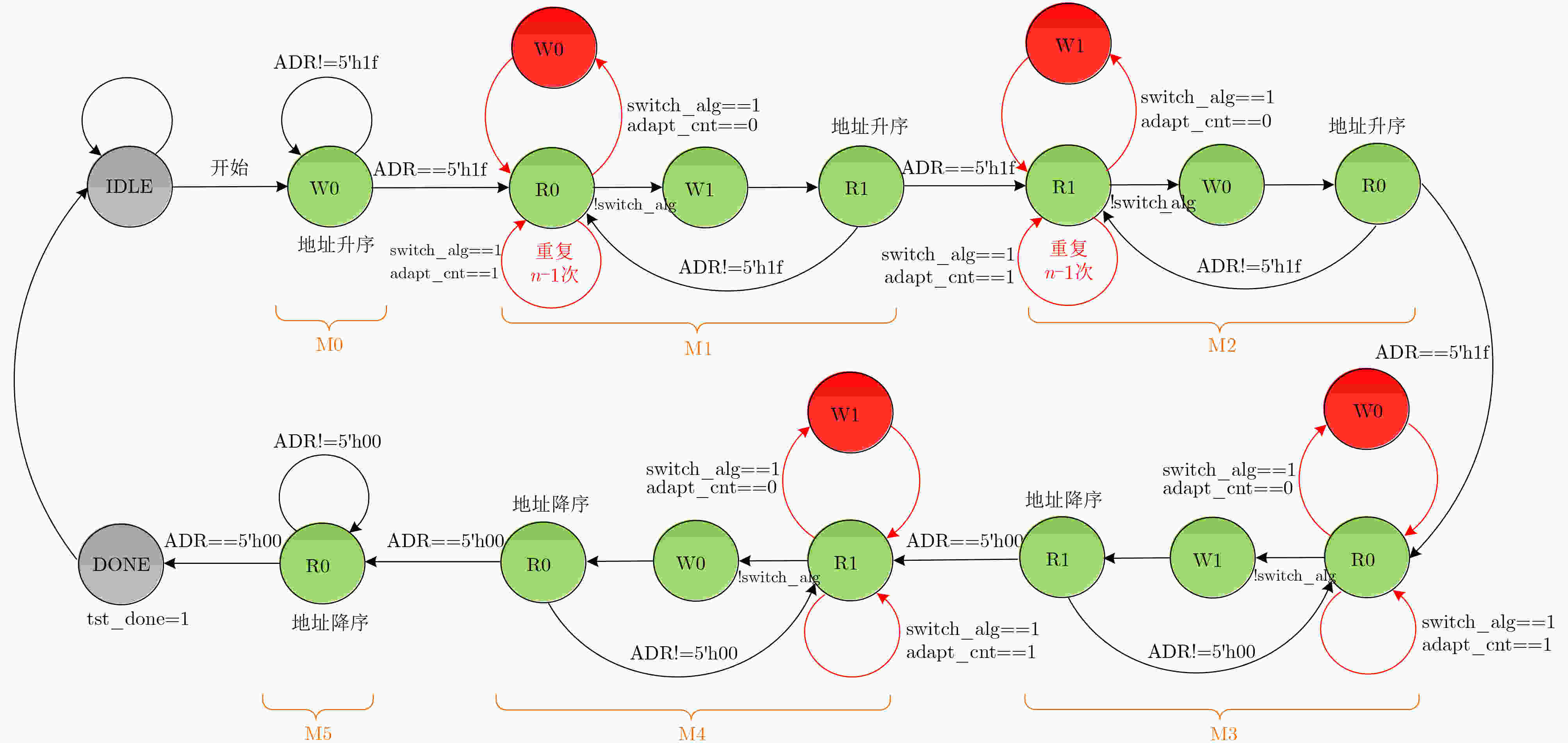

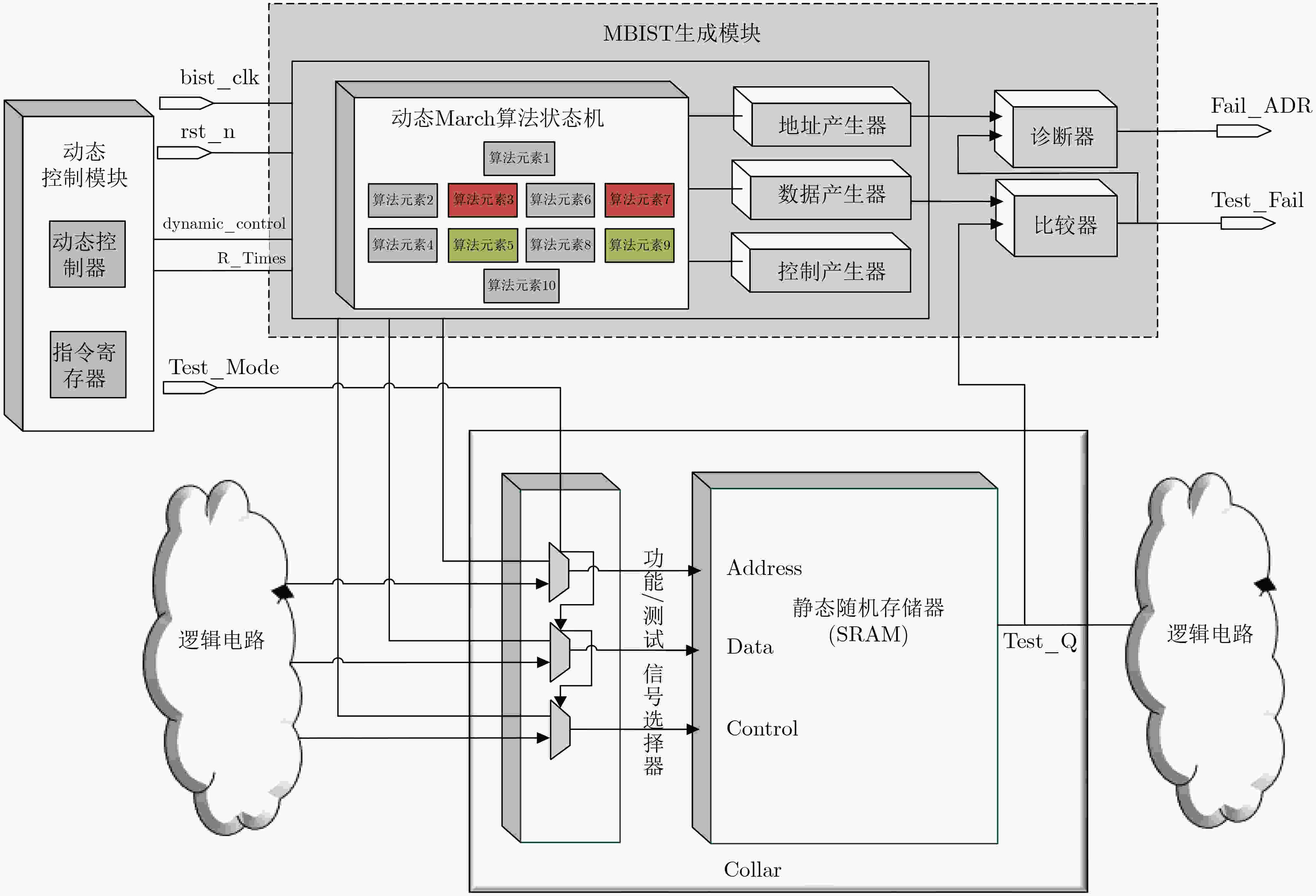

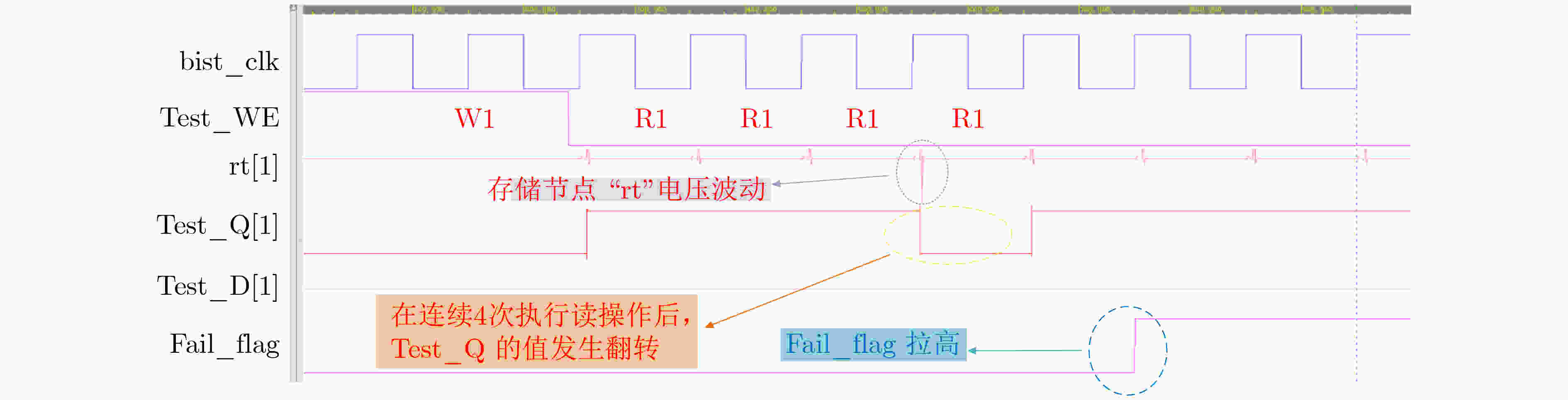

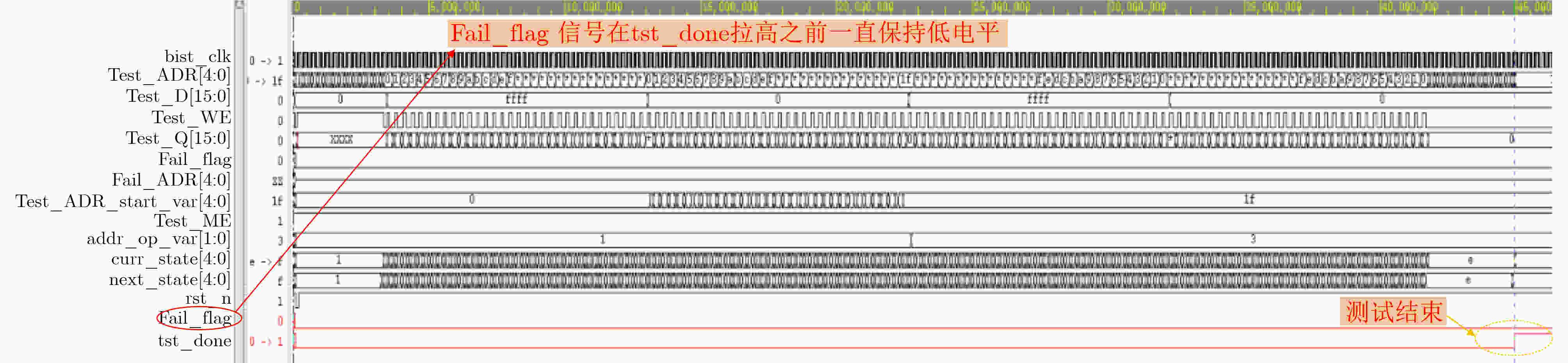

摘要: 存储器作为片上系统(SoC)中最大和最重要的模块之一,它的稳定性和可靠性关乎着整个芯片能否正常工作。为了提高存储器的测试效率,该文提出一种新型动态March算法——Dynamic-RAWC。相比经典的March RAW算法,Dynamic-RAWC算法有着更良好的故障检测效果:动态故障覆盖率提高了31.3%。这个可观的效果得益于所提算法以经典的March RAW算法为基础进行优化,融入了Hammer, March C+算法的测试元素和一些新的测试元素。不同于普通March型算法的固定元素,所提算法支持用户自定义算法的执行顺序以适应不同的故障检测需求,能够动态地控制算法元素,在时间复杂度和故障覆盖率之间进行调整从而达到良好的平衡。Abstract: As the largest module and one of the most important modules in the System on Chip (SoC), the stability and reliability of memory are related to whether the whole chip can work normally. In order to improve the test efficiency of memory, a novel Dynamic March algorithm—Dynamic-RAWC is proposed. The fault detection effect of the Dynamic-RAWC algorithm is better than that of the classic March RAW algorithm: the dynamic fault coverage is increased by 31.3%. This considerable effect is due to the fact that the test elements of Hammer, March C+ algorithm and some new test elements are integrated into the proposed algorithm which is optimized based on the classic March RAW algorithm. In contrast to ordinary March-type algorithms which have fixed elements, the proposed algorithm supports the user to customize the execution order of the algorithm to meet the detection needs of different faults model, and can dynamically switch the algorithm elements, adjusting between the time complexity and the fault coverage to achieve a good balance.

-

Key words:

- Memory Built-In Self-Test (MBIST) /

- March algorithm /

- Dynamic fault /

- Fault coverage

-

表 1 静态/动态故障原语

静态故障 静态故障原语 动态故障 动态故障原语 (x, y, z, t∈0, 1) SAF <0/1/–>,<1/0/–> dRDF <xWyRy/~y/~y>,<xRxRx/~x/~x> TF <0w1/0/–>,<1w0/1/–> dRDFn <xWyRyn/~y/~y>,<xRxRxn/~x/~x> WDF <0w0/↑/–>,<1w1/↓/–> dIRF <xWyRy/y/~y>,<xRxRx/x/~x> RDF <r0/↑/1>,<r1/↓/0> dDRDF <xWyRy/~y/y>,<xRxRx/~x/x> DRDF <r0/↑/0>,<r1/↓/1> dTF <xWyW(~y)/y/–>,<xRxW(-x)/x/–> IRF <r0/0/1>,<r1/1/0> dWDF <xWyWy/~y/–>,<xRxWx/~x/–> CFst <0;0/1/–>,<0;1/0/–>,<1;0/1/–>,<1;1/0/–> dCFdswr <xWyRy;z/~z/–> CFdsrx <r0;0/↑/–>,<r0;1/↓/–>,<r1;0/↑/–>,<r1;1/↓/–> dCFdsww <xWyWt;z/~z/–> CFdsxw!x <0w1;0/↑/–>,<0w1;1/↓/–>,<1w0;0/↑/–>,<1w0;1/↓/–> dCFdsrw <xRxWy;z/~z/–> CFsxwx <0w0;0/↑/–>,<0w0;1/↓/–>,<1w1;0/↑/–>,<1w1;1/↓/–> dCFdsrr <xRxRx;z/~z/–> CFtr <0;0w1/0/–>,<0;1w0/1/–>,<1;0w1/0/–>,<1;1w0/1/–> dCFrd <x;yWzRz/~z/~z>,<x;zRzRz/~z/~z> CFwd <0;0w0/↑/–>,<1;0w0/↑/–>,<0;1w1/↓/–>,<1;1w1/↓/–> dCFir <x;yWzRz/z/~z>,<x;zRzRz/z/~z> CFrd <0;r0/↑/1>,<1;r0/↑/1>,<0;r1/↓/0>,<1;r1/↓/0> dCFdrd <x;yWzRz/~z/z>,<x;zRzRz/~z/z> CFdrd <0;r0/↑/0>,<1;r0/↑/0>,<0;r1/↓/1>,<1;r1/↓/1> dCFtr <x;yWzW(-z)/z/–>,<x;zRzW(-z)/z/–> CFir <0;r0/0/1>,<1;r0/0/1>,<0;r1/1/0>,<1;r1/1/0> dCFwd <x;yWzRz/~z/–>,<x;zRzRz/~z/–> 表 2 常见March算法与动态March算法的优势和局限性分析

测试算法 算法优势 算法局限性 MATS++ 时间复杂度低,能够覆盖SAF故障和RDF故障 算法元素过于单一,故障覆盖率低 March C- 经典的March算法,提升了静态故障覆盖率 覆盖不到WDF, DRDF等静态故障 March C+ March C-算法的改进算法,对静态故障有较为全面的覆盖 对静态双单元耦合故障覆盖不全面 March AB 对静态双单元耦合故障覆盖全面,对动态故障覆盖率较好 对动态双单元耦合故障覆盖率较低 March RAW 静态故障覆盖率高,对动态故障覆盖率较好 对dRDF, dDRDF等动态故障覆盖不全面,算法元素固定 Dynamic-RAWC 动态故障覆盖率有很大提升,测试元素可根据不同需求动态调整,测试效率高 对少数动态故障覆盖不全面,如dCFtr故障 表 3 常见March算法及动态March算法的具体描述与时间复杂度

测试算法 算法描述 时间复杂度 MATS++ {↑↓(w0);↑↓(r0,w1);↑↓(r1,w0,r0)} 6N March C- {↑↓(w0);↑(r0,w1);↑(r1,w0);↓(r0,w1); ↓(r1,w0);↑↓(r0)} 10N March C+ {↑↓(w0);↑(r0,w1,r1);↑(r1,w0,r0);↓(r0,w1,r1); ↓(r1,w0,r0);↑↓(r0)} 14N March AB {↑↓(w1);↓(r1,w0,r0,w0,r0);↓(r0,w1,r1,w1,r1);

↑(r1,w0,r0,w0,r0);↑(r0,w1,r1,w1,r1);↑(r0)}14N March RAW {↑↓(w0);↑(r0,w0,r0,r0,w1,r1);↑(r1,w1,r1,r1,w0,r0);

↓(r0,w0,r0,r0,w1,r1);↓(r1,w1,r1,r1,w0,r0);↑↓(r0)}26N Dynamic-RAWC1 {↑↓(w0);↑(r0,w0,r0n,r0,w1,r1);↑(r1,w1,r1n,r1,w0,r0);

↓(r0,w0,r0,r0,w1,r1);↓(r1,w1,r1,r1,w0,r0);↑↓(r0)}14N/

(24N+2nN),

0<n<10Dynamic-RAWC2 {↑↓(w0);↑(r0,w0,w0,r0n,r0,r0,w0,r0,w1,r1);

↑(r1,w1,w1,r1n,r1,r1,w1,r1,w0,r0);

↓(r0,w0,w0,r0,r0,r0,w0,r0,w1,r1);

↓(r1,w1,w1,r1,r1,r1,w1,r1,w0,r0);↑↓(r0)}14N/

(40N+2nN),

0<n<9表 4 不同March算法的静态故障覆盖率

March算法 MATS++ March C- March C+ March AB March RAW Dynamic-RAWC SF 2/2 2/2 2/2 2/2 2/2 2/2 TF 1/2 2/2 2/2 2/2 2/2 2/2 WDF 0/2 0/2 0/2 2/2 2/2 2/2 RDF 2/2 2/2 2/2 2/2 2/2 2/2 DRDF 0/2 0/2 2/2 2/2 2/2 2/2 IRF 2/2 2/2 2/2 2/2 2/2 2/2 CFst 4/8 8/8 8/8 8/8 8/8 8/8 CFdsrx 3/8 8/8 8/8 8/8 8/8 8/8 CFdsxw!x 3/8 8/8 8/8 8/8 8/8 8/8 CFsxwx 0/8 0/8 0/8 8/8 8/8 8/8 CFtr 2/8 8/8 8/8 8/8 8/8 8/8 CFwd 0/8 0/8 0/8 8/8 8/8 8/8 CFrd 4/8 8/8 8/8 8/8 8/8 8/8 CFdrd 0/8 0/8 8/8 8/8 8/8 8/8 CFir 4/8 8/8 8/8 8/8 8/8 8/8 总计 27/84 56/84 66/84 84/84 84/84 84/84 故障覆盖率(%) 32.14 66.67 78.57 100 100 100 表 5 不同March算法的动态故障覆盖率

故障模型 March算法 MATS++ March C- March C+ March AB March RAW Dynamic-RAWC dRDF 0/6 0/6 2/6 4/6 6/6 6/6 dRDFn(1<n≤10) 0/6n 0/6n 0/6n 0/6n 0/6n 6n/6n dIRF 0/6 0/6 2/6 4/6 6/6 6/6 dDRDF 0/6 0/6 2/6 4/6 4/6 6/6 dTF 1/6 2/6 2/6 2/6 2/6 2/6 dWDF 0/6 0/6 2/6 2/6 2/6 4/6 dCFdswr 0/16 0/16 8/16 16/16 16/16 16/16 dCFdsww 0/32 0/32 0/32 0/32 0/32 8/32 dCFdsrw 3/16 8/16 8/16 16/16 16/16 16/16 dCFdsrr 0/8 0/8 0/8 0/8 8/8 8/8 dCFrd 0/24 0/24 8/24 16/24 24/24 24/24 dCFir 0/24 0/24 8/24 16/24 24/24 24/24 dCFdrd 0/24 0/24 8/24 16/24 16/24 24/24 dCFtr 2/24 8/24 8/24 8/24 8/24 8/24 dCFwd 0/24 0/24 0/24 8/24 8/24 16/24 总计 6/282 18/282 58/282 112/282 140/282 228/282 故障覆盖率(%) 2.1 6.4 20.6 39.7 49.6 80.9 表 6 不同MBIST电路的面积统计(μm2)

BIST电路 面积 总计 March C+ 194.95 543.48 March RAW 225.86 Hammer 122.67 Dynamic-RAWC 228.45 228.45 表 7 基于FPGA不同测试算法对3种规格存储器的测试时间统计

测试算法 存储器规格 测试时间(μs) MATS++ 1k×16位 245.76 32k×8位 7864.32 256k×16位 62914.56 March C- 1k×16位 409.6 32k×8位 13107.2 256k×16位 10485.6 March C+ 1k×16位 573.44 32k×8位 18350.08 256k×16位 146800.64 March AB 1k×16位 901.12 32k×8位 28835.84 256k×16位 230686.72 March RAW 1k×16位 1064.96 32k×8位 34078.72 256k×16位 272629.76 Dynamic-RAWC 1k×16位 573.44~1720.32 32k×8位 18350.08~5050.24 256k×16位 146800.64~440404.92 -

[1] DU Xiaogang, REDDY S M, CHENG W T, et al. At-speed built-in self-repair analyzer for embedded word-oriented memories[C]. The 17th International Conference on VLSI Design, Mumbai, India, 2004: 895–900. [2] CHENG W T, HILL C J, and KEBICHI O. Full-speed BIST controller for testing embedded synchronous memories[P]. USA Patent, 6829728, 2004. [3] ALNATHEER S and AHMED M A. Optimal method for test and repair memories using redundancy mechanism for SoC[J]. Micromachines, 2021, 12(7): 811. doi: 10.3390/mi12070811 [4] MADDELA V, SINHA S K, PARVATHI M, et al. Fault detection and analysis in embedded SRAM for sub nanometer technology[C]. 2022 International Conference on Applied Artificial Intelligence and Computing (ICAAIC), Salem, India, 2022: 1784–1788. [5] WOJCIECHOWSKI A A, MARCINEK K, and PLESKACZ W A. Configurable MBIST processor for embedded memories testing[C]. 2019 MIXDES-26th International Conference "Mixed Design of Integrated Circuits and Systems", Rzeszow, Poland, 2019: 341–344. [6] BAO Chong and ZHANG Shancong. Algorithm-based fault tolerance for discrete wavelet transform implemented on GPUs[J]. Journal of Systems Architecture, 2020, 108: 101823. doi: 10.1016/j.sysarc.2020.101823 [7] HANTOS G, FLYNN D, and DESMULLIEZ M P Y. Built-in self-test (BIST) methods for MEMS: A review[J]. Micromachines, 2020, 12(1): 40. doi: 10.3390/mi12010040 [8] JIDIN A Z, HUSSIN R, FOOK L W, et al. An automation program for march algorithm fault detection analysis[C]. 2021 IEEE Asia Pacific Conference on Circuit and Systems (APCCAS), Penang, Malaysia, 2021: 149–152. [9] AHMED M A and ABUAGOUB A M. MBIST controller based on March-ee algorithm[J]. Journal of Circuits, Systems and Computers, 2021, 30(9): 2150160. doi: 10.1142/S0218126621501607 [10] 庞理. 基于冗余共享的嵌入式SRAM的内建自测试修复及失效分析[D]. [硕士论文], 西安电子科技大学, 2015.PANG Li. Embedded SRAM build-in-self test and repair for failure analysis based on redundancy shared[D]. [Master dissertation], Xidian University, 2015. [11] BENSO A, BOSIO A, DI CARLO S, et al. Automatic March tests generation for static and dynamic faults in SRAMs[C]. European Test Symposium (ETS'05), Tallinn, Estonia, 2005: 122–127. [12] AL-HARBI S M, NOOR F, and AL-TURJMAN F M. March DSS: A new diagnostic march test for all memory simple static faults[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2007, 26(9): 1713–1720. doi: 10.1109/TCAD.2007.895609 [13] BORRI S, HAGE-HASSAN M, GIRARD P, et al. Defect-oriented dynamic fault models for embedded-SRAMs[C]. The 8th IEEE European Test Workshop, 2003. Proceedings, Maastricht, Netherlands, 2003: 23–28. [14] HAMDIOUI S, AL-ARS Z, and VAN DE GOOR A J. Testing static and dynamic faults in random access memories[C]. The 20th IEEE VLSI Test Symposium (VTS 2002), Monterey, USA, 2002: 395–400. [15] JIDIN A Z, HUSSIN R, MISPAN M S, et al. Novel march test algorithm optimization strategy for improving unlinked faults detection[C]. 2021 IEEE Asia Pacific Conference on Circuit and Systems (APCCAS), Penang, Malaysia, 2021: 117–120. -

下载:

下载:

下载:

下载: