Design of Quaternary Logic Current Mode CMOS Add-subtract Circuit Based on Comparator

-

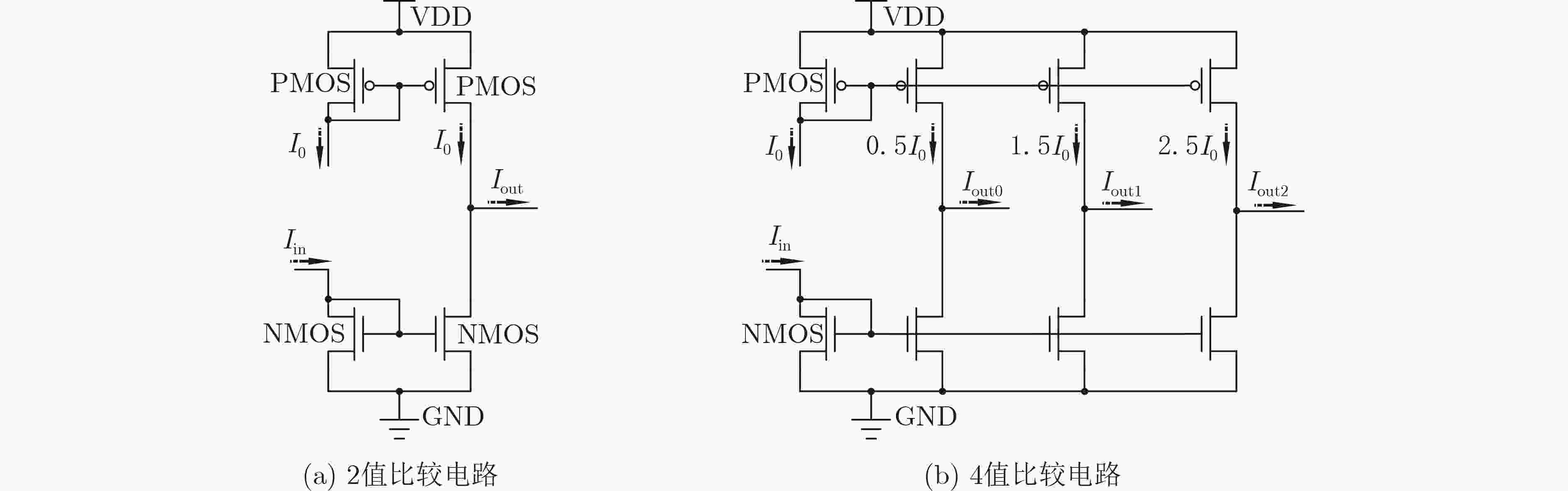

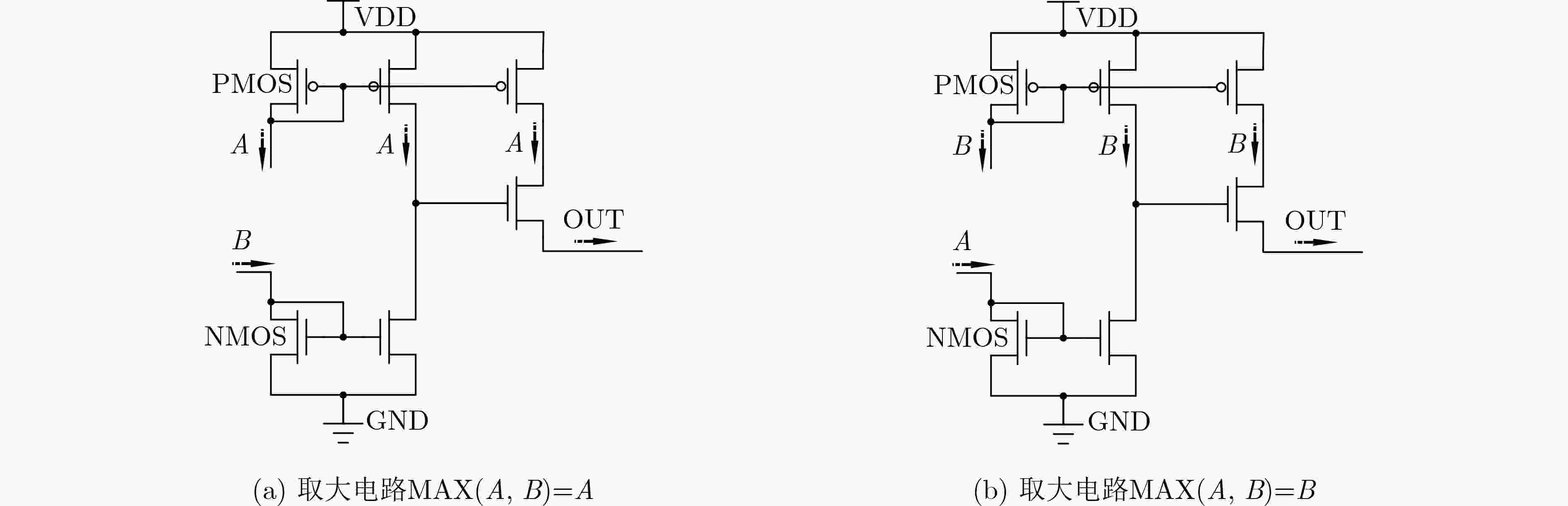

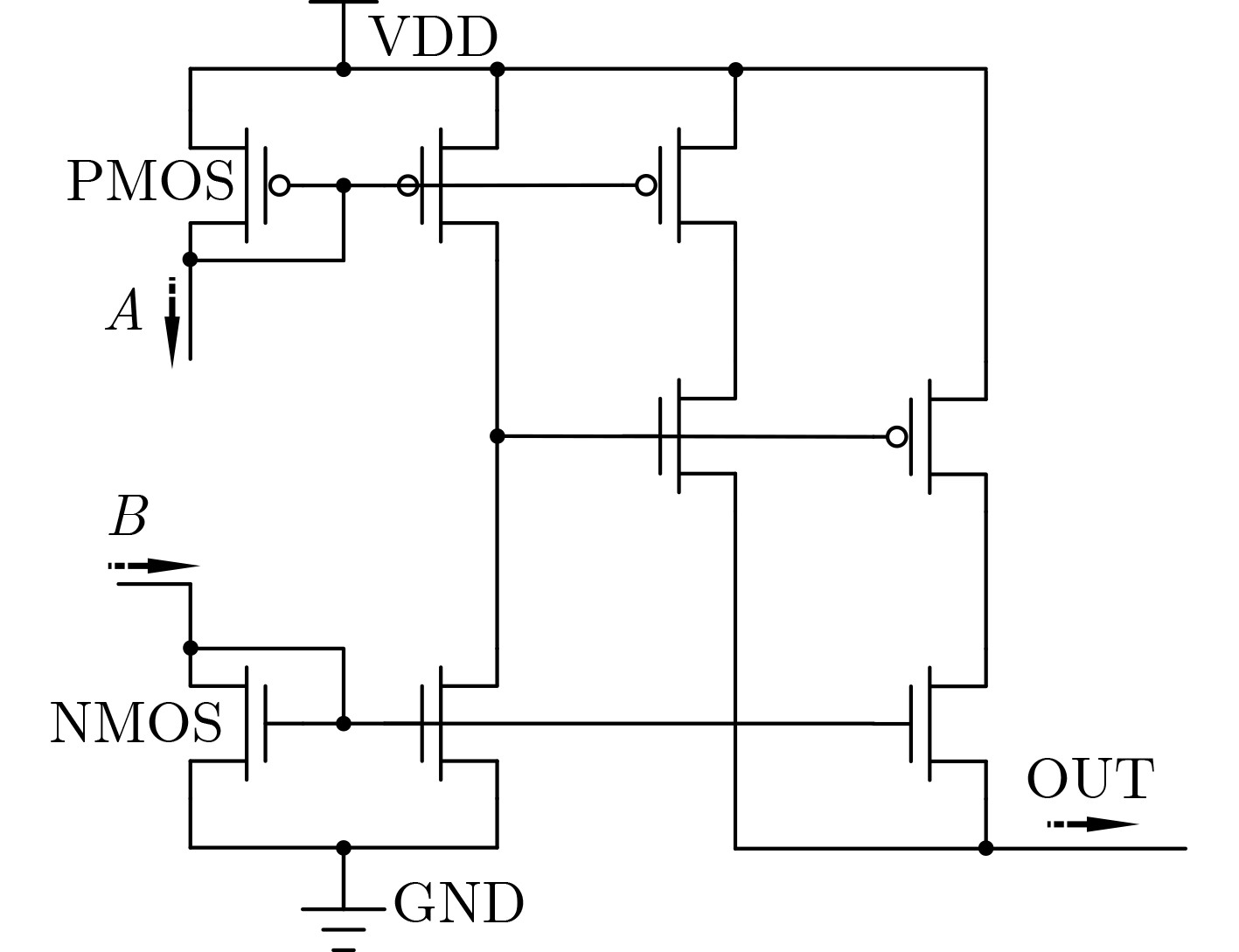

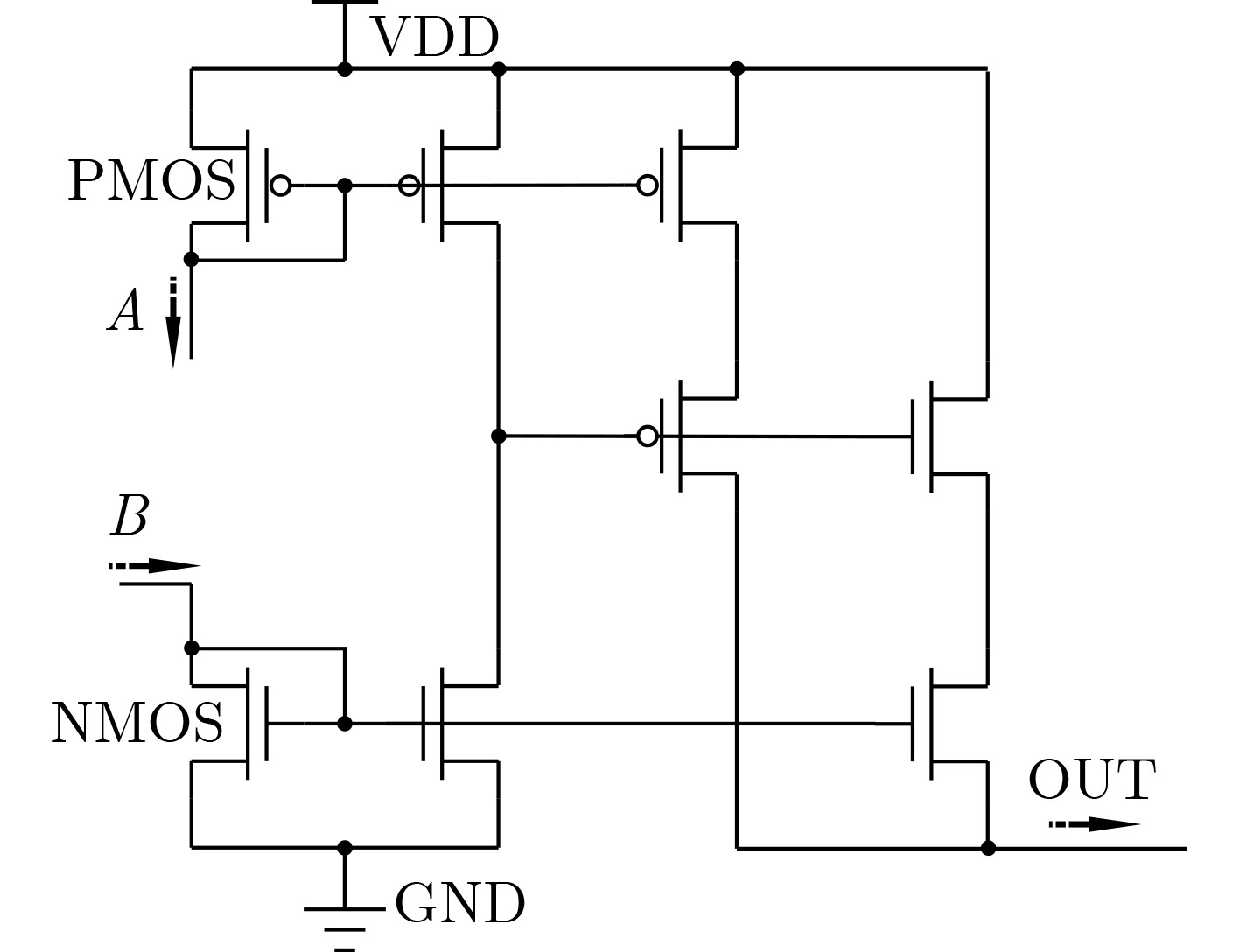

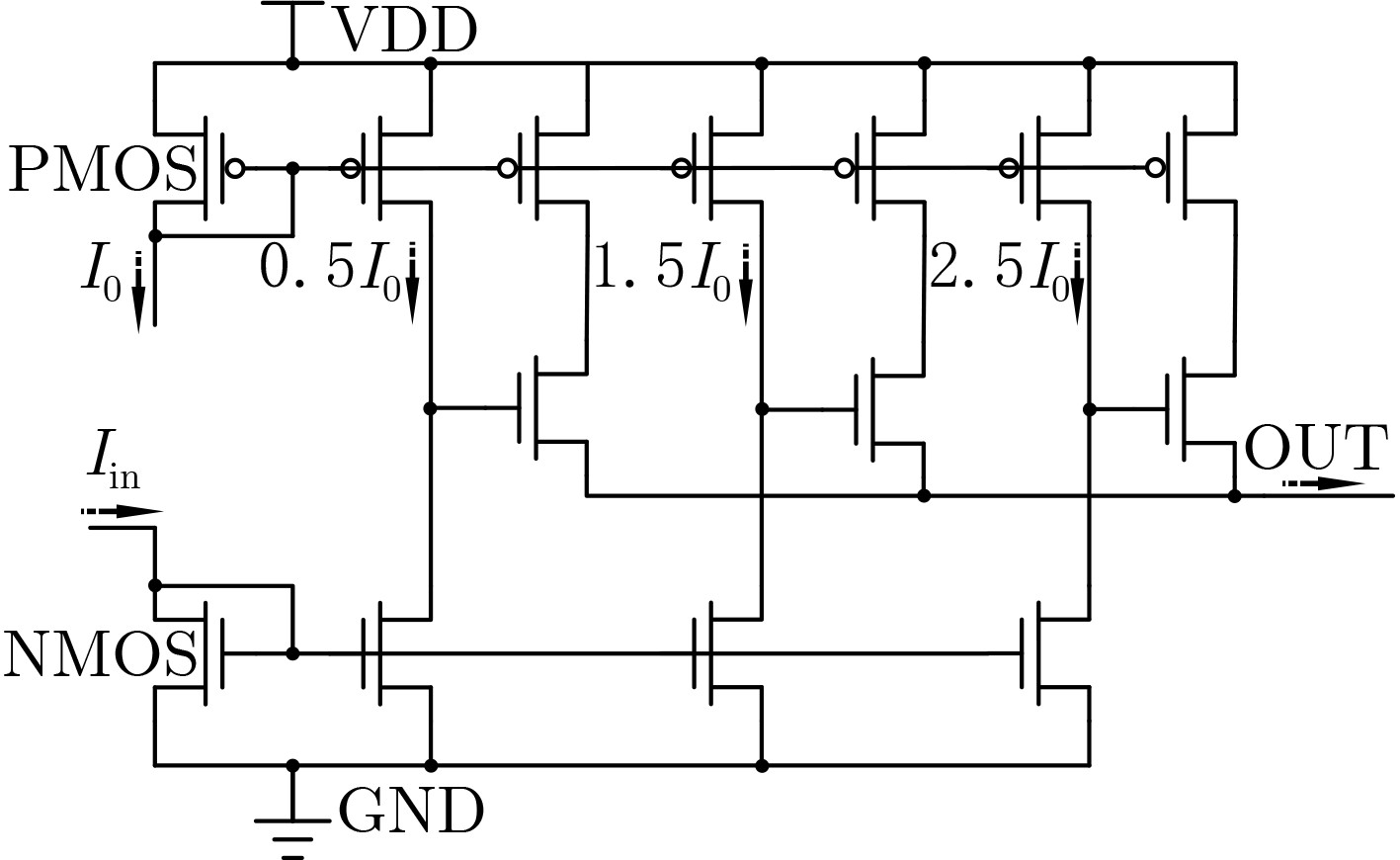

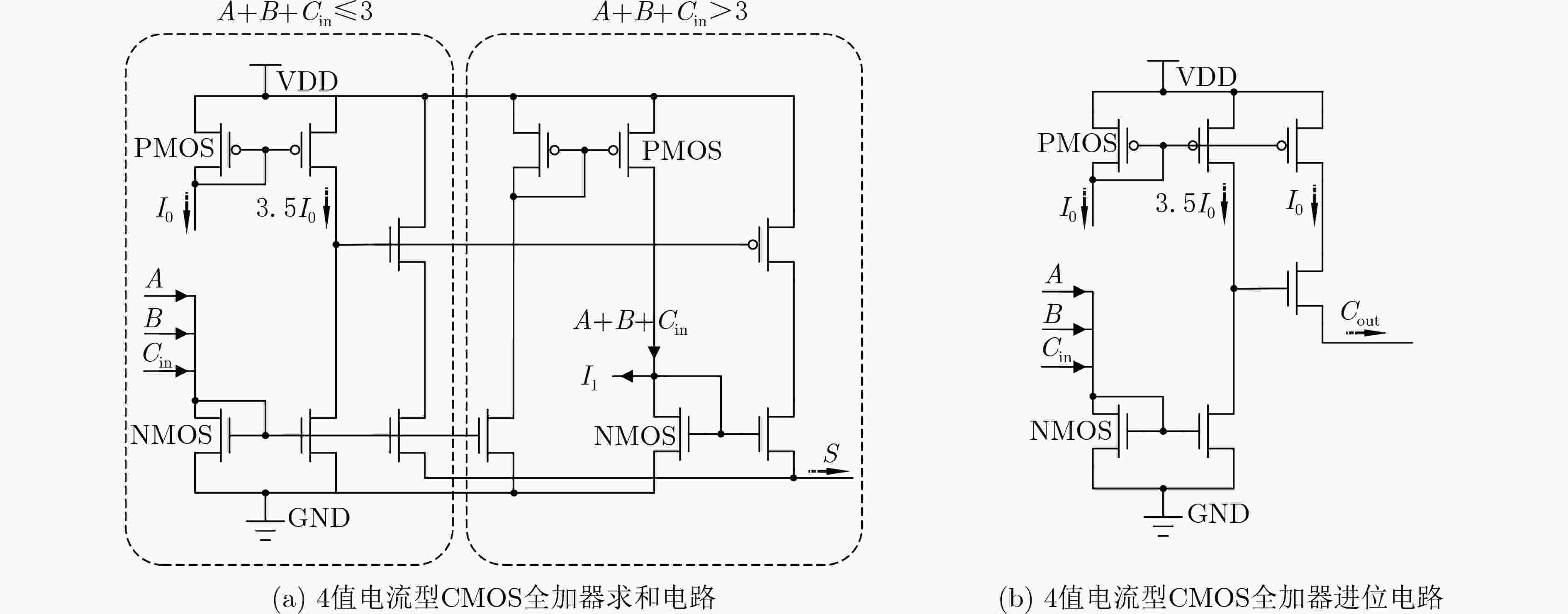

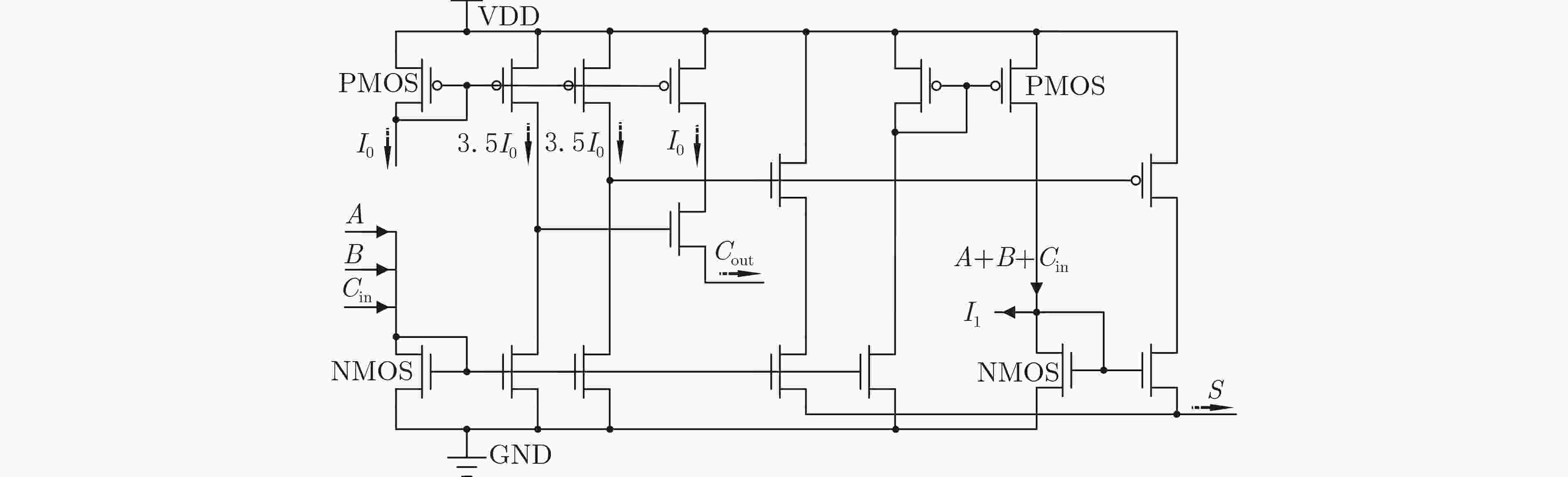

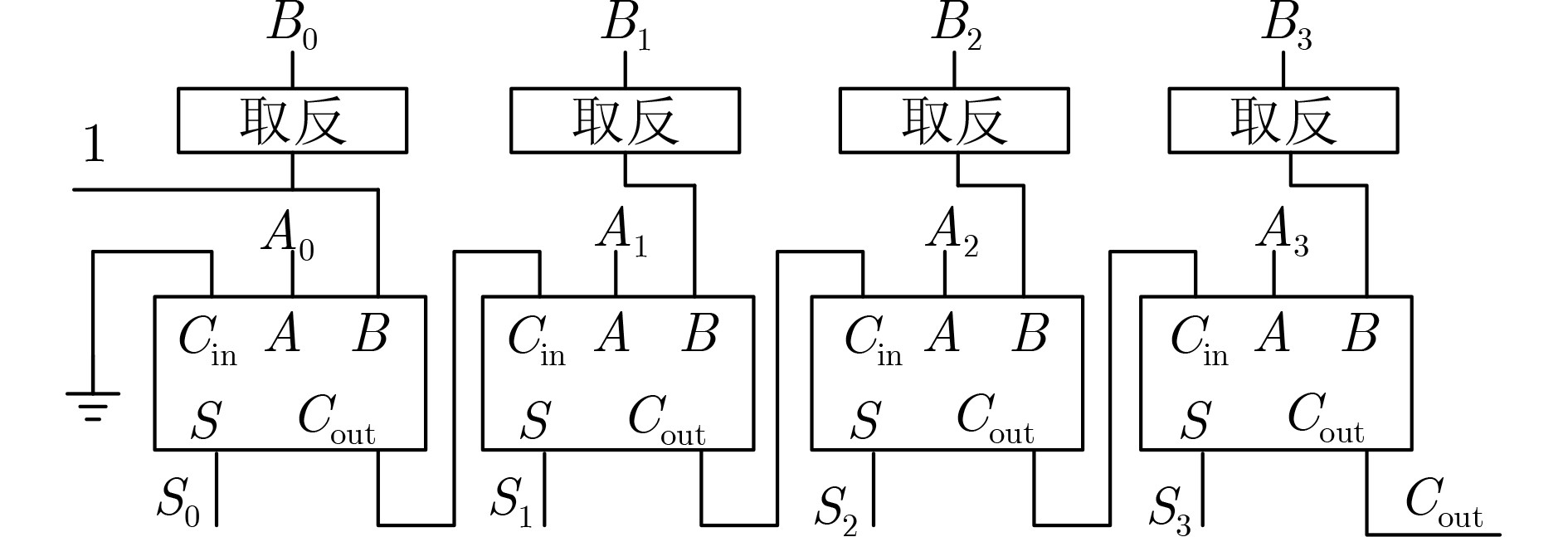

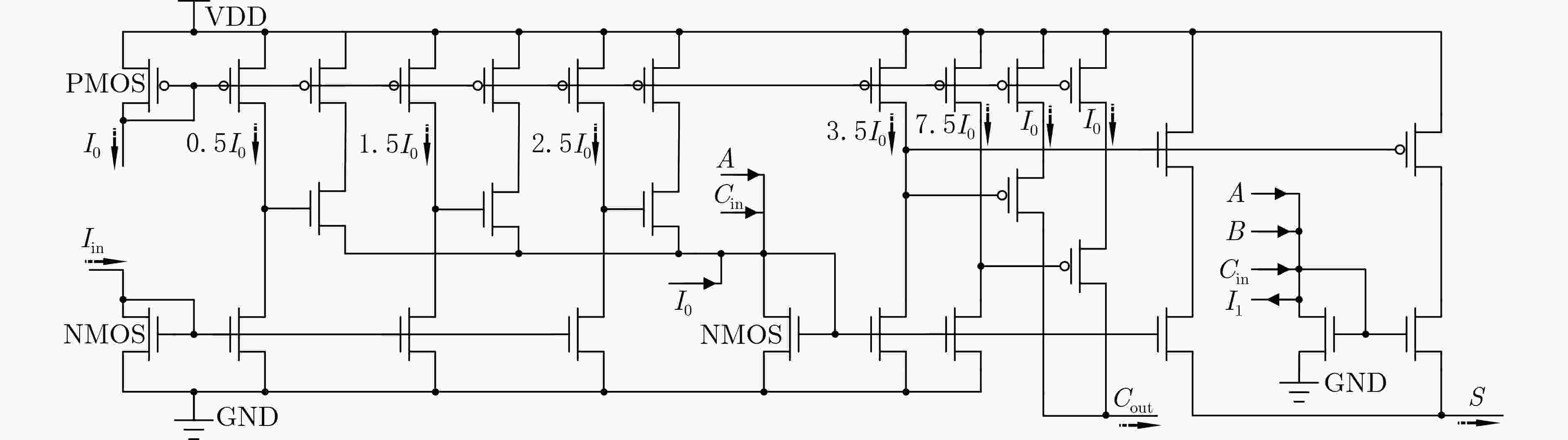

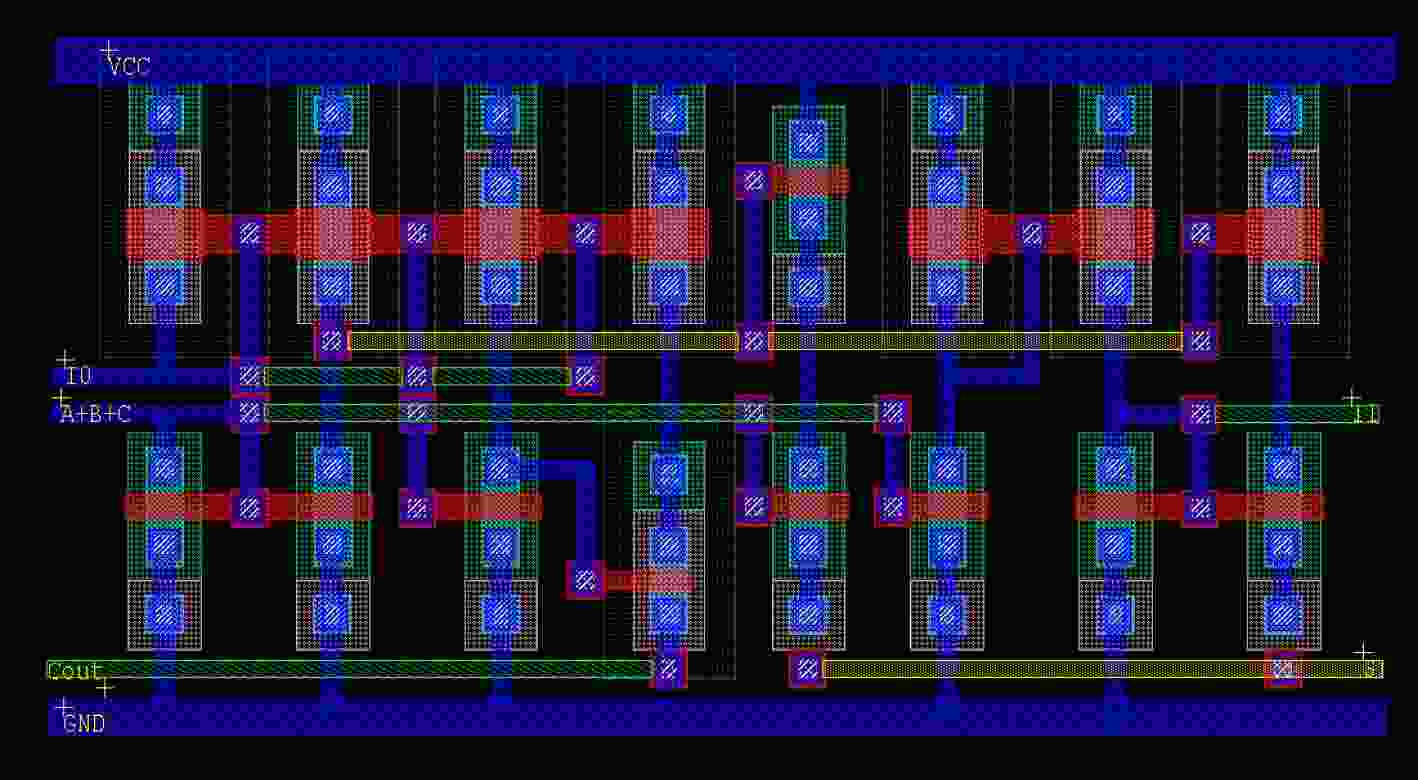

摘要: 该文通过对电流型CMOS电路的阈值控制引入了多值电流型比较器。与2值逻辑电路相比,多值逻辑电路的单条导线允许更多的信息传输。相较于电压信号,电流信号易实现加、减等算术运算,在多值逻辑的设计上更加方便。同时提出了基于比较器的4值基本单元设计方法,实现了4值取大、取小以及反向器的设计,在此基础上设计实现了加法器和减法器。该设计方法在2值、3值以及n值逻辑上同样适用。实验结果表明所设计的电路具有正确的逻辑功能,较之相关文献电流型CMOS全加器有更低的功耗和更少的晶体管数。Abstract: A multiple valued current mode comparator is introduced to control the threshold of current mode CMOS circuits. Compared with binary logic circuits, a single wire of multiple valued logic circuits allows more information transmission. Compared with voltage signal, current signal is easy to realize arithmetic operations, such as addition and subtraction, which is more convenient in the design of multiple valued logic. At the same time, the design method of quaternary valued basic unit based on comparator is proposed, and the designs of quaternary valued max, min and inverter are realized. On this basis, full adder and subtractor are designed and realized. The design method is also applicable to binary, ternary and n-valued logic. The experimental results show that the designed circuit has correct logic function, lower power consumption and fewer transistors than the current mode CMOS full adder in the relevant literature.

-

Key words:

- CMOS /

- Multiple valued logic /

- Current mode /

- Comparator

-

表 1 4值逻辑水平

逻辑电平 参考电流(μA) 0 0 1 10 2 20 3 30 表 2 4值反相器逻辑表

输入电平 输出电平 0 3 1 2 2 1 3 0 -

[1] TAKBIRI M, MIRZAEE R F, and NAVI K. Analytical review of noise margin in MVL: Clarification of a deceptive matter[J]. Circuits, Systems, and Signal Processing, 2019, 38(9): 4280–4301. doi: 10.1007/s00034-019-01063-8 [2] CHATURVEDI B, MOHAN J, KUMAR A, et al. Current-mode first-order universal filter and its voltage-mode transformation[J]. Journal of Circuits, Systems and Computers, 2020, 29(9): 2050149. doi: 10.1142/S0218126620501492 [3] AGRAWAL D and MAHESHWARI S. Design and implementation of current mode circuit for digital modulation[J]. Integration, 2021, 78: 118–123. doi: 10.1016/j.vlsi.2021.02.002 [4] PARK S H, LEE J H, JEONG H G, et al. Design of a CMOS current-mode squaring circuit for training analog neural networks[C]. 2020 International SoC Design Conference (ISOCC), Yeosu, Korea (South), 2020: 250–251. [5] ALJANABI W and ALBAYRAK M. Design and implementation 4-Bit quaternary MVL arithmetic and logic unit[J]. Tehnički Vjesnik, 2018, 25(S2): 330–338. doi: 10.17559/TV-20170210143503 [6] KIM J B. Current mode CMOS quaternary logic full-adder[J]. Journal of Circuits, Systems, and Computers, 2009, 18(1): 199–208. doi: 10.1142/S0218126609005022 [7] NIEMANN P and DRECHSLER R. Synthesis of asymptotically optimal adders for multiple-valued logic[C]. 2021 IEEE 51st International Symposium on Multiple-Valued Logic (ISMVL), Nur-sultan, Kazakhstan, 2021: 178–182. [8] BRITO D, RABUSKE T G, FERNANDES J R, et al. Quaternary logic lookup table in standard CMOS[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23(2): 306–316. doi: 10.1109/TVLSI.2014.2308302 [9] MANE S C, HAJARE S P, and DAKHOLE P. Current mode quaternary logic circuit[C]. 2017 International Conference on Communication and Signal Processing (ICCSP), Chennai, India, 2017: 825–829. [10] CUNHA R, BOUDINOV H, and CARRO L. Quaternary look-up tables using voltage-mode CMOS logic design[C]. The 37th International Symposium on Multiple-Valued Logic (ISMVL'07), Oslo, Norway, 2007: 56. [11] BUTYRLAGIN N V, CHERNOV N I, PROKOPENKO N N, et al. CMOS current logic elements: Application features for processing analog and digital signals[C]. 2018 XIV International Scientific-Technical Conference on Actual Problems of Electronics Instrument Engineering (APEIE), Novosibirsk, Russia, 2018: 196–199. [12] 张立彬, 姚茂群, 王彤. 高性能电流型CMOS显性脉冲触发器设计[J]. 浙江大学学报:理学版, 2013, 40(4): 428–432,436. doi: 10.3785/j.issn.1008-9497.2013.04.014ZHANG Libin, YAO Maoqun, and WANG Tong. Design of novel high-performance current-mode CMOS explicit-pulsed flip-flops[J]. Journal of Zhejiang University:Science Edition, 2013, 40(4): 428–432,436. doi: 10.3785/j.issn.1008-9497.2013.04.014 [13] 姚茂群, 张官志, 施锦河. 阈算术代数系统及多值电流型CMOS电路设计[J]. 电子与信息学报, 2012, 34(7): 1773–1778. doi: 10.3724/SP.J.1146.2011.01185YAO Maoqun, ZHANG Guanzhi, and SHI Jinhe. Threshold—arithmetic algebraic system and design of multiple-valued CMOS circuits[J]. Journal of Electronics &Information Technology, 2012, 34(7): 1773–1778. doi: 10.3724/SP.J.1146.2011.01185 [14] CHAUHAN A, MAHOR L, and TIWARI P. Low power quaternary adder using CNFET[C]. 2020 IEEE VLSI Device Circuit and System (VLSI DCS), Kolkata, India, 2020: 109–114. [15] PRIYA N S and RADHA N. Design and implementation of primitive cells, full adder, full subtractor, and multiplier using modified gate diffusion input logic[C]. 2020 International Conference on Electronics and Sustainable Communication Systems (ICESC), Coimbatore, India, 2020: 1032–1038. [16] TARUN K and HASHMI M S. Multiple valued current mode logic circuits[C]. 2017 International Conference on Multimedia, Signal Processing and Communication Technologies (IMPACT), Aligarh, India, 2017. [17] KIM J B. An area efficient multiplier using current-mode quaternary logic technique[C]. 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 2010. [18] 杭国强. 基于控阈技术的电流型CMOS全加器的通用设计方法[J]. 电子学报, 2004, 32(8): 1367–1369. doi: 10.3321/j.issn:0372-2112.2004.08.033HANG Guoqiang. Universal design method for current-mode CMOS adders based on threshold-controllable technique[J]. Acta Electronica Sinica, 2004, 32(8): 1367–1369. doi: 10.3321/j.issn:0372-2112.2004.08.033 -

下载:

下载:

下载:

下载: