A True Random Number Design of Low Power and High Noise Source

-

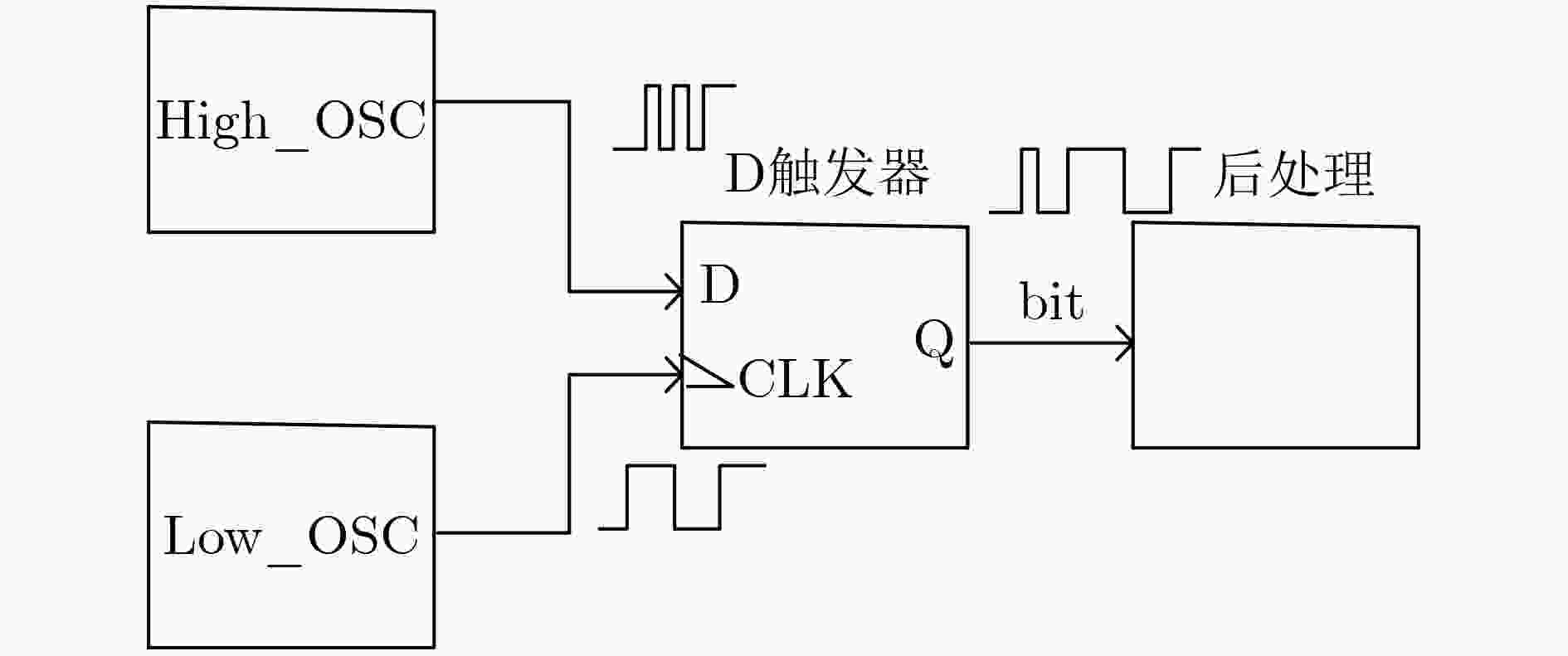

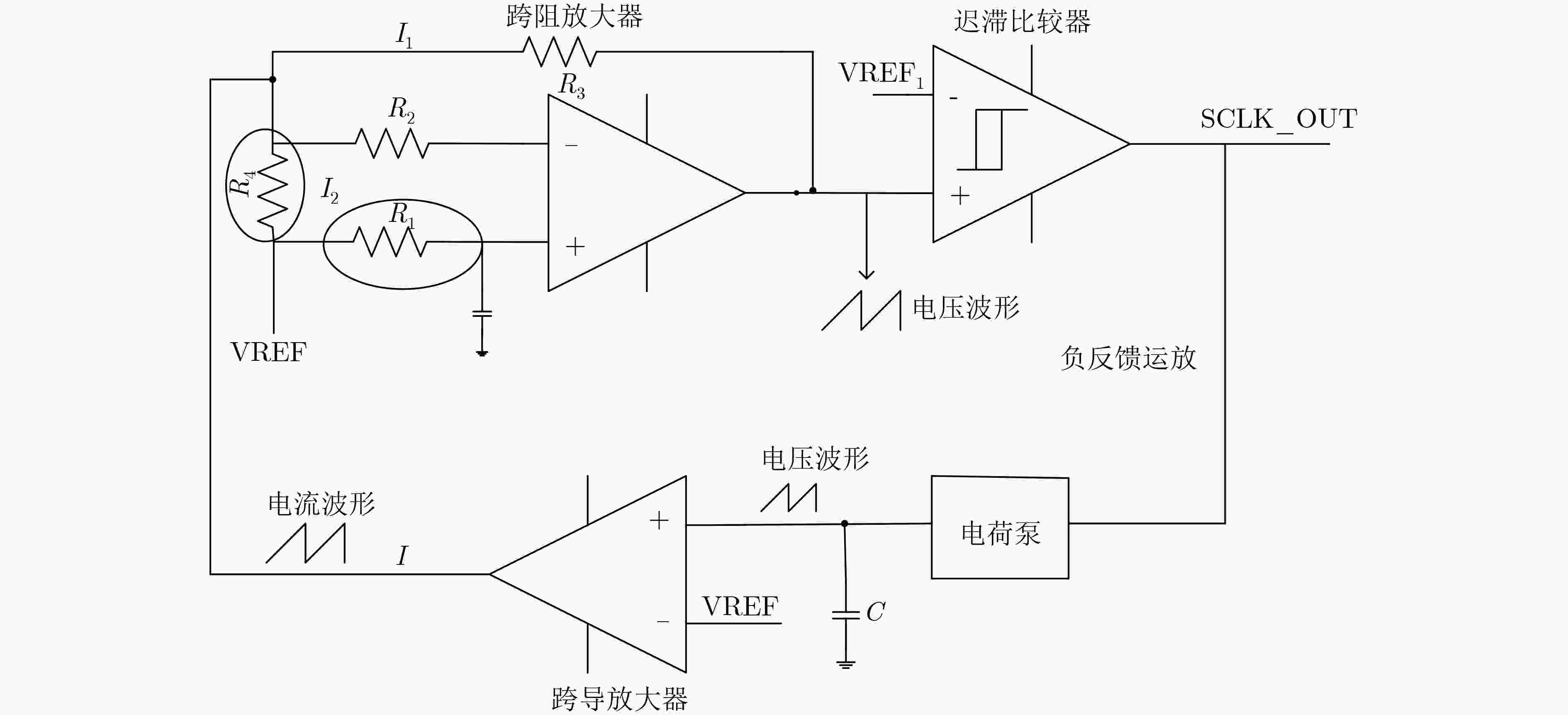

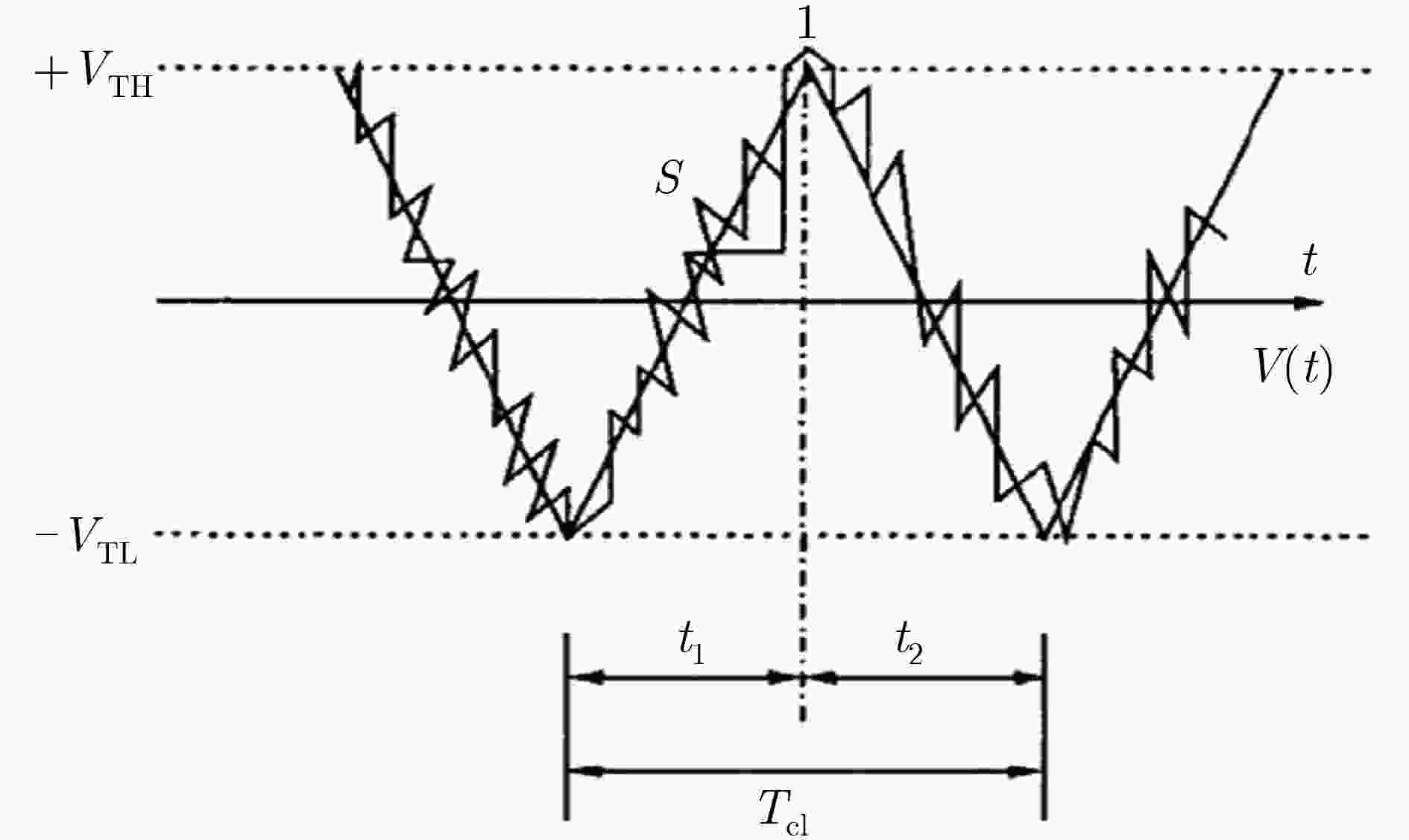

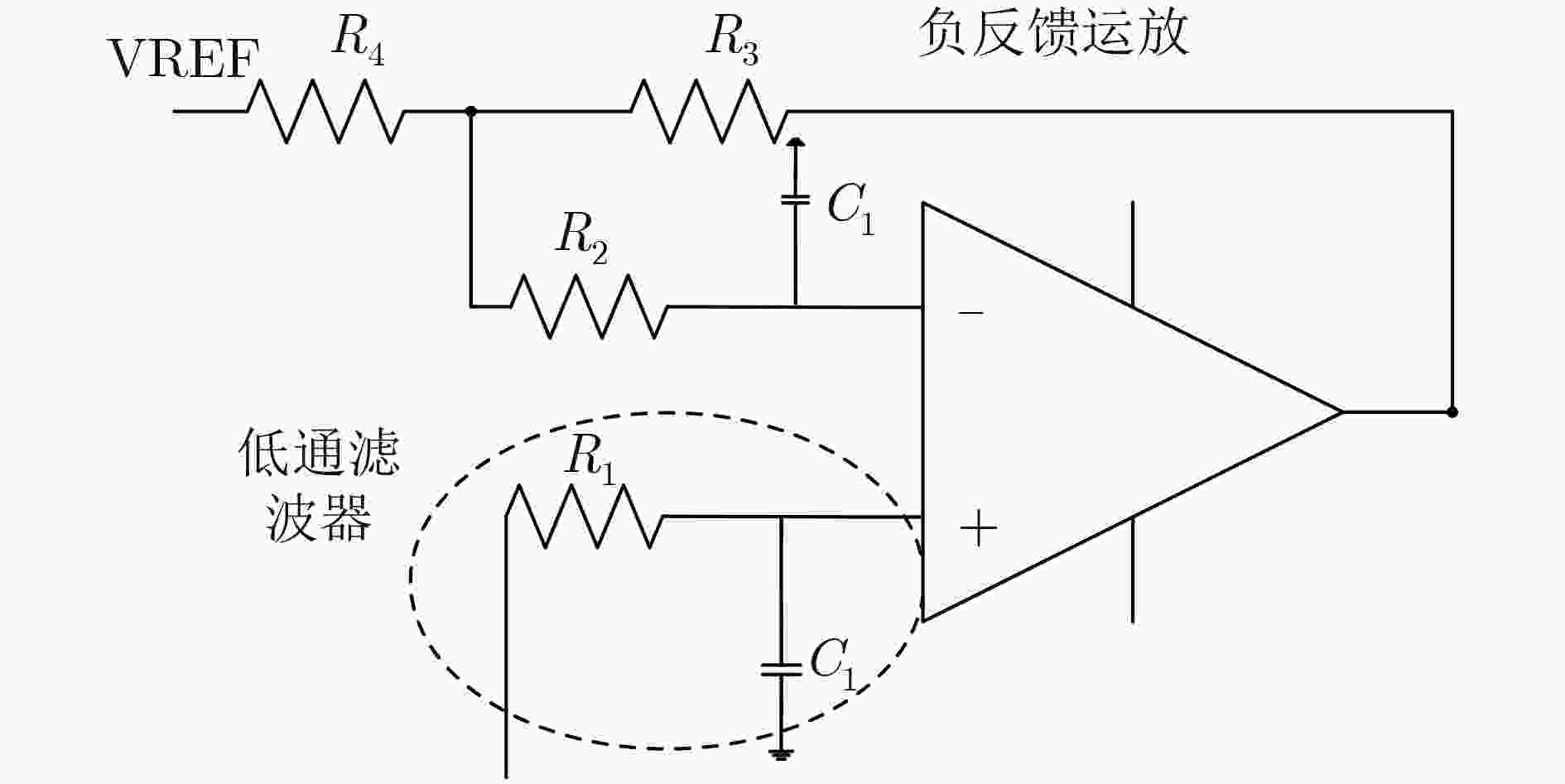

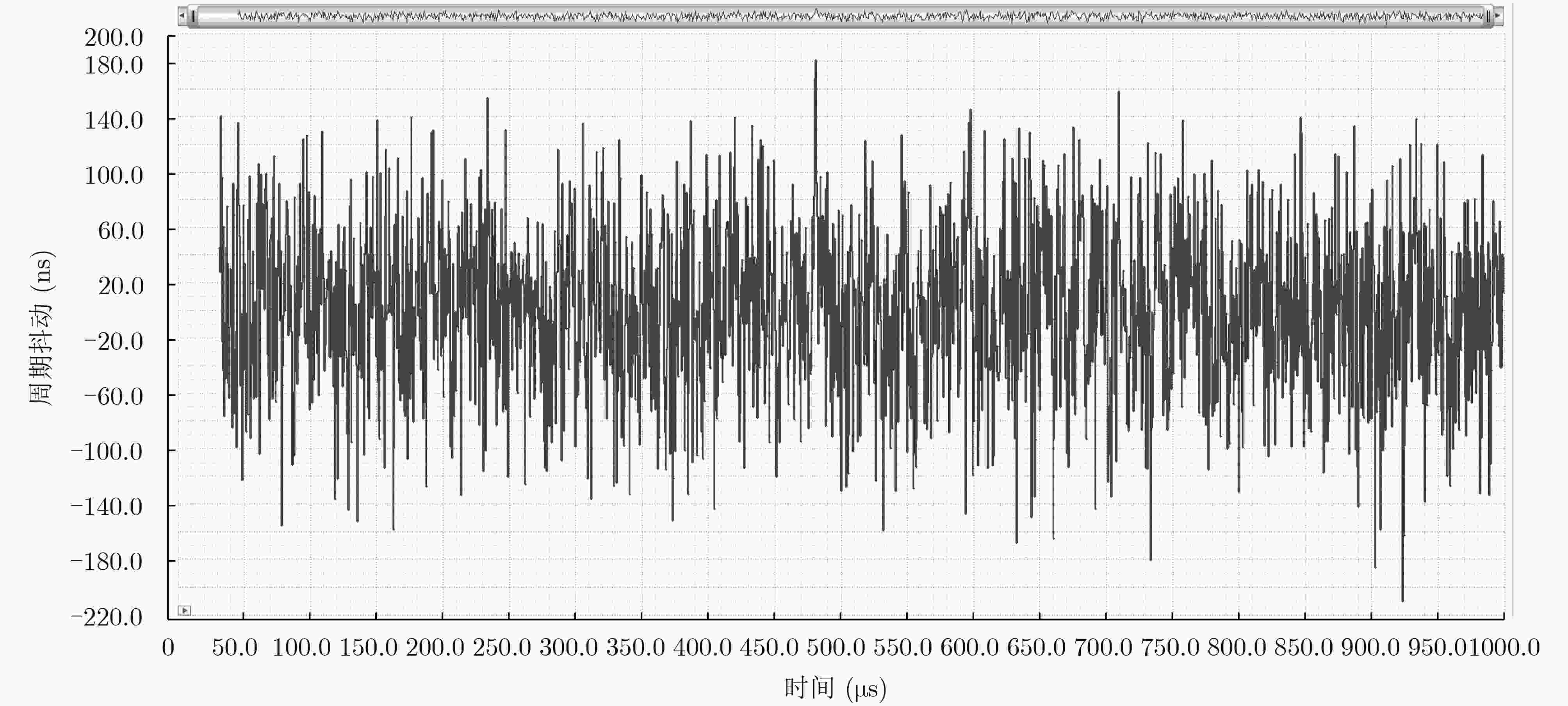

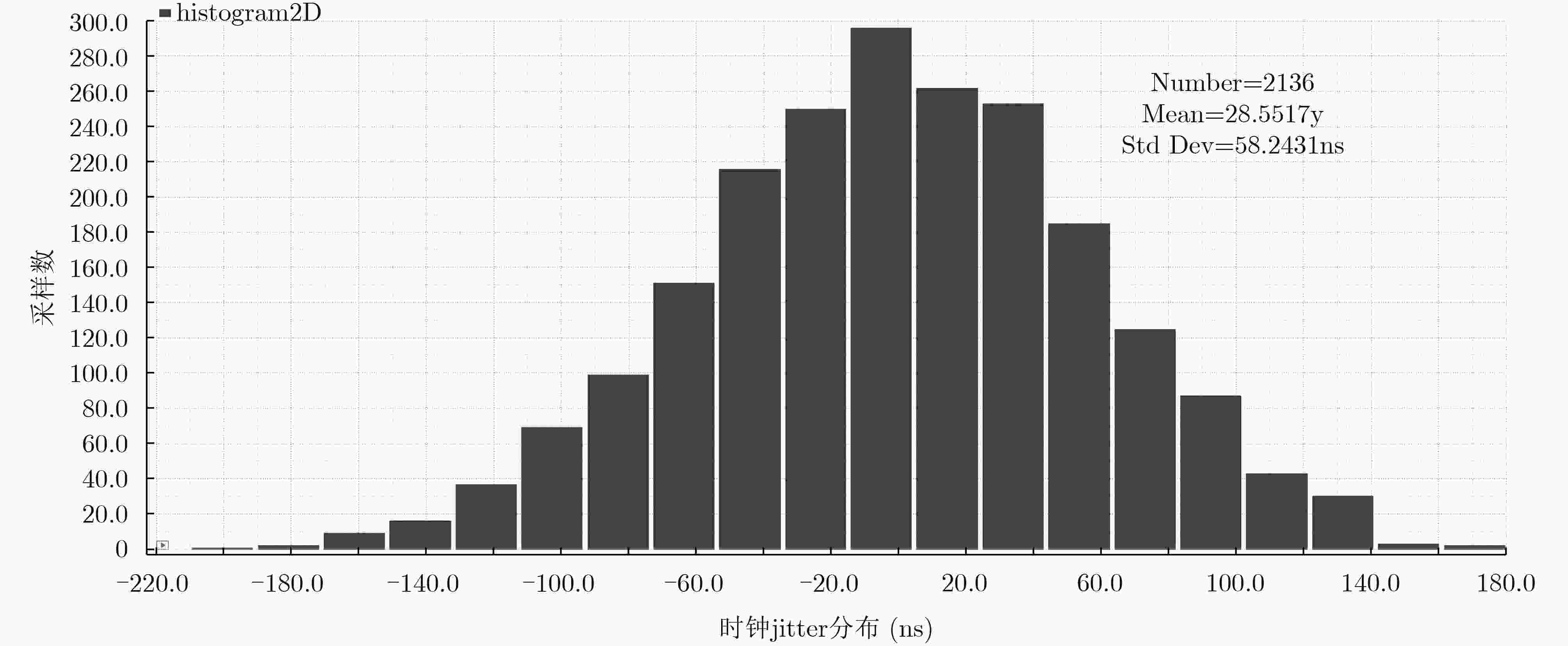

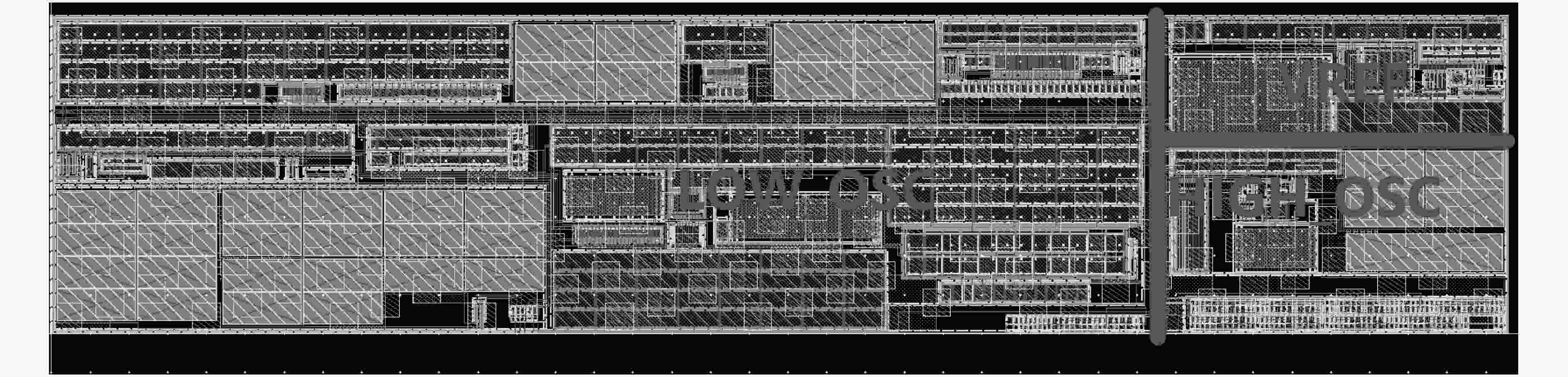

摘要: 通过对一种低功耗高噪声源真随机数发生器(TRNG)的研究,设计了一种新型的低频时钟电路,可以把电阻热噪声放大100倍以上,从而减少低频时钟电路的带宽和电阻值,使电路的面积和功耗减少,并且使低频时钟的jitter到达58.2 ns。电路采用SMIC 40 nm CMOS工艺设计,完成了流片和测试,真随机数产生器输出速度范围为1.38~3.33 Mbit/s,电路整体功耗为0.11 mW,面积为0.00789 mm2。随机数输出满足AIS31真随机数熵源测试要求,并且通过了国密2安全测试。

-

关键词:

- 真随机数产生器 /

- 电阻热噪声 /

- 低频时钟jitter /

- 低功耗

Abstract: Through the research of a True Random Number Generator (TRNG), which is a low-power and high-noise source, a new type of low-frequency clock is designed. It can amplify the thermal noise of resistance more than 100 times, thus reducing the bandwidth and resistance value of the circuit, reducing the area and power consumption of the circuit, and making the jitter of low-frequency clock reach 58.2 ns. The circuit is designed by SMIC 40 nm CMOS technology. The flow sheet and test are completed. The output speed of TRNG ranges from 1.38 to 3.33 Mbit/s. The overall power consumption of the circuit is 0.11 mW and the area is 0.00789 mm2. The output of random number meets the test requirement of AIS31 true random number entropy source, and passes the security test of National Secret 2. -

表 1 两种结构下噪声电阻值和功耗

指标 噪声电阻值

(Ω)信号增益A1(倍) 信号增益A2(倍) 噪声带宽(MHz) 功耗(mW) 跨阻放大器结构 64 k 1 100 1 0.081 电压放大器结构 2 M 5 5 80 0.220 表 2 低频时钟频率仿真结果

指标 仿真结果 MIN TYP MAX 输出频率(MHz) 1.38 2.13 3.34 Jitter(σ{Tcl})(ns) 77.89 58.2 40 功耗(mW) 0.055 0.081 0.110 表 3 高频时钟频率仿真结果

仿真 HOSC频率 MIN TYP MAX 频率(GHz) 0.186 0.25 0.313 功耗(mW) 0.017 0.024 0.035 占空比(%) 50.09 50.28 50.43 -

苏桂平, 吕述望, 杨柱, 等. 真随机数发生器的随机性在信息安全中的应用[J]. 计算机工程, 2002, 28(6): 114–115. doi: 10.3969/j.issn.1000-3428.2002.06.044SU Guiping, LÜ Shuwang, YANG Zhu, et al. Application of the randomness of a random number generator in the information security[J]. Computer Engineering, 2002, 28(6): 114–115. doi: 10.3969/j.issn.1000-3428.2002.06.044 张仿. 随机数在加密技术中的应用分析[J]. 计算机应用与软件, 2004, 21(12): 105–107. doi: 10.3969/j.issn.1000-386X.2004.12.041ZHANG Fang. Analysis and application of random number in encryption[J]. Computer Applications and Software, 2004, 21(12): 105–107. doi: 10.3969/j.issn.1000-386X.2004.12.041 张玉浩, 徐志鹏, 黄新锐, 等. 基于AES加密电路的防复制电路及系统设计[J]. 电子器件, 2015, 38(1): 103–107. doi: 10.3969/j.issn.1005-9490.2015.01.023ZHANG Yuhao, XU Zhipeng, HUANG Xinrui, et al. Design of copy prevention circuit and system based on AES encryption circuit[J]. Chinese Journal of Electron Devices, 2015, 38(1): 103–107. doi: 10.3969/j.issn.1005-9490.2015.01.023 马原, 陈天宇, 吴鑫莹, 等. 随机数发生器的设计与检测[J]. 信息安全研究, 2019, 5(1): 39–49. doi: 10.3969/j.issn.2096-1057.2019.01.005MA Yuan, CHEN Tianyu, WU Xinying, et al. Design, implementation and testing of random number generators[J]. Journal of Information Security Research, 2019, 5(1): 39–49. doi: 10.3969/j.issn.2096-1057.2019.01.005 WIECZOREK P Z. Lightweight TRNG based on multiphase timing of bistables[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2016, 63(7): 1043–1054. doi: 10.1109/TCSI.2016.2555248 臧鸿雁, 李玖, 李国东. 一个一维离散混沌判定定理及其在伪随机数发生器中的应用[J]. 电子与信息学报, 2018, 40(8): 1992–1997. doi: 10.11999/JEIT171139ZANG Hongyan, LI Jiu, and LI Guodong. A one-dimensional discrete map chaos criterion theorem with applications in pseudo-random number generator[J]. Journal of Electronics &Information Technology, 2018, 40(8): 1992–1997. doi: 10.11999/JEIT171139 PARESCHI F, SETTI G, and ROVATTI R. A fast chaos-based true random number generator for cryptographic applications[C]. The 32nd European Solid-State Circuits Conference, Montreux, Switzerland, 2006: 130–133. doi: 10.1109/ESSCIR.2006.307548. LIU Dongsheng, LIU Zilong, LI Lun, et al. A low-cost low-power ring oscillator-based truly random number generator for encryption on smart cards[J]. IEEE Transactions on Circuits and Systems Ⅱ: Express Briefs, 2016, 63(6): 608–612. doi: 10.1109/TCSⅡ.2016.2530800 李冰, 徐云晶, 陈帅, 等. 基于SRAM物理不可克隆函数的高效真随机种子发生器设计[J]. 电子与信息学报, 2017, 39(6): 1458–1463. doi: 10.11999/JEIT160835LI Bing, XU Yunjing, CHEN Shuai, et al. Efficient design of truly random seed generator based on SRAM physical unclonable functions[J]. Journal of Electronics &Information Technology, 2017, 39(6): 1458–1463. doi: 10.11999/JEIT160835 魏子魁, 符令, 王雪, 等. 一种基于热噪声振荡器的高速真随机数设计[J]. 电子技术应用, 2018, 44(10): 29–31, 36. doi: 10.16157/j.issn.0258-7998.180002WEI Zikui, FU Ling, WANG Xue, et al. A high speed truly random number generator based on thermal noise oscilltor[J]. Application of Electronic Technique, 2018, 44(10): 29–31, 36. doi: 10.16157/j.issn.0258-7998.180002 叶少康, 李峥. 基于数模混合的真随机数发生器[J]. 计算机工程与设计, 2012, 33(4): 1602–1606, 1622. doi: 10.16208/j.issn1000-7024.2012.04.017YE Shaokang and LI Zheng. True random number generator based on mixed-signal circuit[J]. Computer Engineering and Design, 2012, 33(4): 1602–1606, 1622. doi: 10.16208/j.issn1000-7024.2012.04.017 王浩宇, 梁华国, 徐秀敏, 等. 一种基于FPGA的Latch结构真随机数发生器[J]. 微电子学, 2018, 48(5): 635–641. doi: 10.13911/j.cnki.1004-3365.170532WANG Haoyu, LIANG Huaguo, XU Xiuming, et al. A latch structure true random number generator based on FPGA[J]. Microelectronics, 2018, 48(5): 635–641. doi: 10.13911/j.cnki.1004-3365.170532 LIU Yao, CHEUNG R C C, and WONG H. A bias-bounded digital true random number generator architecture[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2017, 64(1): 133–144. doi: 10.1109/TCSI.2016.2606353 辛可为, 吕方旭, 王建业, 等. 适用于4通道100 Gbps SerDes的两级架构正交12.5 GHz低功耗低抖动时钟发生器[J]. 空军工程大学学报: 自然科学版, 2019, 20(5): 64–69.XIN Kewei, LÜ Fangxu, WANG Jianye, et al. A 12.5 GHz clock generator applicable for 4 way 100 Gbps high speed serial interface circuits[J]. Journal of Air Force Engineering University:Natural Science Edition, 2019, 20(5): 64–69. YANG Kaiyuan, FICK D, HENRY M B, et al. 16.3 A 23Mb/s 23pJ/b fully synthesized true-random-number generator in 28nm and 65nm CMOS[C]. 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, USA, 2014: 280-281. doi: 10.1109/ISSCC.2014.6757434. 王鹏君, 李桢, 李刚, 等. 基于压控振荡器的真随机数发生器设计[J]. 电子学报, 2019, 47(2): 417–421. doi: 10.3969/j.issn.0372-2112.2019.02.022WANG Pengjun, LI Zhen, LI Gang, et al. Design of true random number generator based on VCO[J]. Acta Electronica Sinica, 2019, 47(2): 417–421. doi: 10.3969/j.issn.0372-2112.2019.02.022 -

下载:

下载:

下载:

下载: