Space-based Computing Chips: Current Status, Trends and Key Technique

-

摘要: 随着航天技术的快速发展,天基计算芯片作为空间信息系统的核心器件,承担着数据处理、任务控制和通信支持等关键功能,其重要性日益凸显。天基计算芯片不仅决定了空间任务的执行效率和可靠性,还在极端环境下为航天器的长期稳定运行提供保障。该文通过回顾天基计算芯片的发展历程,以探讨其未来发展方向。首先按照结构功能划分,从通用处理器(CPU)、现场可编程门阵列(FPGA)和专用芯片3方面对天基计算芯片的发展现状进行归纳和总结;然后深入分析其与地面芯片的主要区别,探讨针对辐射效应等空间环境挑战的关键容错技术,并从不同层面阐述已有的技术方法;最后论述了天基计算芯片未来的主要发展方向,即大算力、商用现货 (COTS)器件广泛应用、第五代精简指令集(RISC-V)架构和芯粒技术。该文能够帮助读者了解该领域现状,掌握关键问题,并为后续的相关研究工作提供有价值的参考和启示。Abstract:

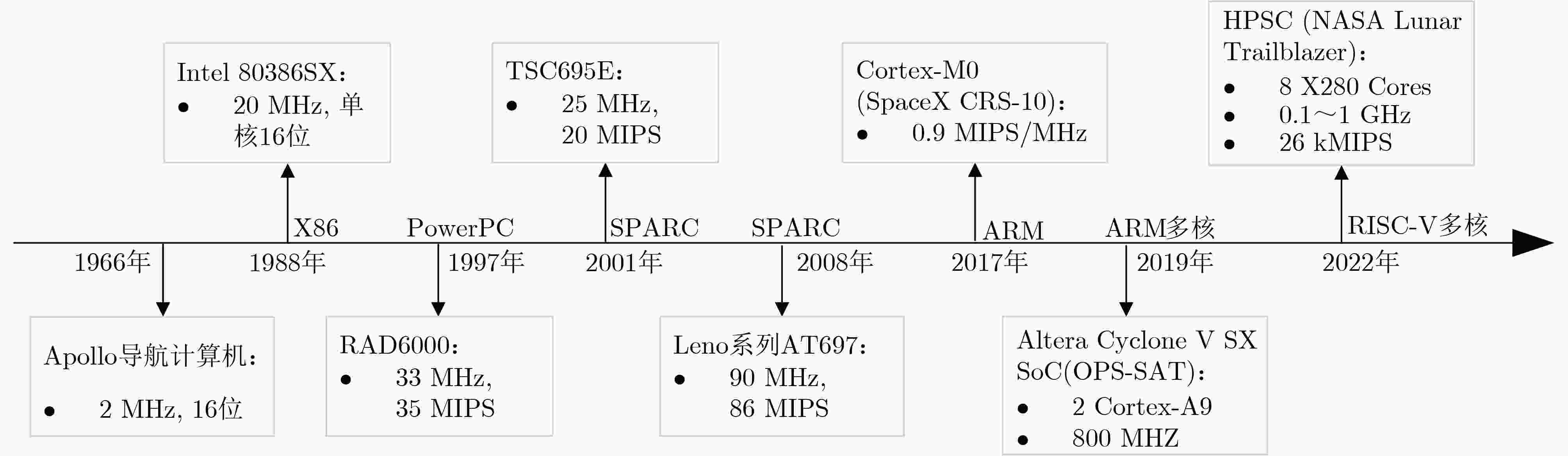

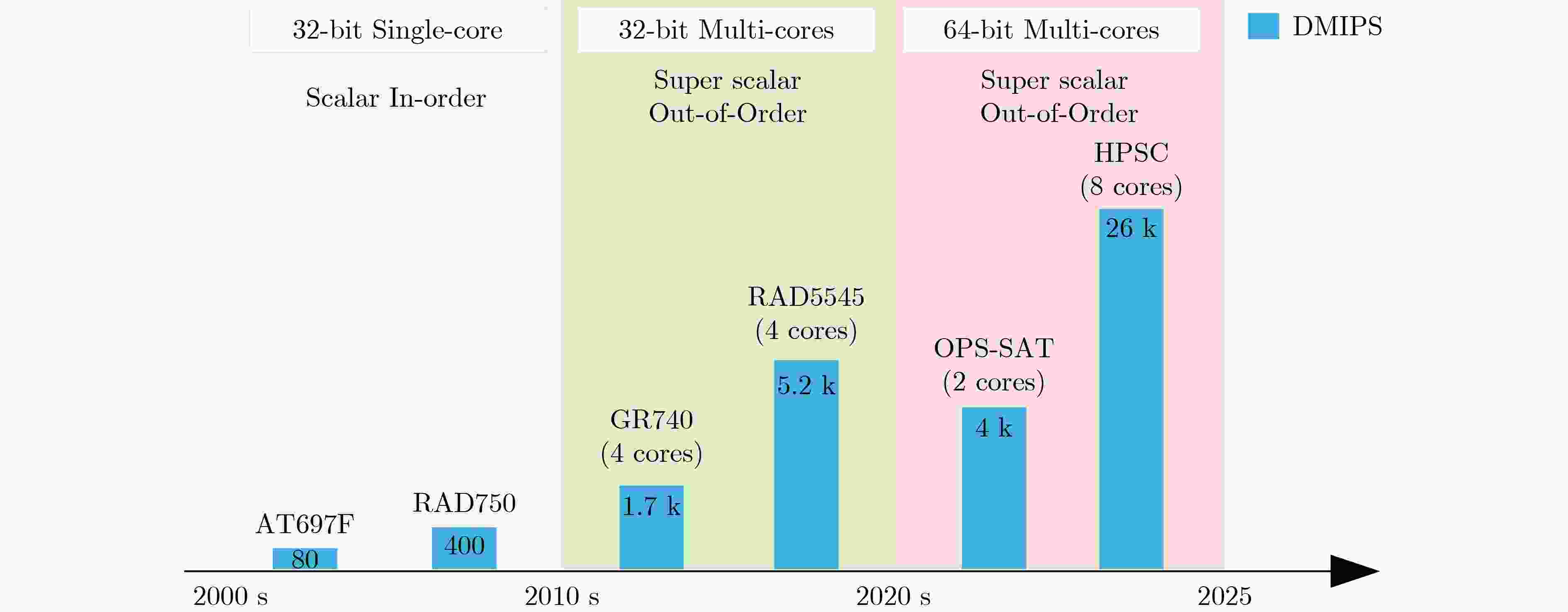

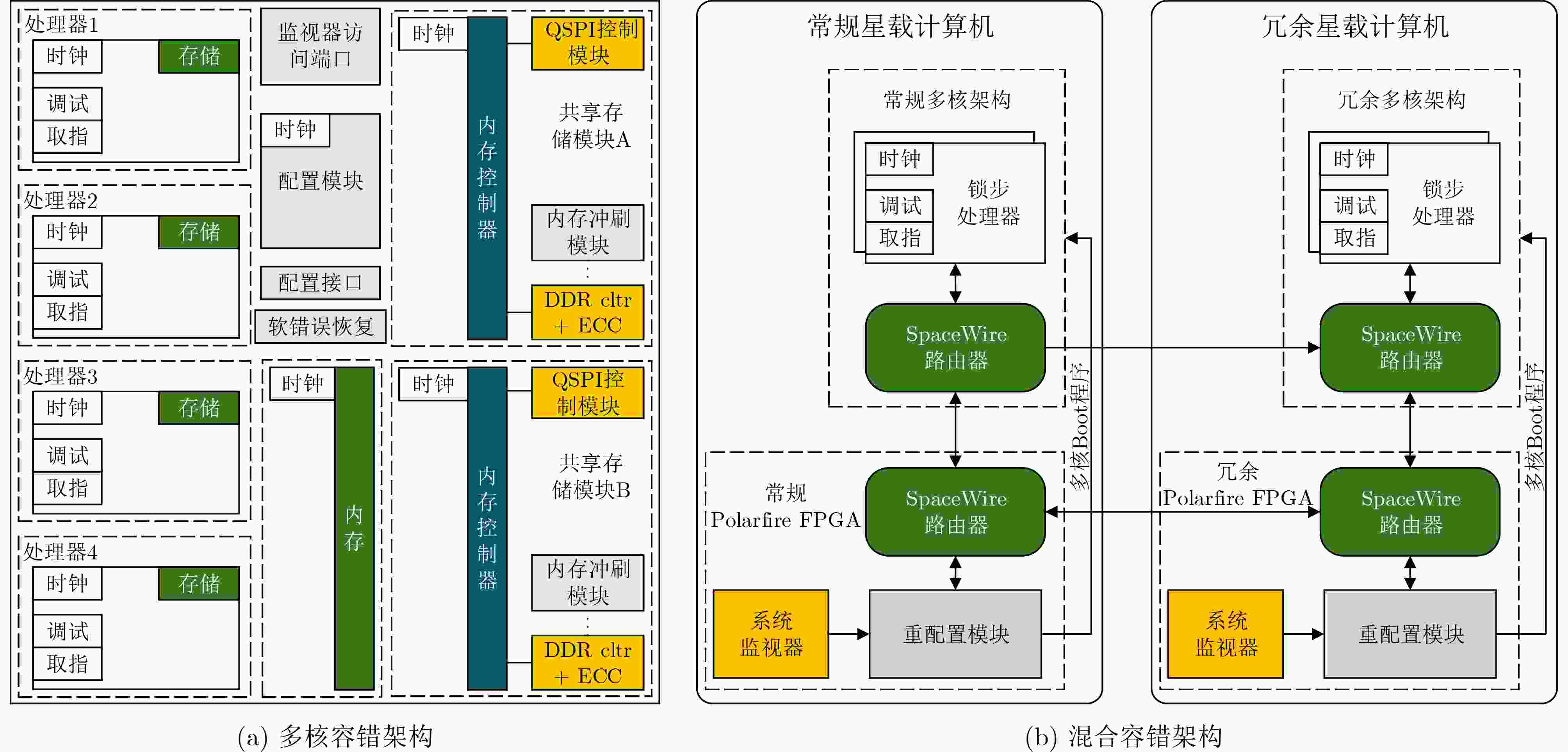

Significance With the continuous advancement of aerospace technology and the growing demand for space applications, space-based computing chips have assumed increasingly important strategic roles as core hardware infrastructure of space information systems. As the technological foundation enabling intelligent data processing and reliable communications for spacecraft—including satellite platforms, space stations, and deep space probes, space-based computing chips not only safeguard national security and support economic development but also play an irreplaceable role in serving civilian needs. Although existing survey literature has systematically reviewed the development of aerospace Central Processing Units (CPUs), comprehensive analyses of other key components within the space-based computing chip ecosystem remain limited. To address this gap, this paper systematically examines the technological evolution of various space-based computing chips and their principal fault-tolerant mechanisms, and further explores potential future trends in this field. Progress This paper adopts a functional architecture-oriented classification to systematically analyze and summarize the current technological status of space-based computing chips across three dimensions: CPU, Field-Programmable Gate Array (FPGA), and dedicated chip. For CPU technology, a classification study of general-purpose processors widely used in aerospace applications is conducted based on instruction set architectures, with in-depth analysis of the technical characteristics and representative products of various architectures, together with an objective evaluation of their advantages and limitations in space environments. In the FPGA domain, the technical specifications and performance characteristics of mainstream space-grade FPGA products, both domestic and international, are comprehensively reviewed to provide a reference for application selection. For dedicated chips, a detailed categorization is carried out according to functional architectural features and application scenario requirements, covering Digital Signal Processing (DSP) chips for signal processing acceleration, Graphics Processing Unit (GPU) chips for graphics computation, and Neural Processing Unit (NPU) chips for space-based artificial intelligence applications, thereby systematically clarifying the applicability of different architectures in complex space environments. In addition, this paper presents an in-depth analysis of the key fault-tolerant technology framework for space-based computing chips at multiple levels, including system, architecture, circuit, and process library, and provides a comprehensive evaluation of the technical advantages, application limitations, and development prospects of various fault-tolerant mechanisms. This analysis offers theoretical guidance for the reliability design of space-based computing chips. Conclusions This review systematically summarizes the technological development of space-based computing chips, providing a comprehensive analysis of the architectural characteristics of different chip types and their associated fault-tolerant technology frameworks, while elucidating the applicable scenarios and technical limitations of various fault-tolerant mechanisms. The central principle of fault-tolerant design for space-based computing chips is to achieve effective detection and correction of circuit faults through redundancy mechanisms. This paper offers an in-depth analysis of the implementation principles and application characteristics of fault-tolerant technologies at four hierarchical levels: system, architecture, circuit, and process library. Although these multi-level approaches substantially improve system reliability, they inevitably introduce hardware resource overhead and performance penalties. Therefore, the engineering design of space-based computing chips requires optimized strategies that combine multi-level fault-tolerant technologies according to specific reliability requirements, aiming to balance reliability, cost, and performance to meet the intended design objectives and technical specifications. Prospects Looking ahead, space-based computing chips present broad prospects in high computing capability, widespread adoption of Commercial Off-The-Shelf (COTS) devices, and the development of Reduced Instruction Set Computer-Five (RISC-V) instruction set architectures. With the rapid advancement of space technology, space-based systems are undergoing a transformation from traditional single-function platforms to integrated platforms characterized by multi-task collaboration, autonomy, and intelligence. Real-time data processing, multi-task parallel computing, and intelligent decision-making have become the principal driving forces in the evolution of space-based computing technology, all of which demand robust computational foundations. Compared with traditional radiation-hardened specialized devices, COTS devices are emerging as a major trend in space-based computing chip development due to their advantages in cost-effectiveness, computational performance, shorter development cycles, and product diversity. In addition, RISC-V, as an open-source instruction set architecture, offers unique advantages and significant potential for space-based computing chip innovation through its modular design philosophy, exceptional scalability, and open ecosystem. Chiplet technology, as an innovative approach to chip design and fabrication, enables cost reduction and accelerates development timelines through its modular architecture, while simultaneously facilitating flexible customization and fault-tolerant mechanisms. This approach is particularly well-positioned to address the evolving and heterogeneous computing demands of space-based platforms. -

表 1 天基芯片中通用处理器按指令架构分类

指令集架构 处理器芯片 年份 国家/地区 核数/位宽 主频 功耗 工艺节点 抗辐射能力 X86 Intel 80386SX 1988 美国 单核32位 20.0 MHz 1.0 W 1.50 μm 无硬化,需屏蔽防护 AMD Steppe Eagle 2021 瑞典 四核64位 1.0 GHz 5.0~10.0 W 28 nm CTOS,未加固 SPARC TSC695E 2001 美国 单核32位 25.0 MHz 1.0 W 0.5 μm TID~300 krad AT697F(LEON2) 2011 法国 单核32位 90.0 MHz 0.5 W 0.18 μm TID~100 krad, SEU加固 BM3803 2011 中国 单核32位 8.0~12.0 MHz < 1.0 W 0.35 μm TID~50 krad级,TMR加固 BM3823 2018 中国 单核32位 300.0 MHz 2.0 W 65 nm TMR加固, SEL≥75 (MeV·cm2)/mg GR740(LEON4FT) 2021 美国 四核32位 250.0 MHz 7.0 W 65 nm TID>100 krad, TMR加固 ARM Phytium D2000 2020 中国 八核64位 2.3 GHz 25.0 W 14 nm CTOS,支持ECC校验 VORAGO VA7230 2021 美国 双核64位 1.5 GHz < 10.0 W - TID≥100 krad,

SEL≥60 (MeV·cm2)/mgRISC-V NOEL-V 2020 瑞典 64/32位 - - - 存储器支持纠正4 bit相邻错误 HPSC (NASA) 2022 美国 十核64位 0.1~1.0 GHz < 15.0 W 7/14 nm TID~100 krad, SEL免疫80 MeV AS32S601 2024 中国 双核32位 180.0 MHz 135.0~275.0 mW - SEU:10–5次/器件·天 MIPS Loongson 3A5000 2015 中国 四核64位 2.5 GHz 30.0 W 12 nm CTOS,部分加固版本研制中 表 2 国内外太空FPGA产品特性

FPGA型号 制造商 架构/工艺 等效逻辑规模 抗辐射能力 特点及应用 Xilinx Virtex-5QV AMD (美) SRAM FPGA /65 nm 130万逻辑门 TID >1 Mrad;

SEL≥75 MeV·cm²/mg首款高性能抗辐射FPGA,

用于图像处理XQRKU060 SRAM FPGA /20 nm 100万逻辑门 TID >100 krad;

SEE加固支持高速收发器,用于宽带通信载荷 Microchip RTAX2000 Microchip (美) Anti-fuse FPGA/150 nm 200万逻辑门 TID >1 Mrad 抗熔丝工艺,配置不可重构,

适用于长寿命任务控制逻辑Microchip RTG4 Flash FPGA /28 nm 15万逻辑单元 TID >100 krad 闪存工艺,无配置单粒子翻转,

中高轨DSP和控制逻辑BRAVE NG-Medium NanoXplore (欧) SRAM FPGA /28 nm 5万 LUT6 TID >100 krad;

SEL~ 68 MeV· cm²/mg用于ESA小卫星接口和控制逻辑 JFM4VSX55RH 复旦微 (中) SRAM FPGA 1000 万逻辑门TID 200 krad; SEL ~

81 MeV·cm²/mg已在高分卫星上验证,

用于图像处理表 3 架构容错技术对比

技术 描述 优缺点 TCLS 配置3个内核执行同一任务,进行周期级比对 效率最高的纠错率,但最大的面积与功耗开销 HMR 构建锁步控制矩阵,实现TCLS、DCLS与独立模式快速切换 面积、性能与可靠度之间均衡折中 ODGR 在每3个核间配置多数表决模块,通过软件配置启用或释放冗余模块 额外硬件开销最小,依赖软件恢复周期长 表 4 电路容错技术对比

技术 描述 应用场景 ECC 检测和纠正内存错误 内存、处理器 TMR 3个模块投票,容忍单一故障 航空航天 BIST 自我检测,切换冗余组件 处理器、存储器 表 5 抗辐照工艺库技术

技术 描述 辐射耐受性 SOI 绝缘基底,减少电荷收集 1000 ~3000 krad宽带隙材料 耐受深层缺陷 高(具体数值待定) DICE锁存器 冗余节点提高抗辐射能力 500 krad+ 非易失性磁阻材料 优化隧道结的材料和结构 100 krad,降低写功耗 表 6 国内外太空项目使用COTS器件用例

项目 COTS器件 功能描述 SpaceX星链 Broadcom BCM2711[94]处理器 数据处理和任务控制 NVIDIA Jetson TX2[95]GPU 加速图像处理与深度学习处理 COTS NAND Flash、DRAM存储芯片 数据记录与存储,支持冗余设计与纠错机制 ADI射频前端模块、TI射频控制器 收发射频信号并进行处理 电源管理芯片功率放大器[96] 发射功率放大器 NASA CubeSat[99] 商用 S/UHF/X 波段射频通信模块 实现地面通信、数据下行与实验验证 银河航天低轨宽带通信卫星 ARM架构MCU、Xilinx Kintex-7 抗辐射FPGA 通过TMR设计保障星上逻辑稳定性,

并搭配 ARM 架构 MCU 加强控制任务[97]长光卫星中遥感卫星 COTS GPU/SoC 实时图像处理与压缩,支持高分辨率遥感任务[98] -

[1] LENTARIS G, MARAGOS K, STRATAKOS I, et al. High-performance embedded computing in space: Evaluation of platforms for vision-based navigation[J]. Journal of Aerospace Information Systems, 2018, 15(4): 178–192. doi: 10.2514/1.I010555. [2] 冯颖, 刘忠健. 单粒子效应对飞行器的影响分析及防护技术[J]. 强度与环境, 2011, 38(1): 26–30. doi: 10.3969/j.issn.1006-3919.2011.01.005.FENG Ying and LIU Zhongjian. Single event effect analysis on the spacecraft and the technique designed in the protection[J]. Structure & Environment Engineering, 2011, 38(1): 26–30. doi: 10.3969/j.issn.1006-3919.2011.01.005. [3] GUERTIN S M, SOME R, NSENGIYUMVA P, et al. Radiation specification and testing of heterogenous microprocessor SOCs[C]. 2019 19th European Conference on Radiation and Its Effects on Components and Systems, Montpellier, France, 2022: 1–7. doi: 10.1109/RADECS47380.2019.9745708. [4] 孙宝三, 章宇兵, 岳兆娟, 等. 面向服务的天基计算技术架构研究[J]. 中国电子科学研究院学报, 2018, 13(4): 427–432. doi: 10.3969/j.issn.1673-5692.2018.04.012.SUN Baosan, ZHANG Yubing, YUE Zhaojuan, et al. Study on service-oriented architecture of space-borne computing[J]. Journal of China Academy of Electronics and Information Technology, 2018, 13(4): 427–432. doi: 10.3969/j.issn.1673-5692.2018.04.012. [5] XU Mengwei, ZHANG Li, LI Hongyu, et al. A satellite-born server design with massive tiny chips towards in-space computing[C]. 2022 IEEE International Conference on Satellite Computing, Shenzhen, China, 2022: 1–6. doi: 10.1109/Satellite55519.2022.00009. [6] 董珊. 星载遥感图像实时处理专用芯片的抗辐照电路设计[D]. [硕士论文], 北京理工大学, 2016.DONG Shan. The radiation-hardened circuit design of a Space-borne remote sensing image real-time processing chip[D]. [Master dissertation], Beijing Institute of Technology, 2016. [7] BAE Systems. BAE Systems RAD6000 datasheet[EB/OL]. https://www.digchip.com/datasheets/parts/datasheet/568/RAD6000-pdf.php, 2025. [8] BEDI R. Spacecraft on-board computing using rad-hard ARM MCUs[EB/OL]. https://www.edn.com/spacecraft-on-board-computing-using-rad-hard-arm-mcus/, 2025. [9] KELLER J. NOVI chooses VORAGO radiation-hardened microcontroller for space computer that will fly on SpaceX mission[EB/OL]. https://www.militaryaerospace.com/computers/article/55093107/vorago-technologies-radiation-hardened-microcontroller-space, 2025. [10] SHILOV A. Nvidia’s Jetson AI board is ready to go to space[EB/OL]. https://www.tomshardware.com/news/nvidias-jetson-ai-board-is-ready-to-go-to-space, 2025. [11] Intel. Intel® Movidius™ Myriad™ X vision processing unit 4GB[EB/OL]. https://www.intel.com/content/www/us/en/products/sku/125926/intel-movidius-myriad-x-vision-processing-unit-4gb/specifications.html, 2025. [12] CRATERE A, GAGLIARDI L, SANCA G A, et al. On-board computer for CubeSats: State-of-the-art and future trends[J]. IEEE Access, 2024, 12: 99537–99569. doi: 10.1109/ACCESS.2024.3428388. [13] GARCÍA L P, FURANO G, GHIGLIONE M, et al. Advancements in onboard processing of synthetic aperture radar (SAR) data: Enhancing efficiency and real-time capabilities[J]. IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing, 2024, 17: 16625–16645. doi: 10.1109/JSTARS.2024.3406155. [14] HAMILTON D. Medical system design challenges for exploration class space missions[EB/OL]. https://marspapers.org/paper/Hamilton_2024.4_1.9contrib.pdf, 2025. [15] UNIBAP. SpaceCloud® iX5–106[EB/OL]. https://unibap.com/wp-content/uploads/2023/09/spacecloud-ix5-100-product-overview-v27.pdf, 2025. [16] ATMEL. Rad-hard 32-bit SPARC embedded processor, TSC695E[EB/OL]. https://pdf.dzsc.com/88889/26096.pdf, 2025. [17] ATMEL. Rad-hard 32 bit SPARC V8 processor, AT697F[EB/OL]. https://ww1.microchip.com/downloads/aemDocuments/documents/OTH/ProductDocuments/DataSheets/doc7703.pdf, 2025. [18] SJÄLANDER M, HABINC S, and GAISLER J. LEON4: Fourth generation of the LEON processor[EB/OL]. https://sjalander.com/research/pdf/sjalander-dasia2009.pdf, 2025. [19] CAES. LEON and NOEL-V SoC architectures[EB/OL]. https://www.frontgrade.com/sites/default/files/documents/Position-Paper-LEON-NOELV-SoC-Architectures-2022-02-22.pdf, 2025. [20] HE Yating, JI Xiaoyan, ZHAO Rui, et al. A software reconfiguration method for CPU of satellite-board controller[C]. SPIE 13079, Third International Conference on Testing Technology and Automation Engineering, Xi’an, China, 2023: 130790P. doi: 10.1117/12.3015550. [21] 北京微电子技术研究所. 300MHz抗辐照SPARC CPU产品使用手册[EB/OL]. https://www.manuallib.com/download/6B25900E1D2FF9CE7479DEC5434FE780.pdf, 2025.Beijing Insititute of Microelectronics. 300MHz Radiation Proof SPARC CPU Manual[EB/OL]. https://www.manuallib.com/download/ 6B25900E1D2FF9CE7479DEC5434FE780.pdf, 2025. [22] 极术社区. 我国星载、机载计算机和核心器件相关公司及水平 [OL]. https://aijishu.com/a/1060000000109171, 2025.AIJISHU. Companies and levels related to satellite-borne and airborne computers and core devices in China [OL]. https://aijishu.com/a/1060000000109171, 2025. [23] WHITTAKER A. Raspberry Pi Zero powers CubeSat space mission[EB/OL]. https://www.raspberrypi.com/news/raspberry-pi-zero-powers-cubesat-space-mission/, 2025. [24] Airbus. Defence and space: PureLine[EB/OL]. https://www.airbus.com/sites/g/files/jlcbta136/files/2024-12/Datasheet_SpE_PureLine_Amethyst_2022.pdf, 2025. [25] VORAGO. VA7230 edge computing microprocessor for space applications[EB/OL]. https://www.voragotech.com/va7230-edge-computing-microprocessor, 2025. [26] Phytium. 飞腾腾锐D2000处理器数据手册[EB/OL]. https://gitcode.com/Open-source-documentation-tutorial/fdcb3/blob/main/%E9%A3%9E%E8%85%BE%E8%85%BE%E9%94%90D2000%E5%A4%84%E7%90%86%E5%99%A8%E6%95%B0%E6%8D%AE%E6%89%8B%E5%86%8C.pdf, 2025.Phytium. Data Sheet for Feiteng Tengrui D2000 Processor [EB/OL]. https://gitcode.com/Open-source-documentation-tutorial/fdcb3/blob/main/%E9%A3%9E%E8%85%BE%E8 %85%BE%E9%94%90D2000%E5%A4%84%E7%90%86%E5 %99%A8%E6%95%B0%E6%8D%AE%E6%89%8B%E5%86%8C.pdf, 2025. [27] Phytium. FT2000/4 [OL]. https://www.phytium.com.cn/homepage/production/6/, 2025. [28] Frontgrade Gaisler. NOEL-V[EB/OL]. https://www.gaisler.com/products/noel-v, 2025. [29] NASA. NASA’s high performance spaceflight computer[EB/OL]. https://www.nasa.gov/wp-content/uploads/2024/07/hpsc-white-paper-tmg-26jun2024-final.pdf, 2025. [30] 国科安芯. MCU芯片-AS32S601数据手册[EB/OL]. https://ansilic.com/wp-content/uploads/2024/09/MCU%E8%8A%AF%E7%89%87-AS32S601%E6%95%B0%E6%8D%AE%E6%89%8B%E5%86%8C.pdf, 2025.Guoke Anxin. MCU chip-AS32S601 data manual[EB/OL]. https://ansilic.com/wp-content/uploads/2024/09/MCU%E8%8A%AF%E7%89%87-AS32S601%E6%95%B0%E6%8D%AE%E6%89%8B%E5%86%8C.pdf, 2025. [31] 胡伟武, 汪文祥, 吴瑞阳, 等. 龙芯指令系统架构技术[J]. 计算机研究与发展, 2023, 60(1): 2–16. doi: 10.7544/issn1000-1239.202220196.HU Weiwu, WANG Wenxiang, WU Ruiyang, et al. Loongson instruction set architecture technology[J]. Journal of Computer Research and Development, 2023, 60(1): 2–16. doi: 10.7544/issn1000-1239.202220196. [32] 国家航天局. “龙芯”上天 北斗有了“中国芯”[EB/OL]. https://www.cnsa.gov.cn/n6758824/n6759009/n6759043/n6759069/c6577136/content.html, 2025.National Space Administration. "Loongson" is launched into space, Beidou now has its own "Chinese core"[EB/OL]. https://www.cnsa.gov.cn/n6758824/n6759009/n6759043/n6759069/c6577136/content.html, 2025. [33] 龙芯中科. 龙芯1F处理器数据手册[EB/OL]. https://www.docin.com/p-1975324773.html, 2025.Loongson Technology. Data sheet for Loongson 1F processor[EB/OL]. https://www.docin.com/p-1975324773.html, 2025. [34] Wikipedia. Apollo guidance computer[EB/OL]. https://en.wikipedia.org/wiki/Apollo_Guidance_Computer, 2025. [35] Wikipedia. IBM RAD6000[EB/OL]. https://en.wikipedia.org/wiki/IBM_RAD6000, 2025. [36] ESA. LEON’s first flights[EB/OL]. https://www.esa.int/Enabling_Support/Space_Engineering_Technology/LEON_s_first_flights, 2025. [37] ARM. ARM and VORAGO technologies take space electronics to new heights[EB/OL]. https://newsroom.arm.com/news/arm-and-vorago-technologies-take-space-electronics-to-new-heights, 2025. [38] ESA. OPS-SAT(Operations nanoSatellite)[EB/OL]. https://www.eoportal.org/satellite-missions/ops-sat#eop-quick-facts-section, 2025. [39] MICROCHIP. High Performance 64 bit HPSC Microprocessor[OL]. 5_2_Microchip_HPSC-RiscV-Space-GTO-April-2025.pdf 2025. [40] Element14. ARM Cortex-A9 Overview [OL]. https://community.element14.com/products/devtools/technicallibrary/w/documents/9939/arm-cortex-a9-overview, 2025. [41] SiFive. SiFive Intelligence X280 [OL]. https://www.sifive.cn/cores/intelligence-x200-series, 2025. [42] 虞志刚, 冯旭, 陆洲, 等. 宇航级处理器发展现状与趋势[J]. 天地一体化信息网络, 2023, 4(1): 9. doi: 10.11959/j.issn.2096-8930.2023006.YU Zhigang, FENG Xu, LU Zhou, et al. Development Status and Trends of Space Processor[J]. Space-Integrated-Ground Information Networks, 2023, 4(1): 9. doi: 10.11959/j.issn.2096-8930.2023006. [43] GARCÉS-SOCARRÁS L M, NIK A, ORTIZ F, et al. Artificial intelligence satellite telecommunication testbed using commercial off-the-shelf chipsets[EB/OL]. arXiv: 2405.18297, https://arxiv.org/abs/2405.18297, 2024. [44] LI Lin, ZHANG Shengbing, and WU Juan. Efficient object detection framework and hardware architecture for remote sensing images[J]. Remote Sensing, 2019, 11(20): 2376. doi: 10.3390/rs11202376. [45] GEIST A, BREWER C, DAVIS M, et al. SpaceCube v3.0 NASA next-generation high-performance processor for science applications[C]. The 33rd Annual AIAA/USU Conference on Small Satellites, Logan, USA, 2019: 158. [46] XILINX. VIRTEX-5QV FPGA FAMILY[EB/OL]. https://www.xilinx.com/publications/prod_mktg/virtex5qv-product-brief.pdf, 2025. [47] XILINX. XQR Space-grade Kintex™ UltraScale™ and space heritage[EB/OL]. https://www.xilinx.com/content/dam/xilinx/publications/solution-briefs/xilinx-space-solution-brief.pdf, 2025. [48] Actel. RTAX-S testing and reliability update[EB/OL]. https://ww1.microchip.com/downloads/aemdocuments/documents/fpga/ProductDocuments/SupportingCollateral/rtaxs_rel_test_wp.pdf, 2025. [49] Microchip. RTG4TM radiation-tolerant FPGAs[EB/OL]. https://www.microchip.com/en-us/products/fpgas-and-plds/radiation-tolerant-fpgas/rtg4-radiation-tolerant-fpgas, 2025. [50] LEON V, STAMOULIAS I, LENTARIS G, et al. Development and testing on the European space-grade BRAVE FPGAs: Evaluation of NG-large using high-performance DSP benchmarks[J]. IEEE Access, 2021, 9: 131877–131892. doi: 10.1109/ACCESS.2021.3114502. [51] 俞军, 徐烈伟, 俞剑, 等. 高可靠亿门级FPGA芯片关键技术及产业化[Z]. 复旦大学, 2020.YU Jun, XU Liewei, YU Jian, et al. Key technologies and industrialization of high-reliability billion-gate FPGA chips[Z]. Fudan University, 2020. [52] KESUMA H, AHMADI-POUR S, JOSEPH A, et al. Artificial intelligence implementation on voice command and sensor anomaly detection for enhancing human habitation in space mission[C]. 2019 9th International Conference on Recent Advances in Space Technologies, Istanbul, Turkey, 2019: 579–584. doi: 10.1109/RAST.2019.8767447. [53] SABOGAL S, GEORGE A, and CRUM G. ReCoN: A reconfigurable CNN acceleration framework for hybrid semantic segmentation on hybrid SoCs for space applications[C]. 2019 IEEE Space Computing Conference, Pasadena, USA, 2019: 41–52. doi: 10.1109/SpaceComp.2019.00010. [54] 航宇微. 高性能嵌入式AI处理器Yulong810A简介[EB/OL]. https://www.myorbita.net/uploadfiles/2024/10/2024102316010919.pdf, 2025.Aero-Chips. Introduction to high-performance embedded AI processor Yulong810A[EB/OL]. https://www.myorbita.net/uploadfiles/2024/10/2024102316010919.pdf, 2025. [55] 新华网浙江. 之江实验室发布多项科技成果 [OL]. http://zj.news.cn/20231213/2acf7245447b4acab471834e3e45d540/c.html, 2025.XINHUANET. Zhijiang Laboratory releases multiple scientific and technological achievements [OL]. http://zj.news.cn/20231213/2acf7245447b4acab471834e3e45d540/c.html, 2025. [56] PERSYN S C, MCLELLAND M, EPPERLY N, et al. Evolution of digital signal processing based spacecraft computing solutions[C]. IEEE Aerospace Conference, Big Sky, USA, 2002: 4. doi: 10.1109/AERO.2002.1036902. [57] CORDIS. DSP for space applications[EB/OL]. https://cordis.europa.eu/project/id/262798/reporting, 2025. [58] ADAMS C, SPAIN A, PARKER J, et al. Towards an integrated GPU accelerated SoC as a flight computer for small satellites[C]. 2019 IEEE Aerospace Conference, Big Sky, USA, 2019: 1–7. doi: 10.1109/AERO.2019.8741765. [59] WANG Mi, ZHANG Zhiqi, ZHU Ying, et al. Embedded GPU implementation of sensor correction for on-board real-time stream computing of high-resolution optical satellite imagery[J]. Journal of Real-Time Image Processing, 2018, 15(3): 565–581. doi: 10.1007/s11554-017-0741-0. [60] ZHANG Zhiqi, WEI Lu, XIANG Shao, et al. Task-driven onboard real-time panchromatic multispectral fusion processing approach for high-resolution optical remote sensing satellite[J]. IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing, 2023, 16: 7636–7661. doi: 10.1109/JSTARS.2023.3305231. [61] MATSUO I B M, ZHAO Long, and LEE W J. A dual modular redundancy scheme for CPU–FPGA platform-based systems[J]. IEEE Transactions on Industry Applications, 2018, 54(6): 5621–5629. doi: 10.1109/TIA.2018.2859386. [62] SIM M T and ZHUANG Yanyan. A dual lockstep processor system-on-a-chip for fast error recovery in safety-critical applications[C]. IECON 2020 the 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, Singapore, 2020: 2231–2238. doi: 10.1109/IECON43393.2020.9255188. [63] FUCHS C M, CHOU Pai, WEN Xiaoqing, et al. A fault-tolerant MPSoC For CubeSats[C]. 2019 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, Noordwijk, Netherlands, 2019: 1–6. doi: 10.1109/DFT.2019.8875417. [64] CALDWELL D W and RENNELS D A. A minimalist fault-tolerant microcontroller design for embedded spacecraft computing[J]. The Journal of Supercomputing, 2000, 16(1/2): 7–25. doi: 10.1023/A:1008142728784. [65] GEIST A, BREWER C, DAVIS M, et al. SpaceCube v3.0 NASA next-generation high-performance processor for science applications[C]. The 33rd Annual AIAA/USU Conference on Small Satellites, Logan, USA, 2019. [66] HARIKRISHNAN P, KARRAS K, CRUZ N, et al. SpaceWire based reconfiguration and redundancy management of COTS based highly integrated onboard computer[C]. 2023 European Data Handling & Data Processing Conference, Juan Les Pins, France, 2023: 1–6. doi: 10.23919/EDHPC59100.2023.10396158. [67] PENG Qiao, WAN Xiaoguo, and ZHANG Jiliang. FOSA: A highly fault-tolerant operating system architecture[C]. 2024 IEEE International Test Conference in Asia, Changsha, China, 2024: 1–6. doi: 10.1109/ITC-Asia62534.2024.10661344. [68] 张吉良, 柴先平, 王爽, 等. 一种软错误防护方法、装置、设备及存储介质[P]. 中国, CN202310715223.5, 2023.ZHANG Jiliang, CHAI Xianping, WANG Shuang, et al. Soft error protection method and device, equipment and storage medium[P]. CN, CN202310715223.5, 2023. [69] FUCHS C M, STEFANOV T P, MURILLO N M, et al. Bringing fault-tolerant Gigahertz-computing to space: A multi-stage software-side fault-tolerance approach for miniaturized spacecraft[C]. 2017 IEEE 26th Asian Test Symposium, Taipei, China, 2017: 100–107. doi: 10.1109/ATS.2017.30. [70] ROGENMOSER M, WIESE P, FORLIN B E, et al. Trikarenos: Design and experimental characterization of a fault-tolerant 28-nm RISC-V-based SoC[J]. IEEE Transactions on Nuclear Science, 2025, 72(8): 2783–2792. doi: 10.1109/TNS.2025.3564739. [71] ROGENMOSER M, TORTORELLA Y, ROSSI D, et al. Hybrid modular redundancy: Exploring modular redundancy approaches in RISC-V multi-core computing clusters for reliable processing in space[J]. ACM Transactions on Cyber-Physical Systems, 2025, 9(1): 8. doi: 10.1145/3635161. [72] ROGENMOSER M, WISTOFF N, VOGEL P, et al. On-demand redundancy grouping: Selectable soft-error tolerance for a multicore cluster[C]. 2022 IEEE Computer Society Annual Symposium on VLSI, Nicosia, Cyprus, 2022: 398–401. doi: 10.1109/ISVLSI54635.2022.00089. [73] DÖRFLINGER A, Guan Yejun, MICHALIK S, et al. ECC memory for fault tolerant RISC-V processors[C]. The 33rd International Conference on Architecture of Computing Systems, Aachen, Germany, 2020: 44–55. doi: 10.1007/978-3-030-52794-5_4. [74] FIFIELD J A and STAPPER C H. High-speed on-chip ECC for synergistic fault-tolerance memory chips[J]. IEEE Journal of Solid-State Circuits, 1991, 26(10): 1449–1452. doi: 10.1109/4.90100. [75] LEROUX P. Radiation tolerant electronics[J]. Electronics, 2019, 8(7): 730. doi: 10.3390/electronics8070730. [76] NICOLAIDIS M. Design for soft error mitigation[J]. IEEE Transactions on Device and Materials Reliability, 2005, 5(3): 405–418. doi: 10.1109/TDMR.2005.855790. [77] BAUMANN R C. Radiation-induced soft errors in advanced semiconductor technologies[J]. IEEE Transactions on Device and Materials Reliability, 2005, 5(3): 305–316. doi: 10.1109/TDMR.2005.853449. [78] SLAYMAN C W. Cache and memory error detection, correction, and reduction techniques for terrestrial servers and workstations[J]. IEEE Transactions on Device and Materials Reliability, 2005, 5(3): 397–404. doi: 10.1109/TDMR.2005.856487. [79] LU Zhaojun, ZHAO Qi, CHEN Qidong, et al. A survey on fault-tolerance methods for SRAM-based FPGAs in radiation environments[C]. 2023 IEEE 32nd Asian Test Symposium, Beijing, China, 2023: 1–6. doi: 10.1109/ATS59501.2023.10318028. [80] SCHWANK J R, FERLET-CAVROIS V, SHANEYFELT M R, et al. Radiation effects in SOI technologies[J]. IEEE Transactions on Nuclear Science, 2003, 50(3): 522–538. doi: 10.1109/TNS.2003.812930. [81] LIU Jia, LI Yao, ZHANG Ruitao, et al. Development of a radiation-hardened standard cell library for 65nm CMOS technology[C]. 2016 China Semiconductor Technology International Conference, Shanghai, China, 2016: 1–3. doi: 10.1109/CSTIC.2016.7464080. [82] GREESHMA N and JAMUNA S. Design and analysis of radiation hardened by design non-volatile RAM for space applications[J]. International Journal of Scientific and Research Publications, 2023, 13(6): 397–409. doi: 10.29322/IJSRP.13.06.2023.p13848. [83] LEYVA-MAYORGA I, MARTINEZ-GOST M, MORETTI M, et al. Satellite edge computing for real-time and very-high resolution earth observation[J]. IEEE Transactions on Communications, 2023, 71(10): 6180–6194. doi: 10.1109/TCOMM.2023.3296584. [84] WANG Yixin, QIU Xiaolan, and WEN Xuejiao. High-resolution SAR imaging characteristics for multiple scattering of rotating targets[J]. IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing, 2024, 17: 9974–9988. doi: 10.1109/JSTARS. 2024.3382038. doi: 10.1109/JSTARS.2024.3382038. doi: 10.1109/JSTARS.2024.3382038.doi:10.1109/JSTARS.2024.3382038. [85] LIU Haoting. Autonomous navigation for mars exploration[M]. PEZZELLA G and VIVIANI A. Mars Exploration - A Step Forward. IntechOpen, 2020. doi: 10.5772/intechopen.92093. [86] ZHANG Qinyu, XU Liang, HUANG Jianhao, et al. Distributed satellite information networks: Architecture, enabling technologies, and trends[J]. Science China Information Sciences, 2025, 68(8): 190301. doi: 10.1007/s11432-024-4408-1. [87] Advanced Cooling Technologies. VME/VPX card frames[EB/OL]. https://www.1-act.com/thermal-solutions/embedded-computing/vme-vpx/, 2025. [88] 薄鹏, 汪悦. 面向航天器型号的COTS元器件选用策略[J]. 航天器环境工程, 2023, 40(4): 430–436. doi: 10.12126/see.2023102.BAO Peng and WANG Yue. Selection strategy of COTS components for spacecraft[J]. Spacecraft Environment Engineering, 2023, 40(4): 430–436. doi: 10.12126/see.2023102. [89] 张泽明, 张楠. 航天任务中宇航级和COTS元器件的比较和选择[J]. 环境技术, 2023, 41(7): 75–79. doi: 10.3969/j.issn.1004-7204.2023.07.016.ZHANG Zeming and ZHANG Nan. Comparison and selection of space-grade and COTS components in space missions[J]. Environmental Technology, 2023, 41(7): 75–79. doi: 10.3969/j.issn.1004-7204.2023.07.016. [90] 侯小宇. 符合我国航空工业发展现状的COTS IP适航要求研究与探索[J]. 民航学报, 2022, 6(4): 82–88,95. doi: 10.3969/j.issn.2096-4994.2022.04.019.HOU Xiaoyu. Research on and exploration of COTS IP airworthiness requirements for China’s aviation industry[J]. Journal of Civil Aviation, 2022, 6(4): 82–88,95. doi: 10.3969/j.issn.2096-4994.2022.04.019. [91] 姜盛鑫, 韩天龙, 施帆, 等. 航天COTS产品标准化发展的透视与浅析[J]. 航天标准化, 2022(1): 36–39,49. doi: 10.19314/j.cnki.1009-234x.2022.01.005.JIANG Shengxin, HAN Tianlong, SHI Fan, et al. Perspective and analysis of the standardization development of COTS for space[J]. Aerospace Standardization, 2022(1): 36–39,49. doi: 10.19314/j.cnki.1009-234x.2022.01.005. [92] NASA. Commercial orbital transportation services: A new era in spaceflight[EB/OL]. https://www.nasa.gov/wp-content/uploads/2016/08/sp-2014-617.pdf, 2025. [93] DOUGLAS S, MAJEWICZ P. Enabling COTS EEEE parts for NASA missions[EB/OL]. https://ntrs.nasa.gov/api/citations/20250001580/downloads/MRQW_20250001580_v2.pdf, 2025. [94] Raspberry Pi. Raspberry Pi processors[EB/OL]. https://www.raspberrypi.com/documentation/computers/processors.html, 2025. [95] NVIDIA. Jetson TX2 module[EB/OL]. https://developer.nvidia.com/embedded/jetson-tx2, 2025. [96] RAMOS R. New tech Tuesdays: Starlink: The satellite-based internet service by SpaceX[EB/OL]. https://my.mouser.com/blog/new-tech-starlink-satellite-based-internet, 2025. [97] 安信证券. 航天产业研究: 卫星互联网蓄势待发[EB/OL]. https://file.iyanbao.com/pdf/d9d90-e3cc170f-bd84-4f31-8692-a4499289d9bb.pdf, 2025.Essence Securities. Aerospace industry research: Satellite internet is ready to take off[EB/OL]. https://file.iyanbao.com/pdf/d9d90-e3cc170f-bd84-4f31-8692-a4499289d9bb.pdf, 2025. [98] 星测未来. 高性能计算助力卫星智能化[EB/OL]. https://mp.weixin.qq.com/s/mbQT4VkcI-i7iUJysnYXJw, 2025.StarDetect. High-performance computing powers satellite intelligence[EB/OL]. https://mp.weixin.qq.com/s/mbQT4VkcI-i7iUJysnYXJw, 2025. [99] VASKA C, et al. The Cubesat communication platform (CCP) – mission overview and ConOps[C]. The 16th International Conference on Space Operations 2021, 2021. [100] WEIGAND R. RISC-V: A rising star in space[EB/OL]. http://microelectronics.esa.int/papers/PresentationSummit-EUR-RISC-V-RisingStarInSpace-2023-06-08.pdf, 2025. [101] FURANO G, TAVOULARIS A, and ROVATTI M. AI in space: Applications examples and challenges[C]. 2020 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, Frascati, Italy, 2020: 1–6. doi: 10.1109/DFT50435.2020.9250908. [102] MALONE S, SAENZ P, and PHELAN P. RISC-V processors for spaceflight embedded platforms[C]. 2023 IEEE Aerospace Conference, Big Sky, USA, 2023: 1–11. doi: 10.1109/AERO55745.2023.10115850. [103] WILSON C. SpaceCube v3.0 mini[EB/OL]. https://ntrs.nasa.gov/api/citations/20190027308/downloads/20190027308.pdf, 2025. [104] 香港航天科技集团. 香港航天科技与中国科学院上海微系统与信息技术研究所合作[EB/OL]. https://www.prnasia.com/story/332577-1.shtml, 2025.Hong Kong Aerospace Technology Group. Hong Kong aerospace technology collaborates with the Shanghai Institute of Microsystems and information technology, Chinese Academy of Sciences[EB/OL]. https://ntrs.nasa.gov/api/citations/20190027308/downloads/20190027308.pdf, 2025. -

下载:

下载:

下载:

下载: