A 2 pJ/bit, 4×112 Gbps PAM4 linear driver for MZM in LPO Application

-

摘要: 针对 AI 数据中心对光模块高集成度、低功耗的要求,该文提出连续时间线性均衡器(CTLE)与可变增益放大器联合设计的电流复用架构,将传统马赫曾德尔调制器驱动器的四级结构简化为两级;输出级采用集电极开路结构使输出级功耗降低一半。该文还首次提出高低频响应独立可调的 CTLE 架构,通过低频增益补偿有效抑制趋肤效应引起的非线性失真,通过高频增益调节有效补偿传输线的高频损耗。该芯片基于130 nm BiCMOS 工艺流片,芯片具有4个通道,每个通道最大通信速率为112 Gbps。测试结果表明,该驱动器达到最大增益19.49 dB、增益可调节范围 13 dB、最大峰值增益9.2 dB、差分输出摆幅3 Vppd和总谐波失真低于3.5%,眼图线性度达到0.95,芯片功耗低至 225.23 mW,达到2 pJ/bit 的超高能效。实现了线性驱动可插拔光模块等应用场景所需的高性能与低功耗平衡。

-

关键词:

- 线性驱动可插拔光模块 /

- 马赫曾德尔调制器驱动器 /

- 连续时间线性均衡器 /

- 四电平脉冲幅度调制 /

- 电流复用

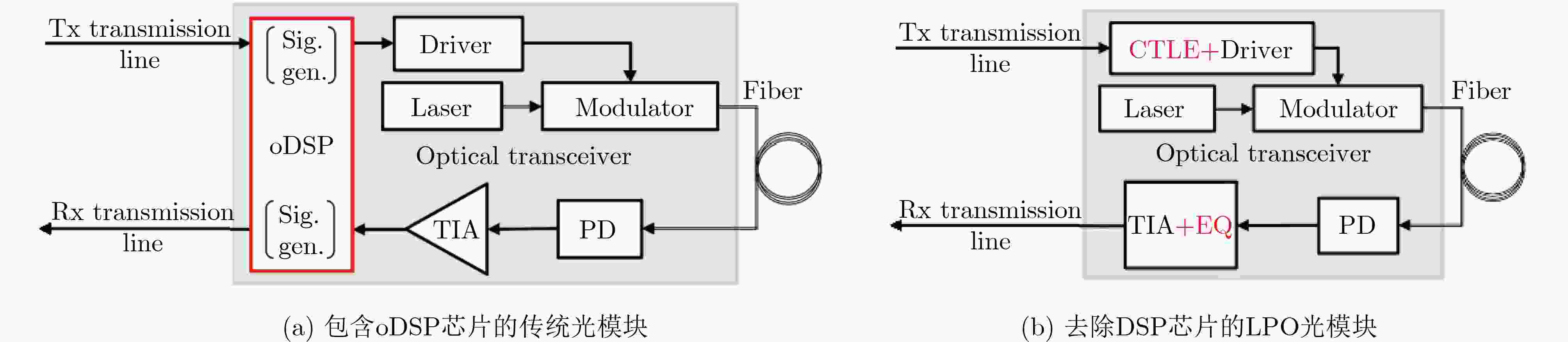

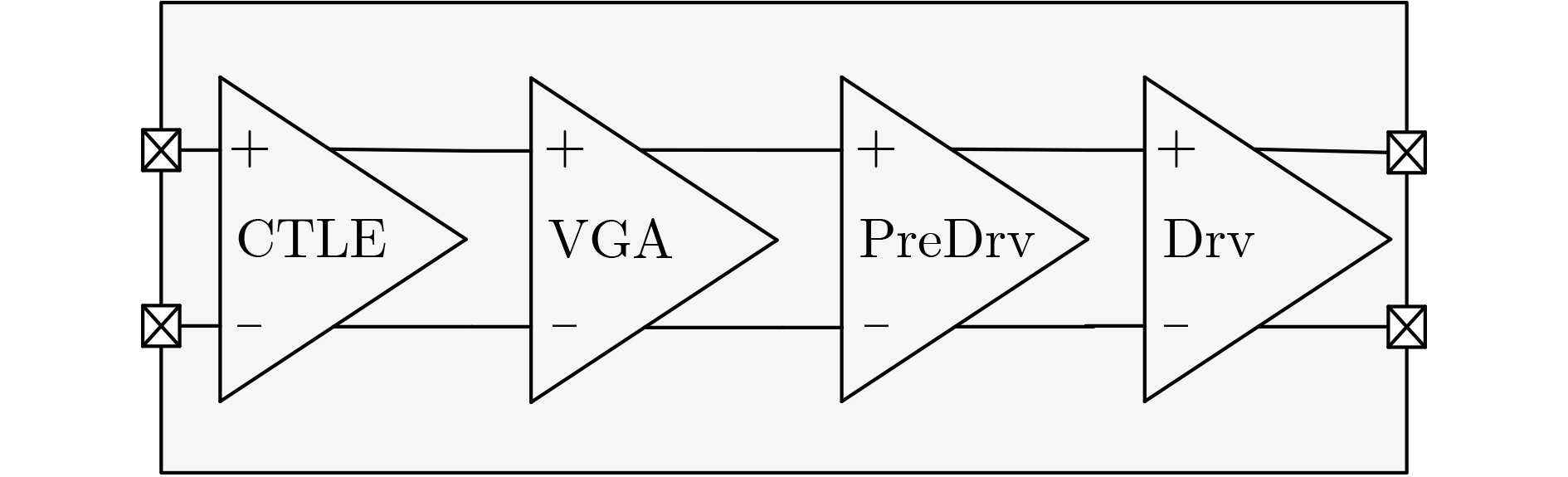

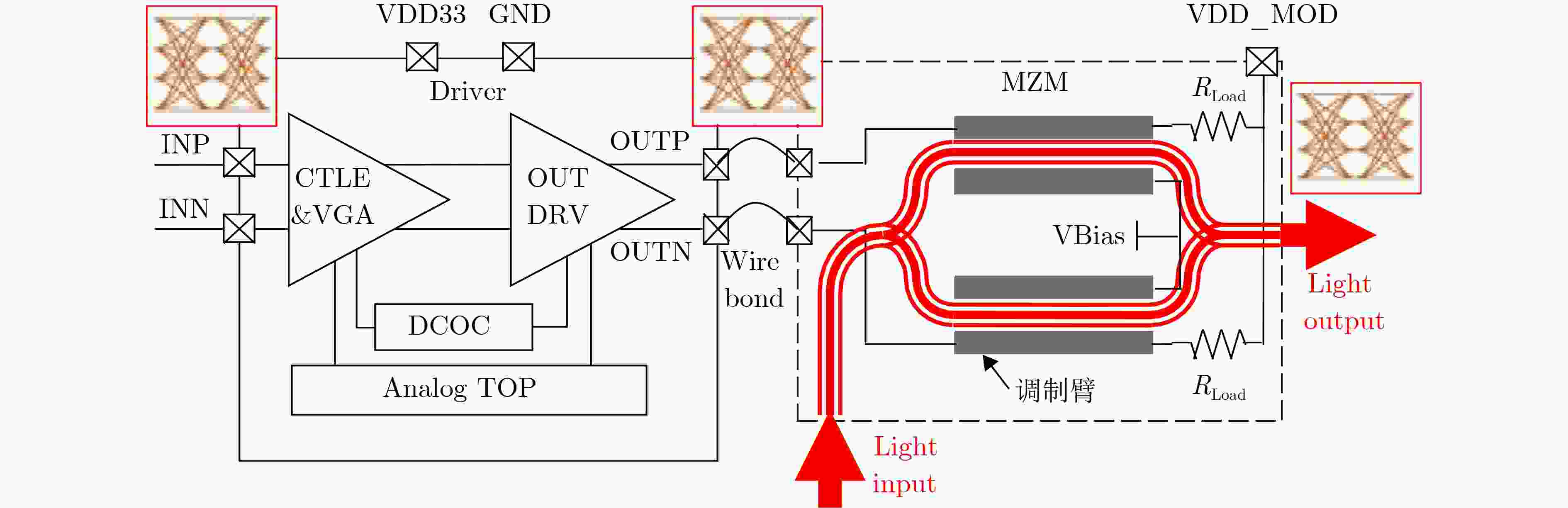

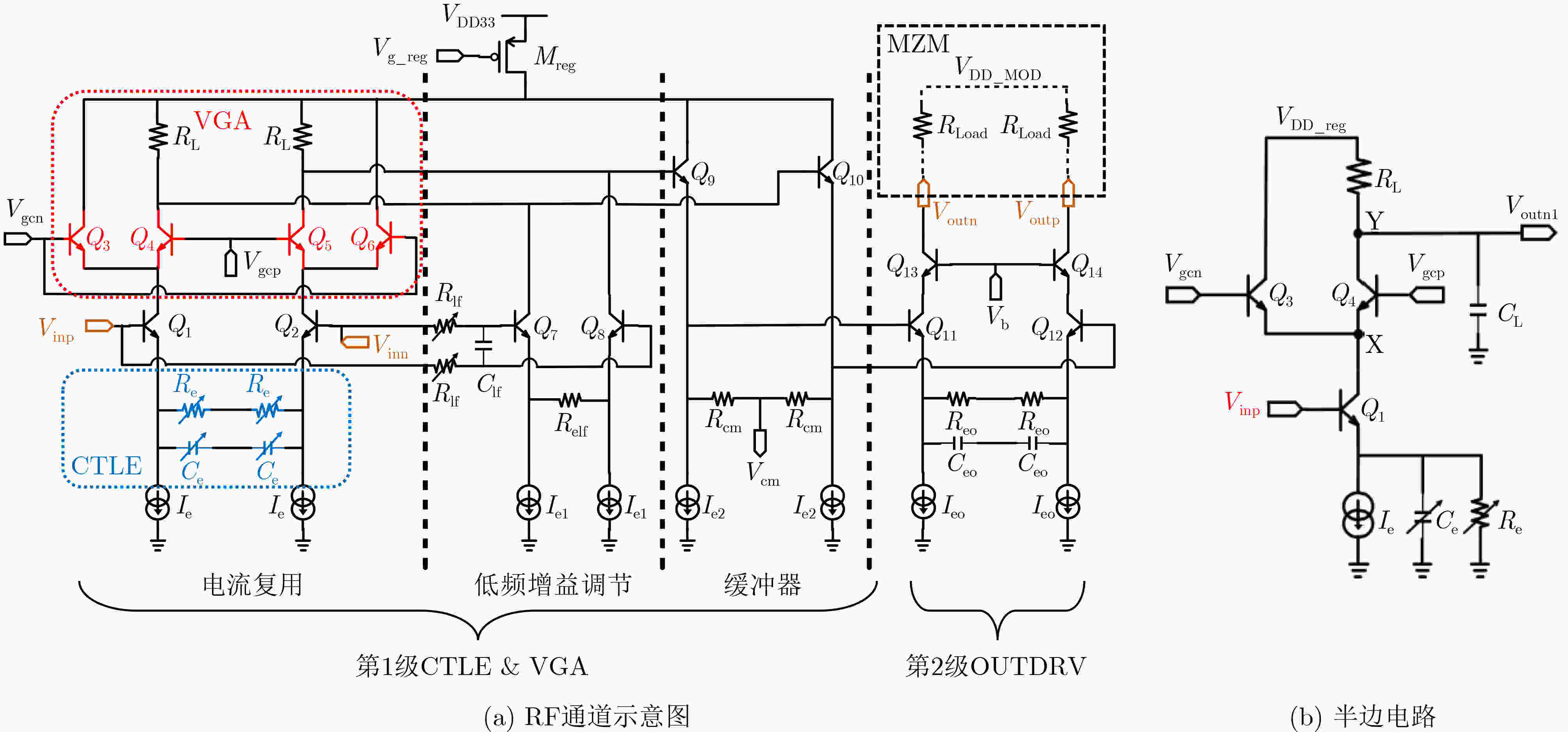

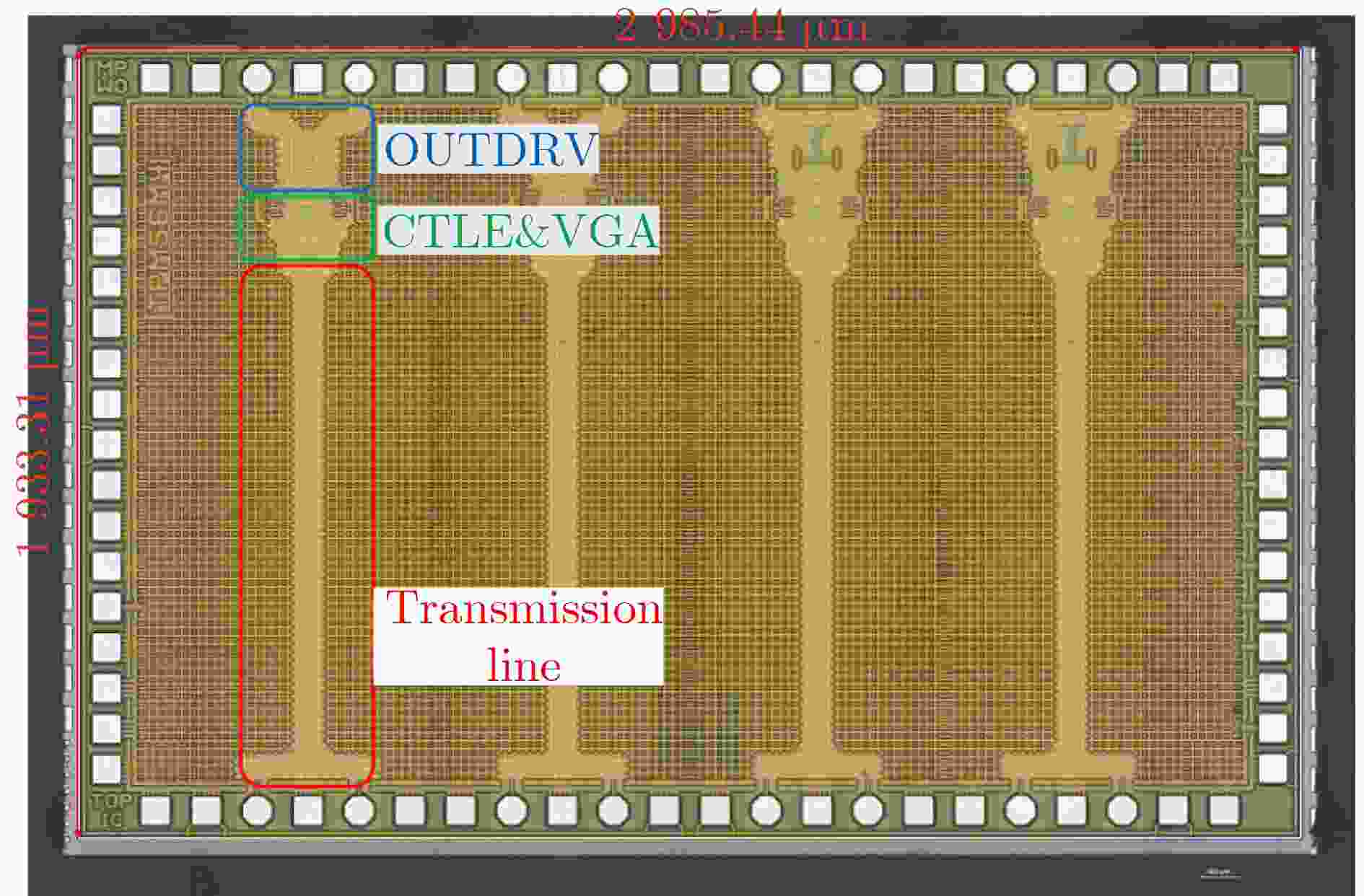

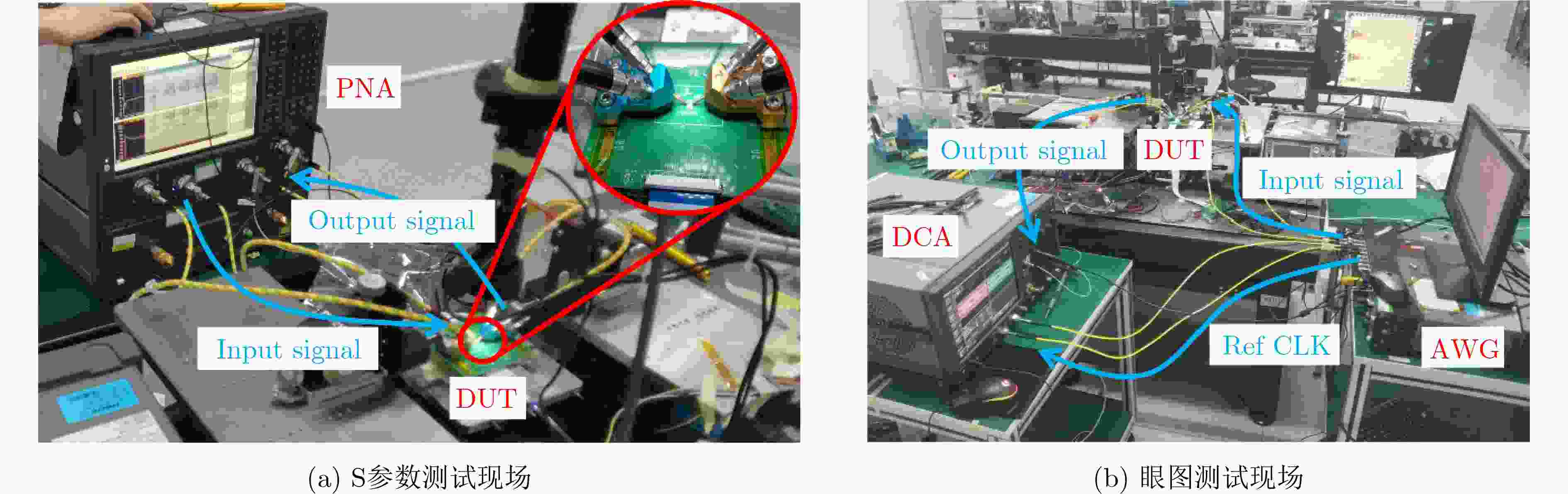

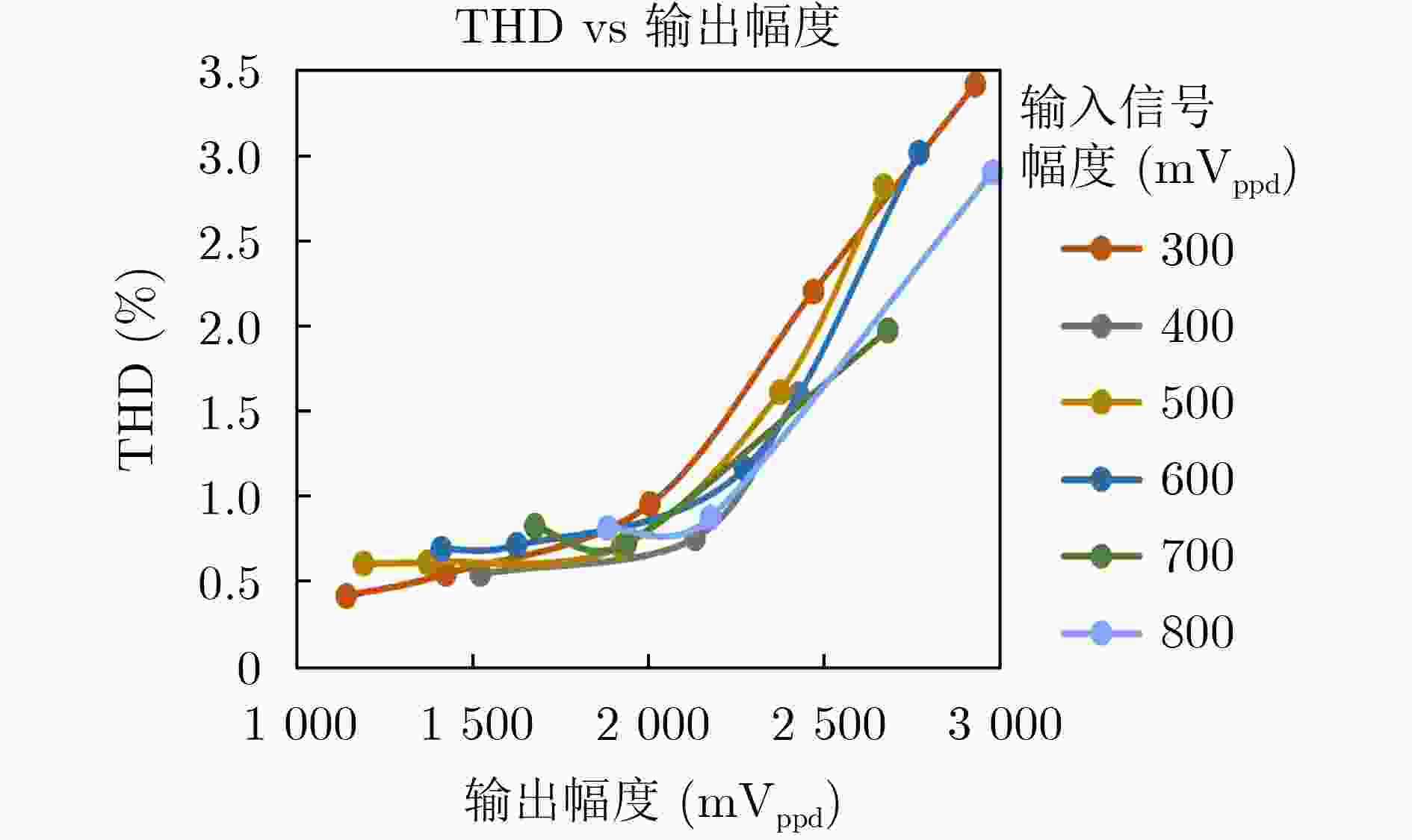

Abstract:Objective The rapid increase in data transmission demands, driven by big data, cloud computing, and Artificial Intelligence (AI), requires advanced optical module technologies capable of supporting higher data rates, such as 800 Gbps. Conventional optical modules depend on power-intensive Digital Signal Processors (DSPs) for signal compensation, which increases cost, complexity, and energy consumption. This study addresses these limitations by proposing a Linear Driver Pluggable Optics (LPO) solution that eliminates the DSP while preserving high performance. The primary objective is to design a low-power, high-efficiency Mach–Zehnder Modulator (MZM) driver using 130 nm SiGe BiCMOS technology for 400 Gbps PAM4 applications. The design integrates Continuous-Time Linear Equalization (CTLE) and gain control to support reliable, cost-effective, and energy-efficient data transmission. Methods The proposed quad-channel MZM driver adopts a two-stage architecture: a merged Continuous-Time Linear Equalizer (CTLE) and Variable Gain Amplifier (VGA) stage (Stage 1), and an output driver (OUTDRV) stage (Stage 2). By integrating CTLE and VGA functions ( Fig. 3 ), the design removes the pre-driver stage, improves current reuse, and enhances drive capability. Stage 1 employs a Gilbert cell-based core amplifier (Fig. 5a ) with programmable peaking via Re and Ce, enabling a transfer function with adjustable gain ($ \eta $) and peaking characteristics (Eq. 1). A novel low-frequency gain adjustment branch (Fig. 6 ) mitigates nonlinearity induced by conductor loss (Fig. 4 ), resulting in a flattened frequency response (Eq. 2). Stage 2 uses a cascode open-drain output structure to achieve a 3 Vppd swing at 56 Gbaud while reducing power consumption. Simulations and measurements confirm the design’s performance, with key metrics including S-parameters, Total Harmonic Distortion (THD), and Transmitter Dispersion Eye Closure for PAM4 (TDECQ).Results and Discussions The driver achieves a maximum gain of 19.49 dB with 9.2 dB peaking and a 12.57 dB gain control range. Measured S-parameters ( Fig. 9 ) confirm the 19.49 dB gain, 47 GHz bandwidth, and a 4.4 dB programmable peaking range. The low-frequency adjustment circuit reduces gain by 1.6 dB below 3 GHz (Fig. 9c ), effectively compensating for distortion caused by the skin effect. THD remains below 3.5% across input swings of 300~800 mVppd (Fig. 10 ). Eye diagrams (Fig. 11 ) demonstrate 56 Gbaud PAM4 operation, achieving a 3 Vppd output swing with TDECQ below 2.57 dB. The driver achieves a power efficiency of 2 pJ/bit (225.23 mW per channel), outperforming previous designs (Table 1 ). The use of a single 3.3 V supply eliminates the need for external DC-DC converters, facilitating system integration. Compared with recent drivers [11,14–16], this work demonstrates the highest data rate (112 Gb/s via PAM4) implemented in a mature 130 nm process while maintaining the lowest power consumption per bit.Conclusions This study presents a high-performance, energy-efficient MZM driver designed for LPO-based 400 Gbps optical modules. Key contributions include the merged CTLE–VGA architecture for optimized current reuse, a low-frequency gain adjustment technique that mitigates skin effect distortion, and a cascode output stage that achieves high swing and linearity. Measured results are consistent with simulations, confirming 19.49 dB gain, 3 Vppd output swing, and 2 pJ/bit energy efficiency. The elimination of DSPs, compatibility with cost-effective BiCMOS technology, and improved power performance highlight the driver’s potential for deployment in next-generation data centers and high-speed optical interconnects. -

图 1 传统光模块与LPO光模块对比[6]

表 1 近年发表的驱动器性能比较

本文 文献[11] 文献[14] 文献[15] 文献[16] 工艺节点 130 nm BiCMOS 55 nm BiCMOS 28 nm CMOS 90 nm BiCMOS 65 nm CMOS Peak (dB) 9.2 10 – – – 低频响应优化 Yes No No No No 速率 (Gb/s) 112 100 28 112 50 带宽 (GHz) 47 36.3 – 42.1 28.5 数据格式 PAM4 PAM4 PAM4 PAM4 NRZ 电源 (V) 3.3 2.5 1.2, 2.4 5 – 输出摆幅 (Vppd) 3 2 2.4 3.6 4 功耗 (mW) 225.3 385 88 905 267 能量效率 (pJ/bit) 2 3.85 3.14 8.05 5.35 FoM [pJ/(bit·Vppd)] 0.67 1.93 1.31 2.24 1.34 -

[1] NOWELL M and ROBERTS E. 400G, 800G, and terabit pluggable optics: What you need to know[EB/OL]. https://www.ciscolive.com/c/dam/r/ciscolive/global-event/docs/2024/pdf/BRKOPT-2699.pdf, 2024. [2] TARTAGLIA A, CAVALIERE F, LOSTEDT M, et al. Perspectives for co-packaged optics in radio access networks[C]. 2023 23rd International Conference on Transparent Optical Networks (ICTON), Bucharest, Romania, 2023: 1–7. doi: 10.1109/ICTON59386.2023.10207522. [3] MINKENBERG C, KRISHNASWAMY R, ZILKIE A, et al. Co-packaged datacenter optics: Opportunities and challenges[J]. IET Optoelectronics, 2021, 15(2): 77–91. doi: 10.1049/ote2.12020. [4] Arista: 800G LPO[EB/OL]. https://www.ecocexhibition.com/wp-content/uploads/Arista-Networks-ECOC-2023-LPO_.pdf, 2024. [5] BEN-HAMIDA N, GHARAN S O, ABDO A, et al. From analog coherent optics to linear drive pluggable optics: Lessons learnt[C]. Signal Processing in Photonic Communications 2024, Québec City, Canada, 2024. doi: 10.1364/SPPCOM.2024.SpTh1H.3. [6] CHOU E S, HUANG Yishen, AMIRALIZADEH S, et al. 100G and 200G per lane linear drive optics for data center applications[C]. 2024 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, USA, 2024: 1–3. doi: 10.1364/OFC.2024.W4H.3. [7] SVENSSON C and DERMER G H. Time domain modeling of lossy interconnects[J]. IEEE Transactions on Advanced Packaging, 2001, 24(2): 191–196. doi: 10.1109/6040.928754. [8] ZHANG G, LIAO Yu, MA E, et al. 25G long reach cable link system equalization optimization[C]. DesignCon 2016: Where the Chip Meets the Board, Santa Clara, California, USA, 2016. [9] KONG Weikun, CHEN Wenbo, ZHONG Cheng, et al. A study on transmission loss of build-up film applied to IC substrate[C]. 2023 24th International Conference on Electronic Packaging Technology (ICEPT), Shihezi City, China, 2023: 1–5. doi: 10.1109/ICEPT59018.2023.10492264. [10] HAO Kai, HE Jian, LI Leliang, et al. A 28GBaud high-swing linear Mach-Zehnder modulators driver for PAM-4 and coherent optical communications[C]. 2020 IEEE International Conference on Integrated Circuits, Technologies and Applications, Nanjing, China, 2020: 94–95. doi: 10.1109/ICTA50426.2020.9332018. [11] BREYNE L, RAMON H, VAN GASSE K, et al. 50 GBd PAM4 transmitter with a 55nm SiGe BiCMOS driver and silicon photonic segmented MZM[J]. Optics Express, 2020, 28(16): 23950–23960. doi: 10.1364/OE.397765. [12] RAZAVI B. Design of Analog CMOS Integrated Circuits[M]. 2nd ed. New York, US: McGraw-Hill Education, 2017: 126–128. [13] RAZAVI B. Design of Integrated Circuits for Optical Communications[M]. 2nd ed. Hoboken, US: Wiley, 2012: 140–143. [14] KIM M, KWON D H, RHO D W, et al. A low-power 28-Gb/s PAM-4MZM driver with level pre-distortion[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2021, 68(3): 908–912. doi: 10.1109/TCSII.2020.3020128. [15] FAN Wentian, CHEN Yingmei, CUI Haojie, et al. A 56Gbaud PAM-4 linear driver for Mach-Zehnder Modulators in 90-nm SiGe BICMOS technology[C]. 2022 3rd Asia Symposium on Signal Processing (ASSP), Singapore, Singapore, 2022: 51–55. doi: 10.1109/ASSP57481.2022.00016. [16] SHI Jingbo, LIU Han, YANG Tao, et al. An 800G integrated silicon-photonic transmitter based on 16-channel Mach-Zehnder Modulator and co-designed 5.35pJ/bit CMOS drivers[C]. 2023 IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, USA, 2023: 1–4. doi: 10.1109/ISCAS46773.2023.10181563. -

下载:

下载:

下载:

下载: