Low-Power Multi-Node Radiation-Hardened SRAM Design for Aerospace Applications

-

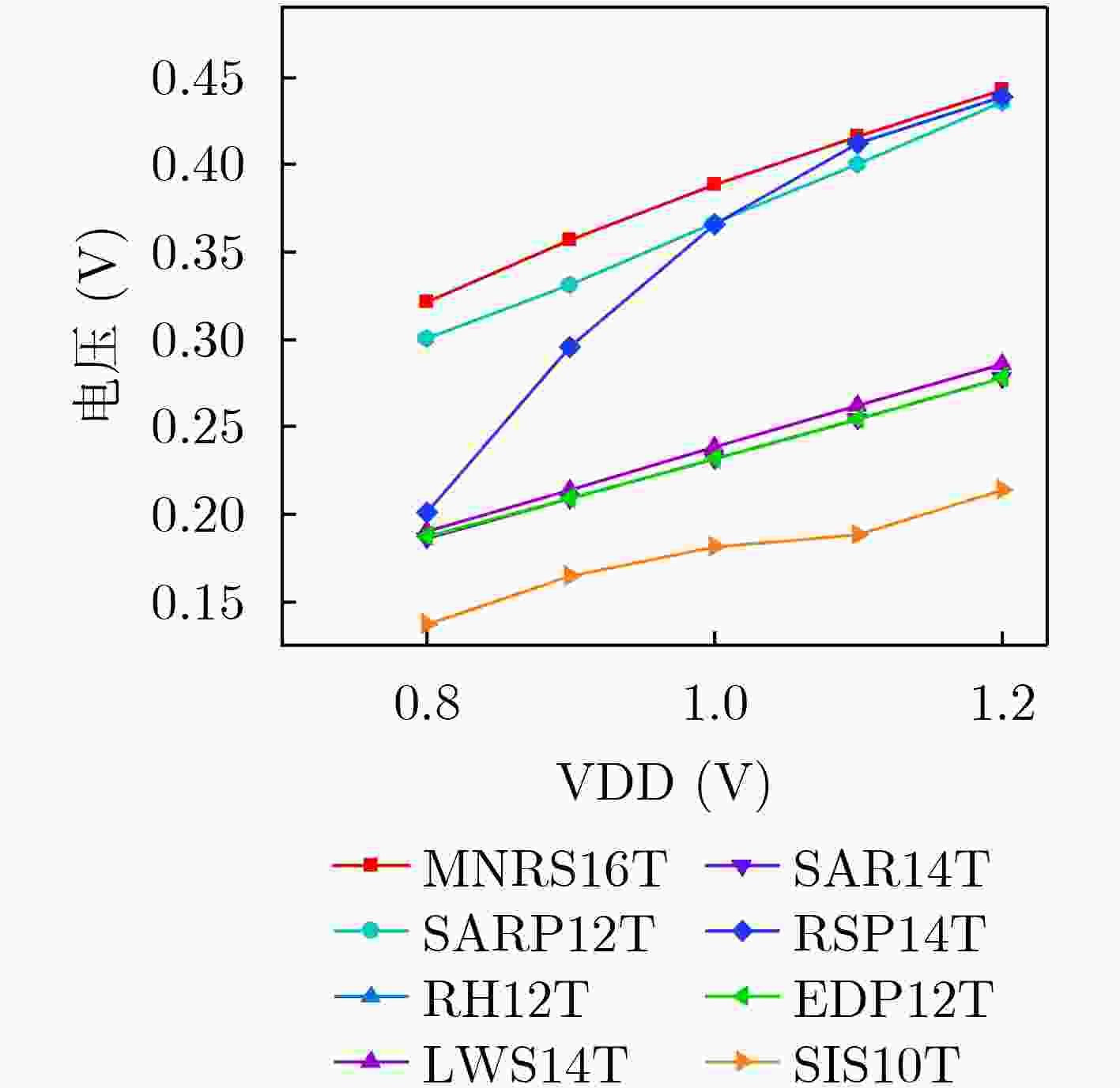

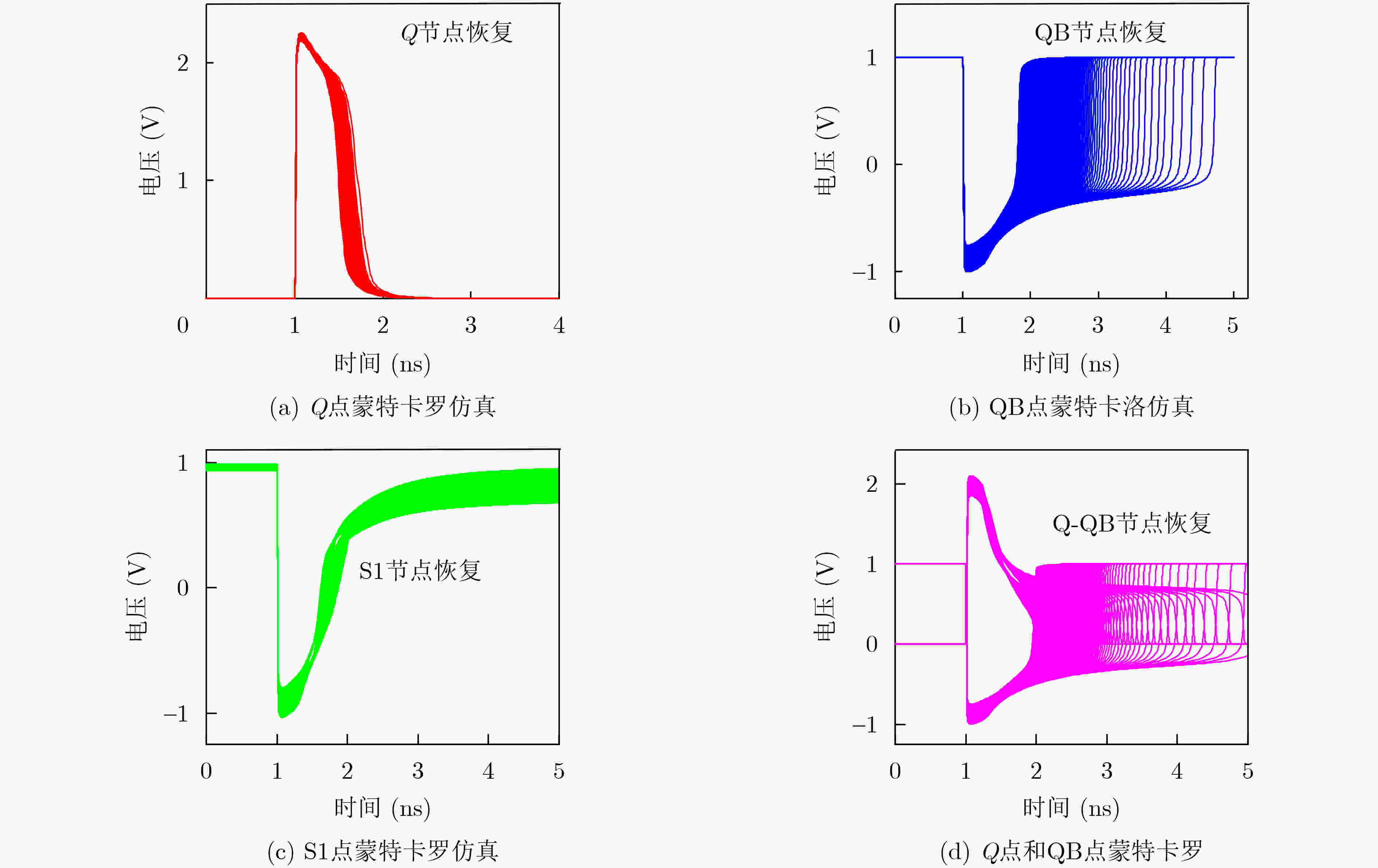

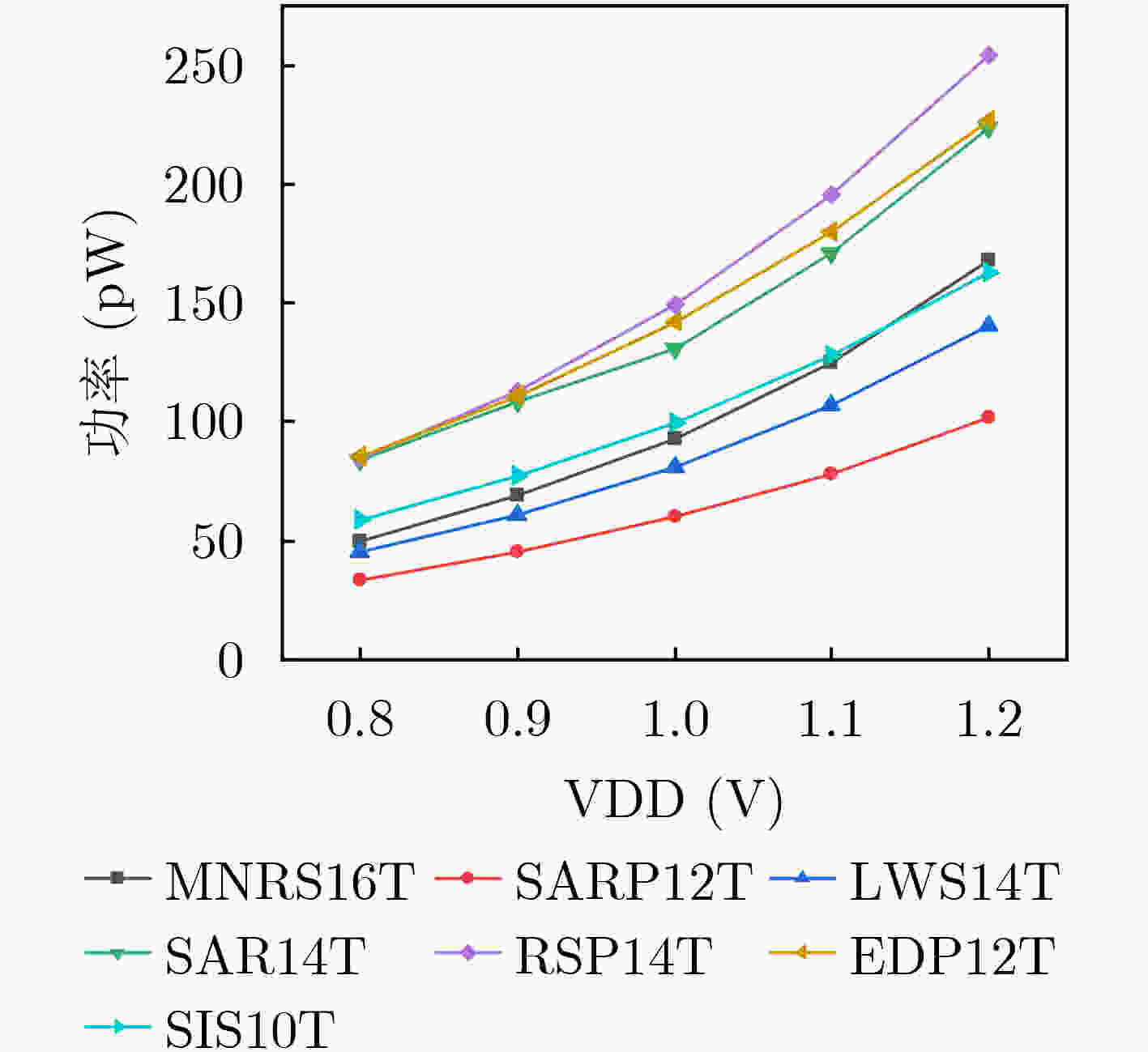

摘要: 随着对太空的探索的深入,人们发现应用于航天领域的静态随机存取存储器(SRAM)易受到高能粒子轰击发生电节点翻转(SEU)和多节点翻转(SEMNU)。该文为解决SRAM的单粒子翻转问题提出一种16TSRAM单元可以用于SRAM的抗翻转应用,该单元包含3个敏感节点,使用金属氧化物半导体(MOS)管堆叠结构,较大提高了单元的稳定性。在65 nm CMOS工艺下仿真证明该单元可以解决SEU和SEMNU问题。相比于SARP12T, LWS14T, SAR14T, RSP14T, EDP12T和SIS10T, MNRS16T的保持静态噪声容限(HSNM)分别提升了1.4%, 54.9%, 58.9%, 0.7%, 59.1%和107.4%。相比于SARP12T, RH12T, SAR14T, RSP14T, S8N8P16T, EDP12T和SIS10T, MNRS16T的读取静态噪声容限(RSNM)分别提升了94.3%, 31.4%, 90.3%, 8.9%, 71.5%, 90.4%和90.3%。相较于SAR14T, RSP14T和EDP12T, MNRS16T的保持功率(Hpwr)降低了24.7%, 33.9% 和25.7%。Abstract:

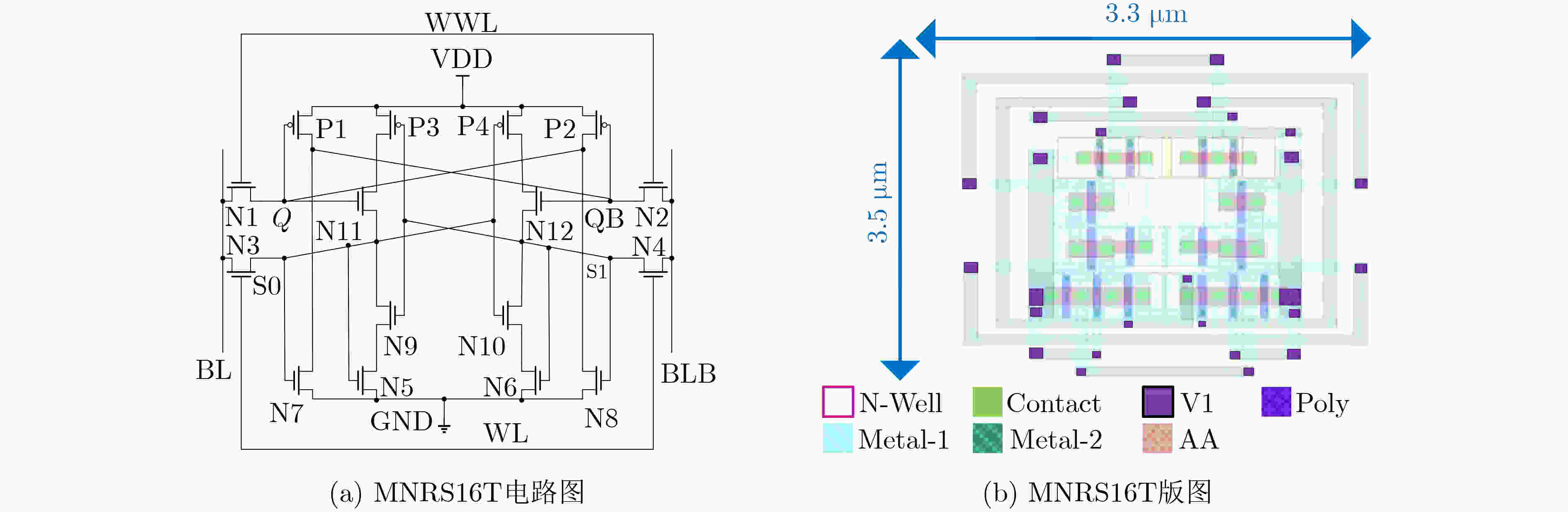

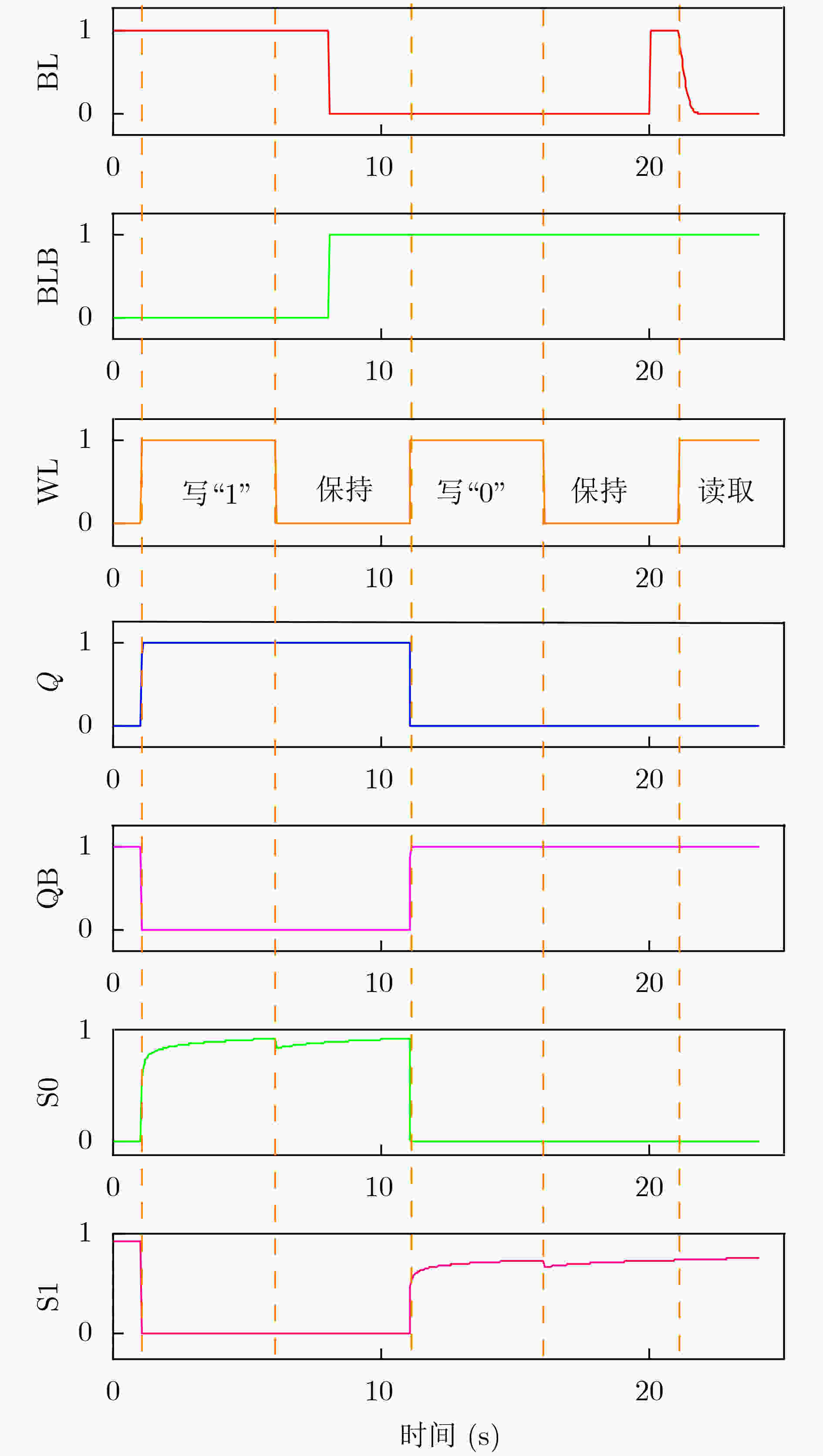

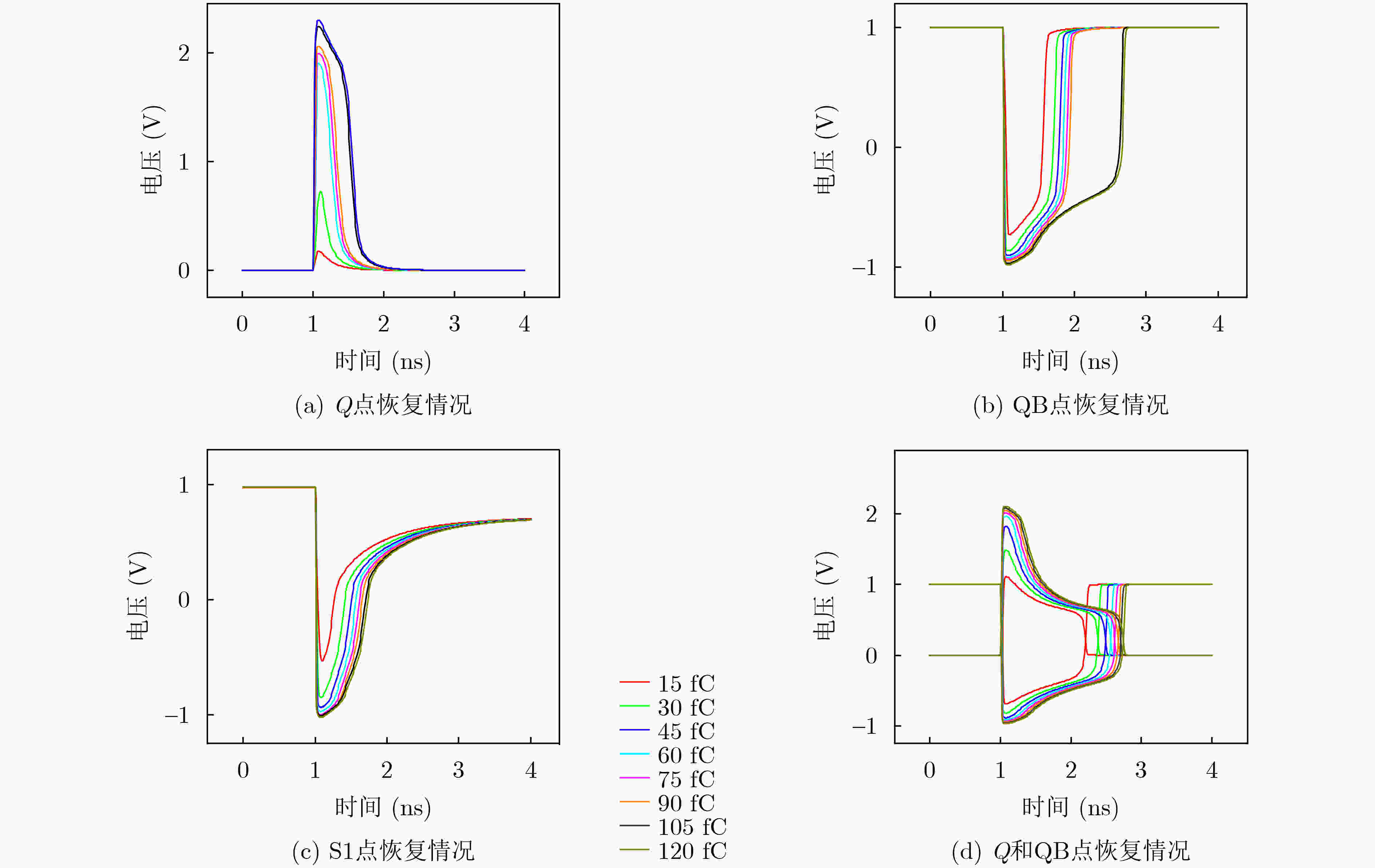

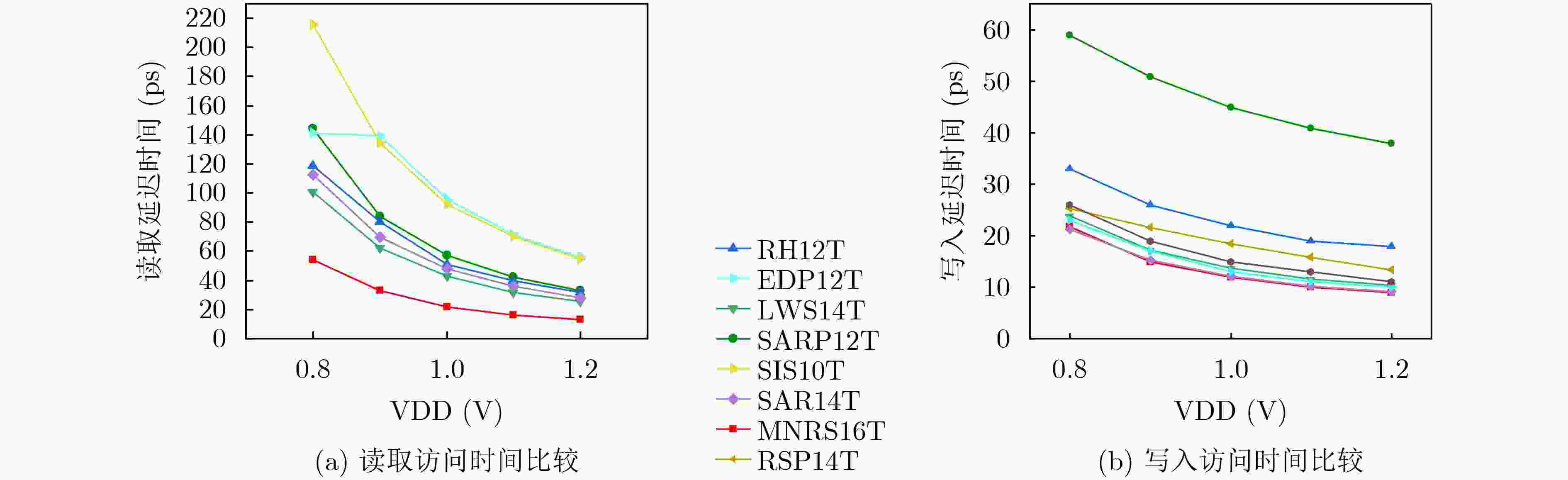

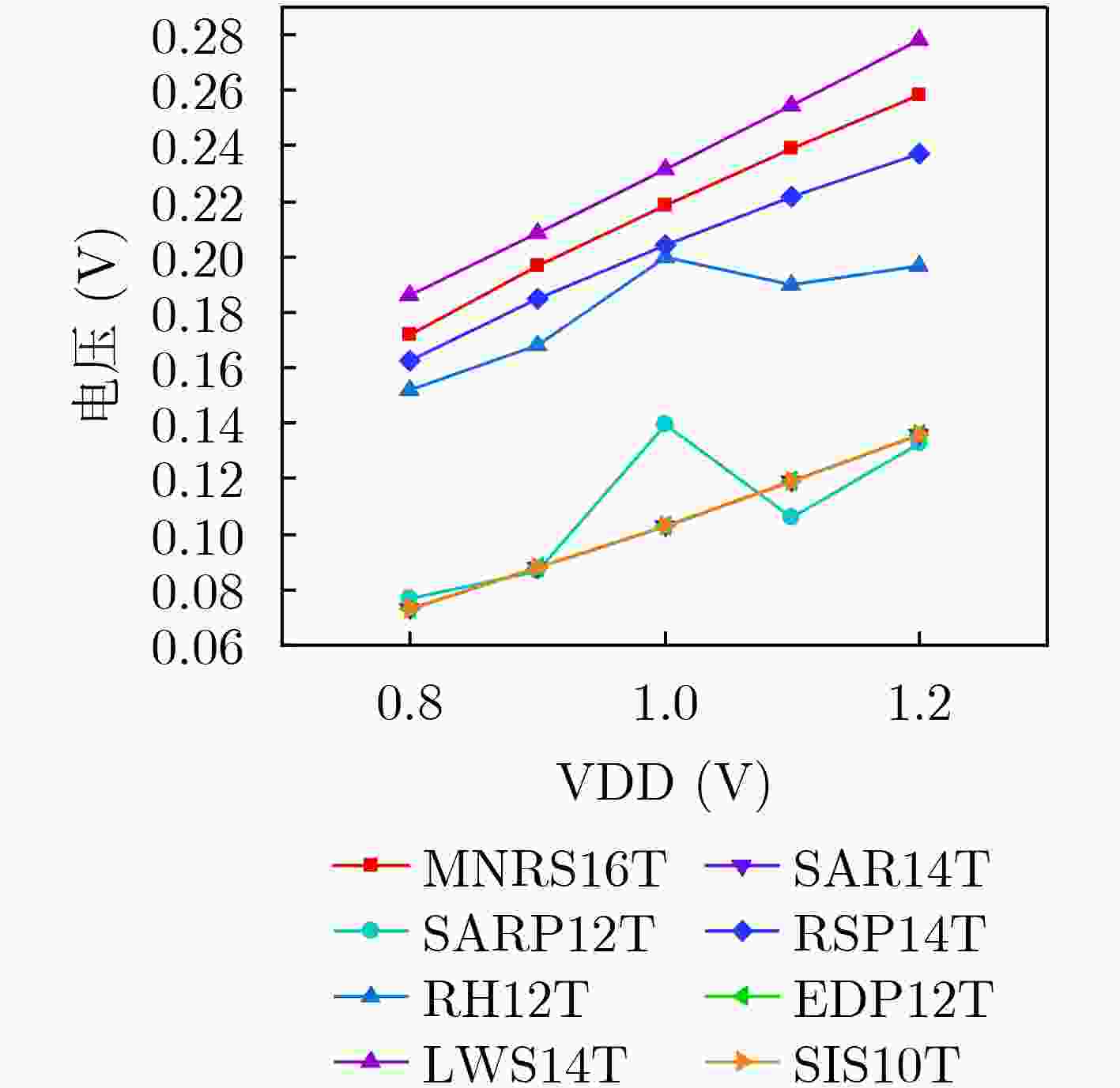

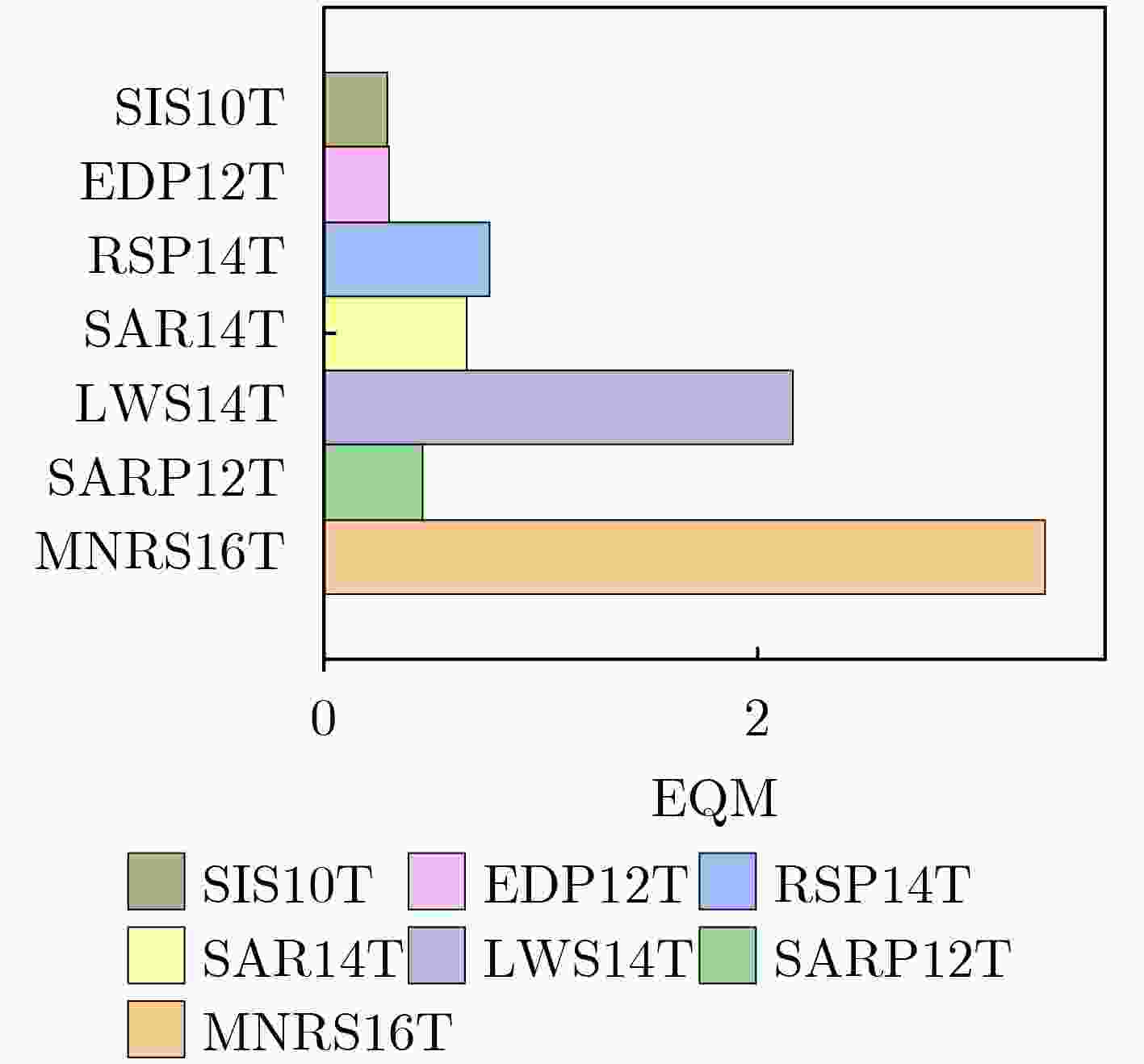

Objective As space exploration advances, the requirement for high-density memory in spacecraft escalates. However, SRAMs employed in aerospace applications face susceptibility to Single-Event Upsets (SEUs) and Multiple-Node Upsets (MNUs) due to high-energy particle bombardment, compromising the reliability of spacecraft systems. Hence, it is essential to engineer an SRAM design characterized by superior radiation resistance, reduced power consumption, and enhanced stability, fulfilling the rigorous demands of aerospace applications. Methods This paper proposes a 16T SRAM cell, designated as MNRS16T, featuring three sensitive nodes and utilizing a MOS transistor stacking structure. In this configuration, the upper tier of the stack employs a cross-coupling technique to enhance the pull-up drive capability while simultaneously diminishing that of the pull-down structure, thus balancing the driving abilities of both. The fundamental operations of the MNRS16T include write, read, and hold functions. For the write operation, bit lines WL and WWL are set to VDD, with specific MOS transistors managed to input data. During the read operation, word lines BL and BLB are precharged to VDD, and data is retrieved by assessing the voltage disparity across the bit lines. In the hold operation, bit lines are connected to ground, and word lines are precharged to VDD to preserve the data integrity. To assess the efficacy of MNRS16T, simulations are conducted using a 65nm CMOS process. Performance metrics, benchmarked against other SRAM cells include read access time, write access time, Hold Static Noise Margin (HSNM), Read Static Noise Margin (RSNM), Hold power (Hpwr), and soft error recovery capability. Results and Discussions MNRS16T exhibits superior performance across various metrics. In terms of read access time, MNRS16T exceeds other cells like SIS10T, SARP12T, and LWS14T, attributed to its efficient discharge path and optimal cell ratio ( Fig. 4(a) ). Regarding write access time, MNRS16T outperforms most counterparts. Specifically, its write access time is reduced compared to SARP12T, facilitated by the properties of the S1 node and the elimination of a lengthy feedback path (Fig. 4(b) ). Concerning the hold static noise margin, MNRS16T achieves a higher HSNM than units such as SIS10T and RSP14T, a result of the balanced pull-up and pull-down driving forces provided by the transistor stacking structure and cross-coupling method (Fig. 5 ). In the RSNM assessment, although MNRS16T’s RSNM falls below that of LWS14T at elevated voltages, it remains superior to several others, including RH12T and RSP14T (Fig. 6 ). Regarding hold power, MNRS16T achieves reductions of 24.7%,33.9% and 25.7% relative to SAR14T, RSP14T and EDP12T respectively, demonstrating significant energy efficiency (Fig. 8 ). In simulations of soft error recovery capability, MNRS16T consistently returns to its original logic state post-SEU, even when sensitive nodes receive a 120 fC charge. Additionally,1000 Monte Carlo simulations affirm its resilience against single-node and multi-node flips under Process, Voltage, and Temperature (PVT) variations (Fig. 3 ,Fig. 7 ). In terms of physical dimensions, MNRS16T’s 16 transistors necessitate a layout area of 3.3 μm×3.5 μm, which is comparatively larger. Finally, in the comprehensive performance index EQM, MNRS16T significantly outstrips other SRAM cells, indicating its overall performance (Fig. 9 ).Conclusions This paper presents the design of an MNRS16T SRAM cell tailored for aerospace applications, effectively addressing SEU and MNUs. The MNRS16T cell demonstrates reduced read and write delay times, decreased hold power, and enhanced HSNM and RSNM compared to other units. An extensive evaluation using the EQM performance index reveals that MNRS16T exceeds other radiation-hardened SRAM cells in overall performance. Nevertheless, the relatively large area of MNRS16T represents a drawback that warrants optimization in future studies. -

Key words:

- Single-Event Upset (SEU) /

- Radiation-resistant /

- SRAM

-

表 1 SRAM面积比较

SRAM单元 相对面积 SARP12T 0.61 LWS14T 0.82 SAR14T 0.74 RSP14T 0.77 EDP12T 0.72 SIS10T 0.58 MNRS16T 1.00 表 2 SRAM各项参数比较

SRAM单元 RAT (ps) WAT (ps) Hpwr (pW) HSNM (V) RSNM (V) SARP12T 33 38 102 0.435 9 0.132 9 LWS14T 25 10 140 0.285 5 0.278 3 SAR14T 28 9 223 0.278 3 0.135 7 RSP14T 40 13 254 0.439 1 0.237 2 EDP12T 56 10 226 0.278 3 0.135 7 MNRS16T 23 8 168 0.442 4 0.258 3 SIS10T 55 11 163 0.213 3 0.135 6 RH12T 32 18 2 354 0.453 1 0.196 6 -

[1] SUDHIR KUMAR K, KEERTHI PRIYA B, VINEELA M, et al. A design of low power full seu tolerance RHBD 10t SRAM cell[C]. 2020 IEEE India Council International Subsections Conference, Visakhapatnam, India, 2020: 27–32. doi: 10.1109/INDISCON50162.2020.00018. [2] SU Zexin, LI Bo, SU Xiaohui, et al. An SEU (single-event upset) mitigation strategy on read-write separation SRAM cell for low power consumption[C]. The 2020 IEEE 15th International Conference on Solid-State & Integrated Circuit Technology, Kunming, China, 2020: 1–3. doi: 10.1109/ICSICT49897.2020.9278325. [3] AHMED S, AMBULKAR J, MONDAL D, et al. Soft error immune with enhanced critical charge SIC14T SRAM cell for avionics applications[C]. The 2023 IFIP/IEEE 31st International Conference on Very Large Scale Integration, Dubai, United Arab Emirates, 2023: 1–6. doi: 10.1109/VLSI-SoC57769.2023.10321888. [4] NAGA RAGHURAM C H, GUPTA B, KAUSHAL G, et al. Single-event multiple effect tolerant RHBD14T SRAM cell design for space applications[J]. IEEE Transactions on Device and Materials Reliability, 2021, 21(1): 48–56. doi: 10.1109/TDMR.2021.3049215. [5] MOHD SAKIB ANSARI S, KAVITHA S, RENIWAL B S, et al. Design of radiation hardened 12T SRAM with enhanced reliability and read/write latency for space application[C]. The 2023 36th International Conference on VLSI Design and 2023 22nd International Conference on Embedded Systems, Hyderabad, India, 2023: 104–108. doi: 10.1109/VLSID57277.2023.00034. [6] PRASAD G, MANDI B C, ALI M, et al. Soft-error-aware SRAM for terrestrial applications[J]. IEEE Transactions on Device and Materials Reliability, 2021, 21(4): 658–660. doi: 10.1109/TDMR.2021.3118715. [7] PAL S, MOHAPATRA S, KI W H, et al. Soft-error-aware read-decoupled SRAM with multi-node recovery for aerospace applications[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2021, 68(10): 3336–3340. doi: 10.1109/TCSII.2021.3073947. [8] PAL S, KI W H, and TSUI C Y. Soft-error-aware read-stability-enhanced low-power 12T SRAM with multi-node upset recoverability for aerospace applications[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2022, 69(4): 1560–1570. doi: 10.1109/TCSI.2022.3147675. [9] PAL S, CHOWDARY G, KI W H, et al. Energy-efficient dual-node-upset-recoverable 12T SRAM for low-power aerospace applications[J]. IEEE Access, 2023, 11: 20184–20195. doi: 10.1109/ACCESS.2022.3161147. [10] PAL S, SAHAY S, KI W H, et al. A 10T soft-error-immune SRAM with multi-node upset recovery for low-power space applications[J]. IEEE Transactions on Device and Materials Reliability, 2022, 22(1): 85–88. doi: 10.1109/TDMR.2022.3147864. [11] BAI Na, XIAO Xin, XU Yaohua, et al. Soft-error-aware SRAM with multinode upset tolerance for aerospace applications[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2024, 32(1): 128–136. doi: 10.1109/TVLSI.2023.3328717. [12] 张景波, 杨志平, 彭春雨, 等. PMOS晶体管工艺参数变化对SRAM单元翻转恢复效应影响的研究[J]. 电子与信息学报, 2017, 39(11): 2755–2762. doi: 10.11999/JEIT170547.ZHANG Jingbo, YANG Zhiping, PENG Chunyu, et al. Study on the effect of upset and recovery for SRAM under the varying parameters of PMOS transistor[J]. Journal of Electronics & Information Technology, 2017, 39(11): 2755–2762. doi: 10.11999/JEIT170547. [13] ZHAO Qiang, PENG Chunyu, CHEN Junning, et al. Novel write-enhanced and highly reliable RHPD-12T SRAM cells for space applications[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2020, 28(3): 848–852. doi: 10.1109/TVLSI.2019.2955865. [14] PENG Chunyu, YANG Zhou, LIN Zhiting, et al. Reverse bias current eliminated, read-separated, and write-enhanced tunnel FET SRAM[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2021, 68(1): 466–470. doi: 10.1109/TCSII.2020.3011950. [15] PAL S, MOHAPATRA S, KI W H, et al. Soft-error-immune read-stability-improved SRAM for multi-node upset tolerance in space applications[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2021, 68(8): 3317–3327. doi: 10.1109/TCSI.2021.3085516. [16] LI Tianwen, YANG Haigang, CAI Gang, et al. A CMOS triple inter-locked latch for SEU insensitivity design[J]. IEEE Transactions on Nuclear Science, 2014, 61(6): 3265–3273. doi: 10.1109/TNS.2014.2366999. [17] LI Tianwen, YANG Haigang, ZHAO He, et al. Investigation into SEU effects and hardening strategies in SRAM based FPGA[C]. The 2017 17th European Conference on Radiation and Its Effects on Components and Systems, Geneva, Switzerland, 2017: 1–5. doi: 10.1109/RADECS.2017.8696177. [18] 赵磊, 王祖林, 郭旭静, 等. 一种SRAM型FPGA抗软错误物理设计方法[J]. 电子与信息学报, 2013, 35(4): 994–1000. doi: 10.3724/SP.J.1146.2012.01030.ZHAO Lei, WANG Zulin, GUO Xujing, et al. A physical design approach for mitigating soft errors in SRAM-based FPGAs[J]. Journal of Electronics & Information Technology, 2013, 35(4): 994–1000. doi: 10.3724/SP.J.1146.2012.01030. -

下载:

下载:

下载:

下载: