| [1] |

GUPTA S N, DEV R, SAMAD A, et al. IoT based smart extension board[C]. 2023 International Conference on Disruptive Technologies (ICDT), Greater Noida, India, 2023: 325–327. doi: 10.1109/ICDT57929.2023.10150457.

|

| [2] |

HUANG Y H, HSIEH Y C, LIN Yucheng, et al. High density embedded 3D stackable Via RRAM in advanced MCU applications[C]. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 2023: 1–2. doi: 10.23919/VLSITechnologyandCir57934.2023.10185230.

|

| [3] |

QIAN Liyu, LU Jie, LI Wenzhuo, et al. MCU-enabled epileptic seizure detection system with compressed learning[J]. IEEE Internet of Things Journal, 2024, 11(5): 8771–8782. doi: 10.1109/JIOT.2023.3323264.

|

| [4] |

SCHIAVONE P D, ROSSI D, DI MAURO A, et al. Arnold: An eFPGA-augmented RISC-V SoC for flexible and low-power IoT end nodes[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2021, 29(4): 677–690. doi: 10.1109/TVLSI.2021.3058162.

|

| [5] |

BOL D, SCHRAMME M, MOREAU L, et al. SleepRunner: A 28-nm FDSOI ULP cortex-M0 MCU with ULL SRAM and UFBR PVT compensation for 2.6–3.6-μW/DMIPS 40–80-MHz active mode and 131-nW/kB fully retentive deep-sleep mode[J]. IEEE Journal of Solid-State Circuits, 2021, 56(7): 2256–2269. doi: 10.1109/JSSC.2021.3056219.

|

| [6] |

郑黎明, 刘培国, 王宏义, 等. 无源物联网: 背景、概念、挑战及研究进展[J]. 电子与信息学报, 2023, 45(7): 2293–2310. doi: 10.11999/JEIT221219.ZHENG Liming, LIU Peiguo, WANG Hongyi, et al. Passive internet of things: Background, concept, challenges and progress[J]. Journal of Electronics & Information Technology, 2023, 45(7): 2293–2310. doi: 10.11999/JEIT221219.

|

| [7] |

HUANG Cong and JIAO Hailong. C3MLS: An ultra-wide-range energy-efficient level shifter with CCLS/CMLS hybrid structure[J]. IEEE Journal of Solid-State Circuits, 2023, 58(10): 2685–2695. doi: 10.1109/JSSC.2023.3266221.

|

| [8] |

LIN Longyang, JAIN S, and ALIOTO M. Sub-nW microcontroller with dual-mode logic and self-startup for battery-indifferent sensor nodes[J]. IEEE Journal of Solid-State Circuits, 2021, 56(5): 1618–1629. doi: 10.1109/JSSC.2020.3038115.

|

| [9] |

PRABHAT P, LABBE B, KNIGHT G, et al. 27.2 M0N0: A performance-regulated 0.8-to-38MHz DVFS ARM cortex-M33 SIMD MCU with 10 nW sleep power[C]. 2020 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, USA, 2020: 422–424. doi: 10.1109/ISSCC19947.2020.9063136.

|

| [10] |

SCHRAMME M and BOL D. UFBBR: A unified frequency and back-bias regulation unit for ultralow-power microcontrollers in 28-nm FDSOI[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2023, 70(6): 2464–2477. doi: 10.1109/TCSI.2023.3257270.

|

| [11] |

KIM J S, JAVED K, MIN K H, et al. A 13.5-nA quiescent current LDO with adaptive ultra-low-power mode for low-power IoT applications[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2023, 70(9): 3278–3282. doi: 10.1109/TCSII.2023.3263876.

|

| [12] |

SERRANO R, SARMIENTO M, DURAN C, et al. A low-power low-area SoC based in RISC-V processor for IoT applications[C]. 2021 18th International SoC Design Conference (ISOCC), Jeju Island, Korea, 2021: 375–376. doi: 10.1109/ISOCC53507.2021.9613880.

|

| [13] |

LIU Xinning, LI Xiaomin, ZHANG Huanqing, et al. SCVR-less dynamic voltage-stacking scheme for IoT MCU[J]. IEEE Journal of Solid-State Circuits, 2022, 57(1): 103–114. doi: 10.1109/JSSC.2021.3095621.

|

| [14] |

YOKOYAMA Y, ISHII Y, NII K, et al. Cost-effective test screening method on 40-nm embedded SRAMs for low-power MCUs[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2021, 29(7): 1495–1499. doi: 10.1109/TVLSI.2021.3082760.

|

| [15] |

RABAEY J M, CHANDRAKASAN A, and NIKOLIC B, 周润德, 译. 数字集成电路—电路、系统与设计[M]. 2版. 北京: 电子工业出版社, 2017: 62–63.RABAEY J M, CHANDRAKASAN A, and NIKOLIC B, ZHOU Runde, translation. Digital Integrated Circuits: A Design Perspective[M]. 2nd ed. Beijing: Publishing House of Electronics Industry, 2017: 62–63.

|

| [16] |

刘浩宇. 适用于MCU低功耗LDO的研究与设计[D]. [硕士论文], 电子科技大学, 2023. doi: 10.27005/d.cnki.gdzku.2023.001888.LIU Haoyu. Research and design of low-power LDO suitable for MCU[D]. [Master dissertation], University of Electronic Science and Technology of China, 2023. doi: 10.27005/d.cnki.gdzku.2023.001888.

|

| [17] |

RIDGEWAY M, REYNOSO L, and CHEN Lixin. Designing a dual-ray smoke detector analog front-end with MSP430FR235x MCUs[EB/OL]. https://www.ti.com.cn/cn/lit/pdf/slaa930.pdf, 2020.

|

| [18] |

程乔. 针对低功耗嵌入式系统的可重构片上存储结构研究[D]. [硕士论文], 西安理工大学, 2022. doi: 10.27398/d.cnki.gxalu.2022.000609.CHENG Qiao. Reconfigurable on-chip memory architecture for low power embedded system[D]. [Master dissertation], Xi’an University of Technology, 2022. doi: 10.27398/d.cnki.gxalu.2022.000609.

|

| [19] |

BACCARIN D, ESSENI D, and ALIOTO M. Low-standby current 4T FinFET buffers: Analysis and evaluation below 45 nm[C]. 2010 International Conference on Microelectronics, Cairo, Egypt, 2010: 296–299. doi: 10.1109/ICM.2010.5696143.

|

| [20] |

SREEKALA K S and KRISHNAKUMAR S. Subthreshold leakage power reduction by feedback sleeper-stack technique[C]. 2016 International Conference on Emerging Technological Trends (ICETT), Kollam, India, 2016: 1–7. doi: 10.1109/ICETT.2016.7873668.

|

| [21] |

FLYNN D, AITKEN R, GIBBONS A, et al. Low Power Methodology Manual: For System-on-Chip Design[M]. Springer Publishing Company, 2010: 7–8.

|

| [22] |

KRISHNAMOHAN T, KIM D, RAGHUNATHAN S, et al. Double-gate Strained-Ge heterostructure Tunneling FET (TFET) With record high drive currents and <<60mV/dec subthreshold slope[C]. 2008 IEEE International Electron Devices Meeting, San Francisco, USA, 2008. 1–3. doi: 10.1109/IEDM.2008.4796839.

|

| [23] |

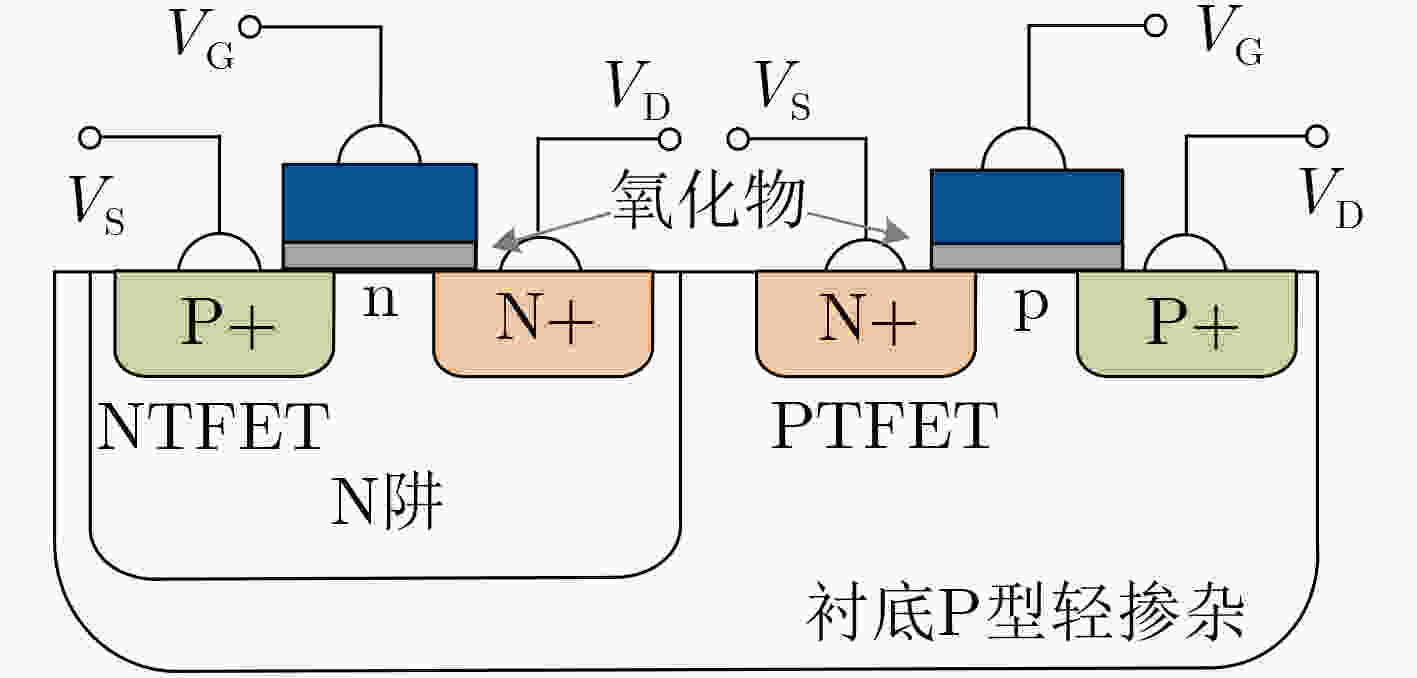

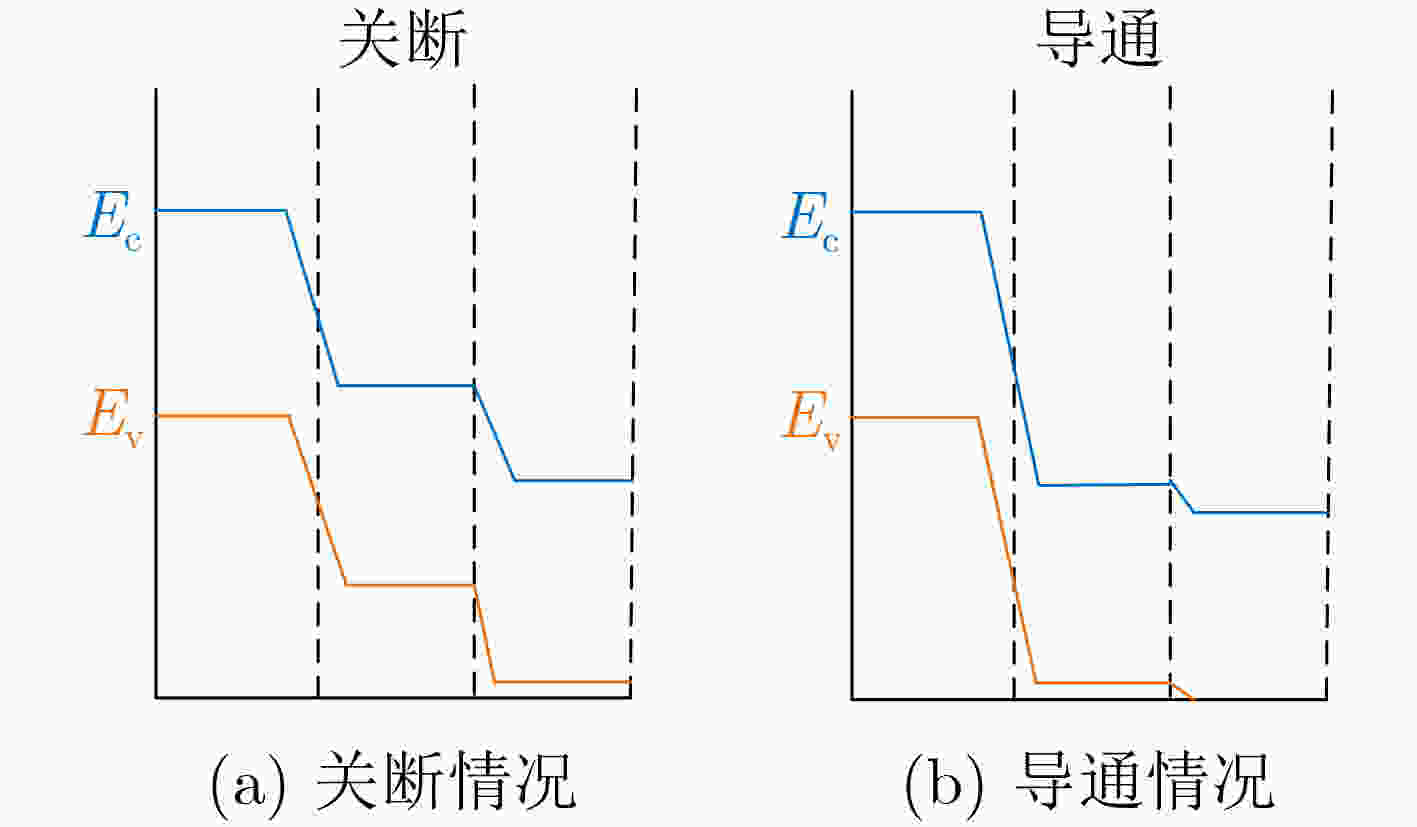

李伟. 隧穿场效应晶体管的新结构设计及应用研究[D]. [博士论文], 西安电子科技大学, 2019. doi: 10.27389/d.cnki.gxadu.2019.000132.LI Wei. Novel structure design and application of research on tunnel field-effect transistor[D]. [Ph. D. dissertation]. Xidian University, 2019. doi: 10.27389/d.cnki.gxadu.2019.000132.

|

| [24] |

WU Chunlei, HUANG Ru, HUANG Qianqian, et al. Design guideline for complementary Heterostructure tunnel fets with steep slope and improved output behavior[J]. IEEE Electron Device Letters, 2016, 37(1): 20–23. doi: 10.1109/LED.2015.2499183.

|

| [25] |

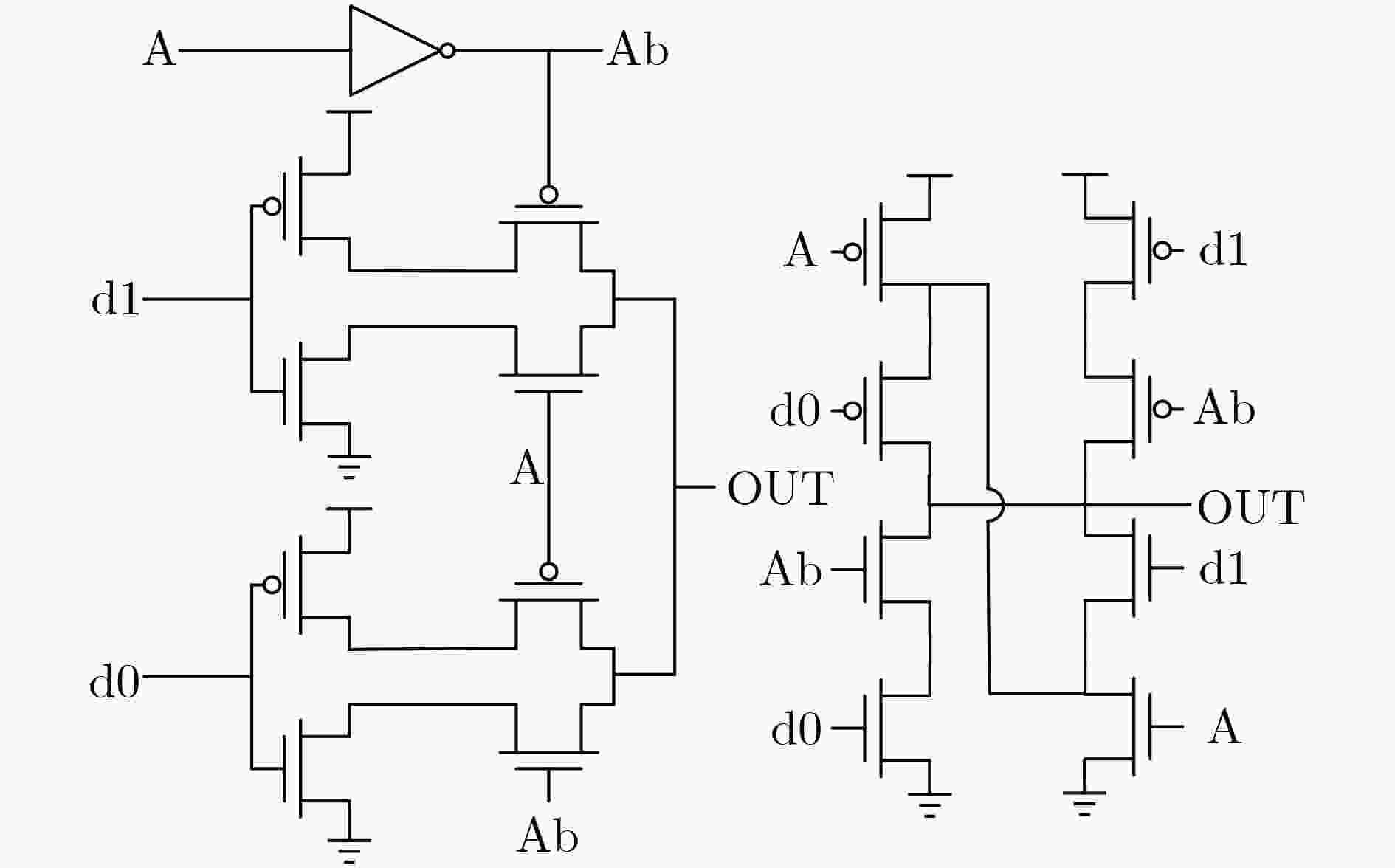

WANG Zhixuan, ZHONG Yuan, CHEN Cheng, et al. Ultra-low power hybrid TFET-MOSFET topologies for standard logic cells with improved comprehensive performance[C]. 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 2019: 1–5. doi: 10.1109/ISCAS.2019.8702101.

|

| [26] |

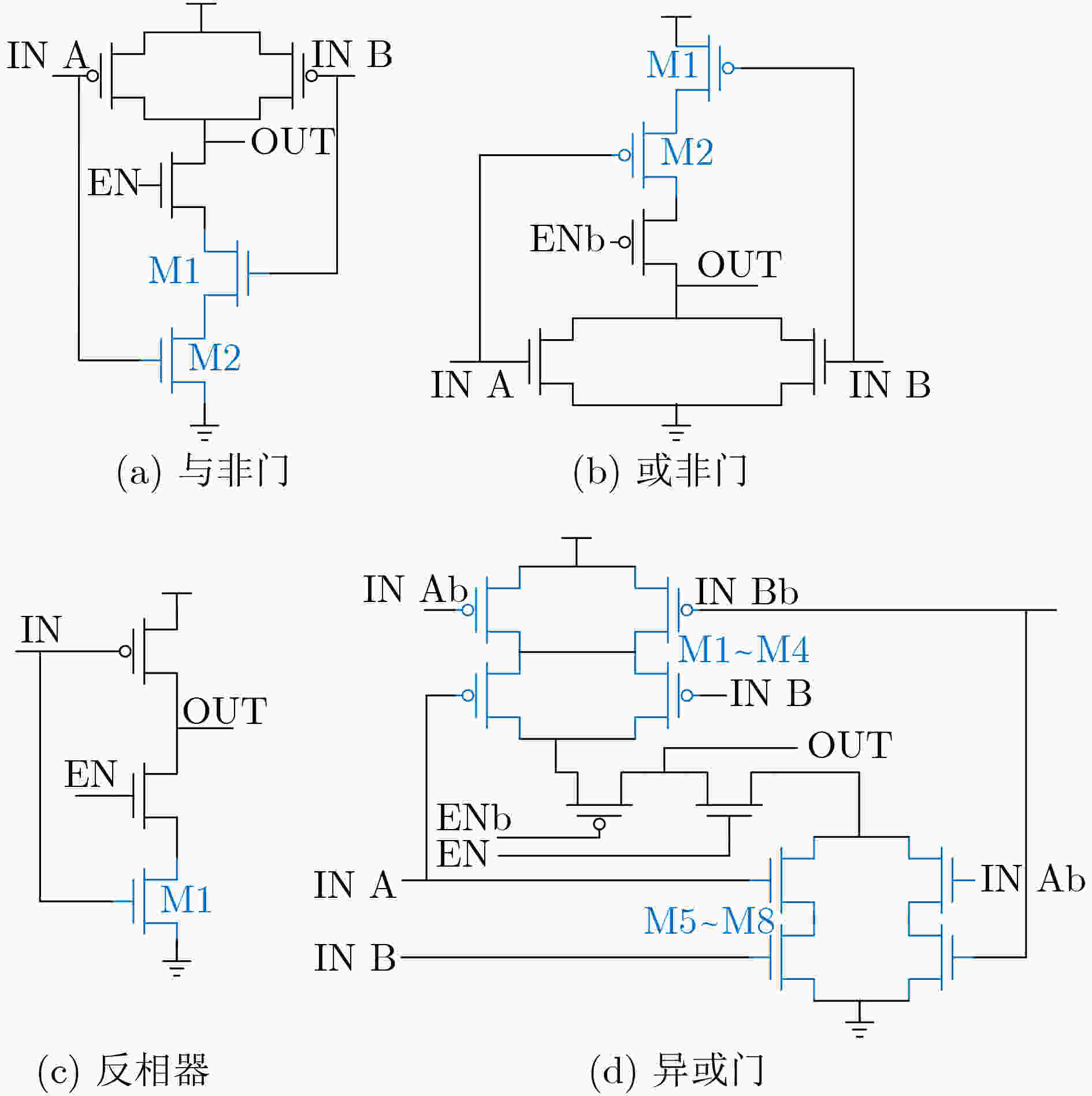

MORRIS D H, AVCI U E, RIOS R, et al. Design of low voltage tunneling-FET logic circuits considering asymmetric conduction characteristics[J]. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2014, 4(4): 380–388. doi: 10.1109/JETCAS.2014.2361054.

|

| [27] |

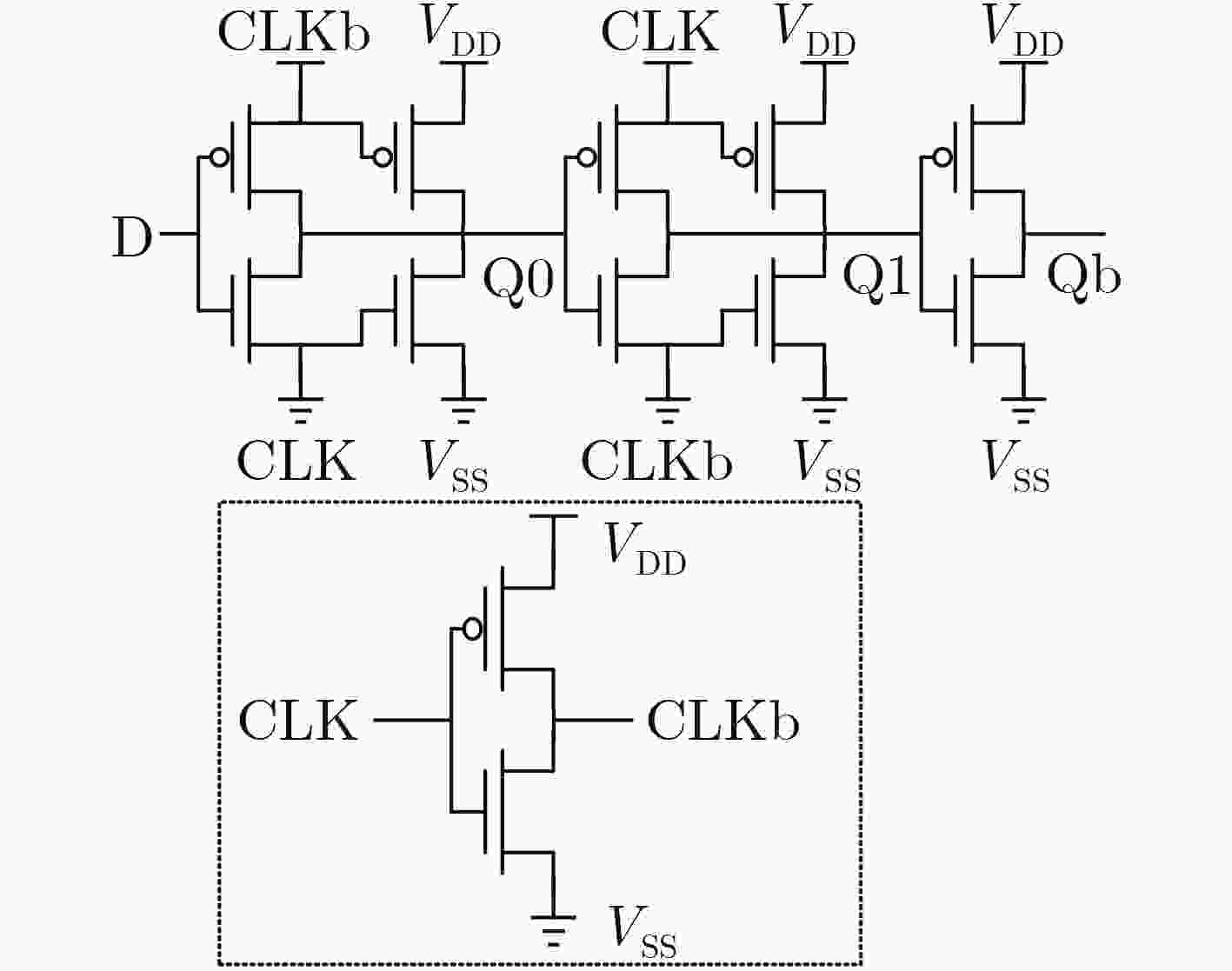

COTTER M, LIU Huichu, DATTA S, et al. Evaluation of tunnel FET-based flip-flop designs for low power, high performance applications[C]. International Symposium on Quality Electronic Design (ISQED), Santa Clara, USA, 2013: 430–437. doi: 10.1109/ISQED.2013.6523647.

|

| [28] |

GUPTA N, MAKOSIEJ A, VLADIMIRESCU A, et al. Ultra-low-power compact TFET flip-flop design for high-performance low-voltage applications[C]. 2016 17th International Symposium on Quality Electronic Design (ISQED), Santa Clara, USA, 2016: 107–112. doi: 10.1109/ISQED.2016.7479184.

|

| [29] |

LEE Y, KIM D, CAI Jin, et al. Low-power circuit analysis and design based on heterojunction tunneling transistors (HETTs)[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2013, 21(9): 1632–1643. doi: 10.1109/TVLSI.2012.2213103.

|

| [30] |

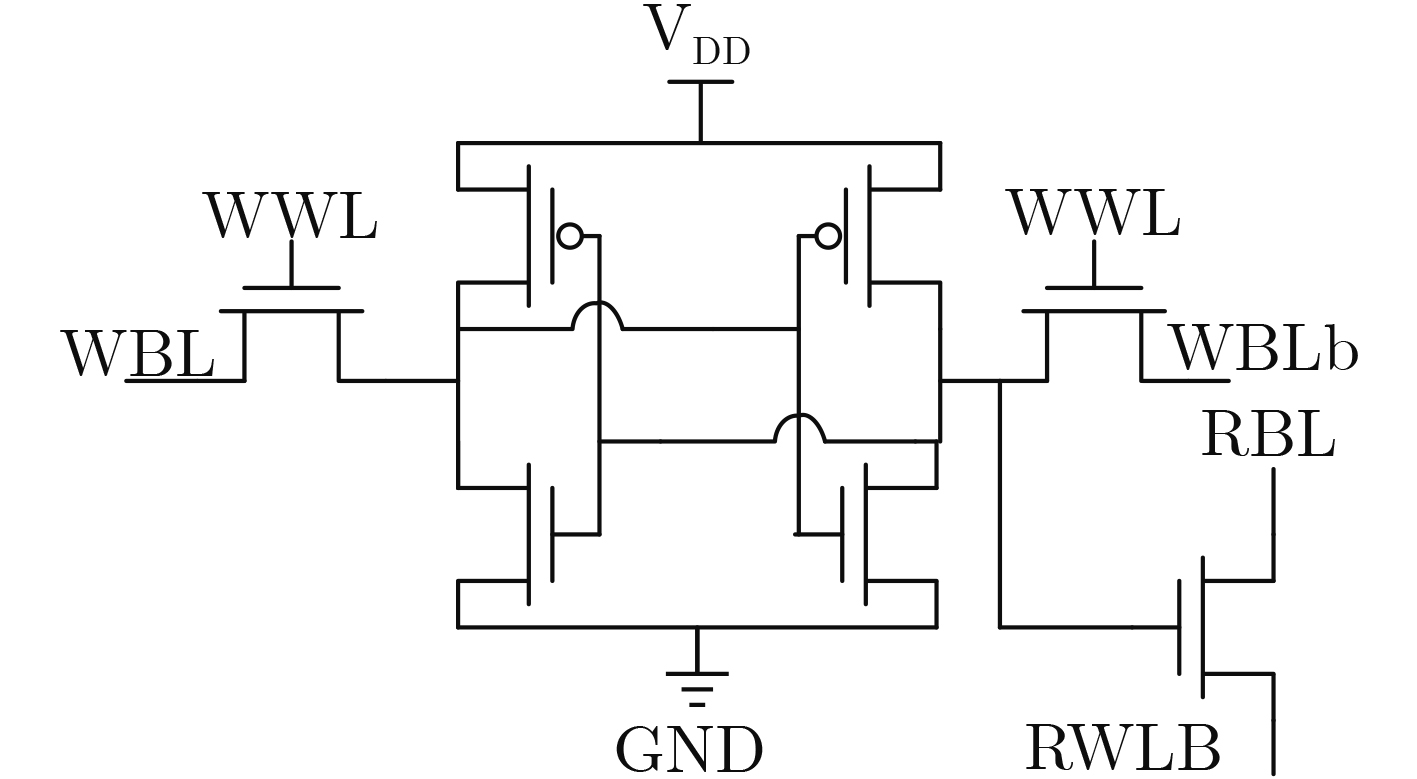

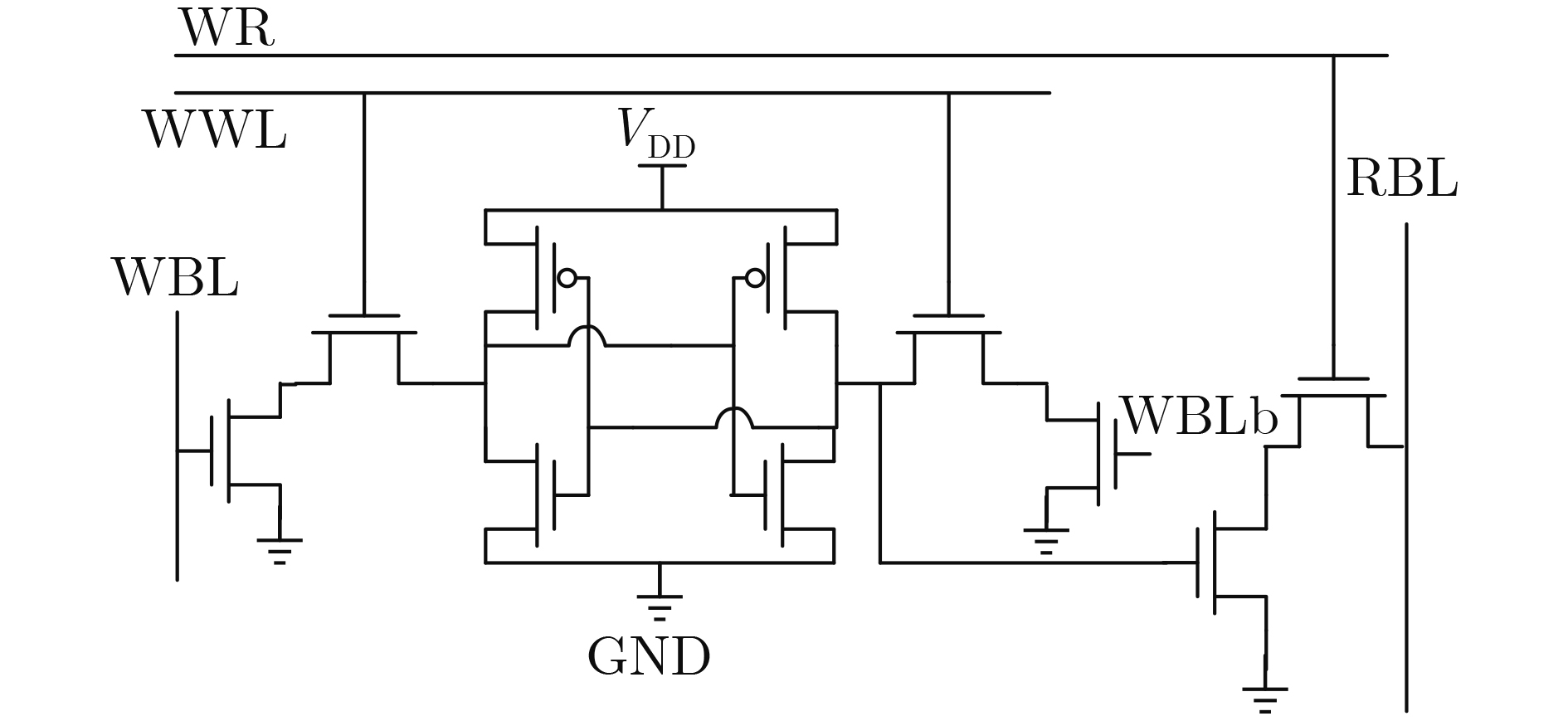

YANG Libo, ZHU Jiadi, CHEN Cheng, et al. Combinational access tunnel FET SRAM for ultra-low power applications[C]. 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 2018: 1–5. doi: 10.1109/ISCAS.2018.8351297.

|

| [31] |

TRIVEDI A R, CARLO S, and MUKHOPADHYAY S. Exploring tunnel-FET for Ultra Low power analog applications: A case study on operational transconductance amplifier[C]. The 50th ACM/EDAC/IEEE Design Automation Conference, Austin, USA, 2013: 1–6. doi: 10.1145/2463209.2488868.

|

| [32] |

SEDIGHI B, HU X S, LIU Huichu, et al. Analog circuit design using tunnel-FETs[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2015, 62(1): 39–48. doi: 10.1109/TCSI.2014.2342371.

|

| [33] |

SETTINO F, LANUZZA M, STRANGIO S, et al. Understanding the potential and limitations of tunnel FETs for low-voltage analog/mixed-signal circuits[J]. IEEE Transactions on Electron Devices, 2017, 64(6): 2736–2743. doi: 10.1109/TED.2017.2689746.

|

| [34] |

YADAV A K and ACHARYA A. Investigation of III-V tunnel FETs for analog circuit design[C]. 2021 Devices for Integrated Circuit (DevIC), Kalyani, India, 2021: 416–420. doi: 10.1109/DevIC50843.2021.9455904.

|

| [35] |

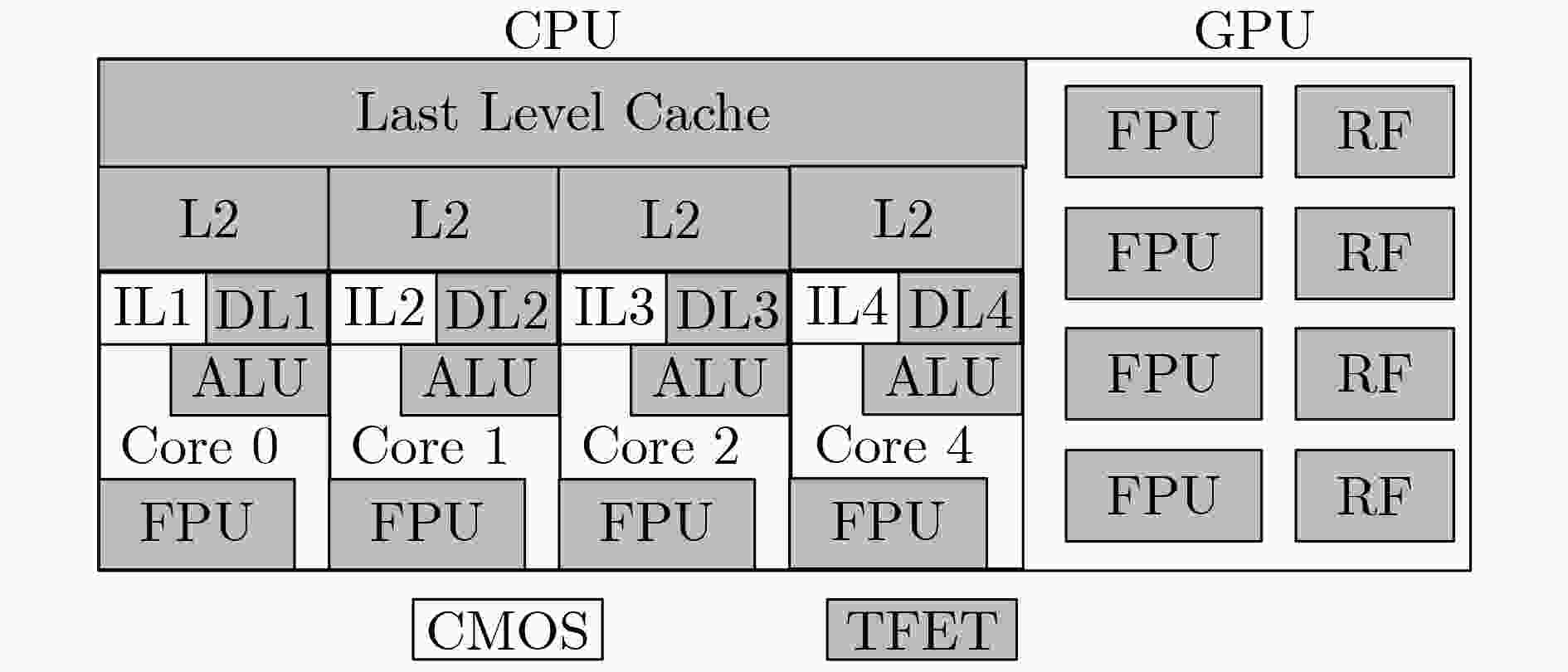

SARIPALLI V, MISHRA A, DATTA S, et al. An energy-efficient heterogeneous CMP based on hybrid TFET-CMOS cores[C]. The 48th ACM/EDAC/IEEE Design Automation Conference, San Diego, USA, 2011: 729–734.

|

| [36] |

GOPIREDDY B, SKARLATOS D, ZHU Wenjuan, et al. HetCore: TFET-CMOS hetero-device architecture for CPUs and GPUs[C]. 2018 ACM/IEEE 45th Annual International Symposium on Computer Architecture (ISCA), Los Angeles, USA, 2018: 802–815. doi: 10.1109/ISCA.2018.00072.

|

| [37] |

HU V P H, LIN H H, LIN Y K, et al. Optimization of negative-capacitance vertical-tunnel FET (NCVT-FET)[J]. IEEE Transactions on Electron Devices, 2020, 67(6): 2593–2599. doi: 10.1109/TED.2020.2986793.

|

| [38] |

TALUKDAR J, RAWAT G, and MUMMANENI K. Dielectrically modulated single and double gate tunnel FET based biosensors for enhanced sensitivity[J]. IEEE Sensors Journal, 2021, 21(23): 26566–26573. doi: 10.1109/JSEN.2021.3122582.

|

| [39] |

GUHA S and PACHAL P. Heterojunction negative-capacitance tunnel-FET as a promising candidate for sub-0.4V VDD digital logic circuits[J]. IEEE Transactions on Nanotechnology, 2021, 20: 576–583. doi: 10.1109/TNANO.2021.3096252.

|

下载:

下载:

下载:

下载: