Switched-Capacitor DC-DC Converter: Evolution from Transformer Model to Circuitry

-

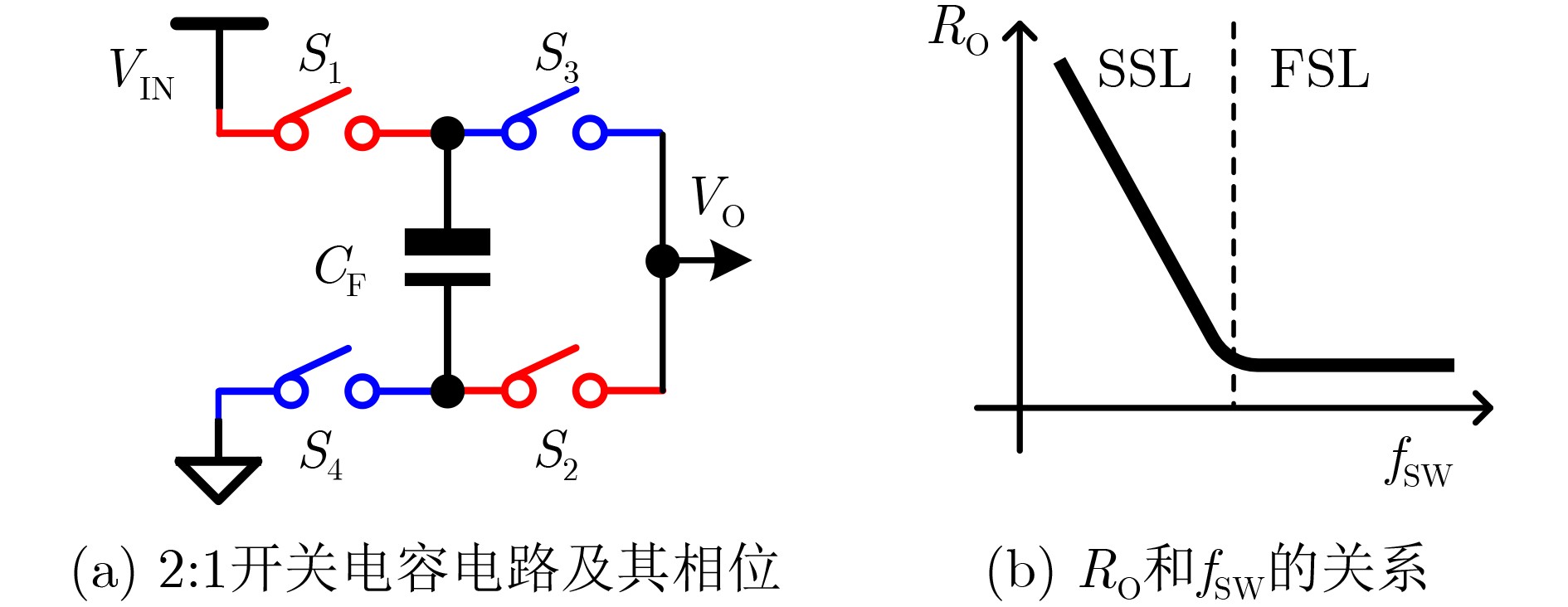

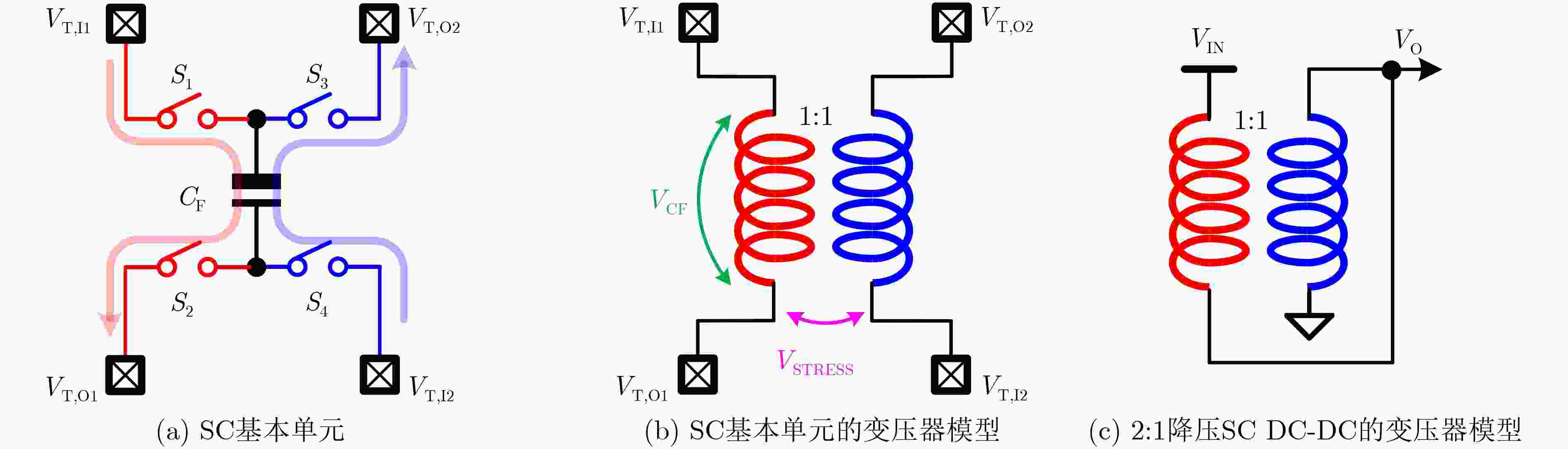

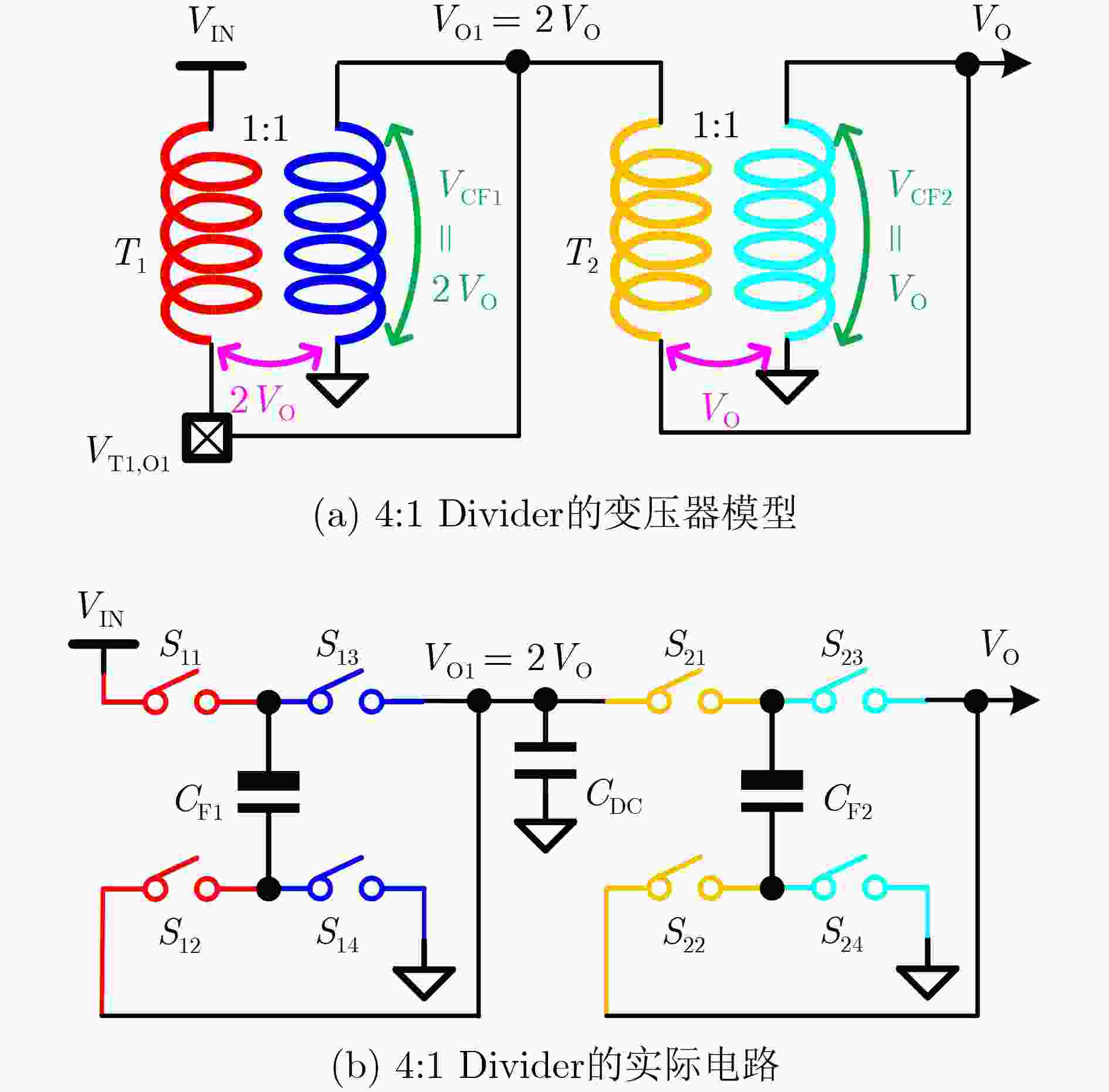

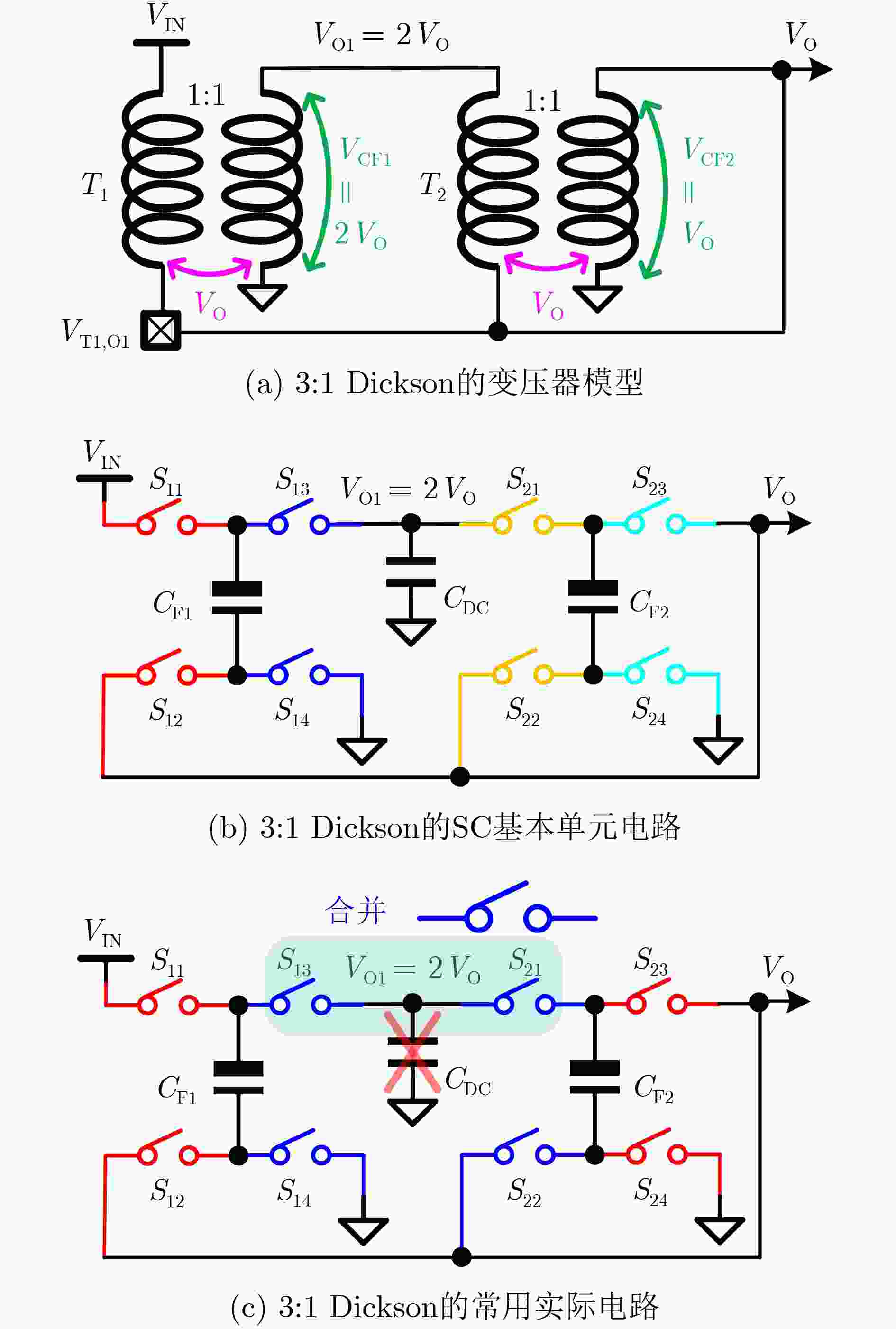

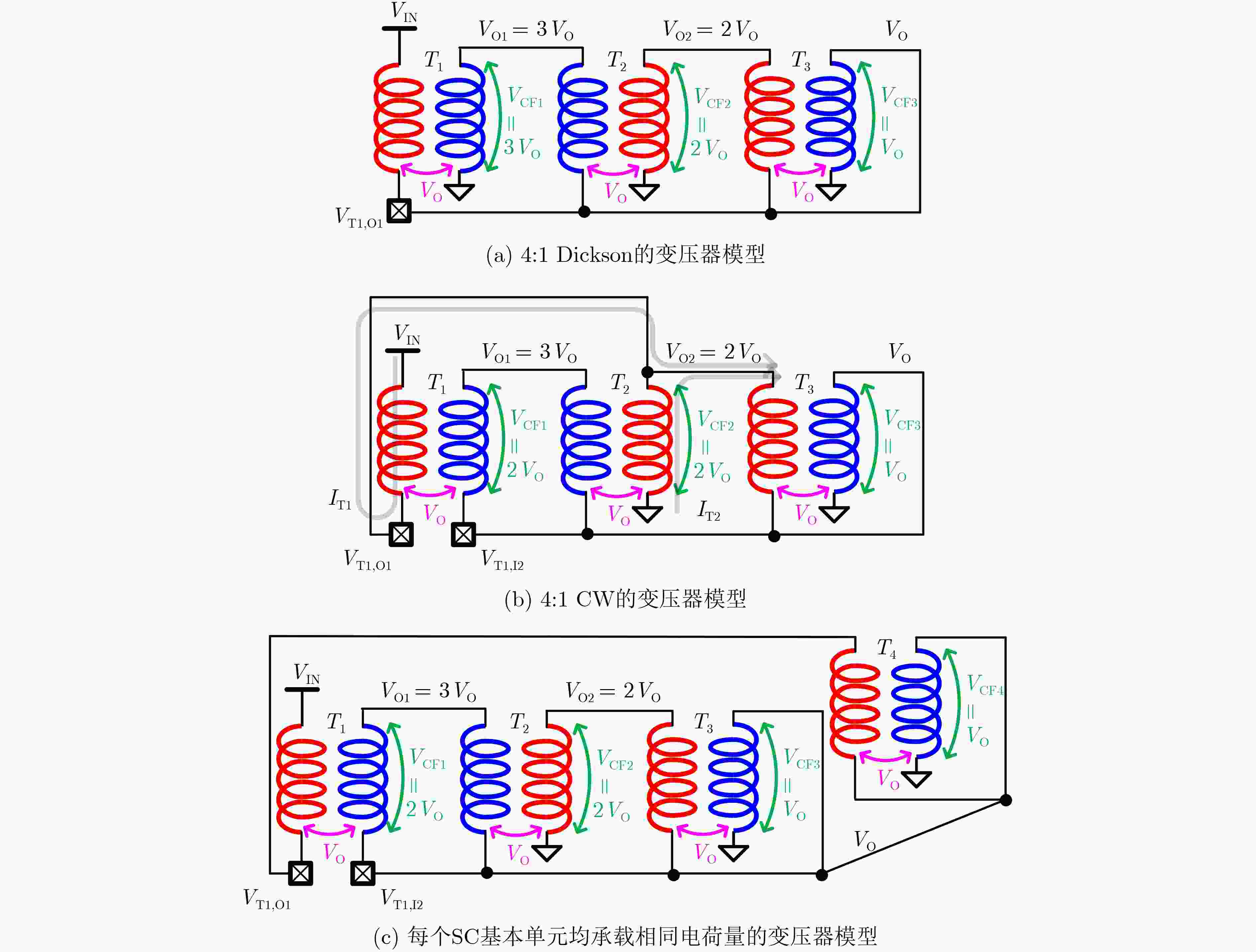

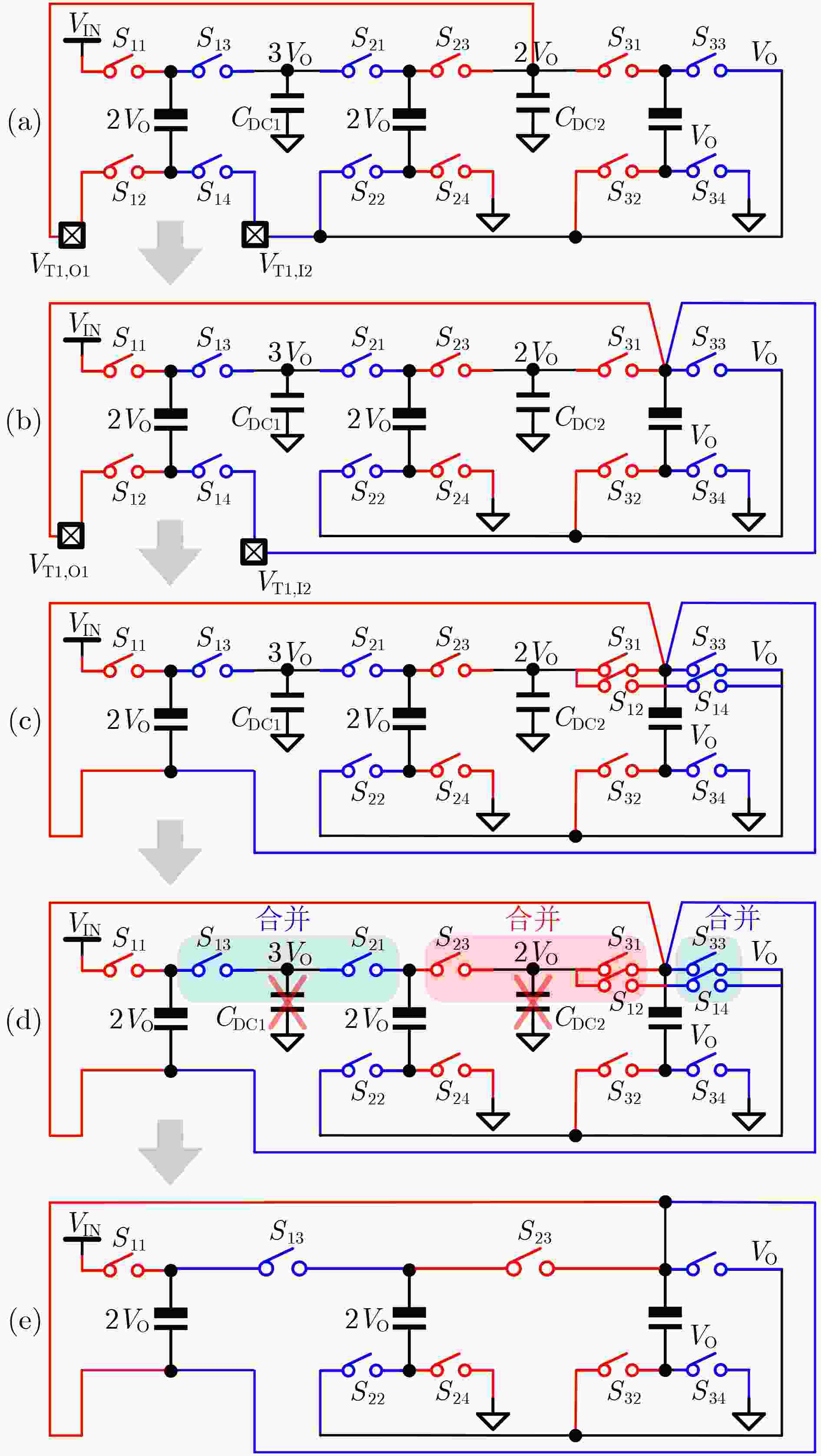

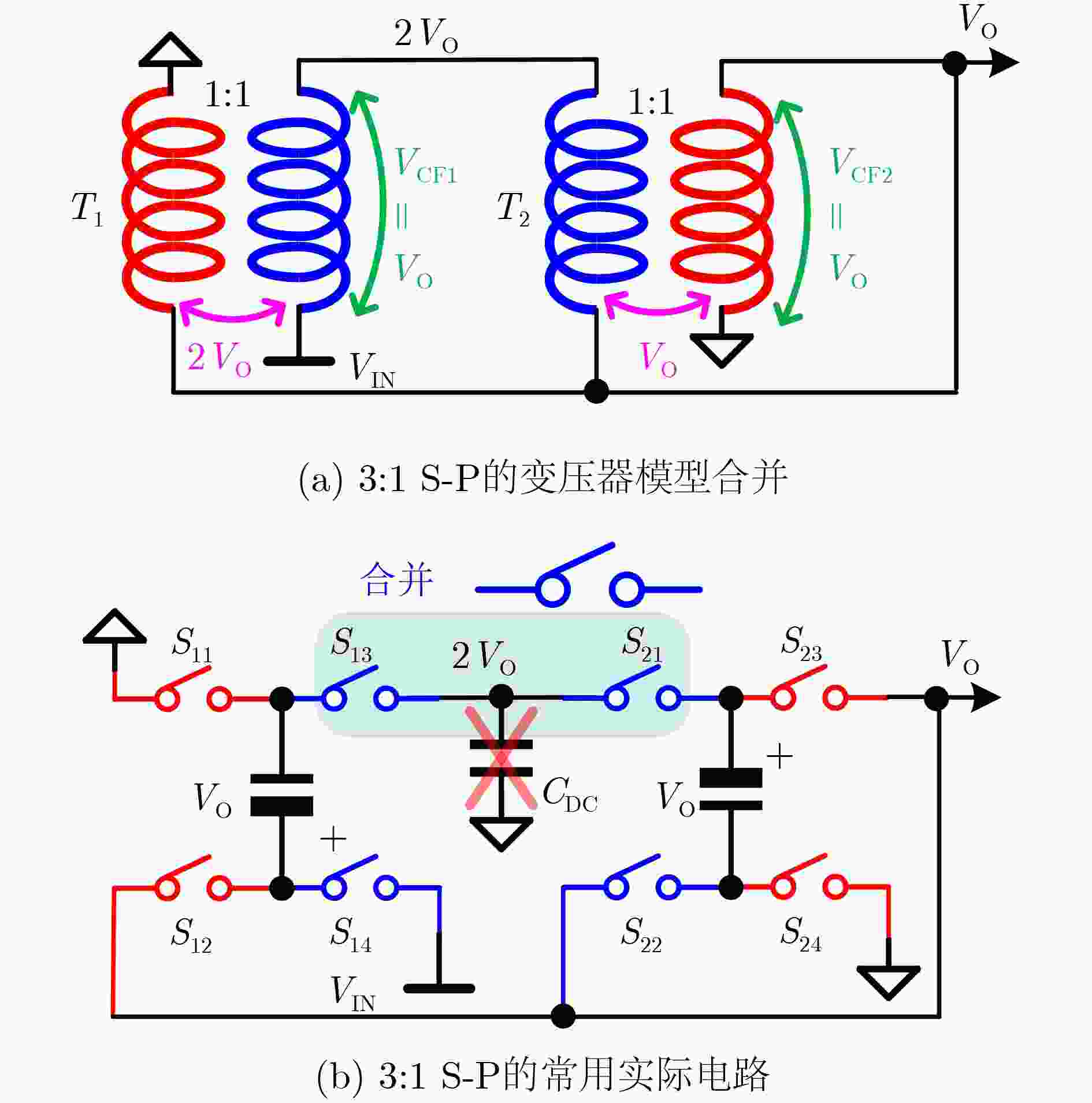

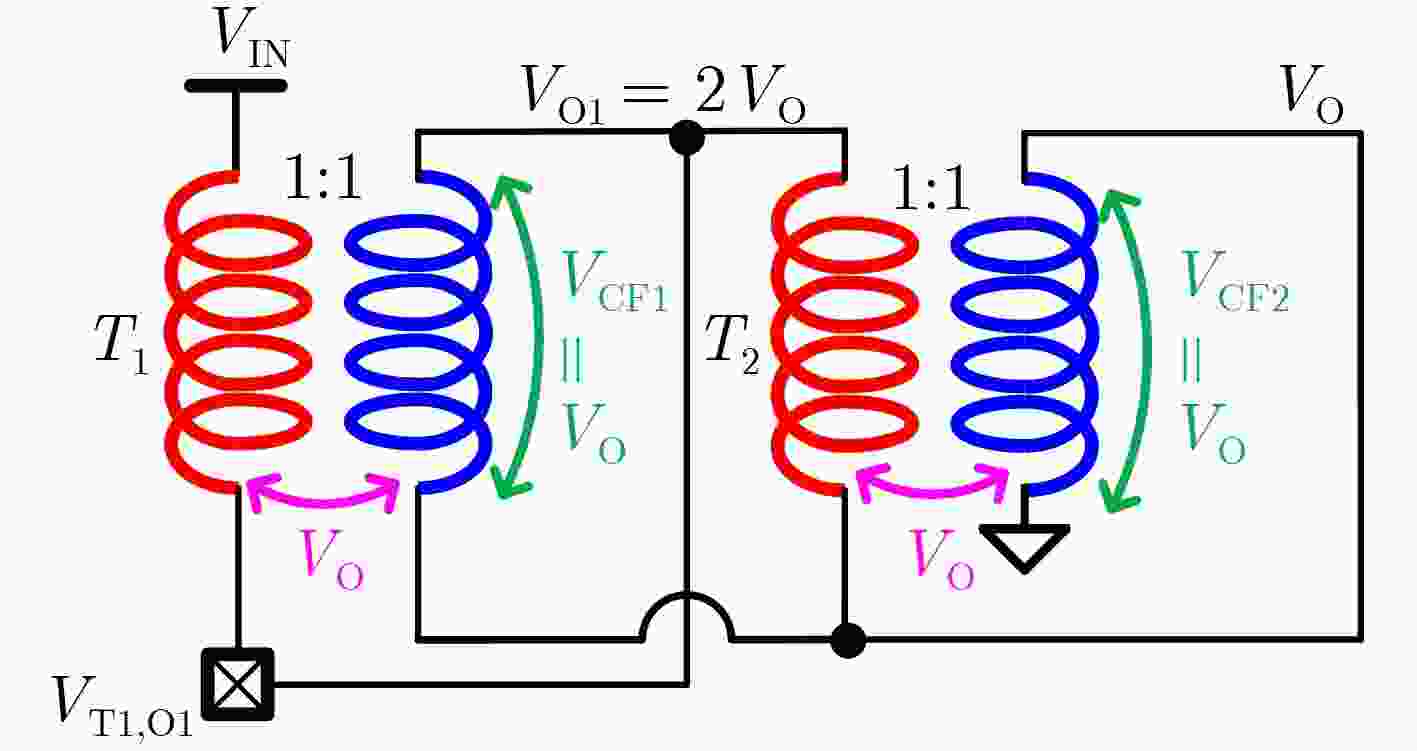

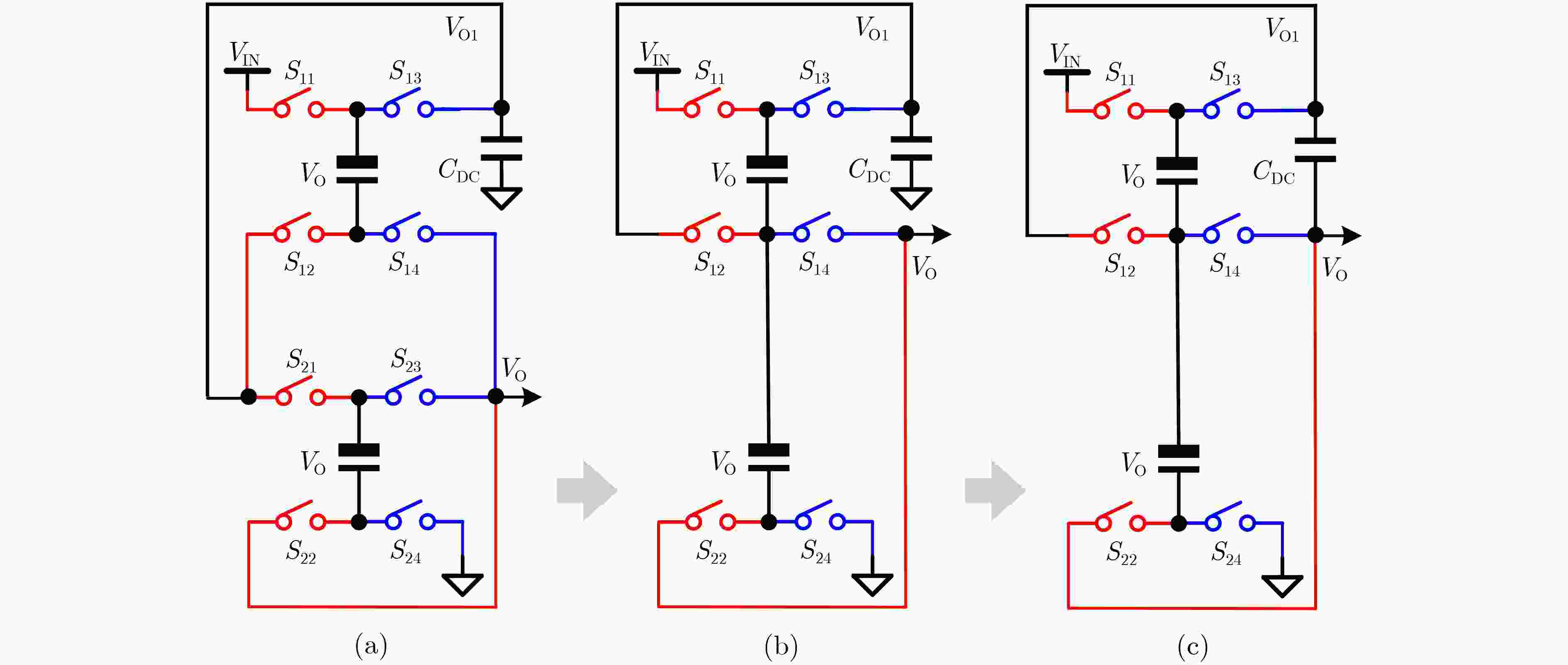

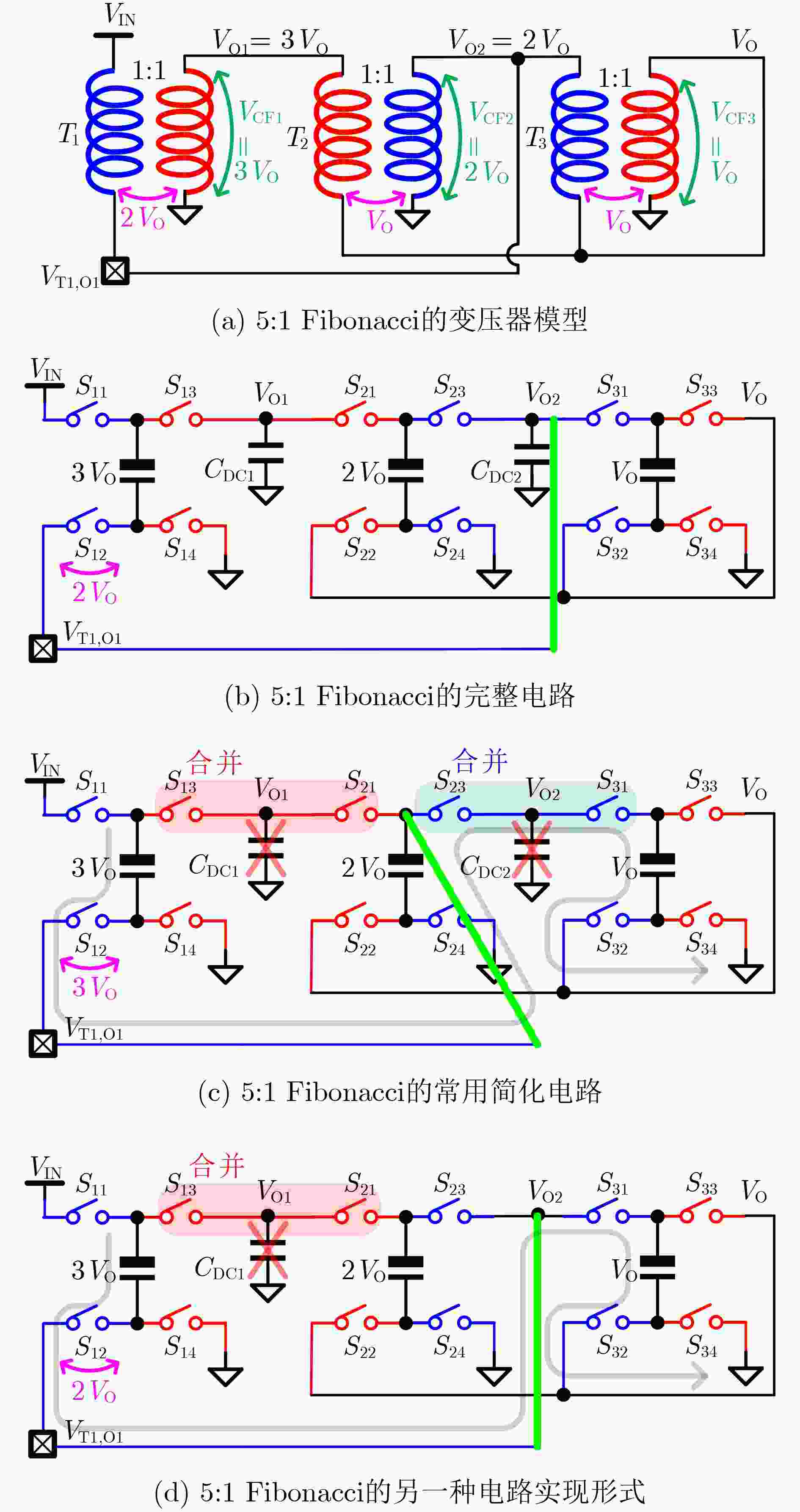

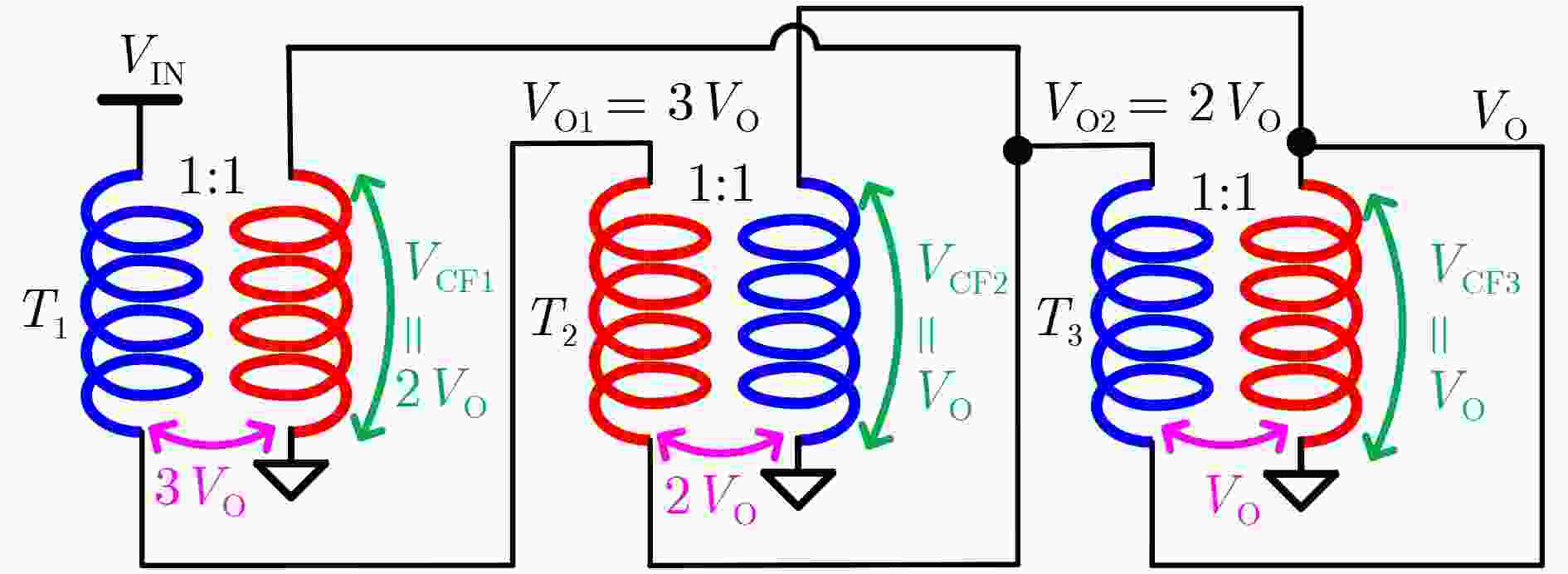

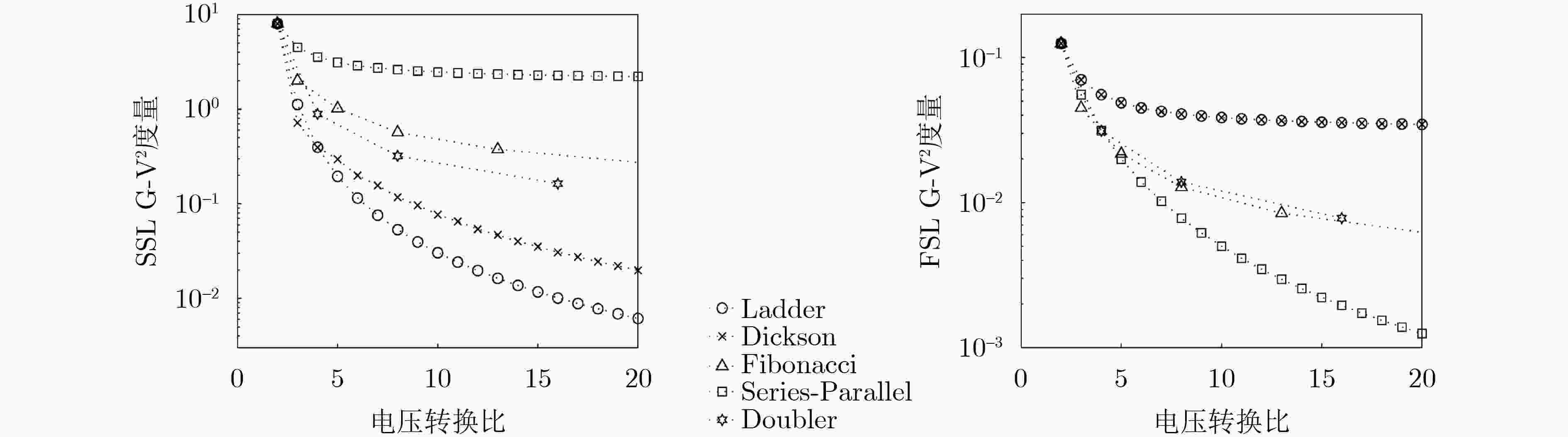

摘要: 开关电容(Switched Capacitor, SC) DC-DC转换器在很多领域有着广泛的应用。为应对大电压转换比(Voltage Conversion Ratio, VCR)的情况,前人提出了诸多拓扑结构。常用的拓扑结构包括Dickson,Cockcroft-Walton,Series-Parallel,Ladder,Fibonacci,Divider等等。这些拓扑结构有着各自的性能特点,适用于不同的场景。然而,对于这些不同的拓扑结构是如何产生的,本质的区别是什么,各自的优缺点是什么,并无直观的解释和分析。因此,该文从开关电容DC-DC转换器的等效变压器模型入手,分析了各个拓扑之间的本质区别,并展示了从等效模型到实际电路的演进过程,解释了规则和原因。Abstract: SC DC-DC converters have wide applications. Previous works proposed multiple topologies for a high voltage conversion ratio scenario, such as Dickson, Cockcroft-Walton, Series-Parallel, Ladder, Fibonacci and Divider. They have their own features, fitting different applications. However, it is unclear how these topologies are generated, what the main differences are between them, and what the advantages and disadvantages are. Therefore, this paper starts from the transformer model of the SC converters, analyzing the difference among them. Then, it is demonstrated how the SC converters evolve from the model to the real circuitries, where multiple intuitive understanding can be obtained.

-

Key words:

- Switched-capacitor /

- DC-DC converter /

- Transformer model /

- Evolution

-

图 12 常见降压型 SC 拓扑的 SSL 和 FSL 性能对比[6]

表 1 常见降压型SC拓扑的开关和电容的耐压汇总

结构 开关耐压 电容耐压 优缺点 4:1 Divider 2×VO, 1×VO 2×(2×VO), 1×VO SSL与FSL性能中等 4:1 Dickson 3×(1×VO) 3×VO, 2×VO, 1×VO SSL性能差 FSL性能好 4:1 CW 3×(1×VO) 2×VO, 2×VO, 1×VO SSL性能差 FSL性能好 4:1 S-P 3×VO, 2×VO, 1×VO 3×(1×VO) SSL性能差 FSL性能好 4:1 Ladder 3×(1×VO) 5×(1×VO) SSL性能差 FSL性能好 5:1 Fibonacci 2×VO, 2×(1×VO) 3×VO, 2×VO, 1×VO SSL与FSL性能中等 -

[1] MEGAHED M and ANAND T. A sub-μW energy harvester architecture with reduced top/bottom plate switching loss achieving 80.66% peak efficiency in 180-nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2023, 58(5): 1386–1399. doi: 10.1109/JSSC.2023.3241878. [2] WANG Yuanfei, HUANG Mo, LU Yan, et al. A continuously scalable-conversion-ratio SC converter with reconfigurable VCF step for high efficiency over an extended VCR range[C]. 2023 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, USA, 2023: 450–451. doi: 10.1109/ISSCC42615.2023.10067756. [3] WANG Yuanfei, HUANG Mo, LUO Ping, et al. Adaptive maximum power point tracking with model-based negative feedback control and improved V–f model[J]. IEEE Transactions on Circuits and Systems II:Express Briefs, 2021, 68(9): 3103–3107. doi: 10.1109/TCSII.2021.3097825. [4] KI W H, SU Feng, and TSUI C Y. Charge redistribution loss consideration in optimal charge pump design[C]. 2005 IEEE International Symposium on Circuits and Systems, Kobe, Japan, 2005: 1895–1898. doi: 10.1109/ISCAS.2005.1464982. [5] LE H P, SANDERS S R, and ALON E. Design techniques for fully integrated switched-capacitor DC-DC converters[J]. IEEE Journal of Solid-State Circuits, 2011, 46(9): 2120–2131. doi: 10.1109/JSSC.2011.2159054. [6] SEEMAN M D and SANDERS S R. Analysis and optimization of switched-capacitor DC–DC converters[J]. IEEE Transactions on Power Electronics, 2008, 23(2): 841–851. doi: 10.1109/TPEL.2007.915182. [7] DICKSON J F. On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique[J]. IEEE Journal of Solid-State Circuits, 1976, 11(3): 374–378. doi: 10.1109/JSSC.1976.1050739. [8] REGINATO L L and SMITH B H. A 600-kV, 10-mA DC Cockcroft-Walton rectifier using silicon diodes at 100 kc[J]. IEEE Transactions on Nuclear Science, 1965, 12(3): 274–278. doi: 10.1109/TNS.1965.4323635. [9] MAKOWSKI M S. A canonical switched capacitor DC-DC converter[C]. 2014 IEEE 15th Workshop on Control and Modeling for Power Electronics (COMPEL), Santander, Spain, 2014: 1–8. doi: 10.1109/COMPEL.2014.6877113. [10] HARADA I, UENO F, INOUE T, et al. Characteristics analysis of Fibonacci type SC transformer[J]. IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 1991, E75-A(6): 655–662. [11] BALLO A, GRASSO A D, and PALUMBO G. Comparison of the wide-frequency range dynamic behavior of the Dickson and Cockcroft-Walton voltage multipliers[C]. 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, USA: IEEE, 2021: 348–351. doi: 10.1109/MWSCAS47672.2021.9531743. [12] ABDULSLAM A and MERCIER P P. A symmetric modified multilevel ladder PMIC for battery-connected applications[J]. IEEE Journal of Solid-State Circuits, 2020, 55(3): 767–780. doi: 10.1109/JSSC.2019.2957658. [13] HU Tingxu, HUANG Mo, LU Yan, et al. 11.2 A 12V-to-1V quad-output switched-capacitor buck converter with shared DC capacitors achieving 90.4% peak efficiency and 48mA/mm3 power density at 85% efficiency[C]. 2023 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA, 2023: 184–186. doi: 10.1109/ISSCC42615.2023.10067463. [14] HU Tingxu, HUANG Mo, MARTINS R P, et al. A 12-to-1 V quad-output switched-capacitor buck converter with shared DC capacitors[J]. IEEE Journal of Solid-State Circuits, 2023, 58(12): 3492–3502. doi: 10.1109/JSSC.2023.3301068. [15] https://en.wikipedia.org/wiki/Fibonacci_sequence. [16] HUANG Mo, LU Yan, and MARTINS R P. 11.5 A 2-phase soft-charging hybrid boost converter with doubled-switching pulse width and shared bootstrap capacitor achieving 93.5% efficiency at a conversion ratio of 4.5[C]. 2020 IEEE International Solid- State Circuits Conference - (ISSCC), Francisco, USA, 2020: 198–200. doi: 10.1109/ISSCC19947.2020.9062902. [17] HUANG Mo, LU Yan, HU Tingxu, et al. A hybrid boost converter with cross-connected flying capacitors[J]. IEEE Journal of Solid-State Circuits, 2021, 56(7): 2102–2112. doi: 10.1109/JSSC.2020.3044062. [18] HU Tingxu, HUANG Mo, LU Yan, et al. A 4A 12-to-1 flying capacitor cross-connected DC-DC converter with inserted D > 0.5 control achieving > 2x transient inductor current slew rate and 0.73× theoretical minimum output undershoot of DSD[C]. 2022 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, USA, 2022: 302–303. doi: 10.1109/ISSCC42614.2022.9731669. [19] HU Tingxu, HUANG Mo, MARTINS R P, et al. A 12-to-1 flying capacitor cross-connected buck converter with inserted D > 0.5 control for fast transient response[J]. IEEE Journal of Solid-State Circuits, 2023, 58(11): 3207–3218. doi: 10.1109/JSSC.2023.3297111. -

下载:

下载:

下载:

下载: