采用自适应连续时间线性均衡器和判决反馈均衡器算法的一种16 Gbit/s 并转串/串转并接口

doi: 10.11999/JEIT230668 cstr: 32379.14.JEIT230668

A 16 Gbit/s Serializer/Deserializer with Adaptive Continuous Time Linear Equalizer and Decision Feedback Equalizer Equalization Algorithm

-

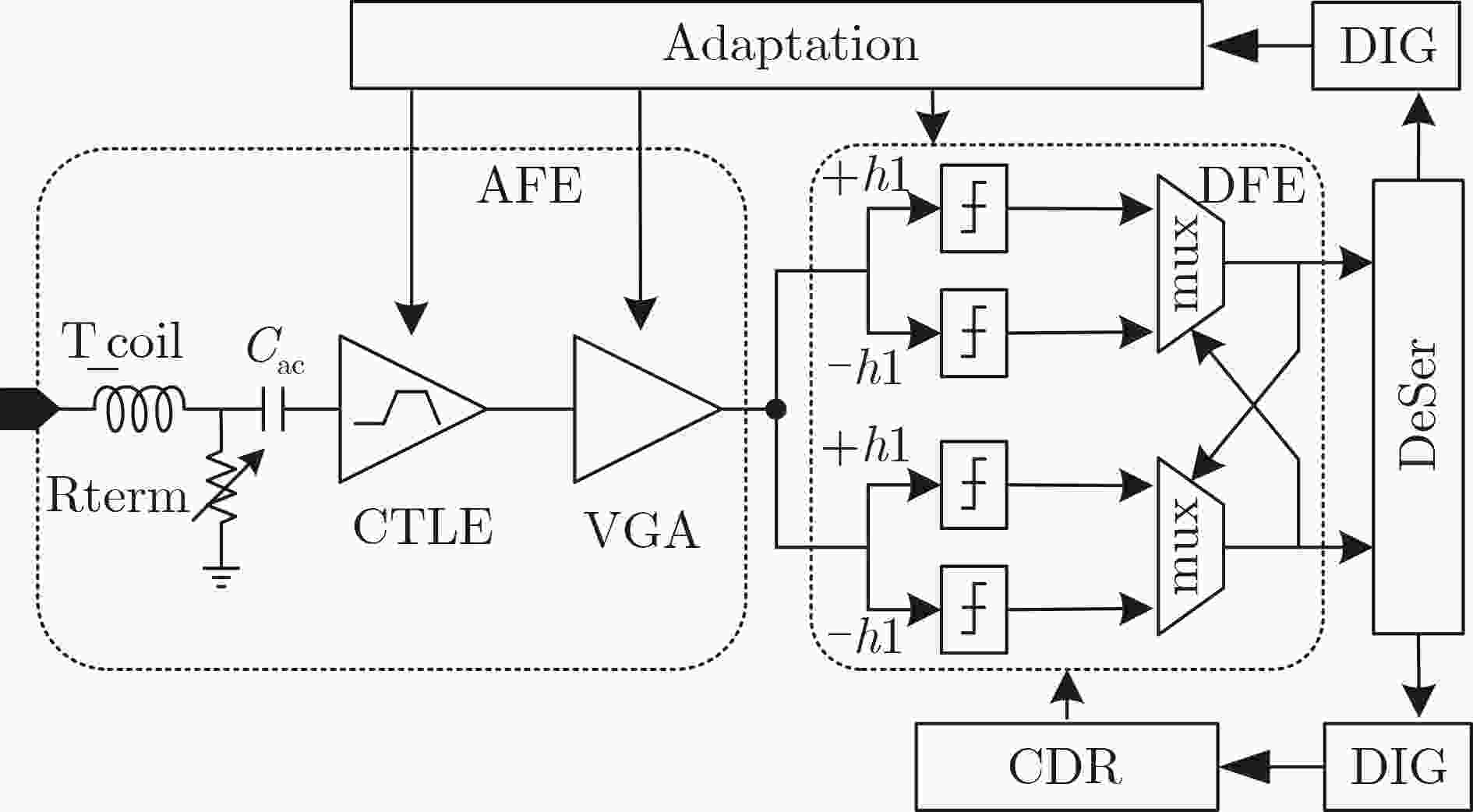

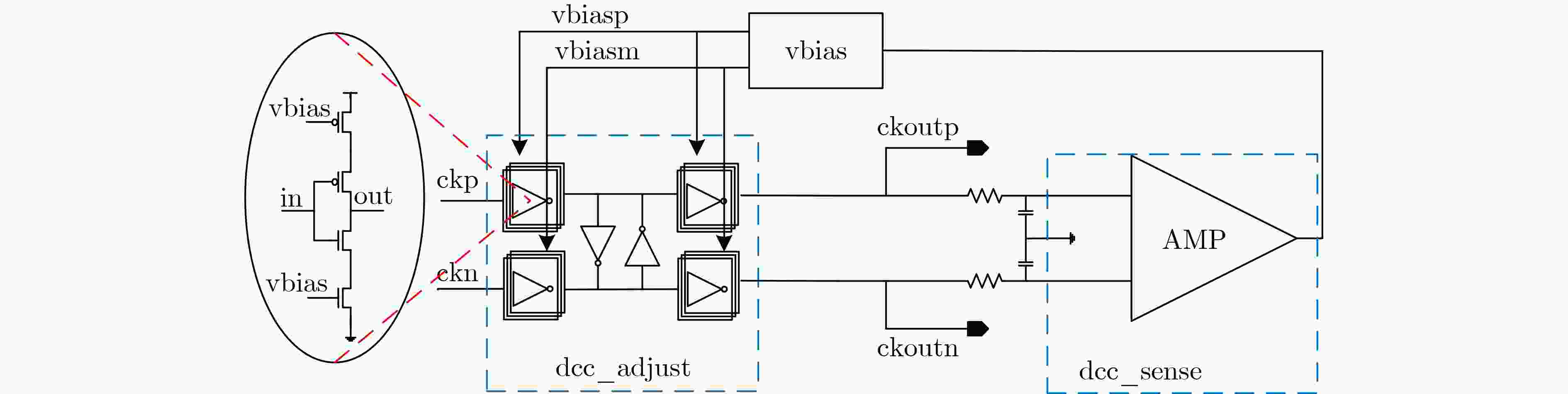

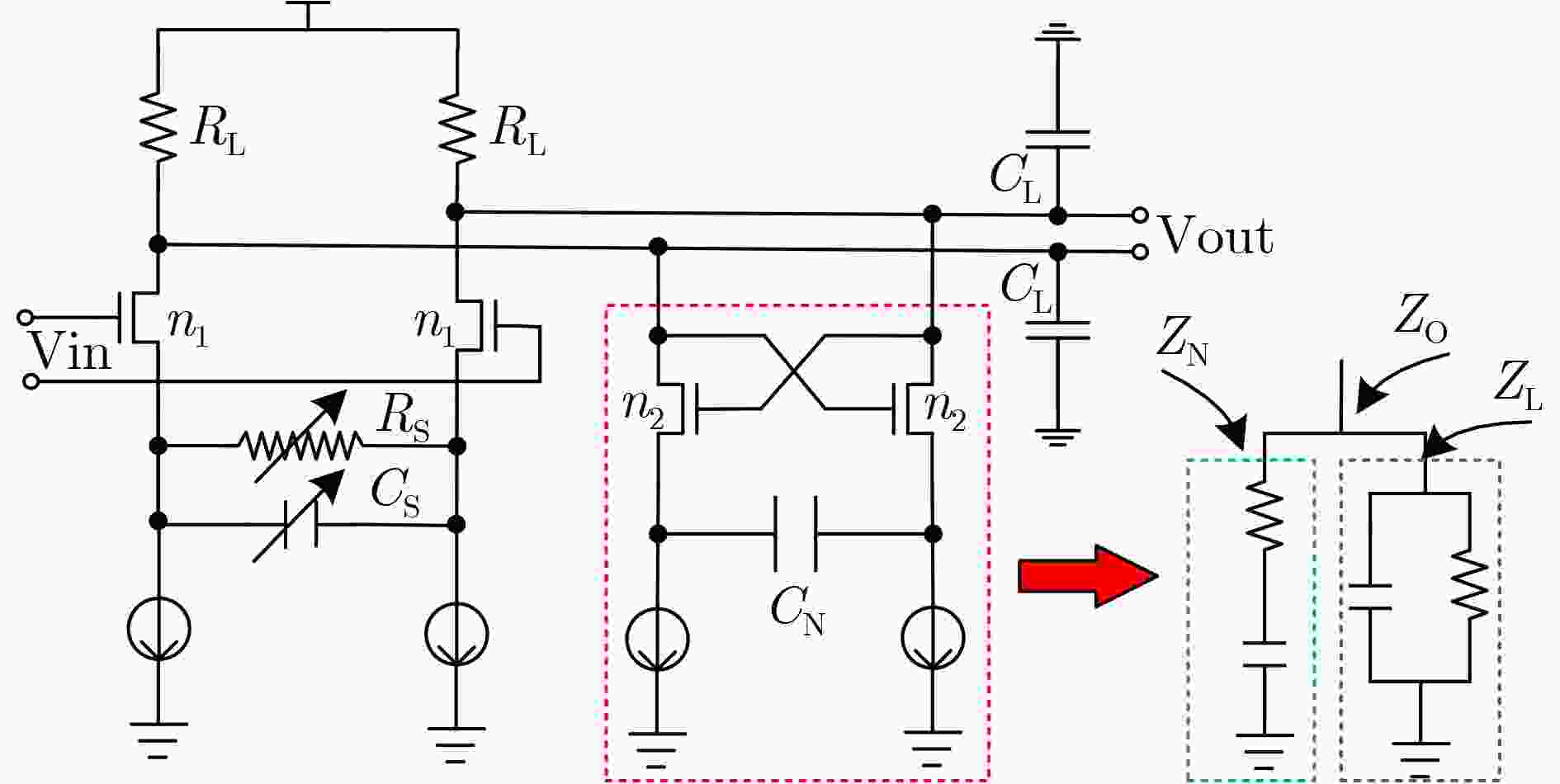

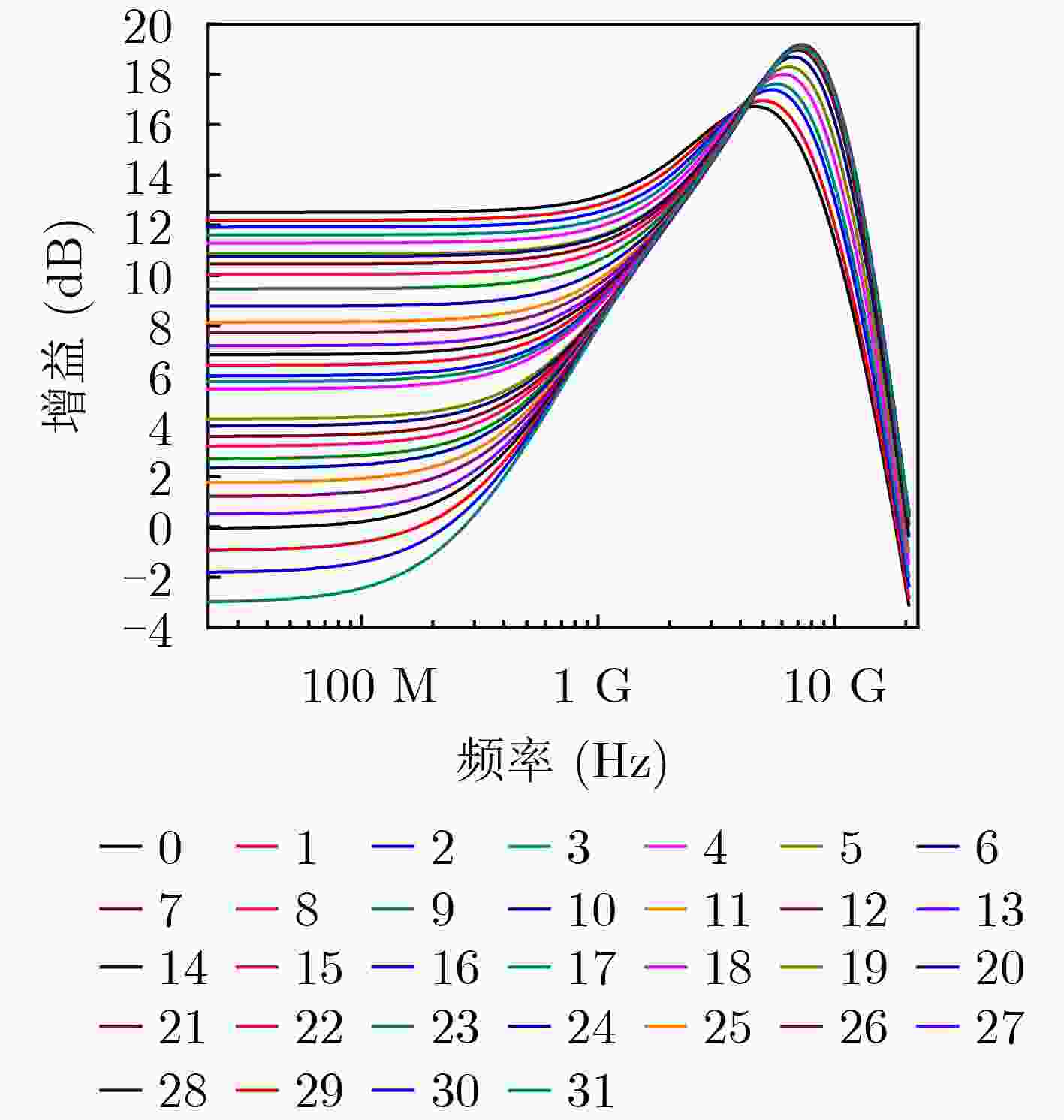

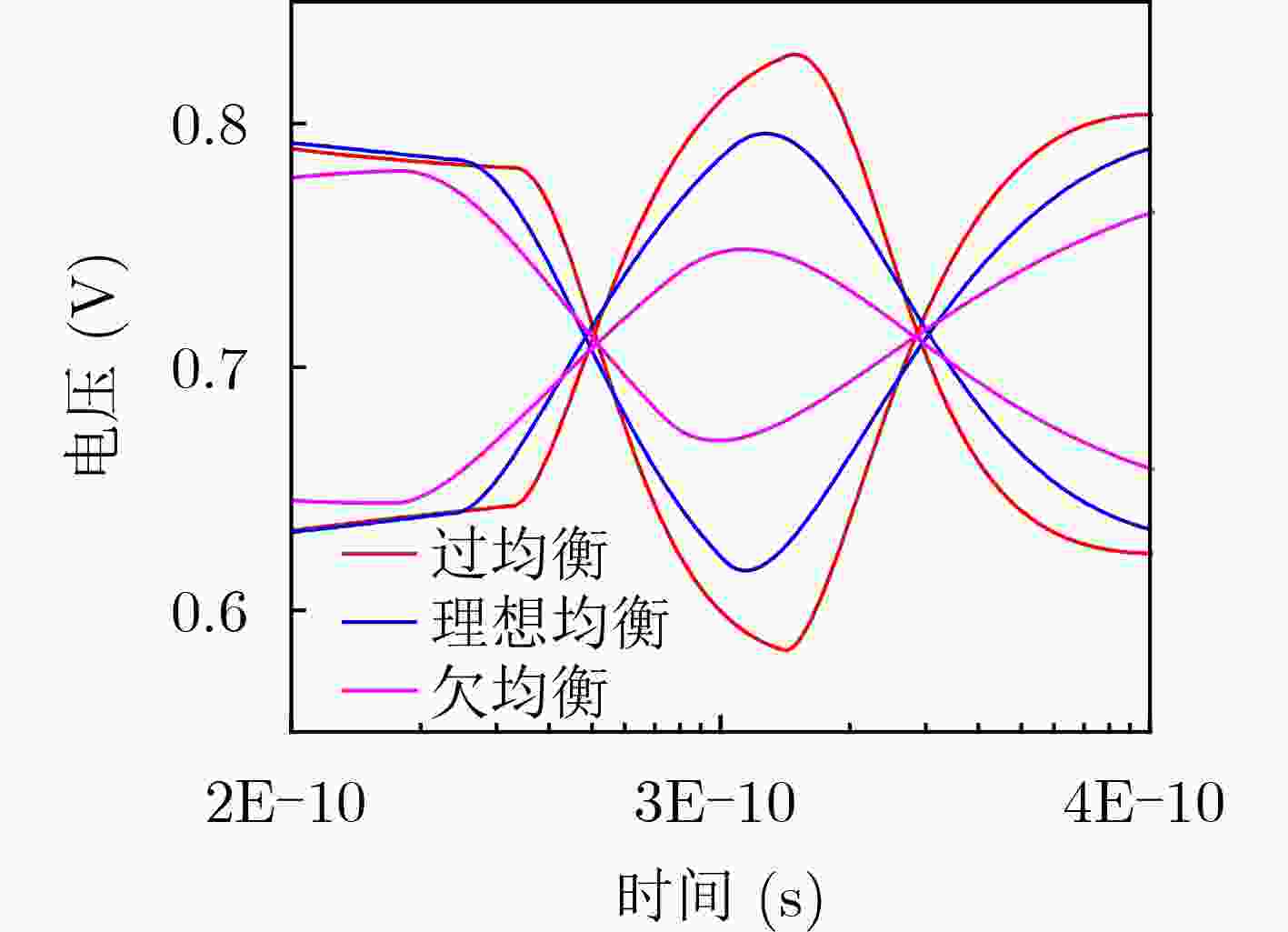

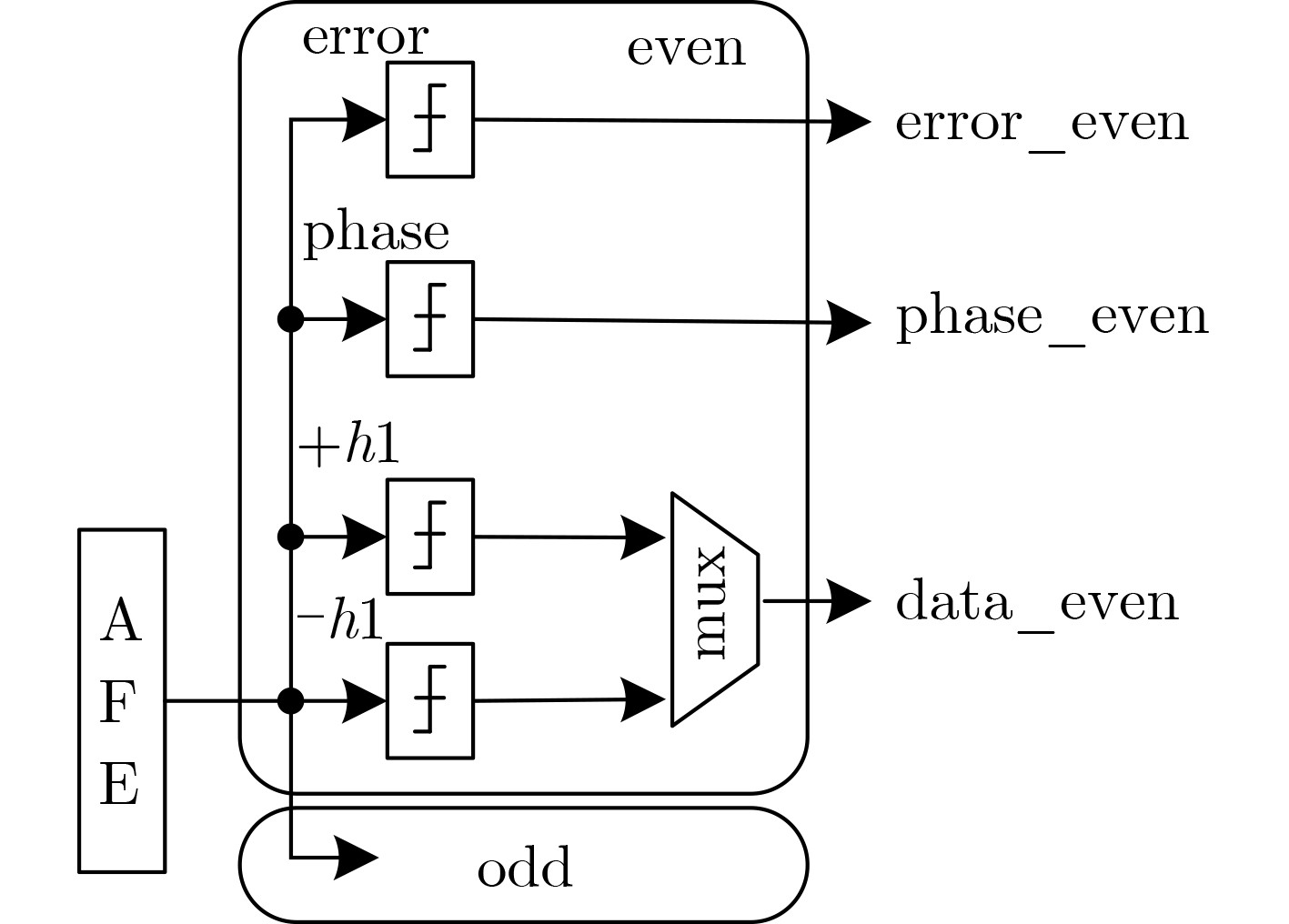

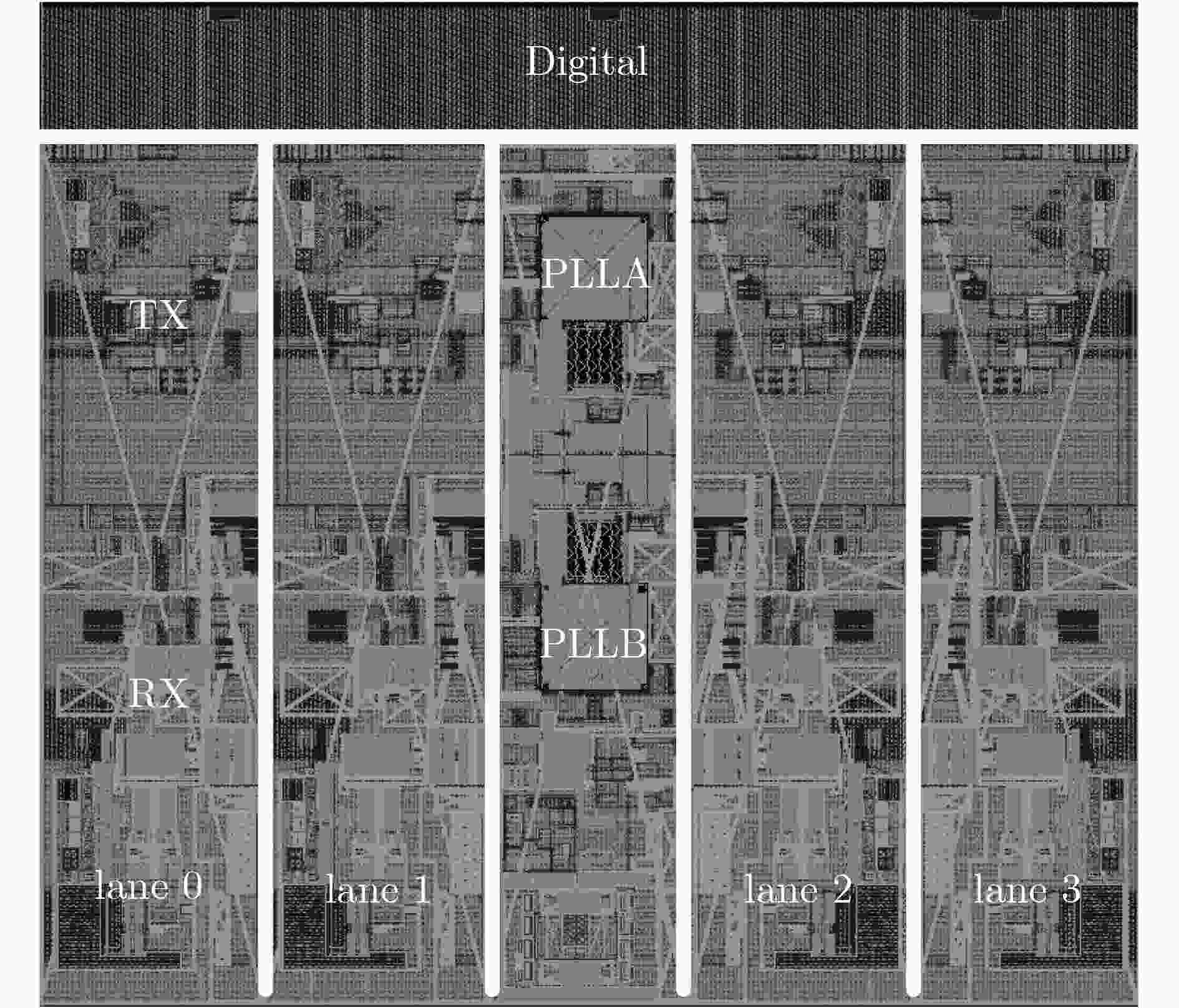

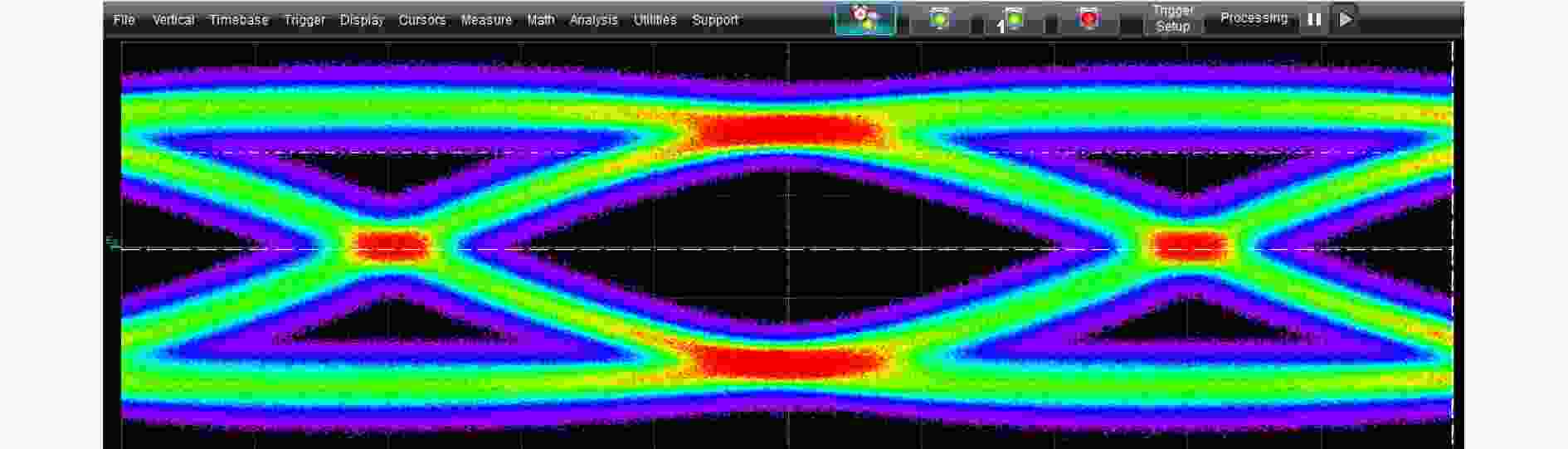

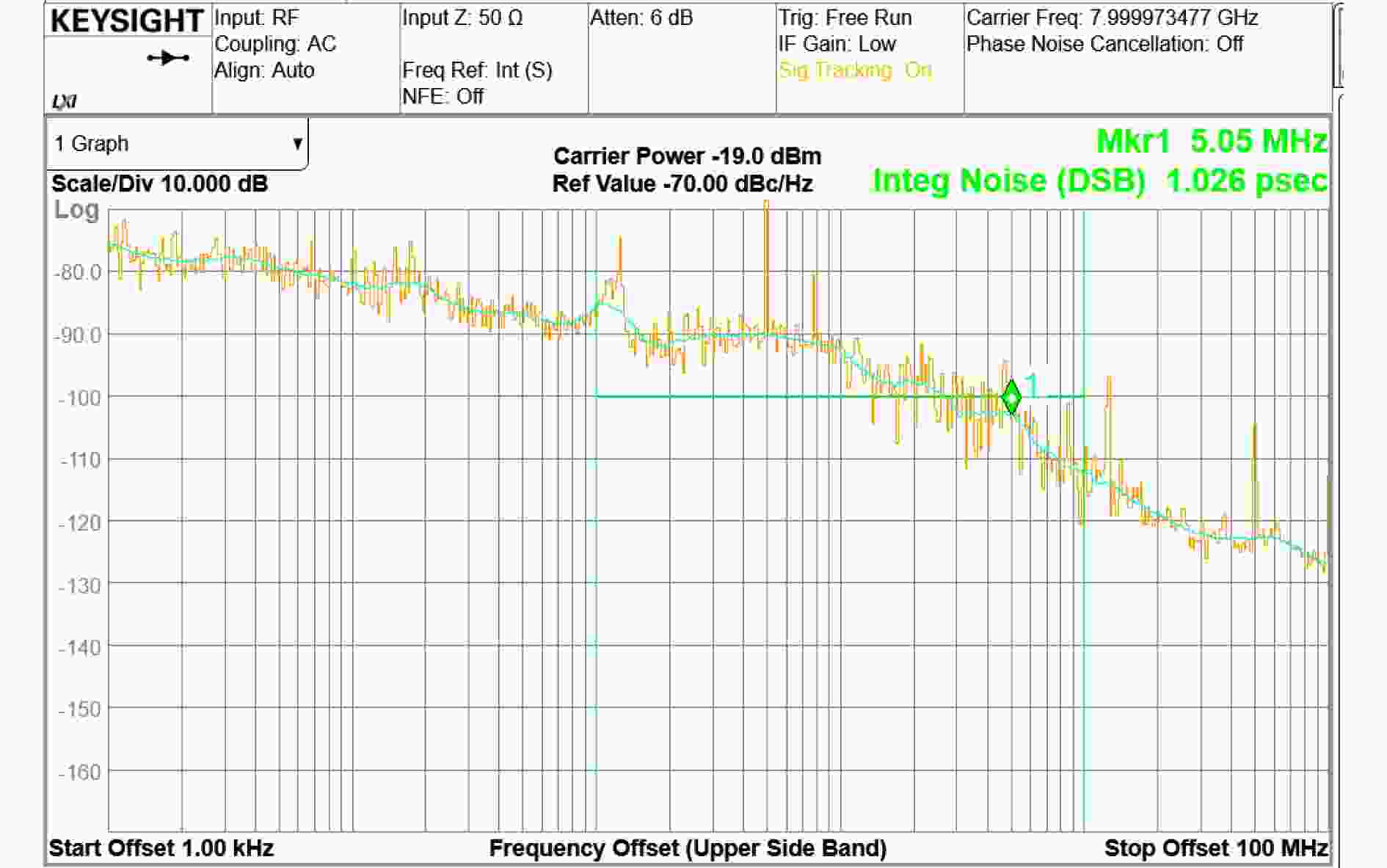

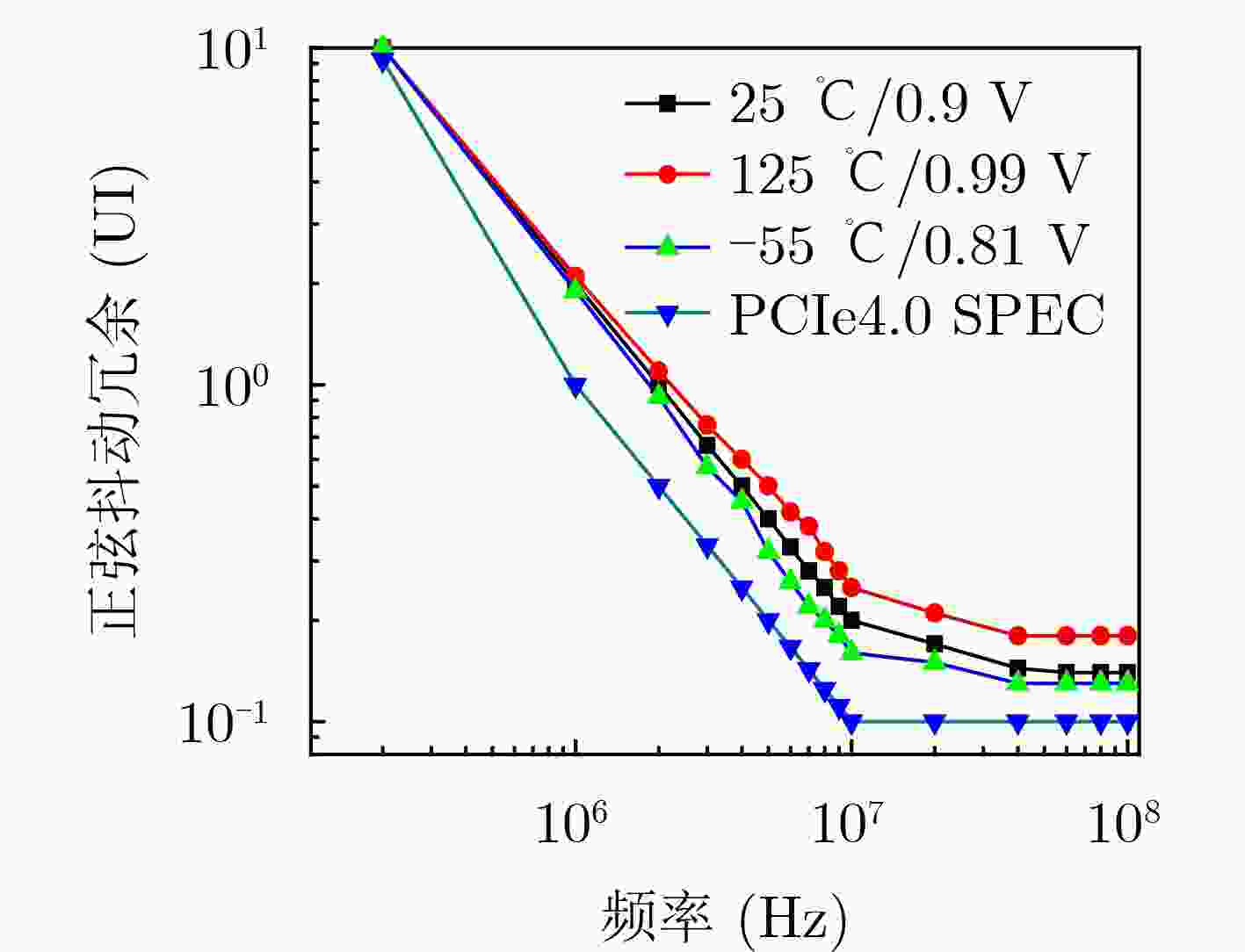

摘要: 该文在体硅CMOS工艺下设计了一种16 Gbit/s并转串/串转并接口(SerDes)芯片,该SerDes由4个通道(lanes)和2个锁相环(PLLs)组成。在接收器模拟前端(AFE)采用负阻抗结构连续时间线性均衡器(CTLE),得到22.9 dB高频增益,利用5-tap判决反馈均衡器(DFE)进一步对信号码间干扰(ISI)做补偿,其中tap1做展开预计算处理,得到充足的时序约束条件。采用最小均方根(LMS)算法自适应控制CTLE和DFE的补偿系数来对抗工艺、电源和温度波动带来的影响。测试结果表明,芯片工作在16 Gbit/s时,总功耗为615 mW。发射器输出信号眼高为143 mV,眼宽43.8 ps(0.7UI),接收器抖动容忍指标在各频点均满足PCIe4.0协议要求,工作温度覆盖–55°C~125°C,电源电压覆盖0.9 V±10%,误码率小于1E-12。Abstract: A 16 Gbit/s Serializer/Deserializer interface(SerDes) chip which is composed of 4 lanes and 2 Phase-Locked Loop(PLLs), is designed in bulk CMOS technology. A negative impedance structure Continuous Time Linear Equalizer(CTLE) is used in the Analog Front End(AFE) of the receiver to obtain 22.9 dB high frequency gain. Further, 5-tap Decision Feedback Equalizer(DFE) is used to compensate the Inter Symbol Interference(ISI), and tap1 unrolled to obtain sufficient timing constraints. Least Mean Square(LMS) algorithm is used to control adaptive CTLE and DFE compensation coefficient to counter the influence of process, power supply and temperature fluctuations. The measurement results show that, the total power consumption is 615mW when working at 16 Gbit/s. Transmitter output signal eye height is 143 mV, width is 43.8 ps(0.7UI), jitter tolerance of the receiver contents the PCIe4.0 protocol requirements at all frequency, working temperature cover –55°C~125°C, power supply voltage cover 0.9 V±10%, bit error rate is less than 1E-12.

-

表 1 判定CTLE均衡情况表

d(n–1) p(n–1) d(n) $\Delta $(n) 状态 –1 –1 1 –1 欠均衡 –1 1 1 1 过均衡 1 –1 –1 1 过均衡 1 1 –1 –1 欠均衡 表 2 不同pattern对眼图的影响

pattern 眼高(mV) 眼宽(ps) 确定性

抖动(ps)随机性

抖动(ps)PRBS7 174 46.8 3.1 0.94 PRBS15 156 45.1 3.2 0.95 PRBS23 147 44.7 3.3 0.98 PRBS31 143 43.8 3.5 1.00 表 3 近年来学者研究成果对比

文献[15]* 文献[16] 文献[17] 本文 工艺 65 nm 40 nm 28 nm 28 nm 电源电压 1.05 V 1.2 V 0.92 V 0.81~0.99 V 工作温度 -- -- -- –55~125°C 传输速率 5~15 Gbit/s 16 Gbit/s 5~28 Gbit/s 1.25~16 Gbit/s 信道插损 24 dB@7.5 GHz 34 dB@8 GHz 15 dB@14 GHz 29 dB@8 GHz 面积/lane 0.09 mm2 0.54 mm2 0.88 mm2 0.54 mm2 功耗/lane 75 mW 235 mW 242.3 mW 153.7 mW *:只研究了TX+RX各项参数 -

[1] ALI T, ABDULLATIF M, PARK H, et al. 56/112Gbps wireline transceivers for next generation data centers on 7nm FINFET CMOS technology[C]. The 2021 IEEE Custom Integrated Circuits Conference (CICC), Austin, USA, 2021: 1–6. [2] KIMURA H, AZIZ P M, JING T, et al. A 28 Gb/s 560 mW multi-standard SerDes with single-stage analog front-end and 14-Tap decision feedback equalizer in 28 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2014, 49(12): 3091–3103. doi: 10.1109/JSSC.2014.2349974 [3] AGHIGHI A, ALAMEH A H, TAHERZADEH-SANI M, et al. A 10-Gb/s low-power low-voltage CTLE using gate and bulk driven transistors[C]. The 2016 IEEE International Conference on Electronics, Circuits and Systems, Monte Carlo, Monaco, 2016: 217–220. [4] LI Bowen, JIAO B, CHOU C, et al. CTLE adaptation using deep learning in high-speed SerDes link[C]. The IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, USA, 2020: 952–955. [5] SEN S, UPADHYAYA U, KONDREDDY K R, et al. A low jitter digital loop CDR based 8–16 Gbps SerDes in 65 nm CMOS technology[C]. The 34th International Conference on VLSI Design and 2021 20th International Conference on Embedded Systems, Guwahati, India, 2021: 216–221. [6] 付玉山, 马奎, 唐重林, 等. 一种28Gbps高速SERDES发射器[J]. 微电子学与计算机, 2021, 38(10): 103–108. doi: 10.19304/J.ISSN1000-7180.2021.0017FU Yushan, MA Kui, TANG Chonglin, et al. 28Gbps high-speed SERDES transmitter[J]. Microelectronics&Computer, 2021, 38(10): 103–108. doi: 10.19304/J.ISSN1000-7180.2021.0017 [7] FAN W, CHEN Yingmei, ZHAO Qingyi, et al. A 56 Gb/s half-rate PAM4 SerDes receiver with LC-VCO based CDR in 40-nm CMOS technology[C]. The IEEE 8th International Conference on Computer and Communications (ICCC), Chengdu, China, 2022: 1106–1110. [8] CHI Runze, CHEN Junkun, GU Youzhi, et al. A 161mW 32Gb/s ADC-based NRZ SerDes receiver front end in 28nm[C]. The 2021 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Zhuhai, China, 2021: 10–11. [9] JAISWAL A, WALK D, FANG Yuan, et al. Low-power high-speed on-chip asynchronous Wave-pipelined CML SerDes[C]. Proceedings of the 27th IEEE International System-on-Chip Conference, Las Vegas, USA, 2014: 5–10. [10] 李沛杰, 沈剑良, 苑红晓, 等. 一种应用于软件定义互连系统的多协议SerDes电路[J]. 电子学报, 2021, 49(4): 817–823. doi: 10.12263/DZXB.20200149LI Peijie, SHEN Jianliang, YUAN Hongxiao, et al. A multi-protocol SerDes circuit for the applications in software defined interconnection system[J]. Acta Electronica Sinica, 2021, 49(4): 817–823. doi: 10.12263/DZXB.20200149 [11] 刘敏, 郑旭强, 李伟杰, 等. 一种应用在50~64Gb/s的SERDES接收机中的DSP的设计与实现[J]. 微电子学与计算机, 2022, 39(11): 102–109. doi: 10.19304/J.ISSN1000-7180.2022.0261LIU Min, ZHENG Xuqiang, LI Weijie, et al. A 50~64Gb/s DSP used in SERDES receiver[J]. Microelectronics&Computer, 2022, 39(11): 102–109. doi: 10.19304/J.ISSN1000-7180.2022.0261 [12] CHEN Jianjun, CHI Yaqing, LIANG Bin, et al. ASET and TID characterization of a radiation hardened bandgap voltage reference in a 28-nm bulk CMOS technology[J]. IEEE Transactions on Nuclear Science, 2022, 69(5): 1141–1147. doi: 10.1109/TNS.2022.3152496 [13] ELSAYED A H, TADROS R N, GHONEIMA M, et al. Low-power all-digital manchester-encoding-based high-speed serdes transceiver for on-chip networks[C]. The 2014 IEEE International Symposium on Circuits and Systems, Melbourne, Australia, 2014: 2752–2755. [14] 文溢, 陈建军, 梁斌, 等. 28nm CMOS工艺8-Gbps SerDes单粒子辐射特性研究[J]. 电子学报, 2022, 50(11): 2653–2658. doi: 10.12263/DZXB.20211691WEN Yi, CHEN Jianjun, LIANG Bin, et al. Research on single-event radiation characteristics of an 8-Gbps SerDes in a 28nm CMOS technology[J]. Acta Electronica Sinica, 2022, 50(11): 2653–2658. doi: 10.12263/DZXB.20211691 [15] BALAMURUGAN G, KENNEDY J, BANERJEE G, et al. A scalable 5–15Gbps, 14–75mW low power I/O transceiver in 65nm CMOS[C]. The 2007 IEEE Symposium on VLSI Circuits, Kyoto, Japan, 2007: 270–271. [16] JOY A K, MAIR H, LEE H C, et al. Analog-DFE-based 16Gb/s SerDes in 40nm CMOS that operates across 34dB loss channels at Nyquist with a baud rate CDR and 1.2Vpp voltage-mode driver[C]. The 2011 IEEE International Solid-State Circuits Conference, San Francisco, USA, 2011: 350–351. [17] MAHANI M, ZAVARI R, LIM S T, et al. Multi-standard 5 Gbps to 28.2 Gbps adaptive, single voltage SerDes transceiver with analog FIR and 2-tap unrolled DFE in 28nm CMOS[C]. The 2017 IEEE Radio Frequency Integrated Circuits Symposium, Honolulu, USA, 2017: 23–26. -

下载:

下载:

下载:

下载: