A Universal Test Access Port Controller Circuit Design for Chiplet Testing

-

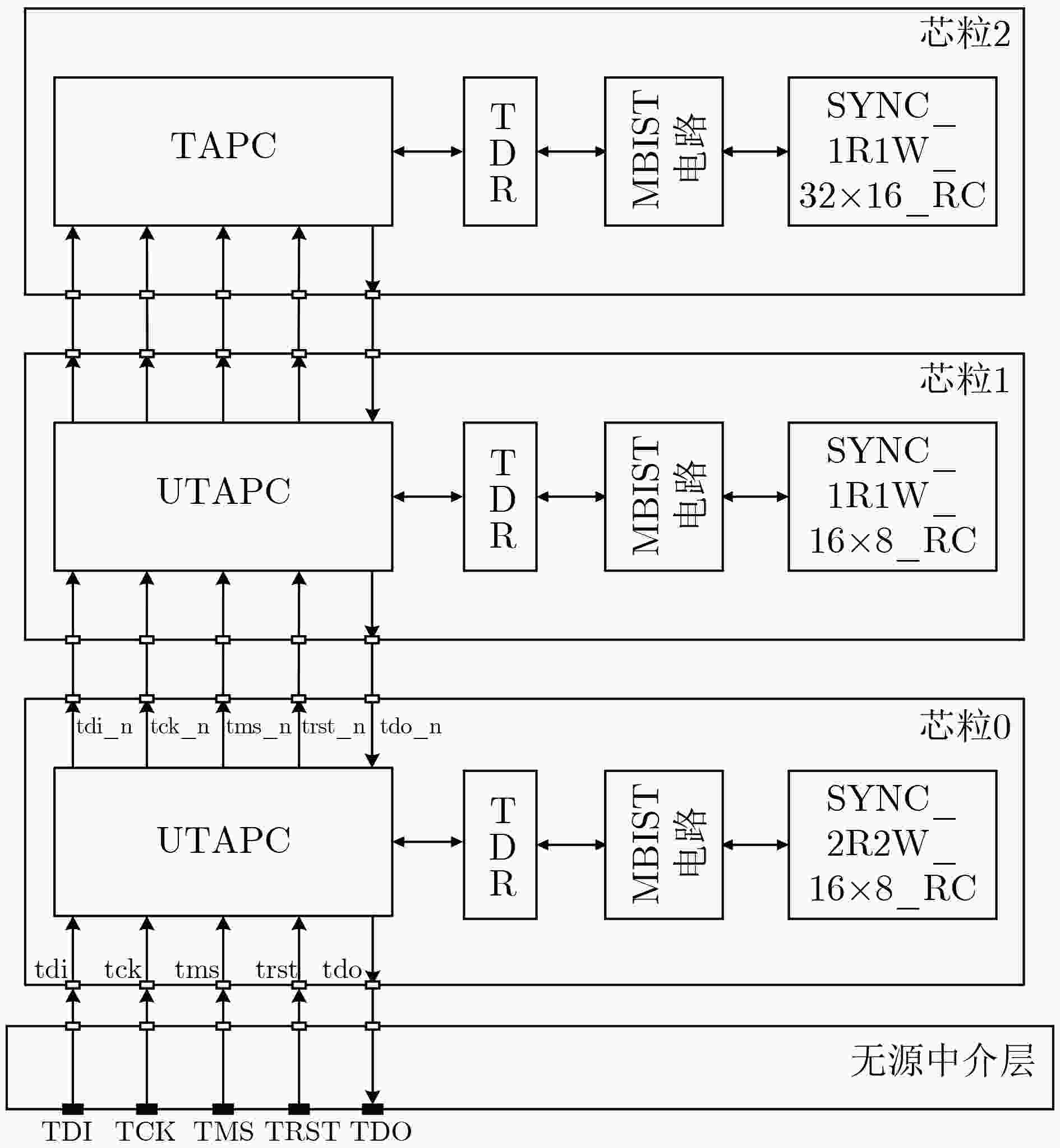

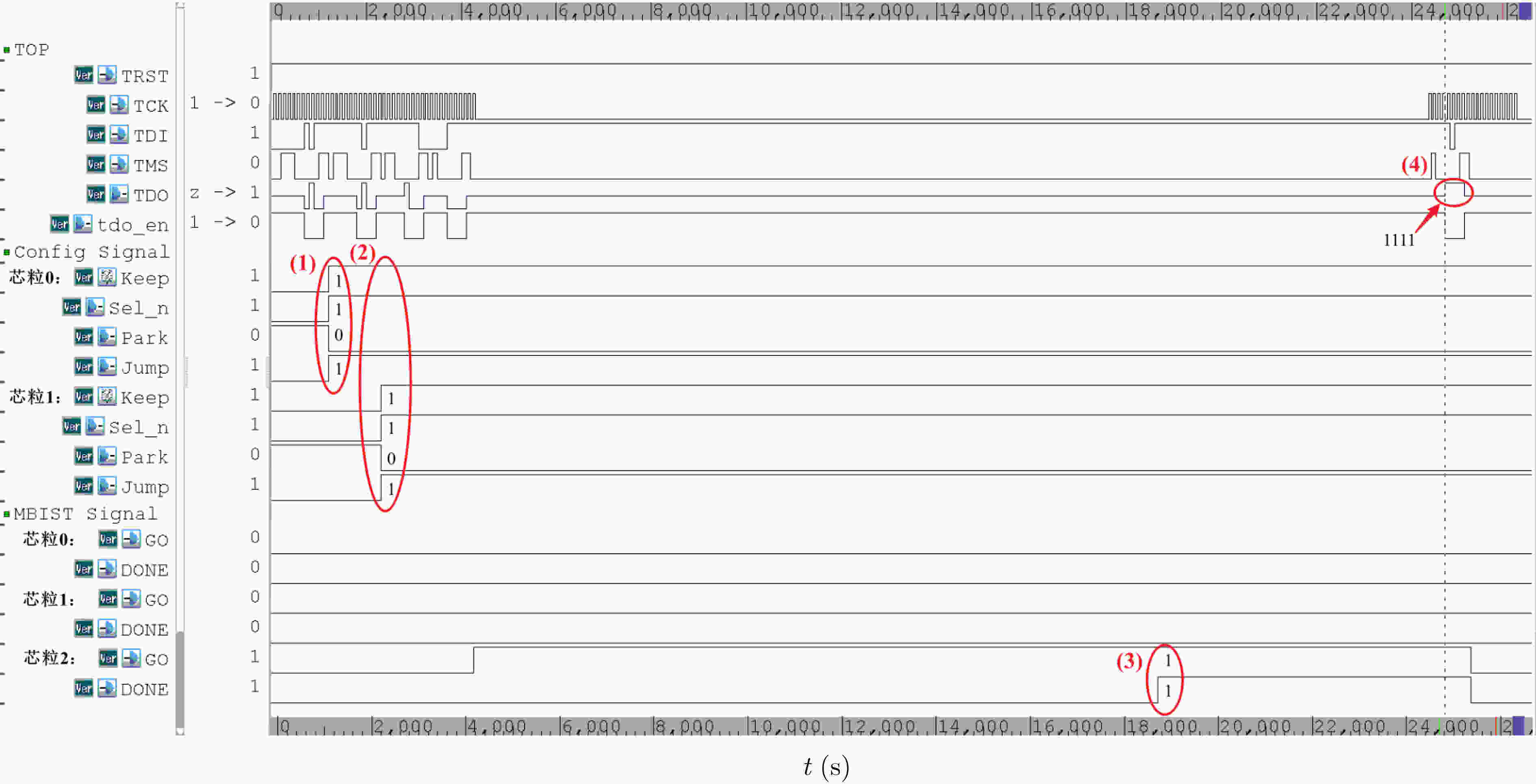

摘要: 在后摩尔时代里,Chiplet是当前最火热的异构芯片集成技术,具有复杂的多芯粒堆叠结构等特点。为了解决Chiplet在不同堆叠结构中的芯粒绑定后测试问题,基于IEEE 1838标准协议,该文提出一种适用于Chiplet测试的通用测试访问端口控制器(UTAPC)电路。该电路在传统测试访问端口(TAP)控制器的基础上设计了Chiplet专用有限状态机(CDFSM),增加了Chiplet测试路径配置寄存器和Chiplet测试接口电路。在CDFSM产生的配置寄存器控制信号作用下,通过Chiplet测试路径配置寄存器输出的配置信号来控制Chiplet测试接口电路以设置Chiplet的有效测试路径,实现跨层访问芯粒。仿真结果表明,所提UTAPC电路适用于任意堆叠结构的Chiplet的可测试性设计,可以有效地选择芯粒的测试,还节省了测试端口和测试时间资源并提升了测试效率。

-

关键词:

- 3维集成电路 /

- Chiplet /

- 中介层 /

- 可测试性设计 /

- IEEE 1838标准协议

Abstract: In the post-Moore era, Chiplet is the most hottest integration technique for heterogeneous integrated circuit, which is characterized by complex multi-core stacked structures. In order to solve the post-bonding test problem of Chiplet in different stacked structures, a Universal Test Access Port Controller (UTAPC) circuit is proposed based on IEEE 1838 standard protocol. Based on the traditional Test Access Port (TAP) controller, the Chiplet Dedicated Finite State Machine (CDFSM) is designed, also the Chiplet configuration registers and Chiplet test interface circuit are added. Under the influence of the configuration registers’ control signals generated by the CDFSM, the configuration signals outputted from the Chiplet configuration registers are used to control the Chiplet test interface circuit to set up the effective test path of Chiplet, which realized to access cores cross layers. The simulation results demonstrate that the proposed UTAPC circuit is suitable for the design for test of Chiplet with arbitrary stacked structures. It can not only choose to test cores flexibly, but also save the resources of test ports and test time, as well as improve the test efficiency.-

Key words:

- 3D integrated circuit /

- Chiplet /

- Interposer /

- Design for test /

- IEEE 1838 standard protocol

-

表 1 基于UTAPC与根据IEEE 1838标准协议设计的两种测试方案进行测试的时间对比(ns)

测试方案 测试目标 配置有效测试

路径阶段的

测试时间测试芯粒阶段的测试时间 总测试时间 根据IEEE 1838标准协议[11]设计 包含无源中介层的3D Chiplet里的芯粒2 3100 24000 27100 包含有源中介层的2.5D Chiplet里的芯粒0、芯粒1和芯粒2 2400 25800 28200 基于UTAPC电路设计 包含无源中介层的3D Chiplet里的芯粒2 2400 22800 25200 包含有源中介层的2.5D Chiplet里的芯粒0、芯粒1和芯粒2 1700 25200 26900 -

[1] LOH G H, NAFFZIGER S, and LEPAK K. Understanding Chiplets today to anticipate future integration opportunities and limits[C]. Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2021: 142–145. [2] HANCOCK T M and DEMMIN J C. Heterogeneous and 3D integration at DARPA[C]. 2019 International 3D Systems Integration Conference (3DIC), Sendai, Japan, 2019: 1–4. [3] 余乐, 杨海钢, 谢元禄, 等. 三维集成电路中硅通孔缺陷建模及自测试/修复方法研究[J]. 电子与信息学报, 2012, 34(9): 2247–2253. doi: 10.3724/SP.J.1146.2012.00048YU Le, YANG Haigang, XIE Yuanlu, et al. A 3D IC self-test and recovery method based on through silicon via defect modeling[J]. Journal of Electronics &Information Technology, 2012, 34(9): 2247–2253. doi: 10.3724/SP.J.1146.2012.00048 [4] HUTNER M, SETHURAM R, VINNAKOTA B, et al. Special session: Test challenges in a Chiplet marketplace[C]. 2020 IEEE 38th VLSI Test Symposium (VTS), San Diego, USA, 2020: 1–12. [5] HERRAULT F, WONG J, RAMOS I, et al. Chiplets in Wafers (CiW) - Process design kit and demonstration of high-frequency circuits with GaN Chiplets in silicon interposers[C]. IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, USA, 2021: 178–184. [6] 常郝, 梁华国, 蒋翠云, 等. 一种3D堆叠集成电路中间绑定测试时间优化方案[J]. 电子学报, 2015, 43(2): 393–398. doi: 10.3969/j.issn.0372-2112.2015.02.029CHANG Hao, LIANG Huaguo, JIANG Cuiyun, et al. Optimization scheme for mid-bond test time on 3D-stacked ICs[J]. Acta Electronica Sinica, 2015, 43(2): 393–398. doi: 10.3969/j.issn.0372-2112.2015.02.029 [7] KABIR M A, HUNG W, HO T Y, et al. Holistic and in-context design flow for 2.5D Chiplet-package interaction co-optimization[C]. 2021 International Symposium on VLSI Design, Automation and Test (VLSI-DAT), Hsinchu, China, 2021: 1–4. [8] FKIH Y, VIVET P, ROUZEYRE B, et al. A JTAG based 3D DfT architecture using automatic die detection[C]. Proceedings of the 2013 9th Conference on Ph. D. Research in Microelectronics and Electronics (PRIME), Villach, Austria, 2013: 341–344. [9] DURUPT J, VIVET P, and SCHLOEFFEL J. IJTAG supported 3D DFT using chiplet-footprints for testing multi-chips active interposer system[C]. 2016 21th IEEE European Test Symposium (ETS), Amsterdam, Netherlands, 2016: 1–6. [10] MARINISSEN E J, DE WACHTER B, O'LOUGHLIN S, et al. Vesuvius-3D: A 3D-DfT demonstrator[C]. 2014 International Test Conference (ITC), Seattle, USA, 2014: 1–10. [11] IEEE Computer Society. IEEE 1838-2019 IEEE standard for test access architecture for three-dimensional stacked integrated circuits[S]. New York: IEEE, 2020. [12] JAN MARINISSEN E, MCLAURIN T, and JIAO Hailong. IEEE Std P1838: DfT standard-under-development for 2.5D-, 3D-, and 5.5D-SICs[C]. 2016 21th IEEE European Test Symposium (ETS), Amsterdam, Netherlands, 2016: 1–10. [13] VIVET P, GUTHMULLER E, THONNART Y, et al. IntAct: A 96-core processor with six chiplets 3D-stacked on an active interposer with distributed interconnects and integrated power management[J]. IEEE Journal of Solid-State Circuits, 2021, 56(1): 79–97. doi: 10.1109/JSSC.2020.3036341 [14] 陈圣俭, 李广进, 高华. 基于外壳架构与测试访问机制的数字芯核可测试性设计[J]. 微电子学与计算机, 2012, 29(6): 42–45,50. doi: 10.19304/j.cnki.issn1000-7180.2012.06.010CHEN Shengjian, LI Guangjing, and GAO Hua. Design for testability of digital cores based on wrapper and TAM[J]. Microelectronics &Computer, 2012, 29(6): 42–45,50. doi: 10.19304/j.cnki.issn1000-7180.2012.06.010 [15] IEEE Computer Society. IEEE 1149.1-2013 IEEE standard for test access port and boundary-scan architecture[S]. New York: IEEE, 2013. -

下载:

下载:

下载:

下载: