Low-cost PUF Circuit Based on Sub-threshold Current Array

-

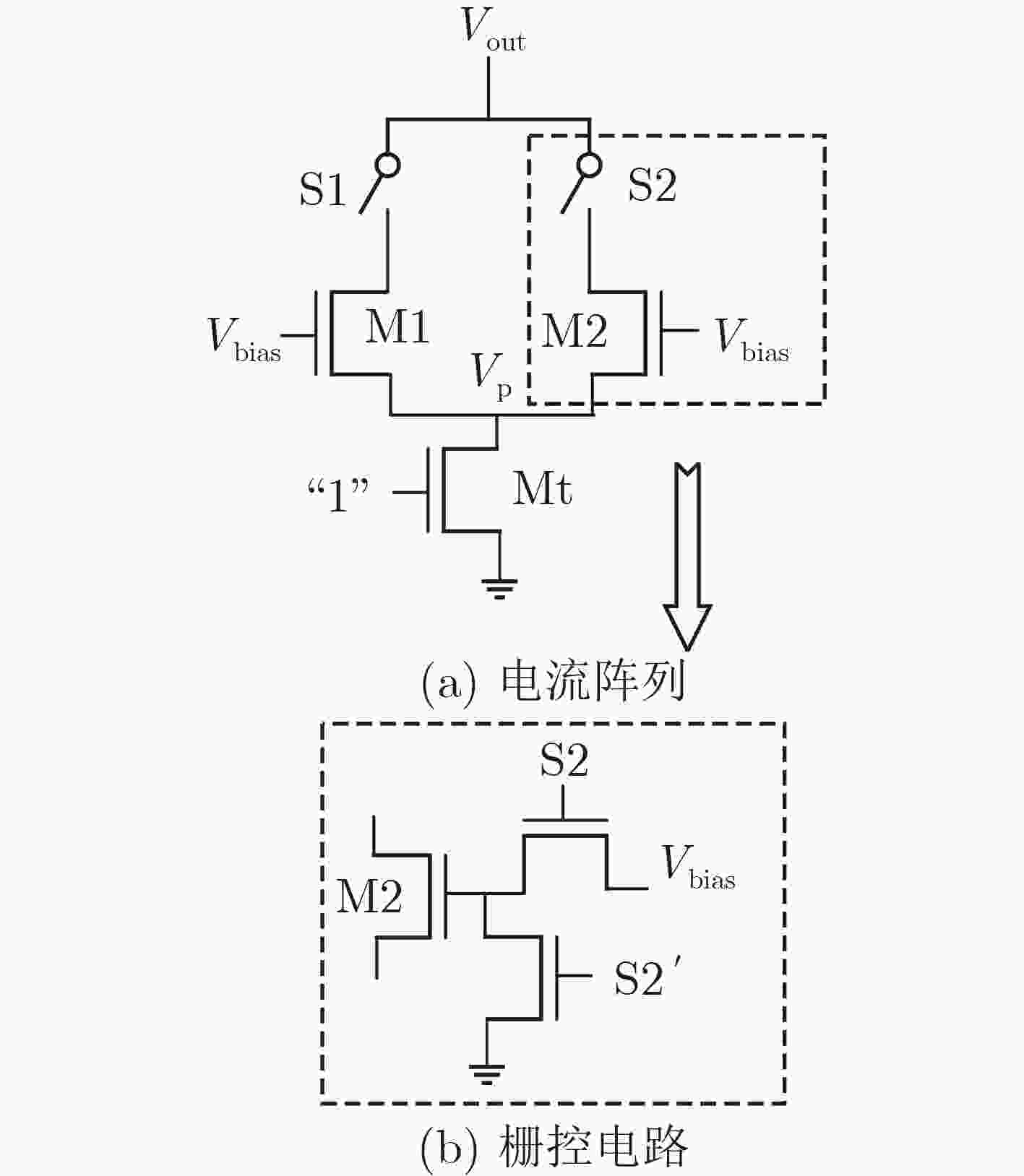

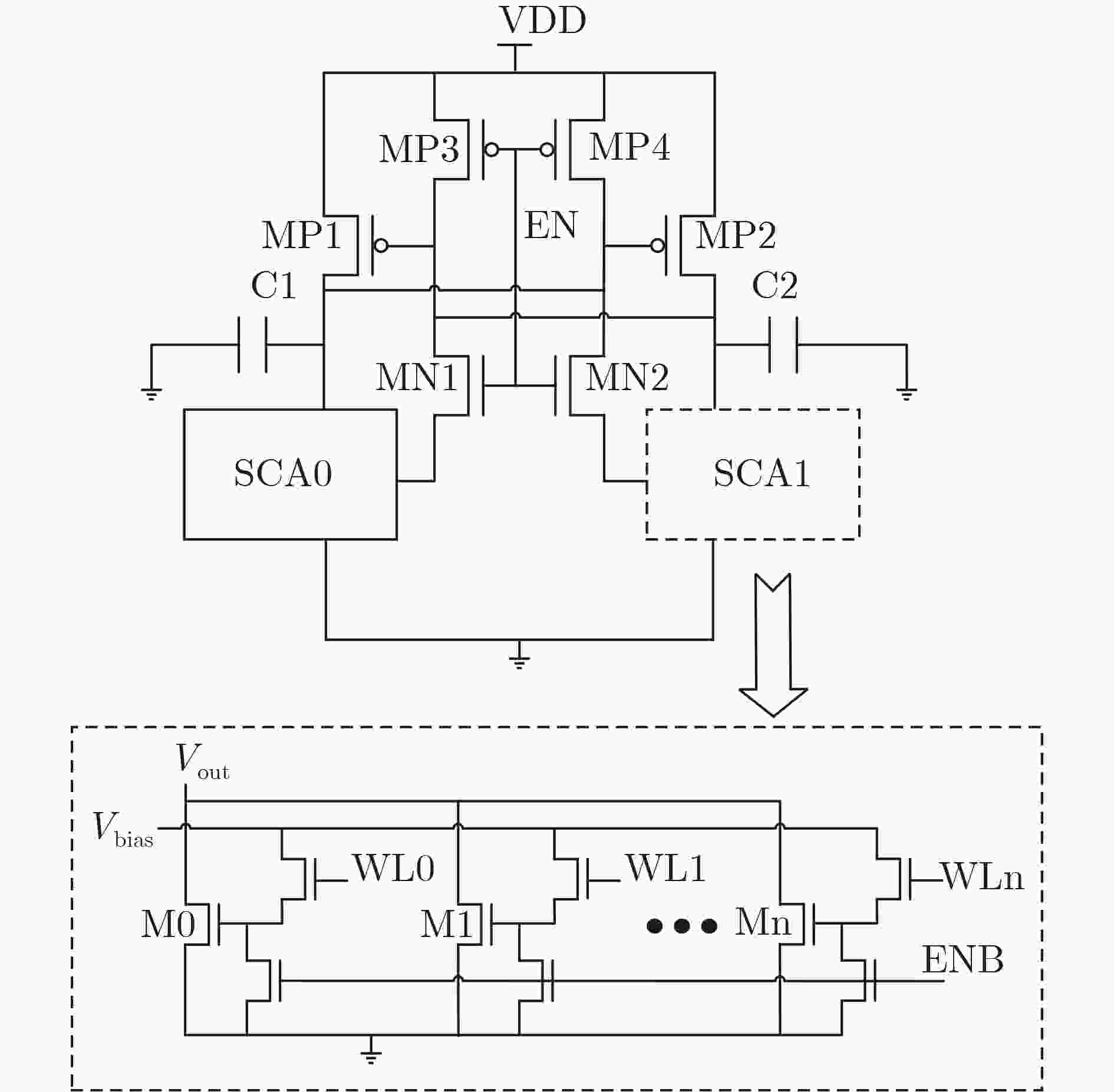

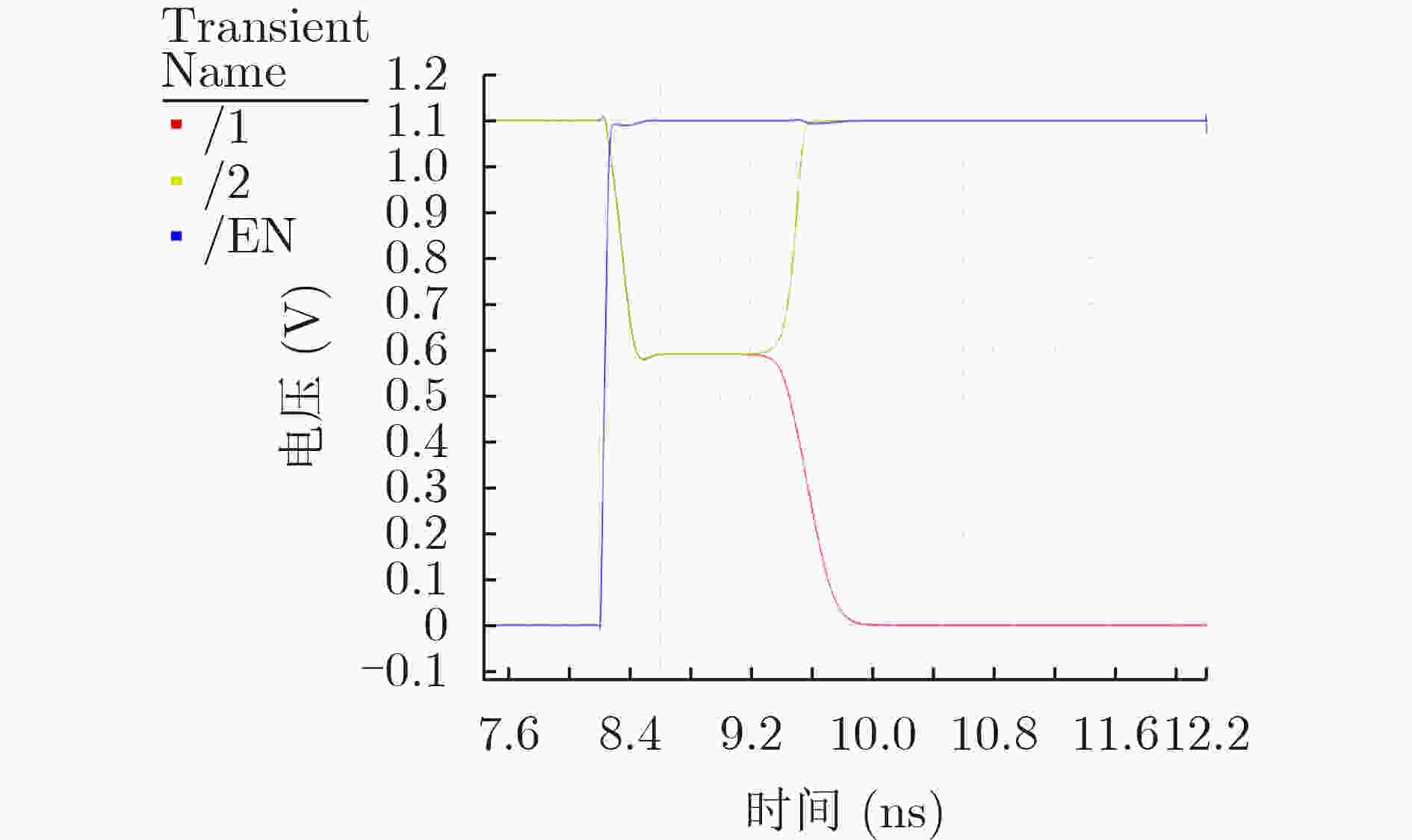

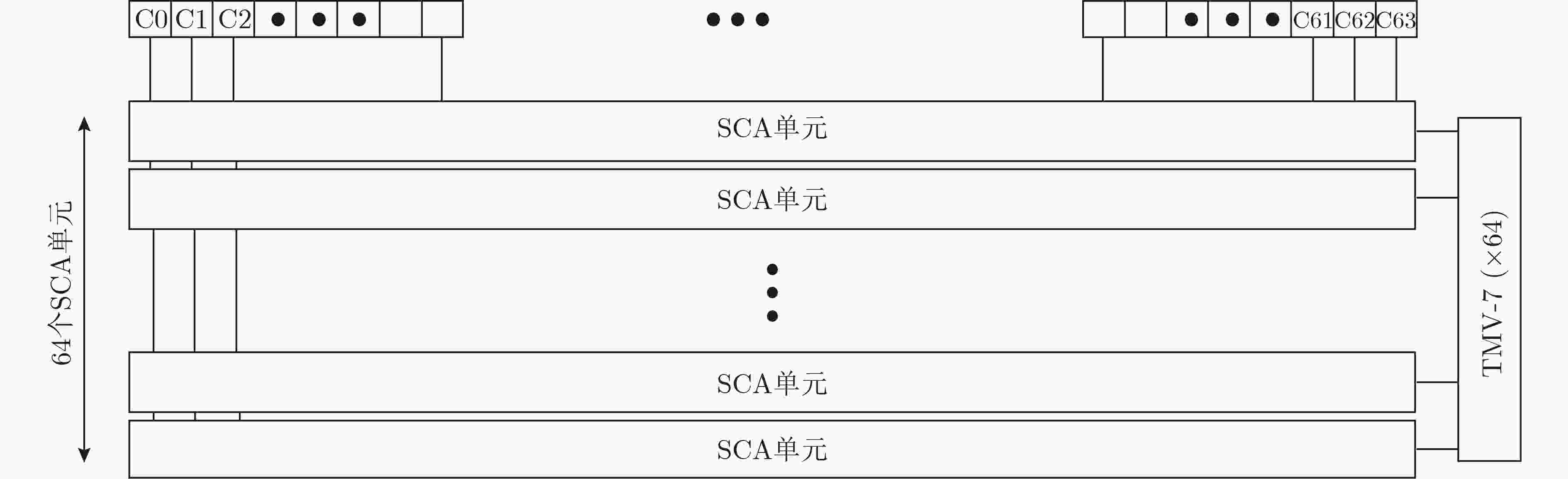

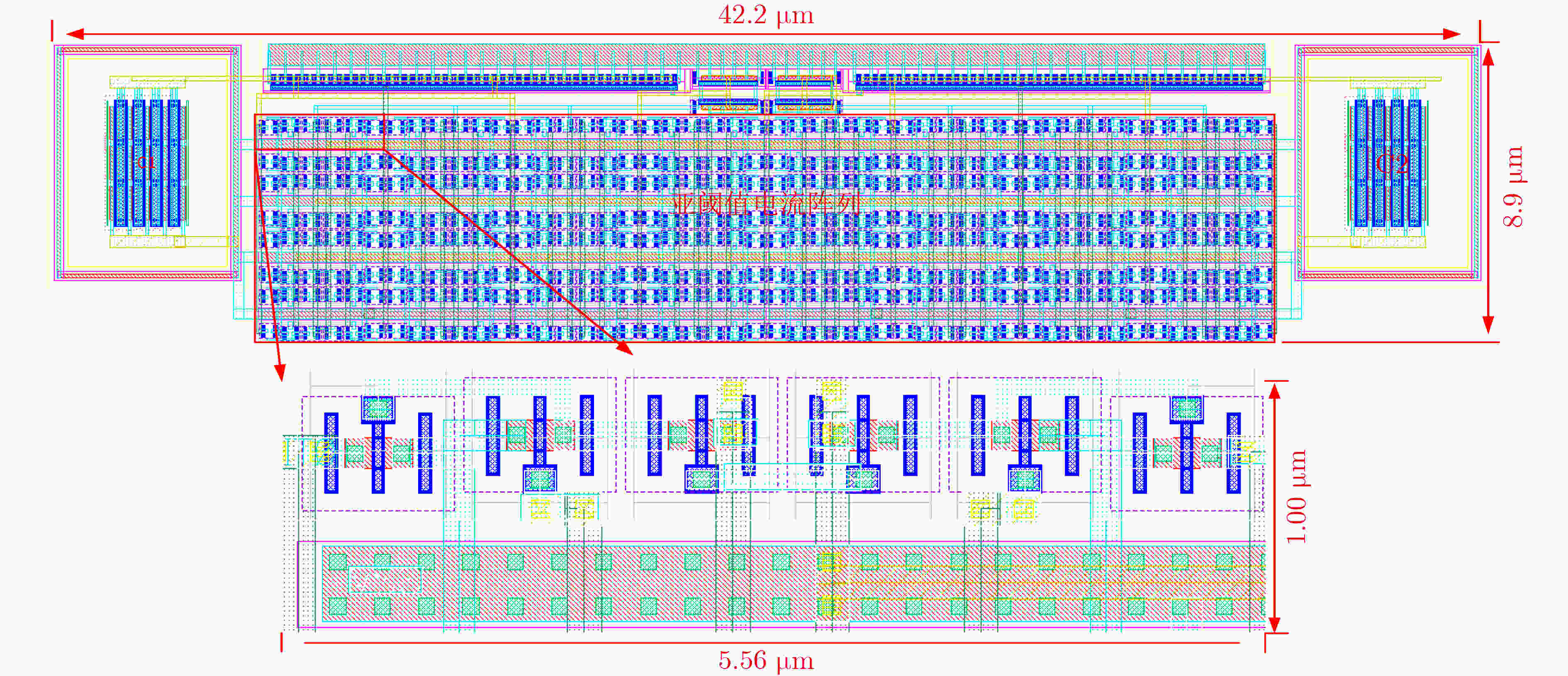

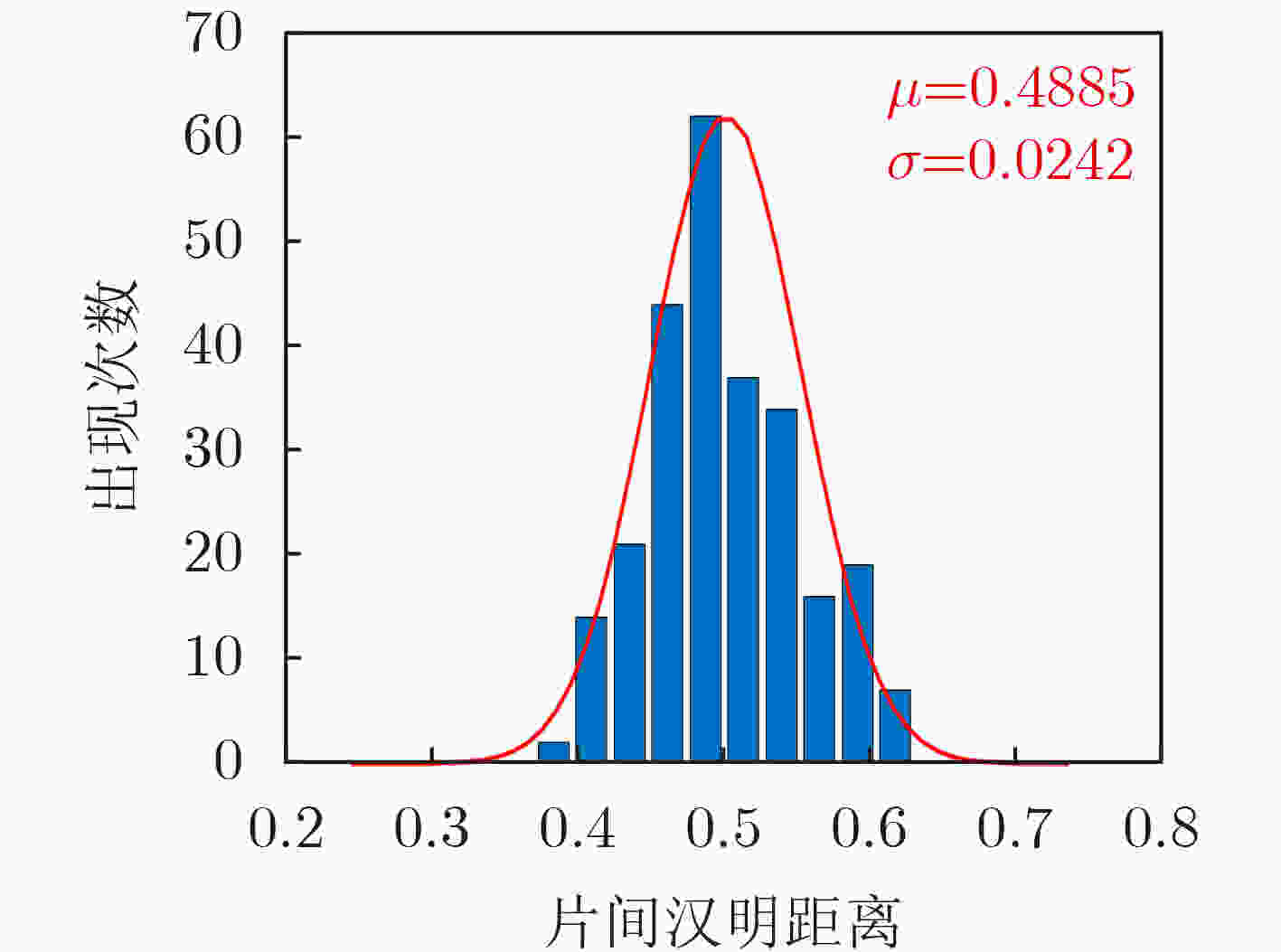

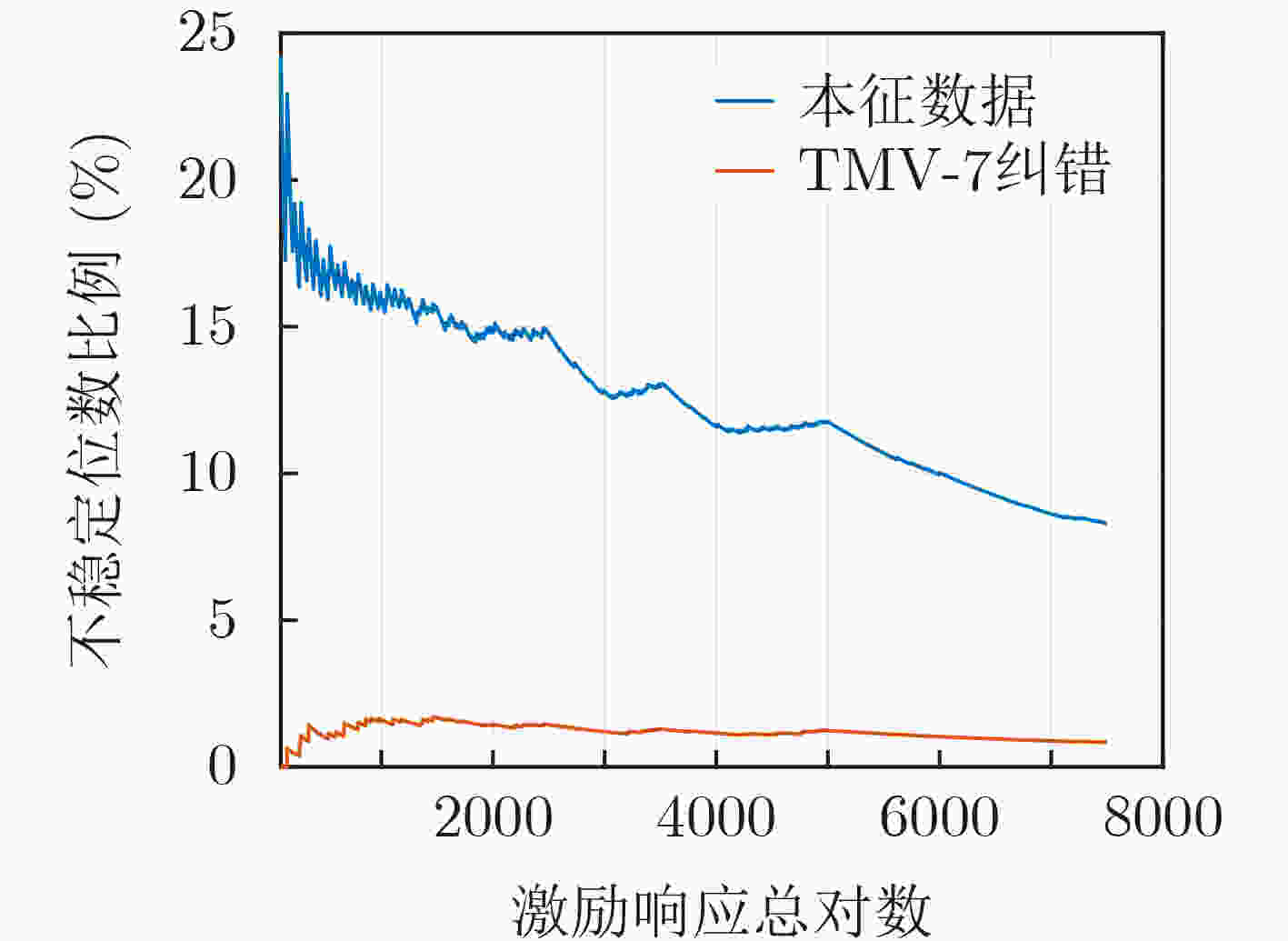

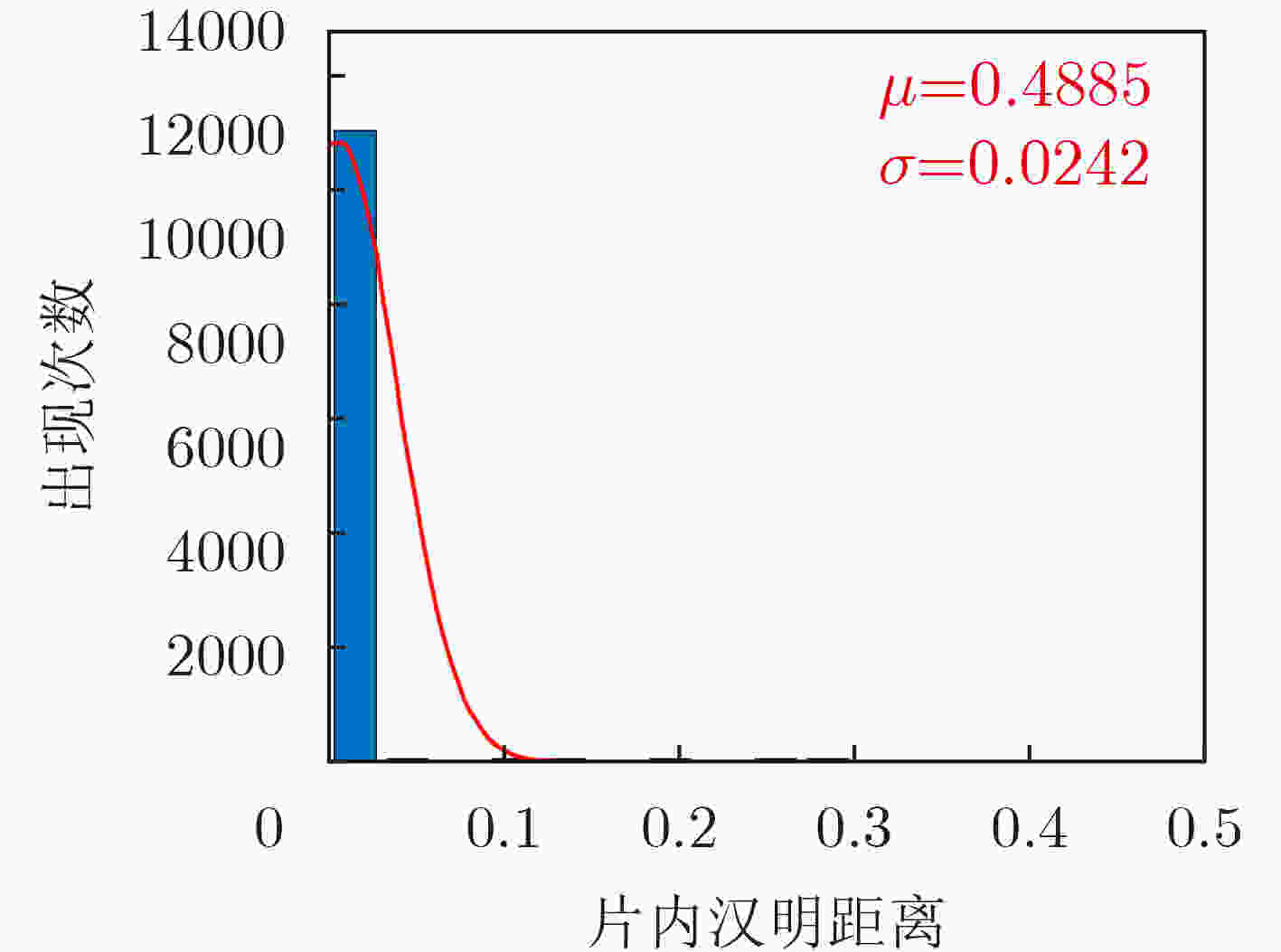

摘要: 物理不可克隆函数(PUF)能够提取出集成电路在加工过程中的工艺误差并将其转化为安全认证的密钥。由于常用于资源及功耗都受限的场合,实用化的PUF电路需要极高的硬件利用效率及较强的抗攻击性能。该文提出一种基于亚阈值电流阵列放电方案的低成本PUF电路设计方案。亚阈值电流阵列的电流具有极高的非线性特点,通过引入栅控开关和交叉耦合的结构,能够显著提升PUF电路的唯一性和稳定性。此外,通过引入亚阈值电流的设计可以极大地提高PUF的安全性,降低传统攻击手段的建模攻击。为了提升芯片的资源利用率,通过详细紧凑的版图设计和优化,该文提出的PUF单元面积仅为377.4 μm2,使得其特别适合物联网等低功耗低成本应用场景。仿真结果表明,该文所提亚阈值电路放电阵列PUF具有良好的唯一性和稳定性,无需校准电路的标准温度电压下唯一性为48.85%;在温度范围–20~80°C,电压变动范围为0.9~1.3V情况下,其可靠性达到了99.47%。Abstract: The Physical Unclonable Function (PUF) can extract the process error of the integrated circuit during the processing and convert it into a key for security authentication. It is often used in occasions where resources and power consumption are limited, practical PUF circuits require extremely high hardware utilization efficiency and resistant to machine learning attack. A low-cost PUF circuit design scheme based on the sub-threshold current array discharge scheme is proposed. The current of the sub-threshold current array has extremely high non-linear characteristics. By introducing a gate-controlled switch and a cross-coupling structure, the uniqueness and stability of the PUF circuit can be significantly improved. In addition, the design of introducing sub-threshold current can greatly improve the security of PUF and reduce the modeling attacks of traditional attack methods. In order to improve the resource utilization of the chip, the area of the proposed PUF cell is only 377.4 μm2 through a detailed and compact layout design and optimization, making it particularly suitable for low-power and low-cost applications such as IoT. The simulation results show that the PUF of the sub-threshold circuit discharge array proposed in this paper has good uniqueness and stability, and the uniqueness is 48.85% under the standard temperature and voltage without the need to calibrate the circuit. In the temperature range of –20°C to 80°C and the voltage variation range of 0.9 V to 1.3 V, its reliability reaches 99.47%.

-

表 1 设计中所用参数

MP1,

MP2MP3,

MP4MN1,

MN2C1,

C2尺寸/

规格12 μm/

100 nm1.2 μm/

40 nm1.2 μm/

40 nm40 pF 表 2 本文PUF电路与其他PUF结构的性能对比

序号 本文PUF TCAS'I[18] TCAS'I[20] TVLSI[21] 工艺制程(nm) 40 130 40 180 CRPs数量 1.8×1019 3.7×1019 1.8×1019 3.4×1038 PUF单元面积(μm2) 382 44700 4719 5175 动态功率(μW) 37 0.068 3.85 – 消耗能量/bit (pJ/bit) 0.29 11 7.7 – 唯一性 0.4885 0.499 0.4989 0.4995 输出响应速率(Mb/s) 89 0.006 0.5 – 本征不稳定位占比(评估CRPs数量) 8.9%(8000) 9%(500) 4.92%(1000) 8.1%(10000) 不稳定位占比(纠错方案后) 0.84%(TMV) 0.40%(掩蔽42%CRPs) 0.82%(掩蔽18.2%CRPs) 10–9(掩蔽80%CRPs) 温度范围(°C) –20~80 –20~80 –40~90 –40~125 电压范围(V) 0.9~1.3 1.08~1.32 0.9~1.3 1.5~2.1 -

[1] SUH G E and DEVADAS S. Physical unclonable functions for device authentication and secret key generation[C]. The 44th Annual Design Automation Conference, San Diego, USA, 2007: 9–14. [2] DELVAUX J, GU D W, SCHELLEKENS D, et al. Helper data algorithms for PUF-based key generation: Overview and analysis[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2015, 34(6): 889–902. doi: 10.1109/TCAD.2014.2370531 [3] 李刚, 汪鹏君, 张跃军, 等. 基于65 nm工艺的多端口可配置PUF电路设计[J]. 电子与信息学报, 2016, 38(6): 1541–1546. doi: 10.11999/JEIT150968LI Gang, WANG Pengjun, ZHANG Yuejun, et al. Design of multi-port configurable PUF circuit based on 65 nm technology[J]. Journal of Electronics &Information Technology, 2016, 38(6): 1541–1546. doi: 10.11999/JEIT150968 [4] 李森森, 黄一才, 郁滨, 等. 基于PUF的低开销物联网安全通信方案[J]. 电子学报, 2019, 47(4): 812–817. doi: 10.3969/j.issn.0372-2112.2019.04.007LI Sensen, HUANG Yicai, YU Bin, et al. A PUF-based low cost secure communication scheme for IoT[J]. Acta Electronica Sinica, 2019, 47(4): 812–817. doi: 10.3969/j.issn.0372-2112.2019.04.007 [5] LIANG Wei, XIE Songyou, ZHANG Dafang, et al. A mutual security authentication method for RFID-PUF circuit based on deep learning[J]. ACM Transactions on Internet Technology, 2022, 22(2): 34. doi: 10.1145/3426968 [6] 刘伟强, 崔益军, 王成华. 一种低成本物理不可克隆函数结构的设计实现及其RFID应用[J]. 电子学报, 2016, 44(7): 1772–1776. doi: 10.3969/j.issn.0372-2112.2016.07.036LIU Weiqiang, CUI Yijun, and WANG Chenghua. Design and implementation of a low-cost physical unclonable function and its application in RFID[J]. Acta Electronica Sinica, 2016, 44(7): 1772–1776. doi: 10.3969/j.issn.0372-2112.2016.07.036 [7] GU Chongyan, LIU Weiqiang, CUI Yijun, et al. A flip-flop based Arbiter Physical Unclonable Function (APUF) design with high entropy and uniqueness for FPGA implementation[J]. IEEE Transactions on Emerging Topics in Computing, 2021, 9(4): 1853–1866. doi: 10.1109/TETC.2019.2935465 [8] SAHOO D P, MUKHOPADHYAY D, CHAKRABORTY R S, et al. A multiplexer-based arbiter PUF composition with enhanced reliability and security[J]. IEEE Transactions on Computers, 2018, 67(3): 403–417. doi: 10.1109/TC.2017.2749226 [9] CUI Yijun, WANG Chenghua, LIU Weiqiang, et al. Low-cost configurable ring oscillator PUF with improved uniqueness[C]. 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, Canada, 2016: 558–561. [10] CAO Yuan, ZHANG Le, CHANG C H, et al. A low-power hybrid RO PUF with improved thermal stability for lightweight applications[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2015, 34(7): 1143–1147. doi: 10.1109/TCAD.2015.2424955 [11] RAHMAN M T, RAHMAN F, FORTE D, et al. An aging-resistant RO-PUF for reliable key generation[J]. IEEE Transactions on Emerging Topics in Computing, 2016, 4(3): 335–348. doi: 10.1109/TETC.2015.2474741 [12] GU Chongyan, MURPHY J, and O’NEILL M. A unique and robust single slice FPGA identification generator[C]. 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, Australia, 2014: 1223–1226. [13] SHIFMAN Y, MILLER A, KEREN O, et al. A method to improve reliability in a 65-nm SRAM PUF array[J]. IEEE Solid-State Circuits Letters, 2018, 1(6): 138–141. doi: 10.1109/LSSC.2018.2879216 [14] 张跃军, 汪鹏君, 李刚, 等. 基于信号传输理论的Glitch物理不可克隆函数电路设计[J]. 电子与信息学报, 2016, 38(9): 2391–2396. doi: 10.11999/JEIT151312ZHANG Yuejun, WANG Pengjun, LI Gang, et al. Design of Glitch physical unclonable functions circuit based on signal transmission theory[J]. Journal of Electronics &Information Technology, 2016, 38(9): 2391–2396. doi: 10.11999/JEIT151312 [15] ZHANG Jiliang and QU Gang. Physical unclonable function-based key sharing via machine learning for IoT security[J]. IEEE Transactions on Industrial Electronics, 2020, 67(8): 7025–7033. doi: 10.1109/TIE.2019.2938462 [16] 汪鹏君, 连佳娜, 陈博. 基于序列密码的强PUF抗机器学习攻击方法[J]. 电子与信息学报, 2021, 43(9): 2474–2481. doi: 10.11999/JEIT210726WANG Pengjun, LIAN Jia’na, and CHEN Bo. Sequence cipher based machine learning-attack resistance method for strong-PUF[J]. Journal of Electronics &Information Technology, 2021, 43(9): 2474–2481. doi: 10.11999/JEIT210726 [17] XI Xiaodan, ZHUANG Haoyu, SUN Nan, et al. Strong subthreshold current array PUF with 265 challenge-response pairs resilient to machine learning attacks in 130nm CMOS[C]. 2017 Symposium on VLSI Circuits, Kyoto, Japan, 2017: C268–C269. [18] ZHUANG Haoyu, XI Xiaodan, SUN Nan, et al. A strong subthreshold current array PUF resilient to machine learning attacks[J]. IEEE Transactions on Circuits and Systems I:Regular Papers, 2020, 67(1): 135–144. doi: 10.1109/TCSI.2019.2945247 [19] LIU Jiahao, ZHU Yan, CHAN Chihang, et al. A 0.04% BER strong PUF with cell-bias-based CRPs filtering and background offset calibration[J]. IEEE Transactions on Circuits and Systems I:Regular Papers, 2020, 67(11): 3853–3865. doi: 10.1109/TCSI.2020.3008683 [20] CAO Yuan, LIU Chaoqun, and CHANG C H. A low power diode-clamped inverter-based strong physical unclonable function for robust and lightweight authentication[J]. IEEE Transactions on Circuits and Systems I:Regular Papers, 2018, 65(11): 3864–3873. doi: 10.1109/TCSI.2018.2855061 [21] HE Zhangqing, WAN Meilin, DENG Jie, et al. A reliable strong PUF based on switched-capacitor circuit[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018, 26(6): 1073–1083. doi: 10.1109/TVLSI.2018.2806041 -

下载:

下载:

下载:

下载: