| [1] |

CHUA L. Memristor-the missing circuit element[J]. IEEE Transactions on Circuit Theory, 1971, 18(5): 507–519. doi: 10.1109/TCT.1971.1083337

|

| [2] |

LI Can, GRAVES C E, SHENG Xia, et al. Analog content-addressable memories with memristors[J]. Nature Communications, 2020, 11(1): 1638. doi: 0.1038/s41467-020-15254-4

|

| [3] |

CAO Qiang, LÜ Weiming, WANG Renshaw, et al. Nonvolatile multistates memories for high-density data storage[J]. ACS Applied Materials & Interfaces, 2020, 12(38): 42449–42471. doi: 10.1021/acsami.0c10184

|

| [4] |

ALI K A, RIZK M, BAGHDADI A, et al. Crossbar memory architecture performing memristor overwrite logic[C]. 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genoa, Italy, 2019: 723–726. doi: 10.1109/ICECS46596.2019.8964910.

|

| [5] |

LUO Li, DONG Zhekang, DUAN Shukai, et al. Memristor-based stateful logic gates for multi-functional logic circuit[J]. IET Circuits, Devices & Systems, 2020, 14(6): 811–818. doi: 10.1049/iet-cds.2019.0422

|

| [6] |

ASCOLI A, SLESAZECK S, MÄHNE H, et al. Nonlinear dynamics of a locally-active memristor[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2015, 62(4): 1165–1174. doi: 10.1109/TCSI.2015.2413152

|

| [7] |

CORINTO F and FORTI M. Nonlinear dynamics of memristor oscillators via the flux-charge analysis method[C]. 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, USA, 2017. doi: 10.1109/ISCAS.2017.8050989.

|

| [8] |

WU Renping and WANG Chunhua. A new simple chaotic circuit based on memristor[J]. International Journal of Bifurcation and Chaos, 2016, 26(9): 1650145. doi: 10.1142/S0218127416501455

|

| [9] |

WANG Chunhua, XIA Hu, and ZHOU Ling. A memristive hyperchaotic multiscroll jerk system with controllable scroll numbers[J]. International Journal of Bifurcation and Chaos, 2017, 27(6): 1750091. doi: 10.1142/s0218127417500912

|

| [10] |

ZHU Minghao, WANG Chunhua, DENG Quanli, et al. Locally active memristor with three coexisting pinched hysteresis loops and its emulator circuit[J]. International Journal of Bifurcation and Chaos, 2020, 30(13): 2050184. doi: 10.1142/S0218127420501849

|

| [11] |

ZHOU Chao, WANG Chunhua, SUN Yichuang, et al. Weighted sum synchronization of memristive coupled neural networks[J]. Neurocomputing, 2020, 403: 211–233. doi: 10.1016/j.neucom.2020.04.087

|

| [12] |

YAO Wei, WANG Chunhua, SUN Yichuang, et al. Exponential multistability of memristive Cohen-Grossberg neural networks with stochastic parameter perturbations[J]. Applied Mathematics and Computation, 2020, 386: 125483. doi: 10.1016/j.amc.2020.125483

|

| [13] |

LIN Hairong, WANG Chunhua, HONG Qinghui, et al. A multi-stable memristor and its application in a neural network[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2020, 67(12): 3472–3476. doi: 10.1109/TCSII.2020.3000492

|

| [14] |

LIN Hairong, WANG Chunhua, SUN Yichuang, et al. Firing multistability in a locally active memristive neuron model[J]. Nonlinear Dynamics, 2020, 100(4): 3667–3683. doi: 10.1007/s11071-020-05687-3

|

| [15] |

LIN Hairong, WANG Chunhua, and TAN Yumei. Hidden extreme multistability with hyperchaos and transient chaos in a Hopfield neural network affected by electromagnetic radiation[J]. Nonlinear Dynamics, 2020, 99(4): 2369–2386. doi: 10.1007/s11071-019-05408-5

|

| [16] |

IELMINI D and WONG H S P. In-memory computing with resistive switching devices[J]. Nature Electronics, 2018, 1(6): 333–343. doi: 10.1038/s41928-018-0092-2

|

| [17] |

CHI Ping, LI Shuangchen, XU Cong, et al. PRIME: A novel processing-in-memory architecture for neural network computation in ReRAM-based main memory[C]. 2016 ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA), Seoul, Korea, 2016: 27–39. doi: 10.1109/ISCA.2016.13.

|

| [18] |

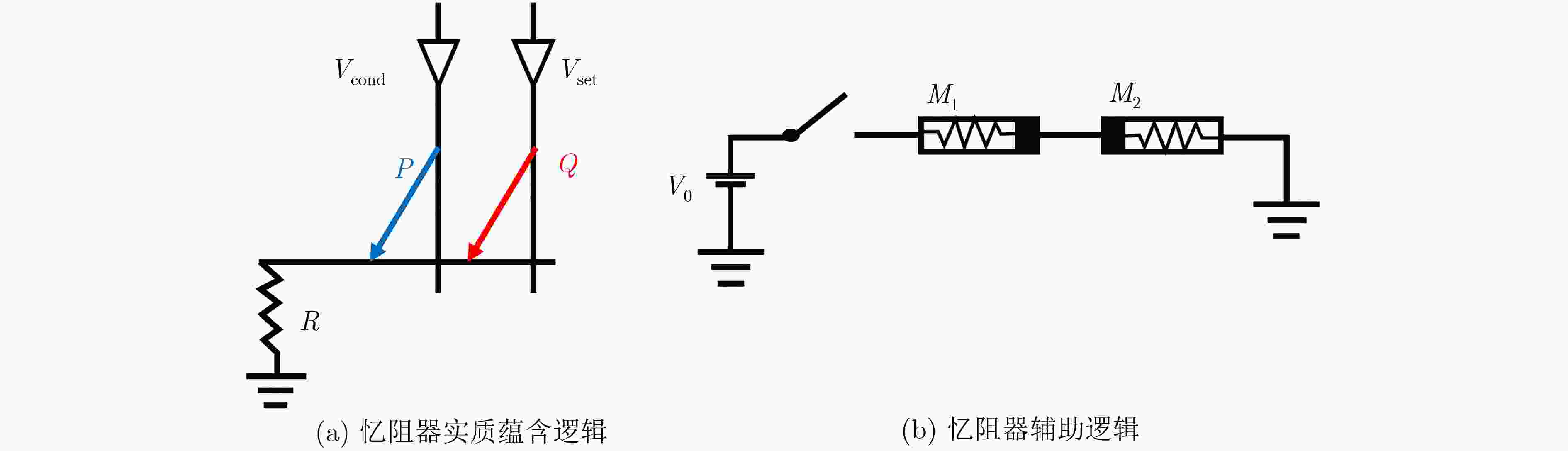

BORGHETTI J, SNIDER G S, KUEKES P J, et al. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication[J]. Nature, 2010, 464(7290): 873–876. doi: 10.1038/nature08940

|

| [19] |

KVATINSKY S, BELOUSOV D, LIMAN S, et al. MAGIC—memristor-aided logic[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2014, 61(11): 895–899. doi: 10.1109/TCSII.2014.2357292

|

| [20] |

ALAMGIR Z, BECKMANN K, CADY N, et al. Flow-based computing on nanoscale crossbars: Design and implementation of full adders[C]. 2016 IEEE International Symposium on Circuits and Systems, Montreal, Canada, 2016: 1870–1873.

|

| [21] |

TALATI N, GUPTA S, MANE P, et al. Logic design within memristive memories using memristor-aided loGIC (MAGIC)[J]. IEEE Transactions on Nanotechnology, 2016, 15(4): 635–650. doi: 10.1109/TNANO.2016.2570248

|

| [22] |

LI H, GAO B, CHEN Z, et al. A learnable parallel processing architecture towards unity of memory and computing[J]. Scientific Reports, 2015, 5: 13330. doi: 10.1038/srep13330

|

| [23] |

CHENG Long, ZHANG Meiyun, LI Yi, et al. Reprogrammable logic in memristive crossbar for in-memory computing[J]. Journal of Physics D: Applied Physics, 2017, 50(50): 505102. doi: 10.1088/1361-6463/aa9646

|

| [24] |

KARIMI A and REZAI A. High-performance digital logic implementation approach using novel Memristor-based multiplexer[J]. International Journal of Circuit Theory and Applications, 2019, 47(12): 1933–1947. doi: 10.1002/cta.2712

|

| [25] |

BEN-HUR R, RONEN R, HAJ-ALI A, et al. SIMPLER MAGIC: Synthesis and mapping of in-memory logic executed in a single row to improve throughput[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2020, 39(10): 2434–2447. doi: 10.1109/TCAD.2019.2931188

|

| [26] |

LIU Xiaoxiao, MAO Mengjie, LIU Beiye, et al. Harmonica: A framework of heterogeneous computing systems with memristor-based neuromorphic computing accelerators[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2016, 63(5): 617–628. doi: 10.1109/TCSI.2016.2529279

|

| [27] |

HALAWANI Y, MOHAMMAD B, Al-QUTAYRI M, et al. A re-configurable memristor array structure for in-memory computing applications[C]. 2018 30th International Conference on Microelectronics (ICM), Sousse, Tunisia, 2018: 160–163. doi: 10.1109/ICM.2018.8704111.

|

| [28] |

ZHANG Xunming, ZHANG Quan, YANG Jianguo, et al. Novel hybrid computing architecture with memristor-based processing-in-memory for data-intensive applications[C]. 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Qingdao, China, 2018: 1–3. doi: 10.1109/ICSICT.2018.8564888.

|

| [29] |

ALAM M R, NAJAFI M H, and NEJAD N T. Exact stochastic computing multiplication in memristive memory[J]. IEEE Design & Test, To be published. doi: 10.1109/MDAT.2021.3051296

|

| [30] |

KOLMS T, LANG C, WALDNER A, et al. Towards in-memory computing: Arithmetic operations on real memristors[C]. The IECON 2020 the 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 2020: 2296–2301. doi: 10.1109/IECON43393.2020.9254441.

|

| [31] |

ZANOTTI T, PUGLISI F M, and PAVAN P. Reconfigurable smart in-memory computing platform supporting logic and binarized neural networks for low-power edge devices[J]. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2020, 10(4): 478–487. doi: 10.1109/JETCAS.2020.3030542

|

| [32] |

CHENG Long, LI Yi, YIN Kangsheng, et al. Functional demonstration of a memristive arithmetic logic unit (MemALU) for in-memory computing[J]. Advanced Functional Materials, 2019, 29(49): 1905660. doi: 10.1002/adfm.201905660

|

| [33] |

DAI Lan, GUO Hong, LIN Qipeng, et al. An in-memory-computing design of multiplier based on multilevel-cell of resistance switching random access memory[J]. Chinese Journal of Electronics, 2018, 27(6): 1151–1157. doi: 10.1049/cje.2018.08.006

|

| [34] |

ZHOU Yaxiong, LI Yi, DUAN Nian, et al. Boolean and sequential logic in a one-memristor-one-resistor (1M1R) structure for in-memory computing[J]. Advanced Electronic Materials, 2018, 4(9): 1800229. doi: 10.1002/aelm.201800229

|

| [35] |

HALAWANI Y, MOHAMMAD B, LEBDEH M A, et al. ReRAM-based in-memory computing for search engine and neural network applications[J]. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2019, 9(2): 388–397. doi: 10.1109/JETCAS.2019.2909317

|

| [36] |

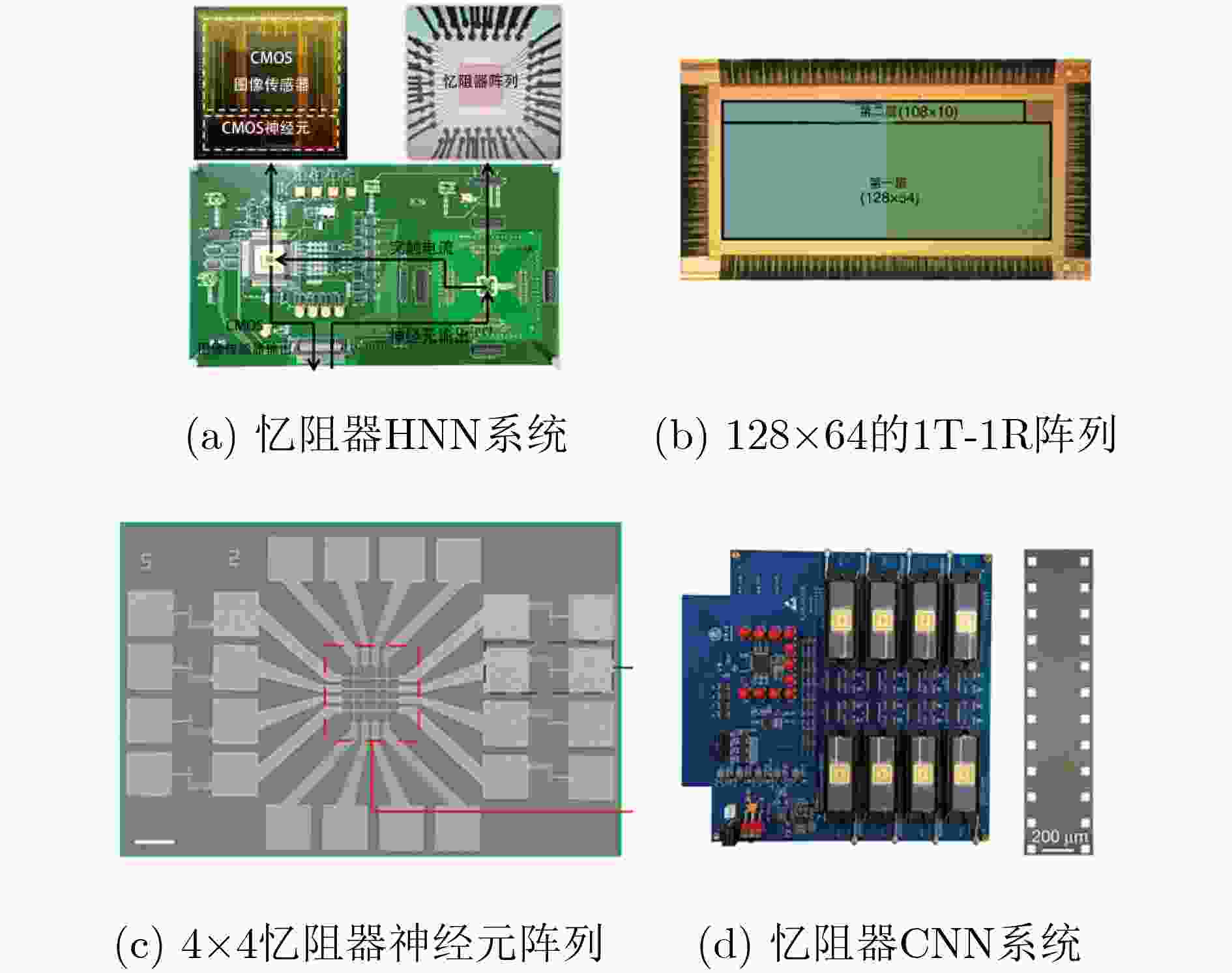

CHU M, KIM B, PARK S, et al. Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron[J]. IEEE Transactions on Industrial Electronics, 2015, 62(4): 2410–2419. doi: 10.1109/TIE.2014.2356439

|

| [37] |

LI Can, BELKIN D, LI Yunning, et al. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks[J]. Nature Communications, 2018, 9(1): 2385. doi: 10.1038/s41467-018-04484-2

|

| [38] |

DUAN Qingxi, JING Zhaokun, ZOU Xiaolong, et al. Spiking neurons with spatiotemporal dynamics and gain modulation for monolithically integrated memristive neural networks[J]. Nature Communications, 2020, 11(1): 3399. doi: 10.1038/s41467-020-17215-3

|

| [39] |

YAO Peng, WU Huaqiang, GAO Bin, et al. Fully hardware-implemented memristor convolutional neural network[J]. Nature, 2020, 577(7792): 641–646. doi: 10.1038/s41586-020-1942-4

|

| [40] |

BALAJI A, DAS A, WU Yuefeng, et al. Mapping spiking neural networks to neuromorphic hardware[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2020, 28(1): 76–86. doi: 10.1109/TVLSI.2019.2951493

|

| [41] |

TAN Hongwei, MAJUMDAR S, QIN Qihang, et al. Mimicking neurotransmitter release and long-term plasticity by oxygen vacancy migration in a tunnel junction memristor[J]. Advanced Intelligent Systems, 2019, 1(2): 1900036. doi: 10.1002/aisy.201900036

|

| [42] |

WIJESINGHE P, ANKIT A, SENGUPTA A, et al. An all-memristor deep spiking neural computing system: A step toward realizing the low-power stochastic brain[J]. IEEE Transactions on Emerging Topics in Computational Intelligence, 2018, 2(5): 345–358. doi: 10.1109/TETCI.2018.2829924

|

| [43] |

ZHANG Yang, WANG Xiaoping, and FRIEDMAN E G. Memristor-based circuit design for multilayer neural networks[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2018, 65(2): 677–686. doi: 10.1109/TCSI.2017.2729787

|

| [44] |

ZHAO Yongyan, SUN Wuji, WANG Jia, et al. All‐inorganic ionic polymer-based memristor for high-performance and flexible artificial synapse[J]. Advanced Functional Materials, 2020, 30(39): 2004245. doi: 10.1002/adfm.202004245

|

| [45] |

GREENBERG-TOLEDO T, MAZOR R, HAJ-ALI A, et al. Supporting the momentum training algorithm using a memristor-based synapse[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2019, 66(4): 1571–1583. doi: 10.1109/TCSI.2018.2888538

|

| [46] |

SUN Shengyang, XU Hui, LI Jiwei, et al. Cascaded architecture for memristor crossbar array based larger-scale neuromorphic computing[J]. IEEE Access, 2019, 7: 61679–61688. doi: 10.1109/ACCESS.2019.2915787

|

| [47] |

HU Lingxiang, YANG Jing, WANG Jingrui, et al. All‐optically controlled memristor for optoelectronic neuromorphic computing[J]. Advanced Functional Materials, 2021, 31(4): 2005582. doi: 10.1002/adfm.202005582

|

| [48] |

LI Haoyang, HUANG Xiaodi, YUAN Junhui, et al. Controlled memory and threshold switching behaviors in a heterogeneous memristor for neuromorphic computing[J]. Advanced Electronic Materials, 2020, 6(8): 2000309. doi: 10.1002/aelm.202000309

|

| [49] |

BAE W and YOON K J. Weight update generation circuit utilizing phase noise of integrated complementary metal-oxide-semiconductor ring oscillator for memristor crossbar array neural network-based stochastic learning[J]. Advanced Intelligent Systems, 2020, 2(5): 2000011. doi: 10.1002/aisy.202000011

|

| [50] |

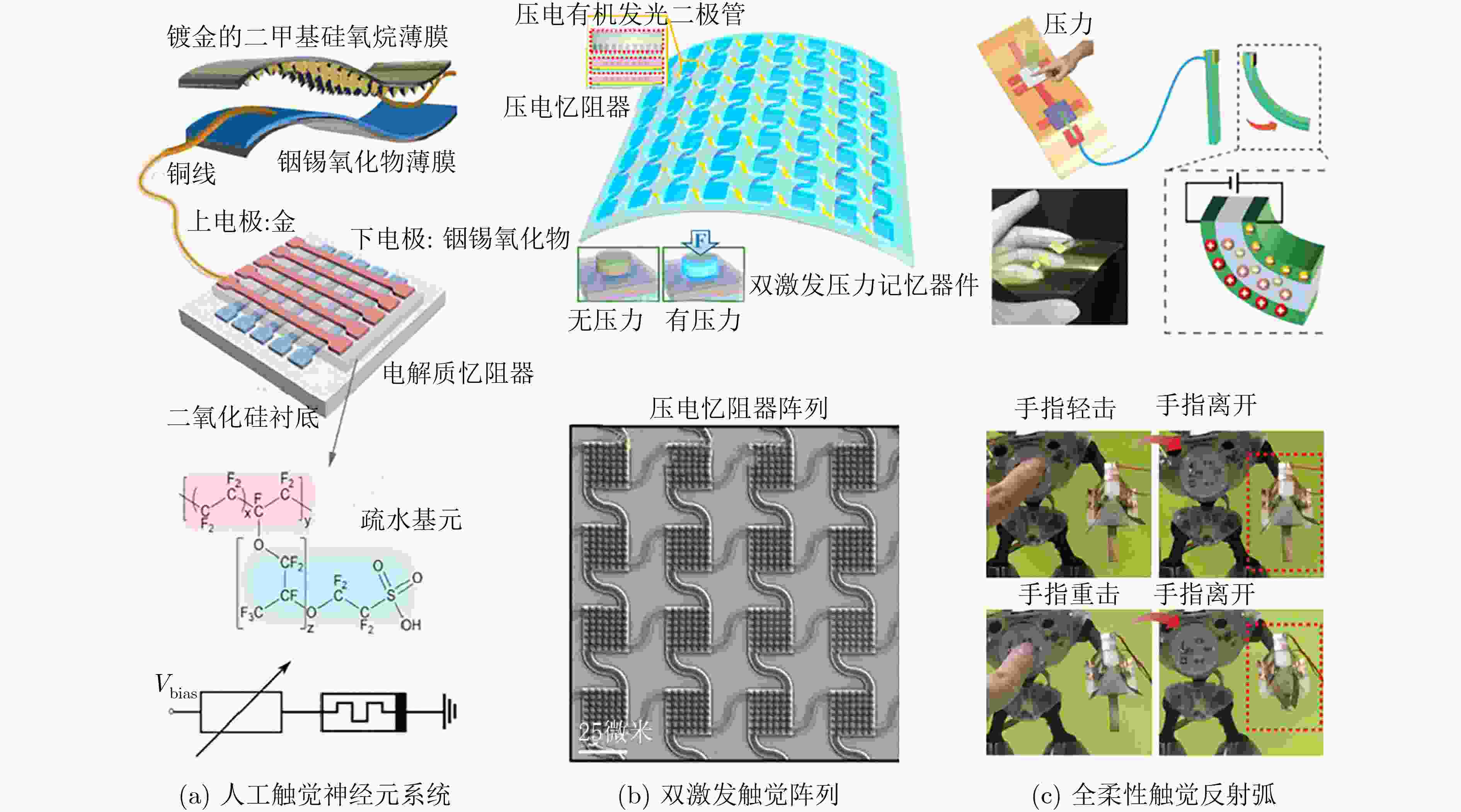

ZHU Bowen, WANG Hong, LIU Yaqing, et al. Skin-inspired haptic memory arrays with an electrically reconfigurable architecture[J]. Advanced Materials, 2016, 28(8): 1559–1566. doi: 10.1002/adma.201504754

|

| [51] |

ZHANG Chen, YE Wenbin, ZHOU Kui, et al. Bioinspired artificial sensory nerve based on nafion memristor[J]. Advanced Functional Materials, 2019, 29(20): 1808783. doi: 10.1002/adfm.201808783

|

| [52] |

JIANG Chengming, LI Qikun, SUN Nan, et al. A high-performance bionic pressure memory device based on piezo-OLED and piezo-memristor as luminescence-fish neuromorphic tactile system[J]. Nano Energy, 2020, 77: 105120. doi: 10.1016/j.nanoen.2020.105120

|

| [53] |

HE Ke, LIU Yaqing, WANG Ming, et al. An artificial somatic reflex arc[J]. Advanced Materials, 2020, 32(4): 1905399. doi: 10.1002/adma.201905399

|

| [54] |

LIU Fengyuan, TAUBE W, YOGESWARAN N, et al. Transforming the short-term sensing stimuli to long-term e-skin memory[C]. 2017 IEEE SENSORS, Glasgow, UK, 2017: 1–3. doi: 10.1109/ICSENS.2017.8234187.

|

| [55] |

SUN Yihui, ZHENG Xin, YAN Xiaoqin, et al. Bioinspired tribotronic resistive switching memory for self-powered memorizing mechanical stimuli[J]. ACS Applied Materials & Interfaces, 2017, 9(50): 43822–43829. doi: 10.1021/acsami.7b15269

|

| [56] |

WANG Zilu, HONG Qinghui, and WANG Xiaoping. Memristive circuit design of emotional generation and evolution based on skin-like sensory processor[J]. IEEE Transactions on Biomedical Circuits and Systems, 2019, 13(4): 631–644. doi: 10.1109/TBCAS.2019.2923055

|

| [57] |

WAN Changjin, CAI Pingqiang, GUO Xintong, et al. An artificial sensory neuron with visual-haptic fusion[J]. Nature Communications, 2020, 11: 4602. doi: 10.1038/s41467-020-18375-y

|

| [58] |

RAHMAN M A, WALIA S, NAZNEE S, et al. Artificial somatosensors: Feedback receptors for electronic skins[J]. Advanced Intelligent Systems, 2020, 2(11): 2000094. doi: 10.1002/aisy.202000094

|

| [59] |

LIU Haitao, HUA Qilin, YU Ruomeng, et al. A bamboo-like GaN microwire-based piezotronic memristor[J]. Advanced Functional Materials, 2016, 26(29): 5307–5314. doi: 10.1002/adfm.201600962

|

| [60] |

KIM Y, CHORTOS A, XU Wentao, et al. A bioinspired flexible organic artificial afferent nerve[J]. Science, 2018, 360(6392): 998–1003. doi: 10.1126/science.aao0098

|

| [61] |

EMBORAS A, GOYKHMAN I, DESIATOV B, et al. Nanoscale plasmonic memristor with optical readout functionality[J]. Nano Letters, 2013, 13(12): 6151–6155. doi: 10.1021/nl403486x

|

| [62] |

TAN Hongwei, LIU Gang, ZHU Xiaojian, et al. An optoelectronic resistive switching memory with integrated demodulating and arithmetic functions[J]. Advanced Materials, 2015, 27(17): 2797–2803. doi: 10.1002/adma.201500039

|

| [63] |

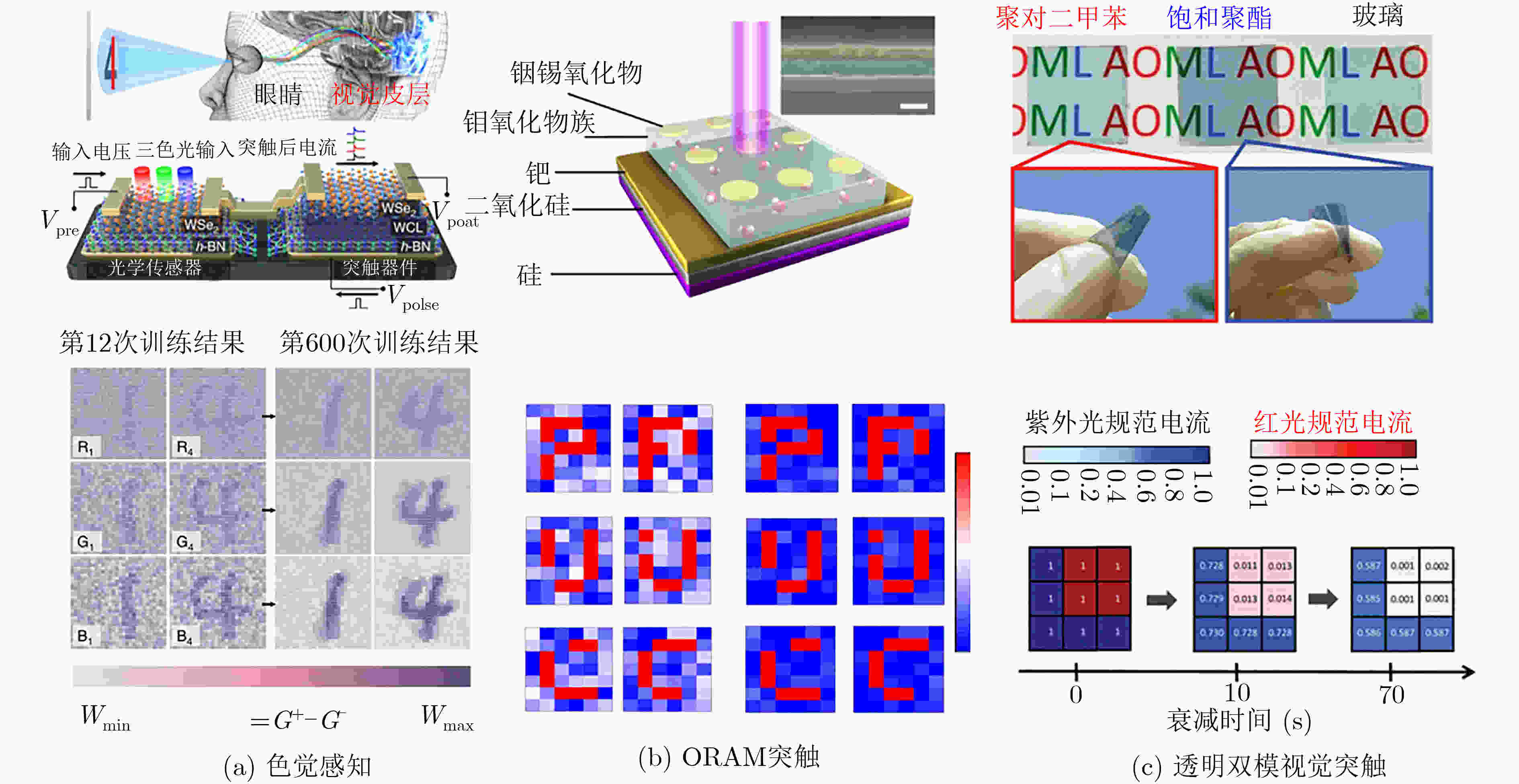

SEO S, JO S H, KIM S, et al. Artificial optic-neural synapse for colored and color-mixed pattern recognition[J]. Nature Communications, 2018, 9(1): 5106. doi: 10.1038/s41467-018-07572-5

|

| [64] |

ZHOU Feichi, ZHOU Zheng, CHEN Jiewei, et al. Optoelectronic resistive random access memory for neuromorphic vision sensors[J]. Nature Nanotechnology, 2019, 14(8): 776–782. doi: 10.1038/s41565-019-0501-3

|

| [65] |

YANG Lin, SINGH M, SHEN S W, et al. Transparent and flexible inorganic perovskite photonic artificial synapses with dual-mode operation[J]. Advanced Functional Materials, 2020, 31(6): 2008259. doi: 10.1002/adfm.202008259

|

| [66] |

LORENZI P, SUCRE V, ROMANO G, et al. Memristor based neuromorphic circuit for visual pattern recognition[C]. 2015 International Conference on Memristive Systems (MEMRISYS), Paphos, Cyprus, 2015: 1–2. doi: 10.1109/MEMRISYS.2015.7378387.

|

| [67] |

SARKAR M, CHOWDHURY A, ARKA A I, et al. A new supervised learning approach for visual pattern recognition using discrete circuit elements and memristor array[C]. The TENCON 2017 – 2017 IEEE Region 10 Conference, Penang, Malaysia, 2017: 223–228. doi: 10.1109/TENCON.2017.8227866.

|

| [68] |

ASCOLI A, MESSARIS I, TETZLAFF R, et al. CNNs with bistable-like non-volatile memristors: A novel mem-computing paradigm for the IoT era[C]. 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 2018: 541–544. doi: 10.1109/ICECS.2018.8617924.

|

| [69] |

DONG Zhekang, LAI C S, HE Yufei, et al. Hybrid dual-CMOS/memristor synapse-based neural network with its applications in image super-resolution[J]. IET Circuits, Devices & Systems, 2019, 13(8): 1241–1248. doi: 10.1049/iet-cds.2018.5062

|

| [70] |

HALAWANI Y, MOHAMMAD B, AL-QUTAYRI M, et al. Memristor-based hardware accelerator for image compression[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018, 26(12): 2749–2758. doi: 10.1109/TVLSI.2018.2835572

|

| [71] |

WU Lindong, WANG Zongwei, WANG Bowen, et al. Emulation of biphasic plasticity in retinal electrical synapses for light-adaptive pattern pre-processing[J]. Nanoscale, 2021, 13(6): 3483–3492. doi: 10.1039/d0nr08012h

|

| [72] |

LIN Ya, WANG Cong, REN Yanyun, et al. Analog-digital hybrid memristive devices for image pattern recognition with tunable learning accuracy and speed[J]. Small Methods, 2019, 3(10): 1900160. doi: 10.1002/smtd.201900160

|

| [73] |

SUN Yilin, QIAN Liu, XIE Dan, et al. Photoelectric synaptic plasticity realized by 2D perovskite[J]. Advanced Functional Materials, 2019, 29(28): 1902538. doi: 10.1002/adfm.201902538

|

| [74] |

YANG C M, CHEN T C, VERMA D, et al. Bidirectional all-optical synapses based on a 2D Bi2O2Se/graphene hybrid structure for multifunctional optoelectronics[J]. Advanced Functional Materials, 2020, 30(30): 2001598. doi: 10.1002/adfm.202001598

|

| [75] |

WANG Xin, LU Yang, ZHANG Junyao, et al. Highly sensitive artificial visual array using transistors based on porphyrins and semiconductors[J]. Small, 2021, 17(2): 2005491. doi: 10.1002/smll.202005491

|

| [76] |

HSU H T, YANG Donglin, WIYANTO L D, et al. Red-light-stimulated photonic synapses based on non-volatile perovskite-based photomemory[J]. Advanced Photonics Research, 2021: 2000185. doi: 10.1002/adpr.202000185

|

| [77] |

ZHANG Lei, YU Hao, XIAO Cancheng, et al. Building light stimulated synaptic memory devices for visual memory simulation[J]. Advanced Electronic Materials, 2021, 7(1): 2000945. doi: 10.1002/aelm.202000945

|

| [78] |

DONG Zhekang, LAI C S, QI Donglian, et al. A general memristor-based pulse coupled neural network with variable linking coefficient for multi-focus image fusion[J]. Neurocomputing, 2018, 308: 172–183. doi: 10.1016/j.neucom.2018.04.066

|

| [79] |

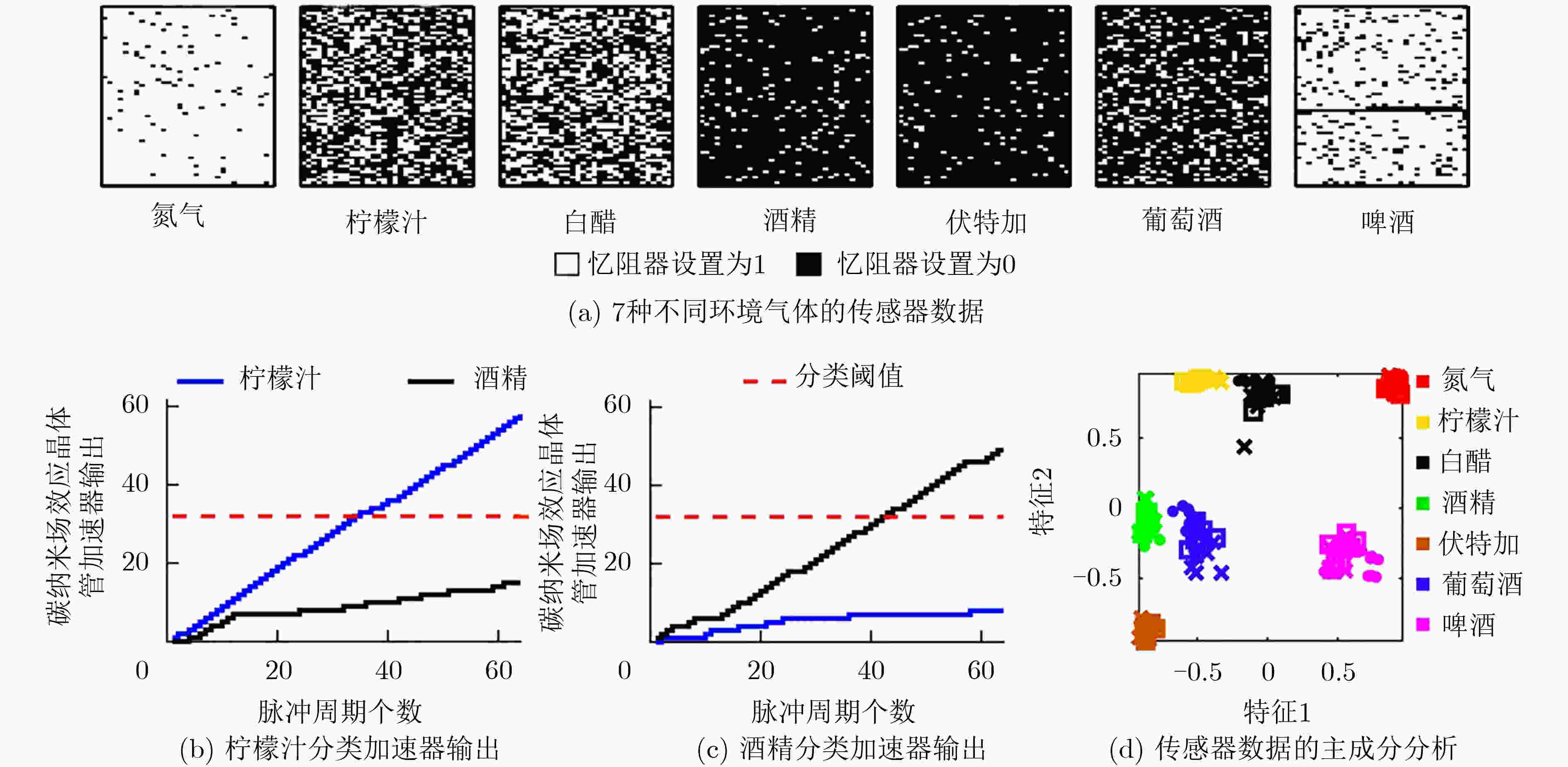

NYENKE C and DONG Lixin. Sensing ambient oxygen using a W/CuxO/Cu memristor[C]. The 10th IEEE International Conference on Nano/Micro Engineered and Molecular Systems, Xi’an, China, 2015: 254–258. doi: 10.1109/NEMS.2015.7147421.

|

| [80] |

SHULAKER M M, HILLS G, PARK R S, et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip[J]. Nature, 2017, 547(7661): 74–78. doi: 10.1038/nature22994

|

| [81] |

IWATA T, ONO K, YOSHIKAWA T, et al. Gas discrimination based on single-device extraction of transient sensor response by a MetalOxide memristor toward olfactory sensor array[C]. 2019 IEEE SENSORS, Montreal, Canada, 2019: 1–4. doi: 10.1109/SENSORS43011.2019.8956826.

|

| [82] |

ADEYEMO A, JABIR A, MATHEW J, et al. Reliable gas sensing with memristive array[C]. 2017 IEEE 23rd International Symposium on On-Line Testing and Robust System Design (IOLTS), Thessaloniki, Greece, 2017: 244–246.

|

| [83] |

KHANDELWAL S, BALA A, GUPTA V, et al. Fault modeling and simulation of memristor based gas sensors[C]. 2019 IEEE 25th International Symposium on On-Line Testing and Robust System Design (IOLTS), Rhodes, Greece, 2019: 58–59. doi: 10.1109/IOLTS.2019.8854459.

|

| [84] |

WEN Changbao, HONG Jitong, RU Feng, et al. A novel memristor-based gas cumulative flow sensor[J]. IEEE Transactions on Industrial Electronics, 2019, 66(12): 9531–9538. doi: 10.1109/TIE.2019.2891436

|

| [85] |

VIDIŠ M, PLECENIK T, MOŠKO M, et al. Gasistor: A memristor based gas-triggered switch and gas sensor with memory[J]. Applied Physics Letters, 2019, 115(9): 093504. doi: 10.1063/1.5099685

|

| [86] |

SHAH J, BARANGI M, and MAZUMDER P. Memristor crossbar memory for hybrid ultra low power hearing aid speech processor[C]. 2013 13th IEEE International Conference on Nanotechnology (IEEE-NANO 2013), Beijing, China, 2013: 83–86. doi: 10.1109/NANO.2013.6720867.

|

| [87] |

SALEH Q, MERKEL C, KUDITHIPUDI D, et al. Memristive computational architecture of an echo state network for real-time speech-emotion recognition[C]. 2015 IEEE Symposium on Computational Intelligence for Security and Defense Applications (CISDA), Verona, USA, 2015: 1–5. doi: 10.1109/CISDA.2015.7208624.

|

| [88] |

RAFIQUE M A, LEE B G, and JEON M. Hybrid neuromorphic system for automatic speech recognition[J]. Electronics Letters, 2016, 52(17): 1428–1430. doi: 10.1049/el.2016.0975

|

| [89] |

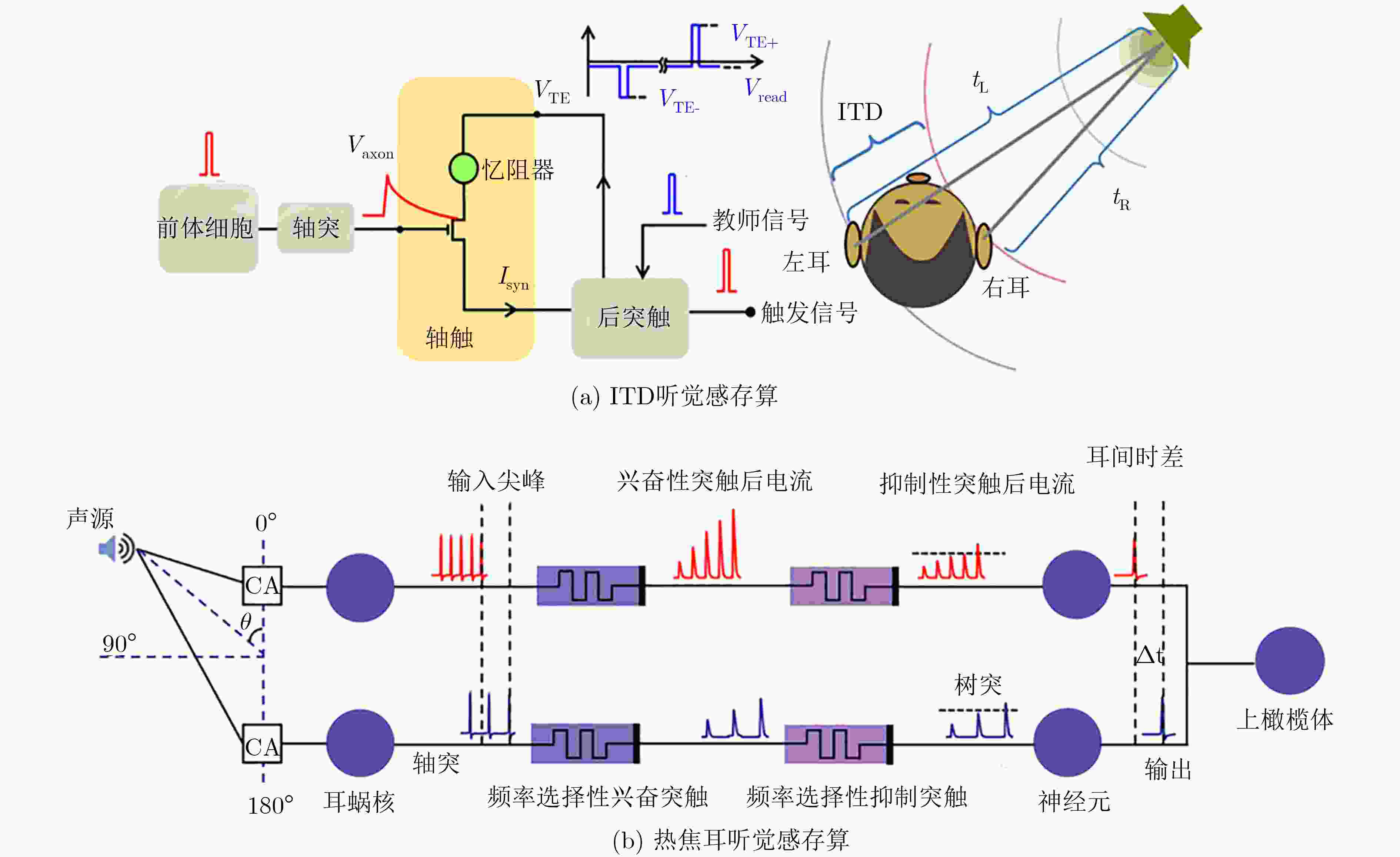

WANG Wei, PEDRETTI G, MILO V, et al. Learning of spatiotemporal patterns in a spiking neural network with resistive switching synapses[J]. Science Advances, 2018, 4(9): eaat4752. doi: 10.1126/sciadv.aat4752

|

| [90] |

SUN Linfeng, ZHANG Yishu, HWANG G, et al. Synaptic computation enabled by joule heating of single-layered semiconductors for sound localization[J]. Nano Letters, 2018, 18(4): 3229–3234. doi: 10.1021/acs.nanolett.8b00994

|

| [91] |

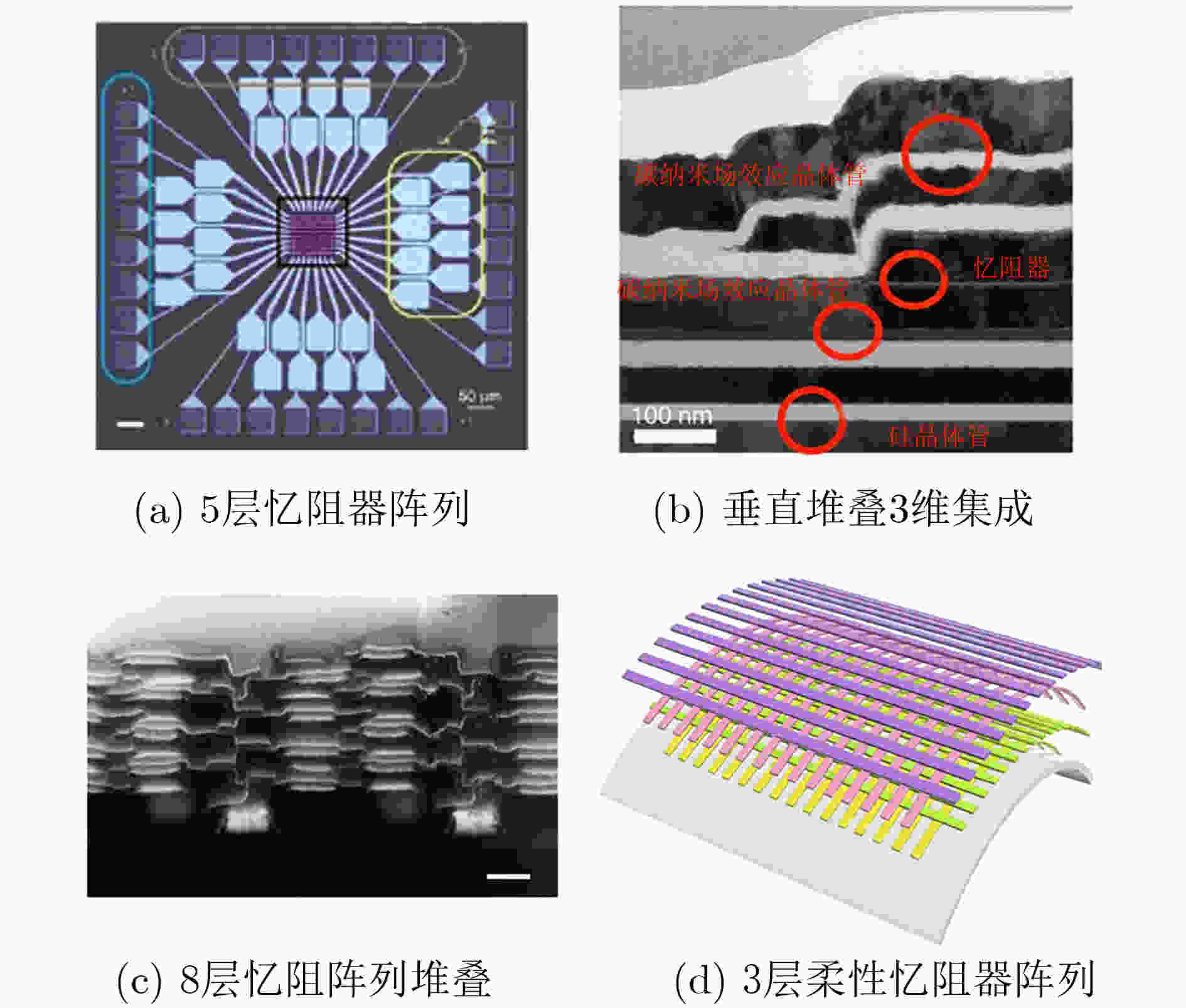

LI Can, HAN Lili, JIANG Hao, et al. Three-dimensional crossbar arrays of self-rectifying Si/SiO2/Si memristors[J]. Nature Communications, 2017, 8: 15666. doi: 10.1038/ncomms15666

|

| [92] |

BISHOP M D, WONG H S P, MITRA S, et al. Monolithic 3-D integration[J]. IEEE Micro, 2019, 39(6): 16–27. doi: 10.1109/MM.2019.2942982

|

| [93] |

LIN Peng, LI Can, WANG Zhongrui, et al. Three-dimensional memristor circuits as complex neural networks[J]. Nature Electronics, 2020, 3(4): 225–232. doi: 10.1038/s41928-020-0397-9

|

| [94] |

WANG Tianyu, MENG Jialin, CHEN Lin, et al. Flexible 3D memristor array for binary storage and multi‐states neuromorphic computing applications[J]. InfoMat, 2021, 3(2): 212–221. doi: 10.1002/inf2.12158

|

| [95] |

AN Hongyu, EHSAN M A, ZHOU Zhen, et al. Monolithic 3D neuromorphic computing system with hybrid CMOS and memristor-based synapses and neurons[J]. Integration, 2019, 65: 273–281. doi: 10.1016/j.vlsi.2017.10.009

|

| [96] |

SUN W, CHOI S, KIM B, et al. Three-dimensional (3D) vertical resistive random-access memory (VRRAM) synapses for neural network systems[J]. Materials, 2019, 12(20): 3451. doi: 10.3390/ma12203451

|

| [97] |

FERNANDO B R, QI Yangjie, YAKOPCIC C, et al. 3D memristor crossbar architecture for a multicore neuromorphic system[C]. 2020 International Joint Conference on Neural Networks (IJCNN), Glasgow, UK, 2020. doi: 10.1109/IJCNN48605.2020.9206929.

|

下载:

下载:

下载:

下载: