A General Method of Generating Code Density Calibration Signal for Time-to-Digital Converter and Its Realization

-

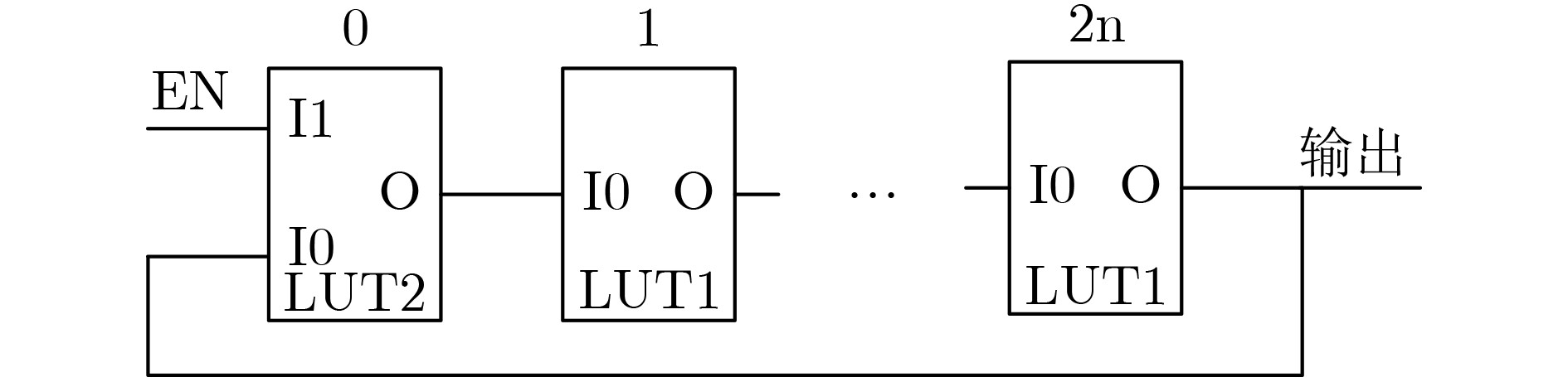

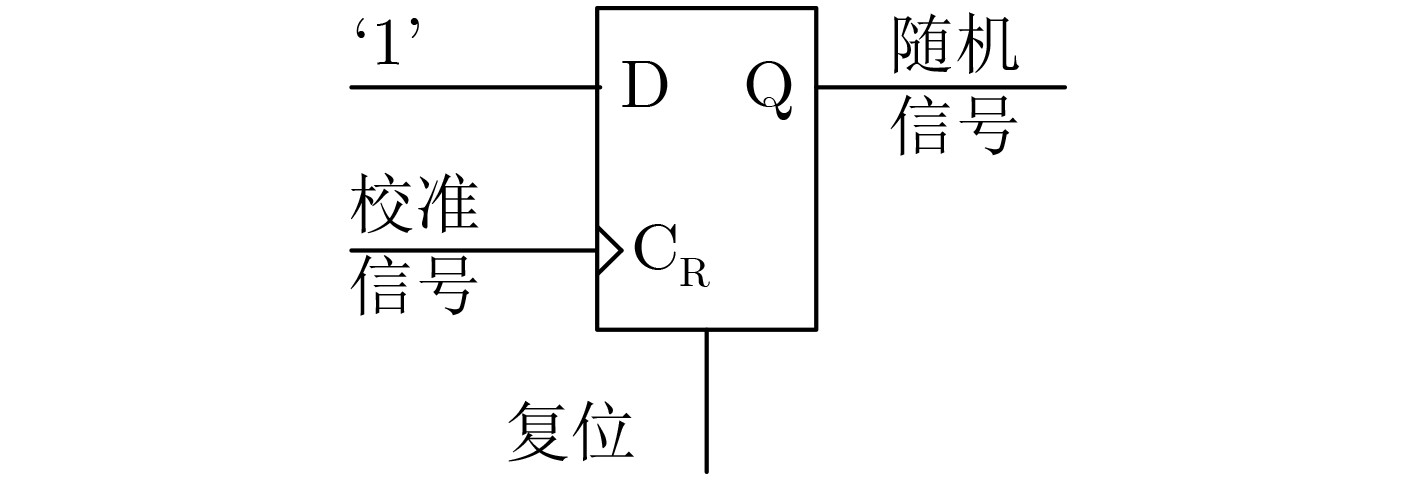

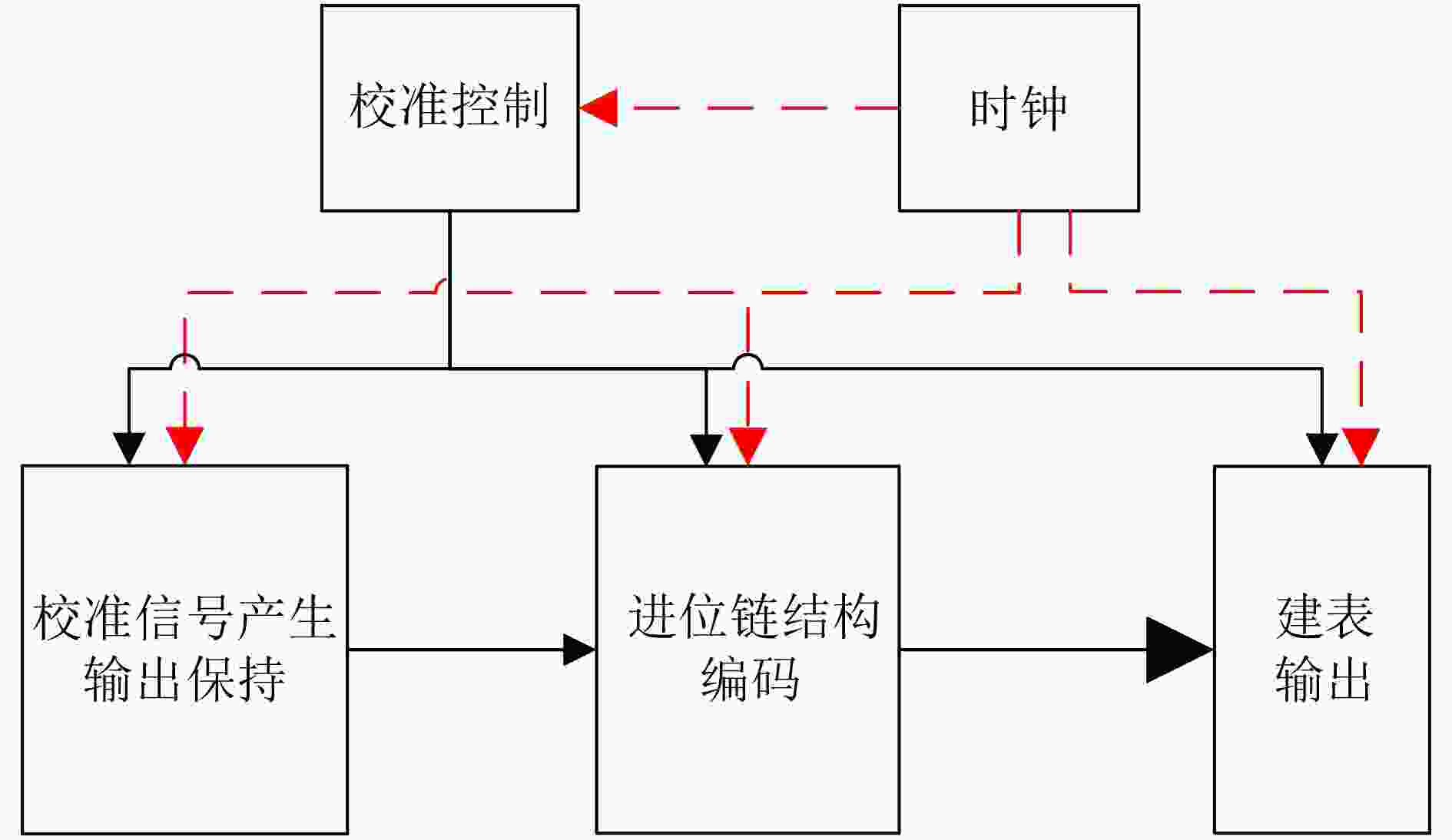

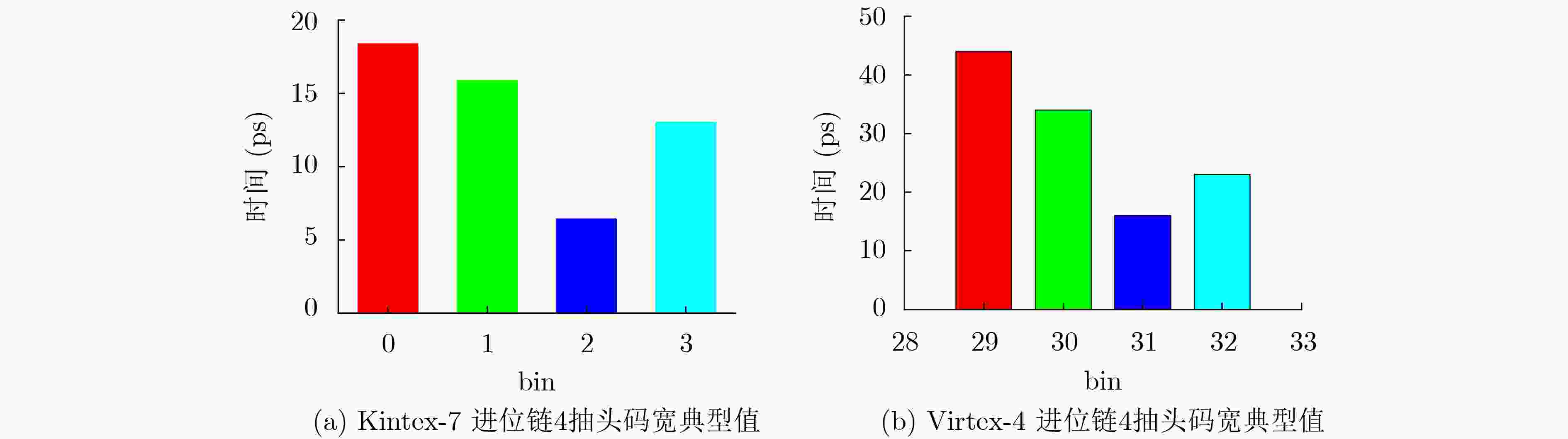

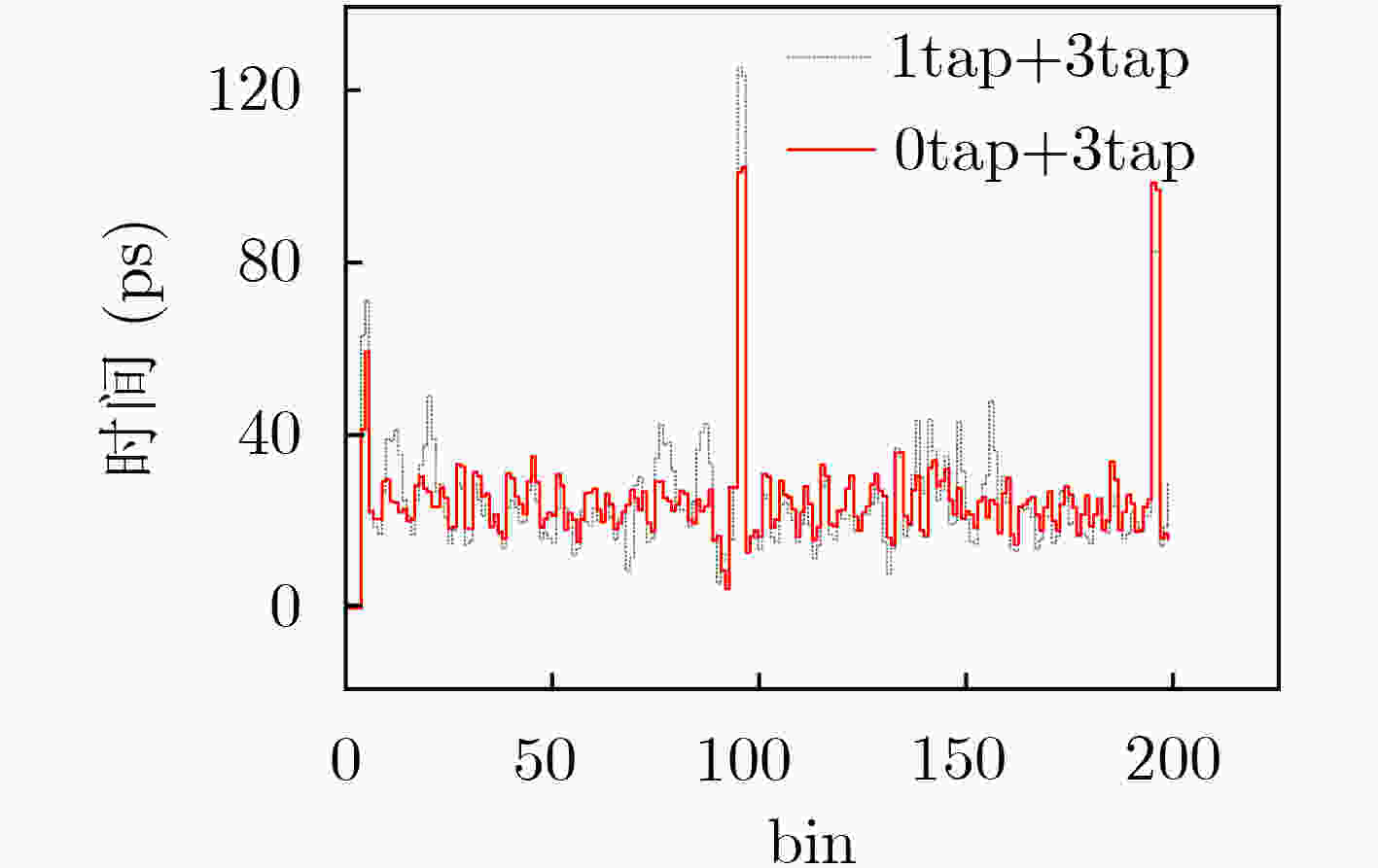

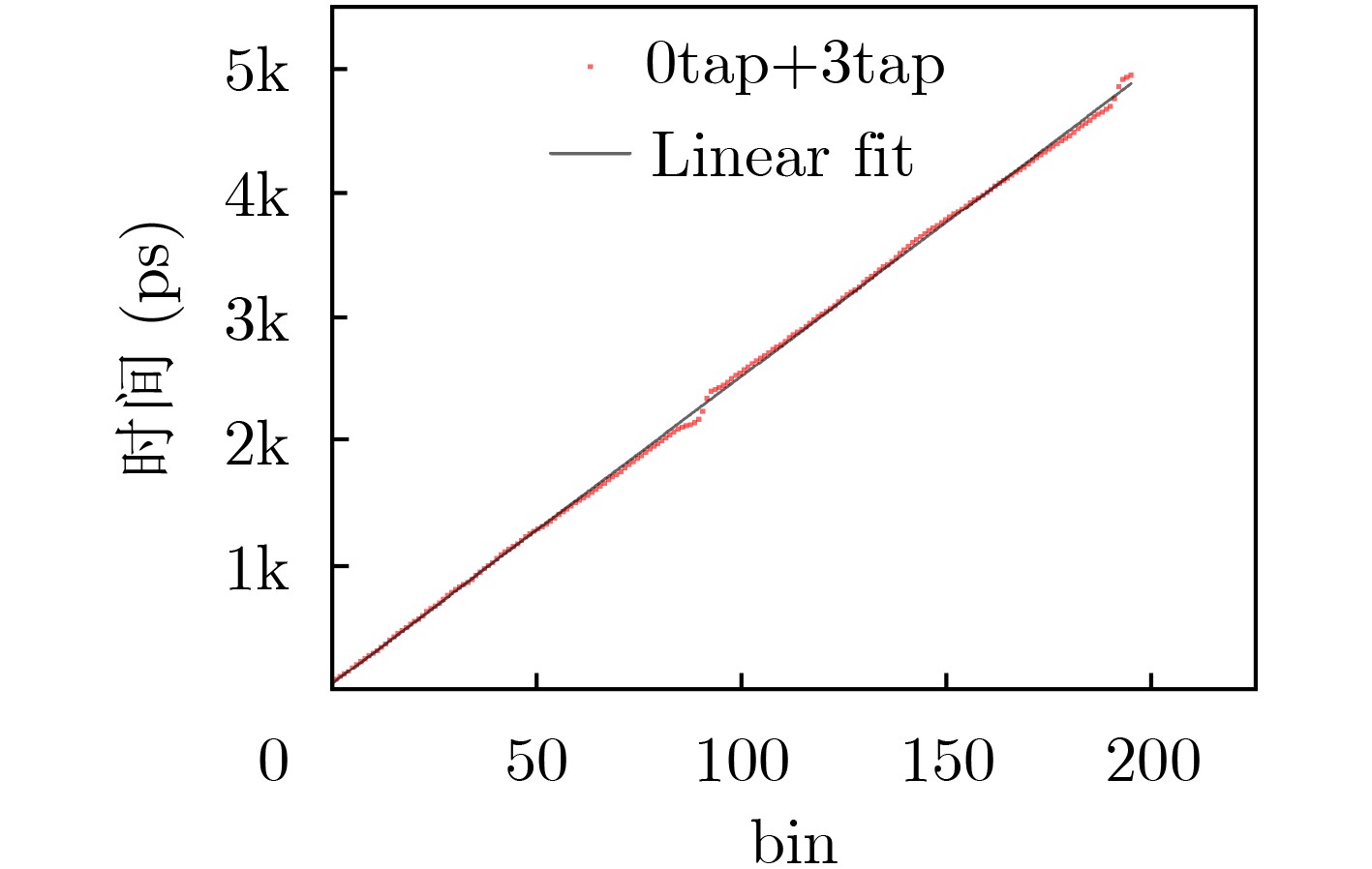

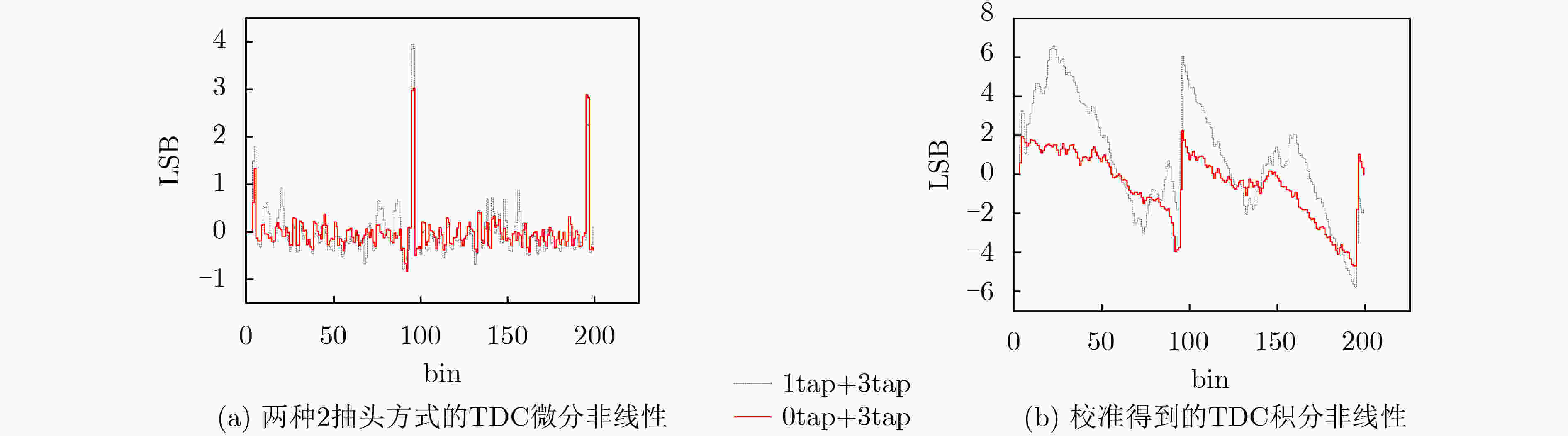

摘要: 该文提出一种通用的时间数字转换器(TDC)码密度校准信号产生方法,该方法基于相干采样理论,通过合理设置TDC主时钟和校准信号之间的频率差,结合输出信号保持电路,产生校准用的随机信号,在码密度校准过程中,随机信号均匀分布在TDC的延时路径上,实现对TDC的bin-by-bin校准。基于Xilinx公司的28 nm工艺的Kintex-7 现场可编程门阵列(FPGA)内部的进位链实现一种plain TDC,利用该方法校准plain TDC的码宽(抽头延迟时间),研究校准了2抽头方式下的TDC的性能参数,时间分辨率(对应TDC的最低有效位,Least Significant Bit, LSB)为24.9 ps,微分非线性为(–0.84~3.1)LSB,积分非线性为(–5.0~2.2)LSB。文中所述的校准方法采用时钟逻辑资源实现,多次测试考核结果表明,单个延时单元的标准差优于0.5 ps。该校准方法采用时钟逻辑资源代替组合逻辑资源,重复性、稳定性较好,实现了对plain TDC的高精度自动校准。该方法同样适用于其他类型的TDC的码密度校准。Abstract: This paper proposes a universal Time-to-Digital Converter (TDC) code density calibration signal generation method, which is based on the theory of coherent sampling. By reasonably setting the frequency difference between the TDC master clock and the calibration signal, combining with the output hold circuit, a random signal for calibration is generated to ensure that the random signal is evenly distributed on the TDC delay path to achieve Bin-by-bin calibration of TDC. The paper implements a carry chain plain TDC based on XILINX’s 28 nm Kintex-7 Field Programmable Gate Array (FPGA). The method is used to calibrate the code width (tap delay time) of plain TDC, and the performance parameters of TDC in 2-tap mode are studied and calibrated. The time resolution (corresponding to the least significant bit of TDC, Least Significant Bit, LSB) is 24.9 ps, with the differential nonlinearity is (–0.84~3.1) LSB, and the integral nonlinearity is (–5.0~2.2) LSB. The calibration method described in the paper is implemented using clock logic resources, and multiple tests show that the standard deviation of a single delay unit is better than 0.5 ps. This calibration method uses clock logic resources instead of combinatorial logic resources to realize high-precision automatic calibration of plain TDC, with good repeatability and stability. This method is also suitable for other types of TDC code density calibration.

-

表 1 LUT1真值表

I0 O 0 1 1 0 表 2 LUT2真值表

I1 I0 O 0 0 0 0 1 0 1 0 1 1 1 0 -

[1] 周浩. 基于FPGA进位链的时间数字转换器设计[D]. [硕士论文], 重庆邮电大学, 2017.ZHOU Hao. Design of a time-to-digital converter based on carry-in lines of FPGA[D]. [Master dissertation], Chongqing University of Posts and Telecommunications, 2017. [2] 范欢欢. 基于FPGA的时间数字转换电路的若干关键技术的研究[D]. [博士论文], 中国科学技术大学, 2015.FAN Huanhuan. Some key technologies about time-to-digital converter based on FPGA[D]. [Ph. D. dissertation], University of Science and Technology of China, 2015. [3] WU Jinyuan. Several key issues on implementing delay line based TDCs using FPGAs[J]. IEEE Transactions on Nuclear Science, 2010, 57(3): 1543–1548. doi: 10.1109/TNS.2010.2045901 [4] BAYER E and TRAXLER M. A high-resolution (< 10 ps RMS)48-channel time-to-digital converter (TDC) implemented in a field programmable gate array (FPGA)[J]. IEEE Transactions on Nuclear Science, 2011, 58(4): 1547–1552. doi: 10.1109/TNS.2011.2141684 [5] FISHBURN M W, MENNINGA L H, FAVI C, et al. A 19.6 ps, FPGA-based TDC with multiple channels for open source applications[J]. IEEE Transactions on Nuclear Science, 2013, 60(3): 2203–2208. doi: 10.1109/TNS.2013.2241789 [6] 高丽江, 杨海钢, 李威, 等. 具有高资源利用率特征的改进型查找表电路结构与优化方法[J]. 电子与信息学报, 2019, 41(10): 2382–2388. doi: 10.11999/JEIT190095GAO Lijiang, YANG Haigang, LI Wei, et al. A circuit optimization method of improved lookup table for Highly efficient resource utilization[J]. Journal of Electronics &Information Technology, 2019, 41(10): 2382–2388. doi: 10.11999/JEIT190095 [7] WANG Yonggang and LIU Chong. A 3.9 ps time-interval RMS precision time-to-digital converter using a dual-sampling method in an UltraScale FPGA[J]. IEEE Transactions on Nuclear Science, 2016, 63(5): 2617–2621. doi: 10.1109/TNS.2016.2596305 [8] HU Xueye, ZHAO Lei, LIU Shubin, et al. A stepped-up tree encoder for the 10-ps wave union TDC[J]. IEEE Transactions on Nuclear Science, 2013, 60(5): 3544–3549. doi: 10.1109/TNS.2013.2265555 [9] ZHAO Lei, HU Xueye, LIU Shubin, et al. The design of a 16-channel 15 ps TDC implemented in a 65 nm FPGA[J]. IEEE Transactions on Nuclear Science, 2013, 60(5): 3532–3536. doi: 10.1109/TNS.2013.2280909 [10] 王巍, 董永孟, 李捷, 等. 基于FPGA的高精度多通道时间数字转换器设计[J]. 微电子学, 2015, 45(6): 698–701, 705.WANG Wei, DONG Yongmeng, LI Jie, et al. Design of a high resolution and multichannel TDC based on FPGA[J]. Microelectronics, 2015, 45(6): 698–701, 705. -

下载:

下载:

下载:

下载: