Low Complexity and Reconfigurable LDPC Encoder for High-speed Satellite-to-ground Data Transmissions

-

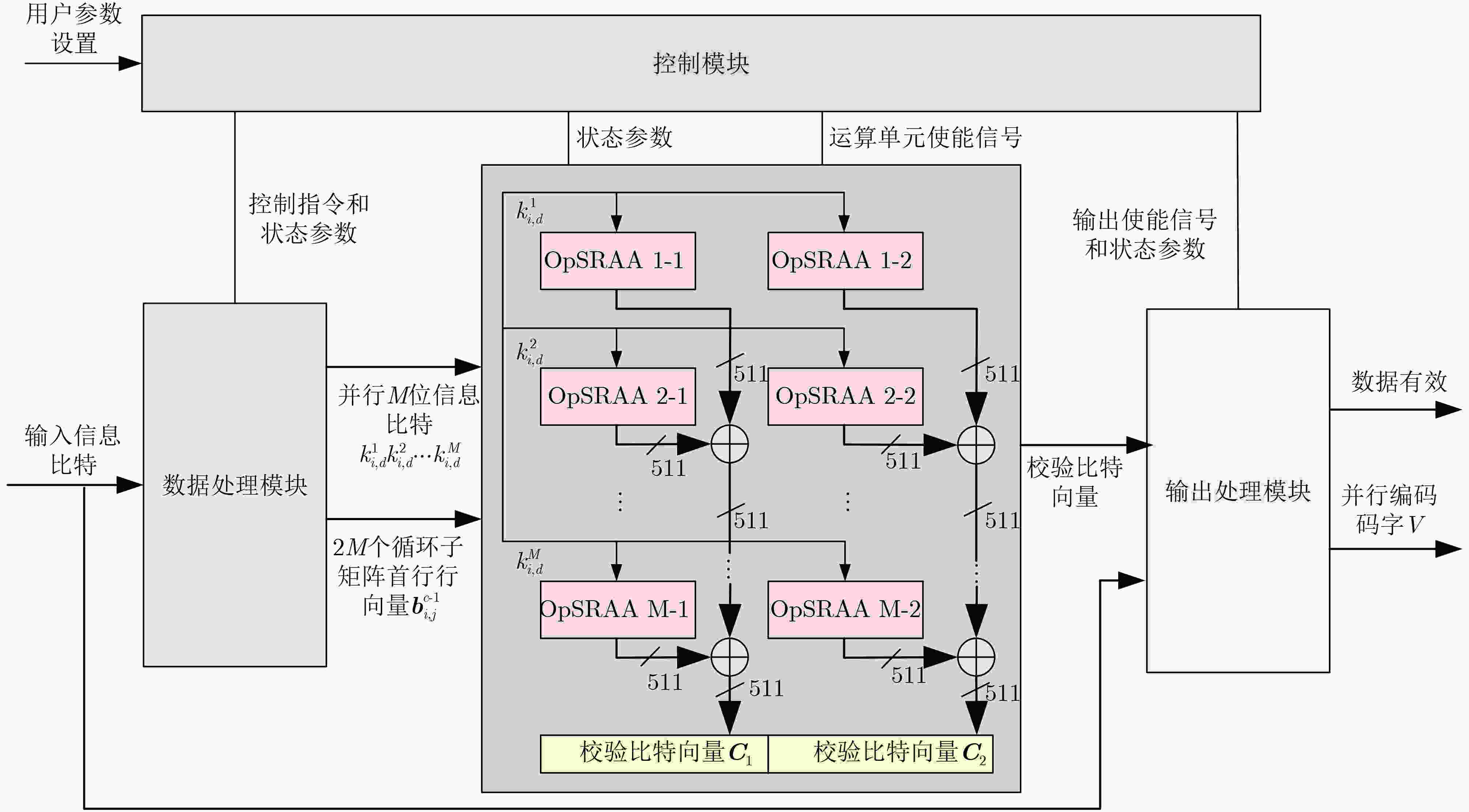

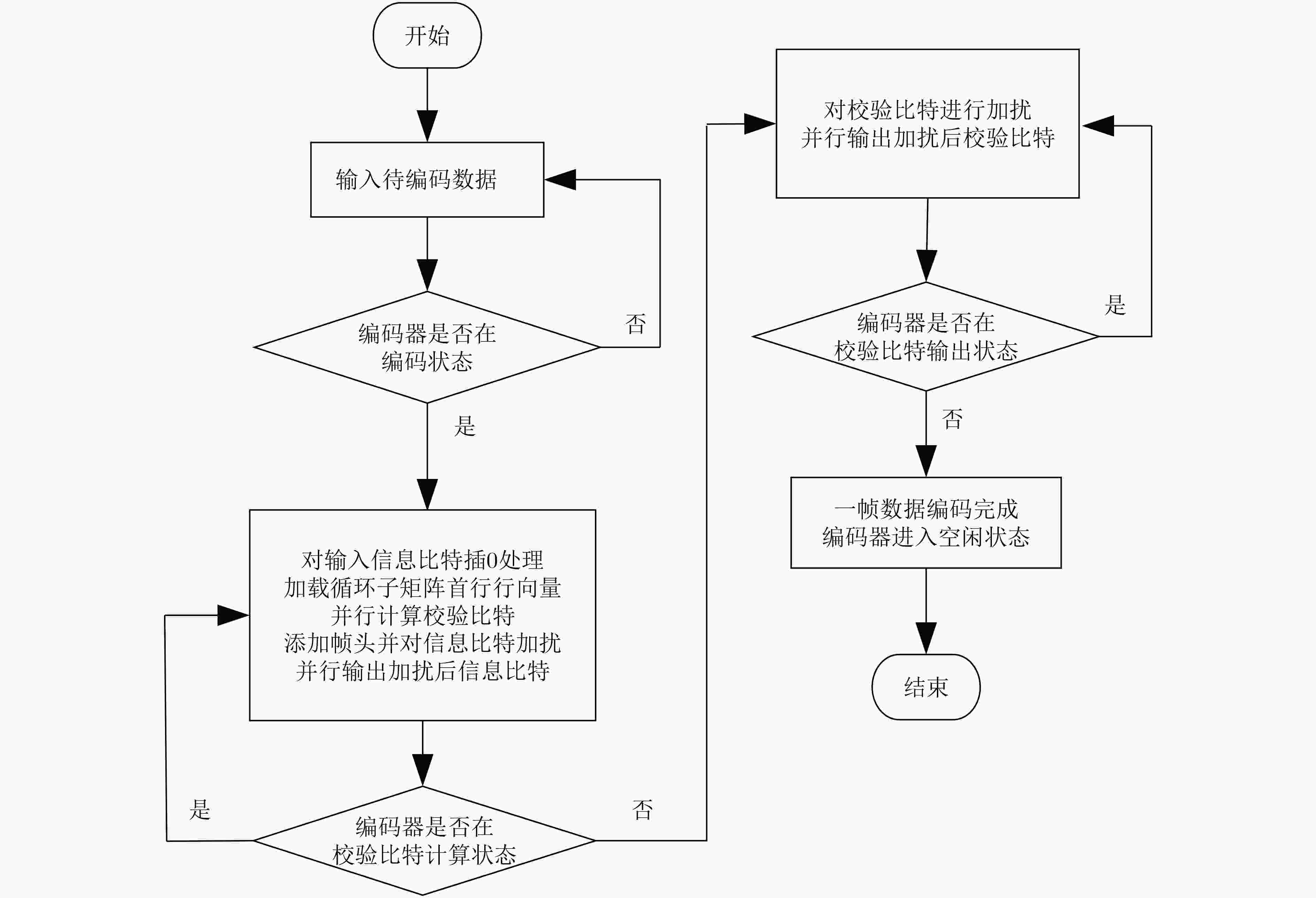

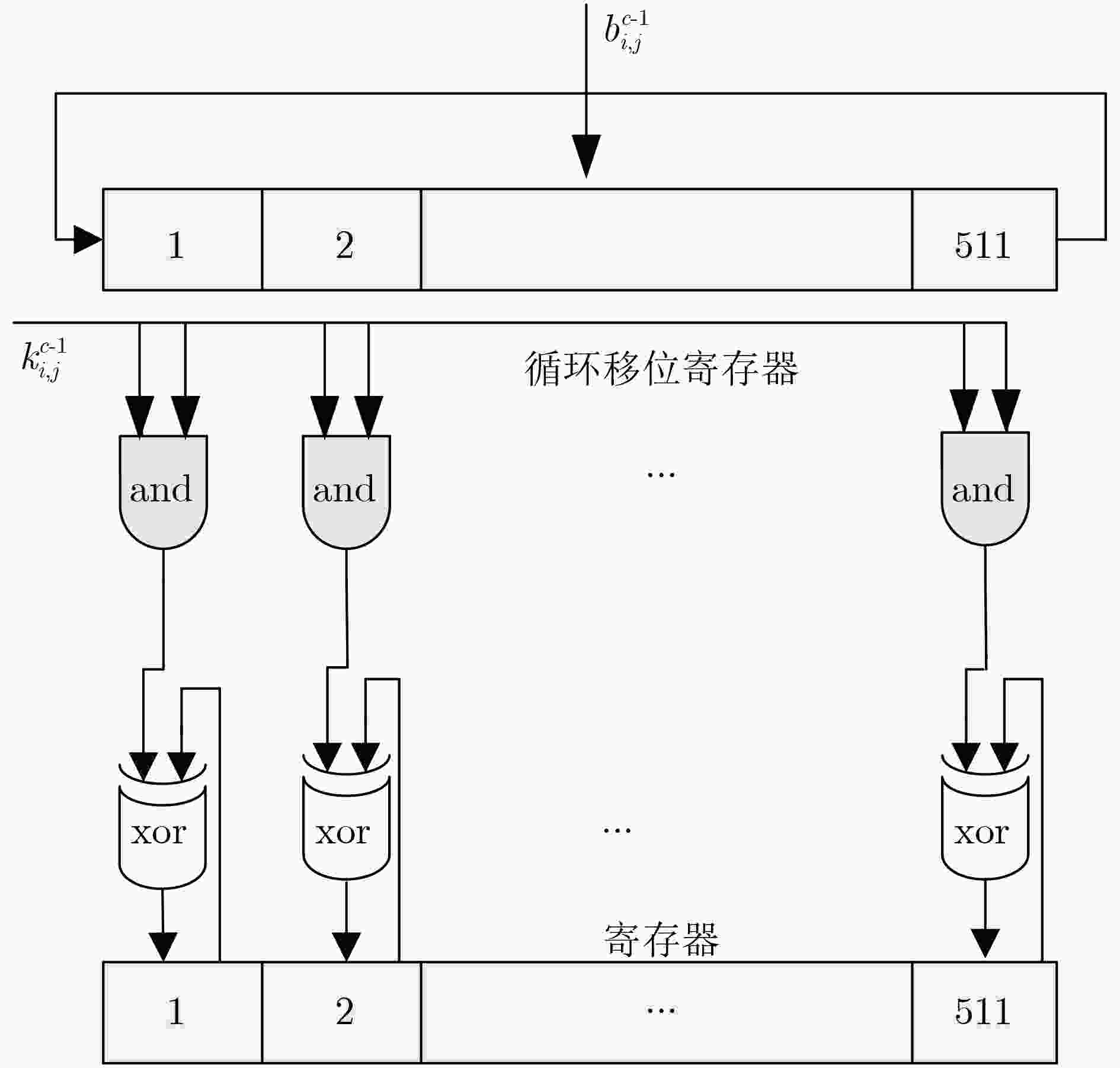

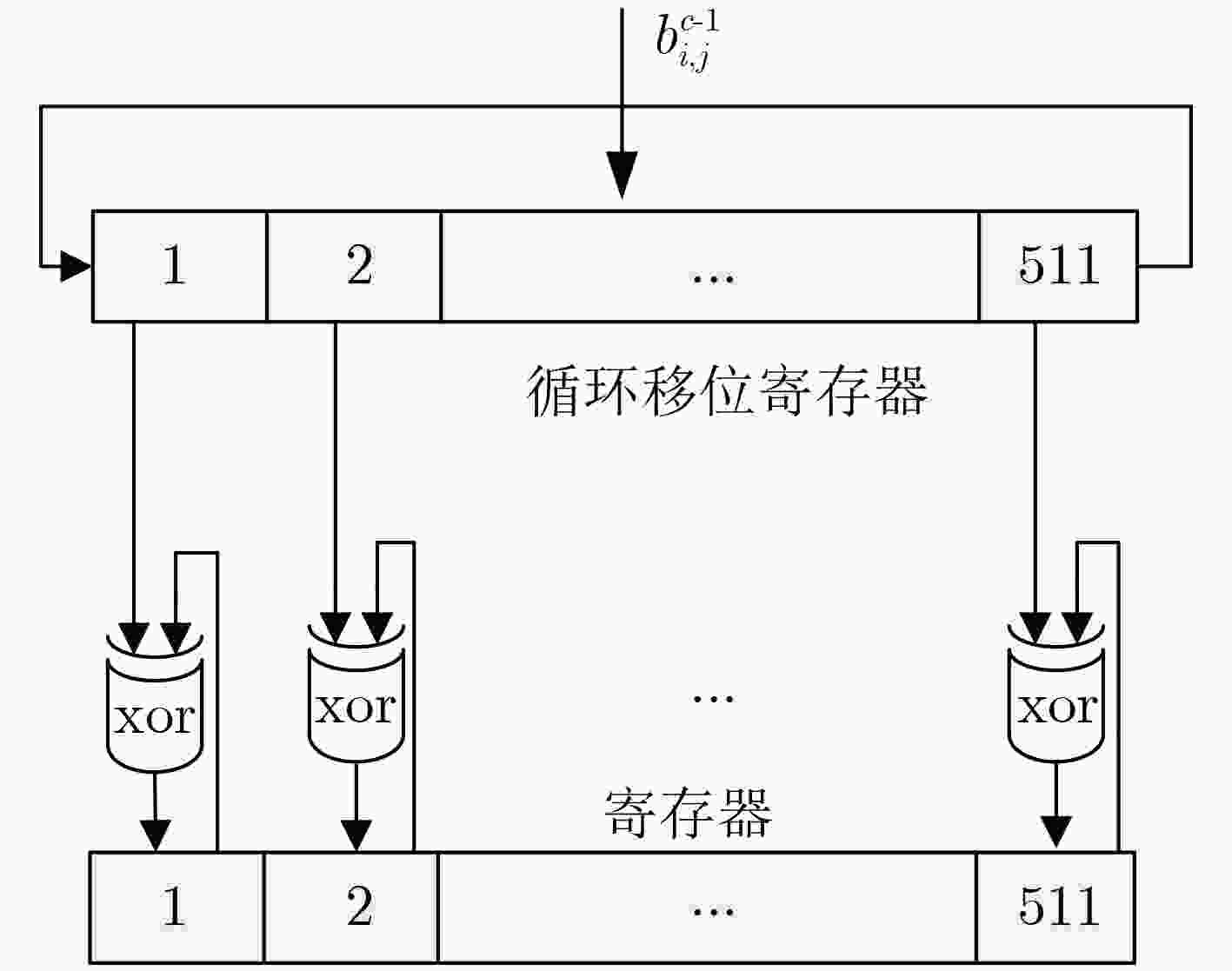

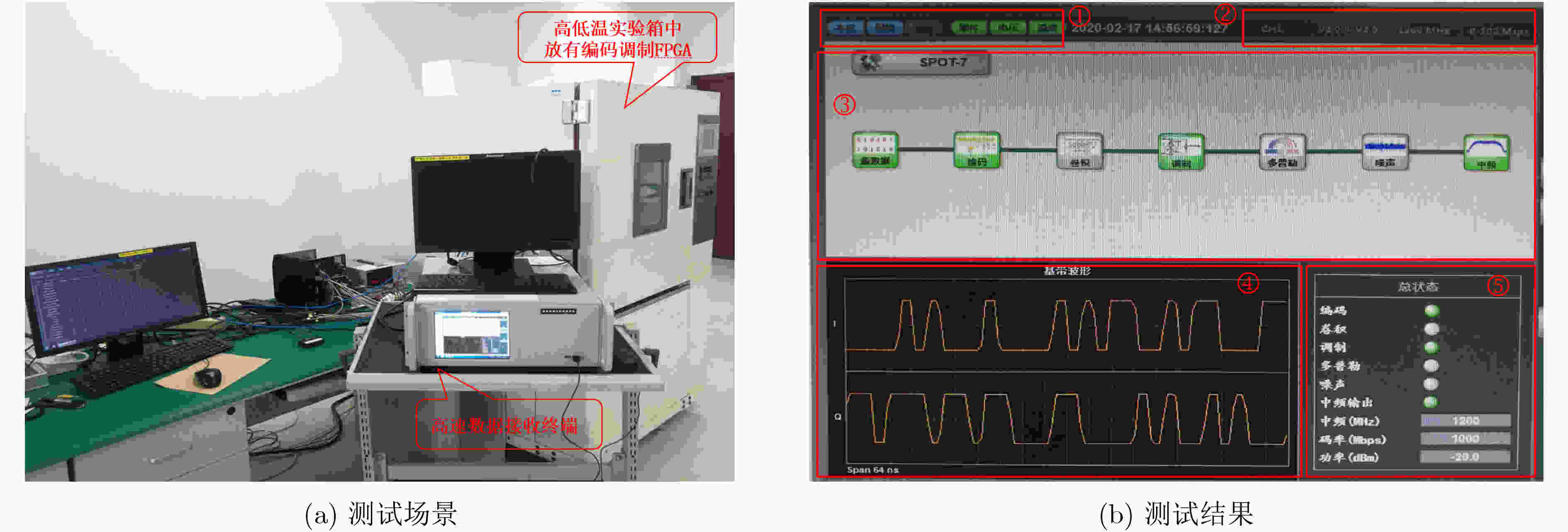

摘要: 为满足近地轨道(LEO)卫星星地高速数传系统对高通量、低复杂度、高可靠性信道编码的应用需求,该文提出一种基于国际空间数据系统咨询委员会(CCSDS)近地卫星通信标准低密度奇偶校验(LDPC)码的低复杂度可重构编码器设计实现方案。通过对输入信息比特插0处理和拆分循环矩阵,并分析不同并行度编码的结构特点,实现了可重构编码方案,提高了编码器的灵活性和编码数据吞吐率;采用优化的移位寄存器累加单元,降低了编码器的整体硬件资源规模。在Xilinx FPGA上对提出的编码器进行了实现,结果表明,在125 MHz系统工作时钟下,编码数据吞吐率最高可达1 Gbps,归一化编码数据吞吐率与其它文献并行度相近的编码器相比提高了17.1%,其寄存器资源和查找表资源与相同平台已有方案相比分别降低了13.7%和14.8%。Abstract: A new low complexity and reconfigurable Low Density Parity Check (LDPC) encoder design based on the Consultative Committee for Space Data Systems (CCSDS) standard is proposed to meet the high throughput, low latency and high reliability requirement for high-speed satellite-to-ground data transmission systems of Low Earth Orbit (LEO). This design is parallel reconfigurable by inserting 0 into information bits and splitting cyclic matrices, and analyzed the structural characteristics of different parallelism encoding. Benefitting from the parallel reconfiguration, the throughput is increased and the flexibility is guaranteed. Furthermore, using optimized shift register adder accumulators can reduce the hardware resources. The proposed encoder design is implemented on Xilinx FPGA. The experimental results show that the maximum encoding speed is up to 1 Gbps @125 MHz, and the normalized throughput is increased by 17.1% compared with the similar parallel encoder. And resources of registers and look-up tables are reduced by 13.7% and 14.8% respectively, compared with the existing encoder.

-

表 1 SRAA和OpSRAA资源对比

寄存器 二输入异或门 二输入与门 SRAA $511 \times 2$ 511 511 OpSRAA $511 \times 2$ 511 0 表 2 不同文献编码器对比

表 3 本文编码器吞吐率

编码并行度$M$ ${t_{{\rm{cycle}}}}$ T(Mbps) 编码延时(ms) 2 4096 259.29 31.59 4 2048 517.58 15.83 8 1024 1031.14 7.94 注:编码延时=n/T,为待编码数据进入编码器到编码完成所需时间。 -

[1] 李炯卉. 基于可变编码多载波调制技术的星地高速数传系统研究[D]. [博士论文], 中国科学院大学(中国科学院国家空间科学中心), 2018.LI Jionghui. Satellite-ground high-rate data transmission system based on variable coding multi-carrier modulation[D].[Ph.D. dissertation], University of Chinese Academy of Sciences (National Space Science Center, the Chinese Academy of Sciences), 2018. [2] 张浩, 殷柳国. 星地高速数传系统LDPC编码器ASIC集成芯片设计[J]. 宇航学报, 2015, 36(1): 96–102. doi: 10.3873/j.issn.1000-1328.2015.01.013ZHANG Hao and YIN Liuguo. ASIC design of an LDPC encoder for satellite-ground high-speed data transmission system[J]. Journal of Astronautics, 2015, 36(1): 96–102. doi: 10.3873/j.issn.1000-1328.2015.01.013 [3] GALLAGER R. Low-density parity-check codes[J]. IRE Transactions on Information Theory, 1962, 8(1): 21–28. doi: 10.1109/TIT.1962.1057683 [4] CCSDS. CCSDS 131.0-B-2-TM Synchronization and channel coding[S]. Washington: CCSDS, 2011. [5] WU Hao and WANG Huayong. A high throughput implementation of QC-LDPC codes for 5G NR[J]. IEEE Access, 2019, 7: 185373–185384. doi: 10.1109/ACCESS.2019.2960839 [6] MAHDI A and PALIOURAS V. A low complexity-high throughput QC-LDPC encoder[J]. IEEE Transactions on Signal Processing, 2014, 62(10): 2696–2708. doi: 10.1109/tsp.2014.2314435 [7] 马明晓, 安军社. 欧氏几何LDPC长码的卫星通信编码方案研究[J]. 计算机测量与控制, 2014, 22(3): 813–815, 829. doi: 10.16526/j.cnki.11-4762/tp.2014.03.051MA Mingxiao and AN Junshe. Research on long Euclidean geometry-based LDPC coding scheme for satellite communications[J]. Computer measurement &Control, 2014, 22(3): 813–815, 829. doi: 10.16526/j.cnki.11-4762/tp.2014.03.051 [8] 燕威, 薛长斌. 高效低功耗低并行度LDPC编码方法[J]. 电子与信息学报, 2016, 38(9): 2268–2273. doi: 10.11999/JEIT151362YAN Wei and XUE Changbin. An efficient LDPC encoder scheme with low-power low-parallel[J]. Journal of Electronics &Information Technology, 2016, 38(9): 2268–2273. doi: 10.11999/JEIT151362 [9] WANG Zhaohui, HAO Xin, LIN Changxing, et al. An efficient hardware LDPC encoder based on partial parallel structure for CCSDS[C]. The IEEE 18th International Conference on Communication Technology, Chongqing, China, 2018: 136–139. [10] 叶荣润, 黄聪, 俞帆. 高速并行LDPC编码的FPGA实现[J]. 无线电工程, 2012, 42(3): 25–26, 37. doi: 10.3969/j.issn.1003-3106.2012.03.008YE Rongrun, HUANG Cong, and YU Fan. FPGA implementation of high-speed parallel LDPC encoding[J]. Radio Engineering, 2012, 42(3): 25–26, 37. doi: 10.3969/j.issn.1003-3106.2012.03.008 [11] 曹明星. 卫星通信中LDPC码高速编译码器实现技术研究[D].[硕士论文], 西安电子科技大学, 2018.CAO Mingxing. Implementation of high-speed codec for LDPC codes in satellite communication[D].[Master dissertation], Xidian University, 2018. [12] 王干. 800 Mbps吞吐率LDPC码并行编译码关键技术与验证[D]. [硕士论文], 电子科技大学, 2017.WANG Gan. Key technology and verification of 800Mbps throughput parallel coding and decoding for LDPC code[D]. [Master dissertation], University of Electronic Science and Technology of China, 2017. [13] 栾志斌, 裴玉奎, 葛宁. 低存储高速可重构LDPC码译码器设计及ASIC实现[J]. 电子与信息学报, 2014, 36(10): 2287–2292. doi: 10.3724/SP.J.1146.2013.01939LUAN Zhibin, PEI Yukui, and GE Ning. Design and ASIC implementation of low memory high throughput reconfigurable LDPC decoder[J]. Journal of Electronics &Information Technology, 2014, 36(10): 2287–2292. doi: 10.3724/SP.J.1146.2013.01939 [14] 魏星, 黄志洪, 杨海钢. 高吞吐率双模浮点可重构FFT处理器设计实现[J]. 电子与信息学报, 2018, 40(12): 3042–3050. doi: 10.11999/JEIT180170WEI Xing, HUANG Zhihong, and YANG Haigang. High throughput dual-mode reconfigurable floating-point FFT processor[J]. Journal of Electronics &Information Technology, 2018, 40(12): 3042–3050. doi: 10.11999/JEIT180170 [15] 王刚, 李冰, 刘勇, 等. 一种可重构LDPC编码器的设计与实现[J]. 微计算机信息, 2010, 26(12-2): 168–170. doi: 10.3969/j.issn.2095-6835.2010.35.067WANG Gang, LI Bing, LIU Yong, et al. Design and implementation of a reconfigurable LDPC encoder[J]. Microcomputer Information, 2010, 26(12-2): 168–170. doi: 10.3969/j.issn.2095-6835.2010.35.067 [16] 袁东风, 张海刚. LDPC码理论与应用[M]. 北京: 人民邮电出版社, 2008: 37–40.YUAN Dongfeng and ZHANG Haigang. LDPC Code Theory and Applications[M]. Beijing: Post & Telecom Press, 2008: 37–40. -

下载:

下载:

下载:

下载: