Study on the Physical Unclonable Function of the Reliable Information Entropy Extracted by the Frequency Characteristic of Oscillating Ring

-

摘要:

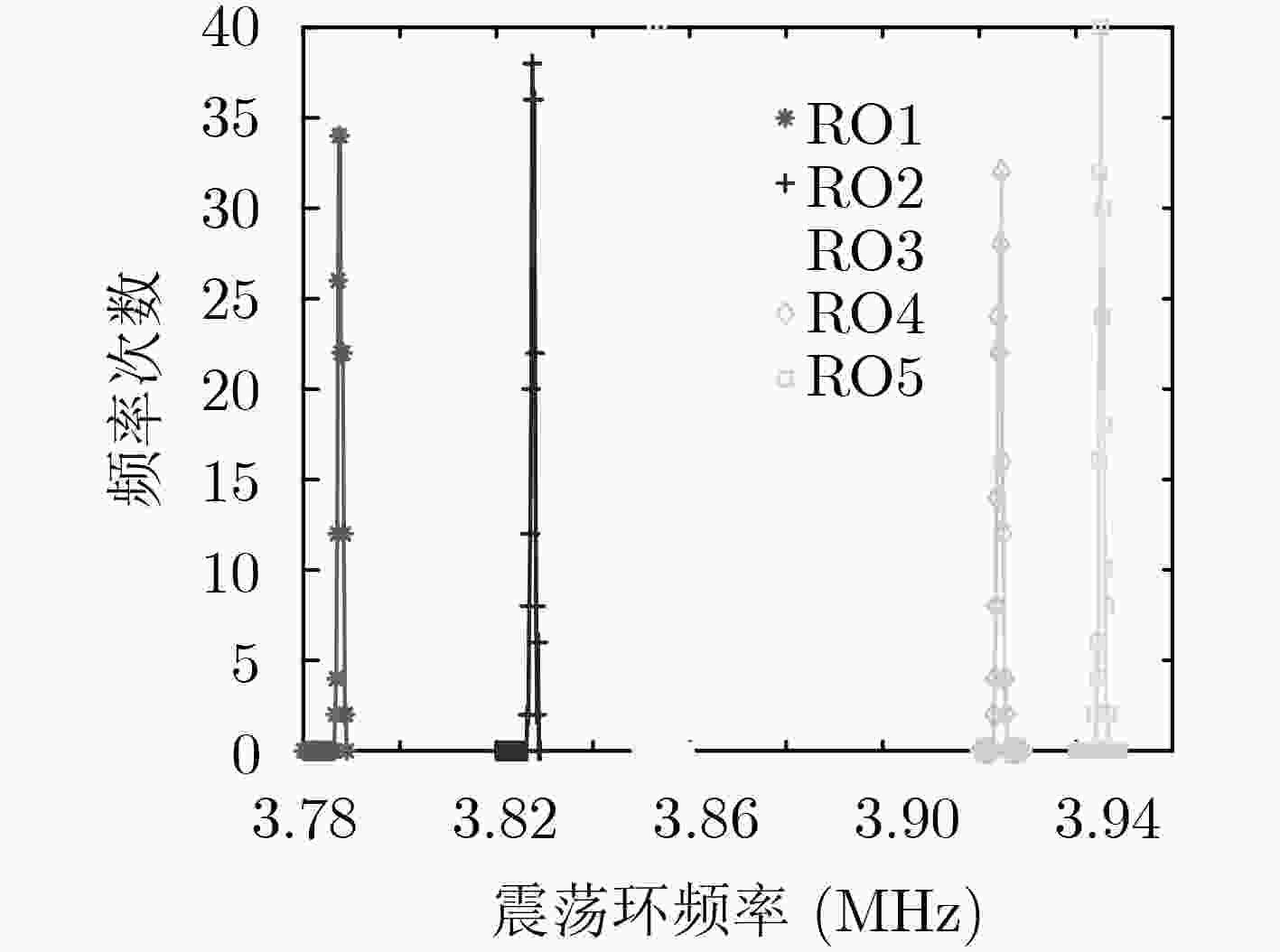

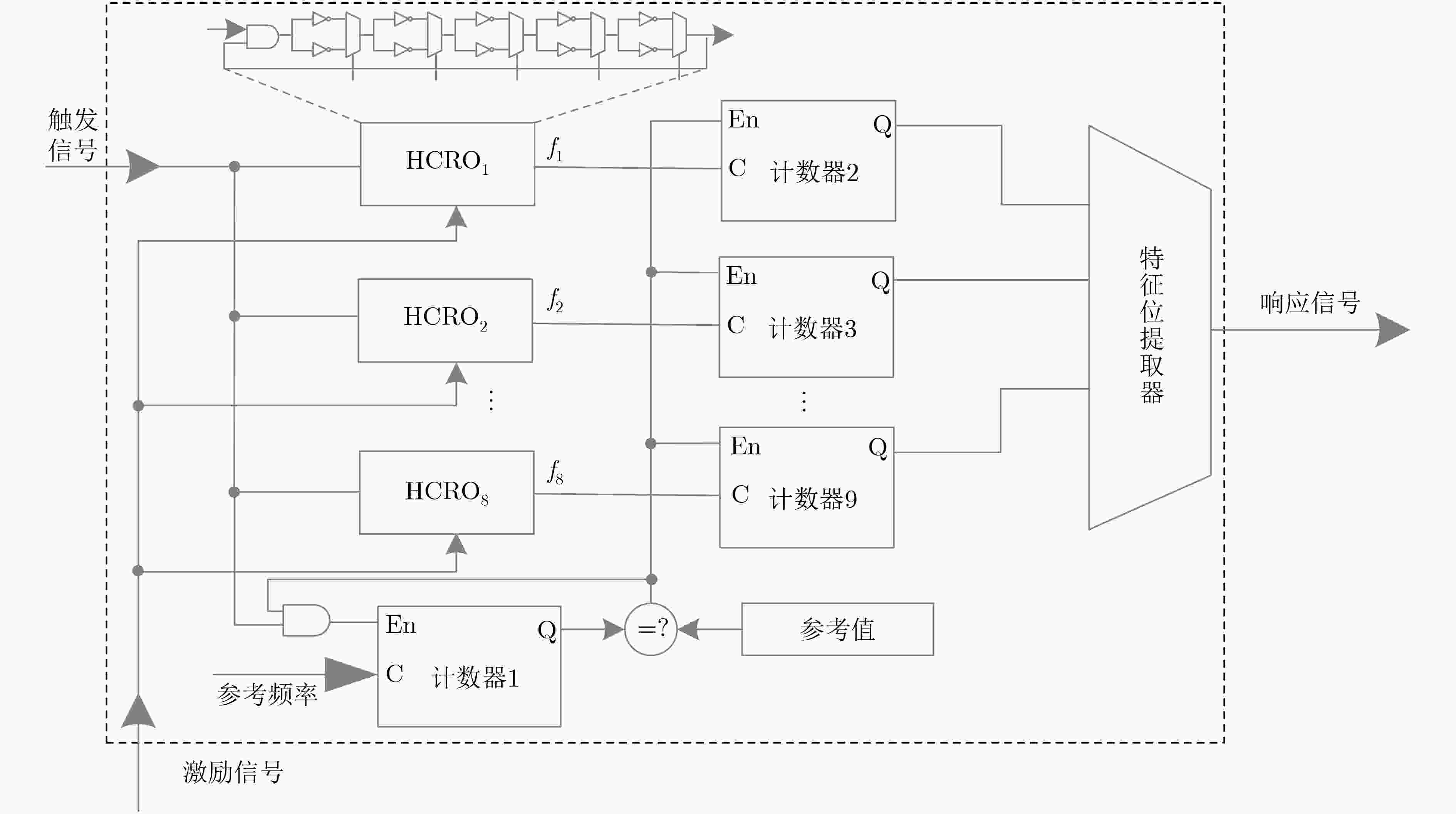

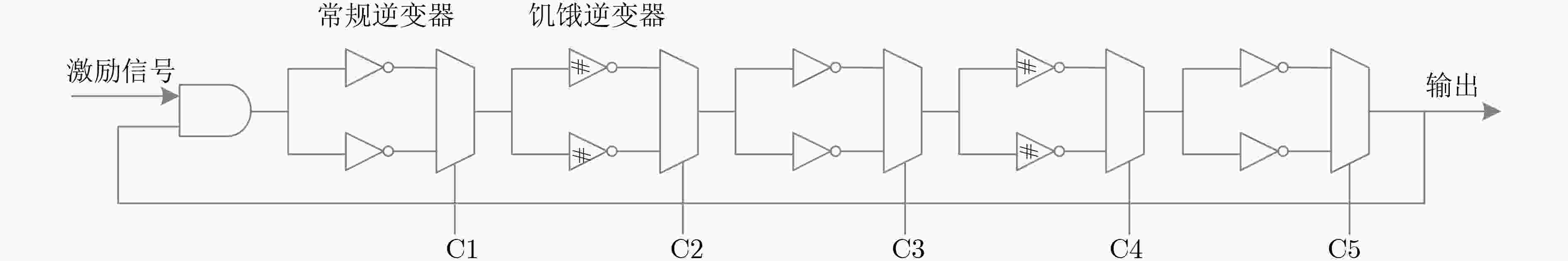

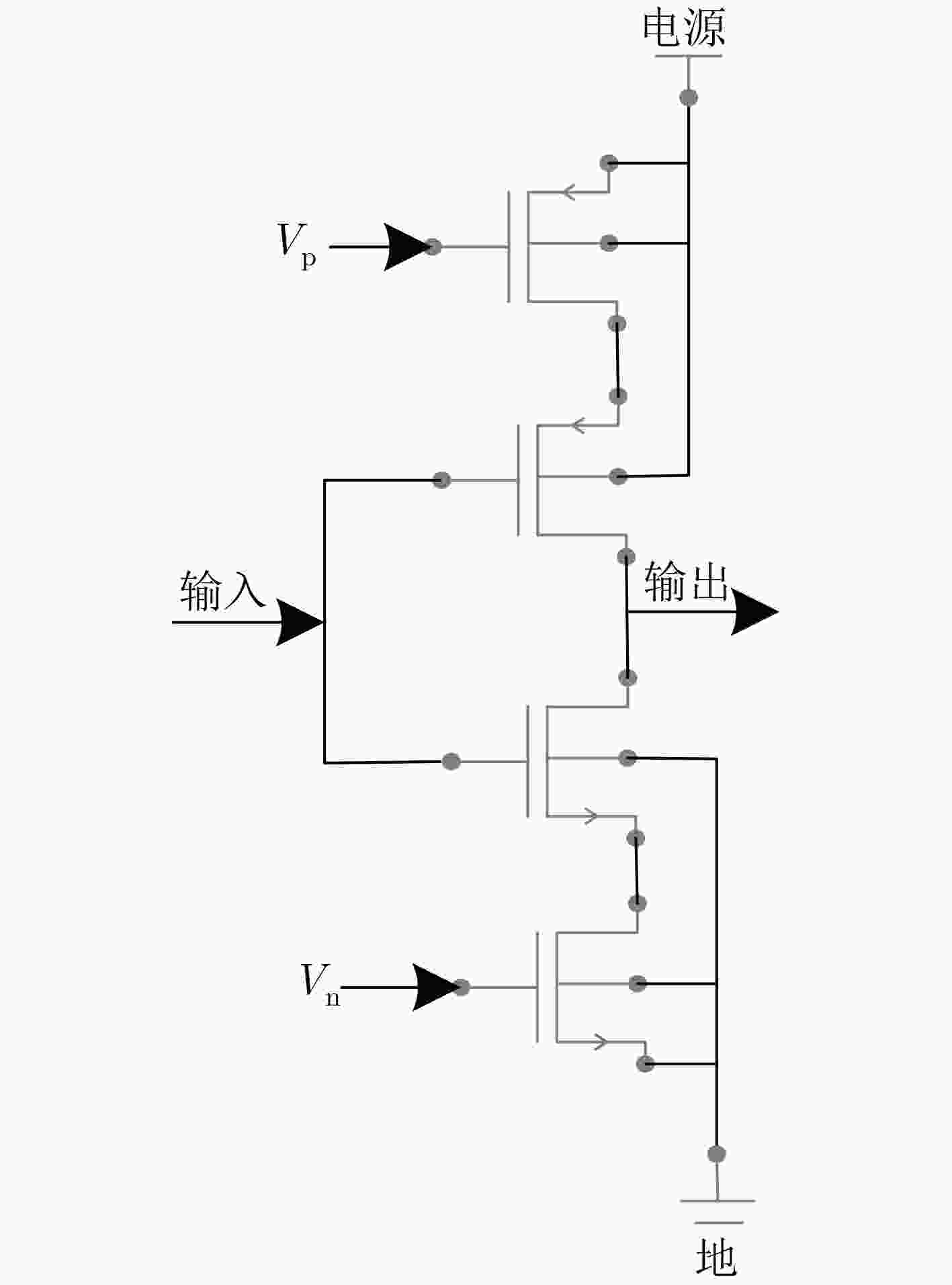

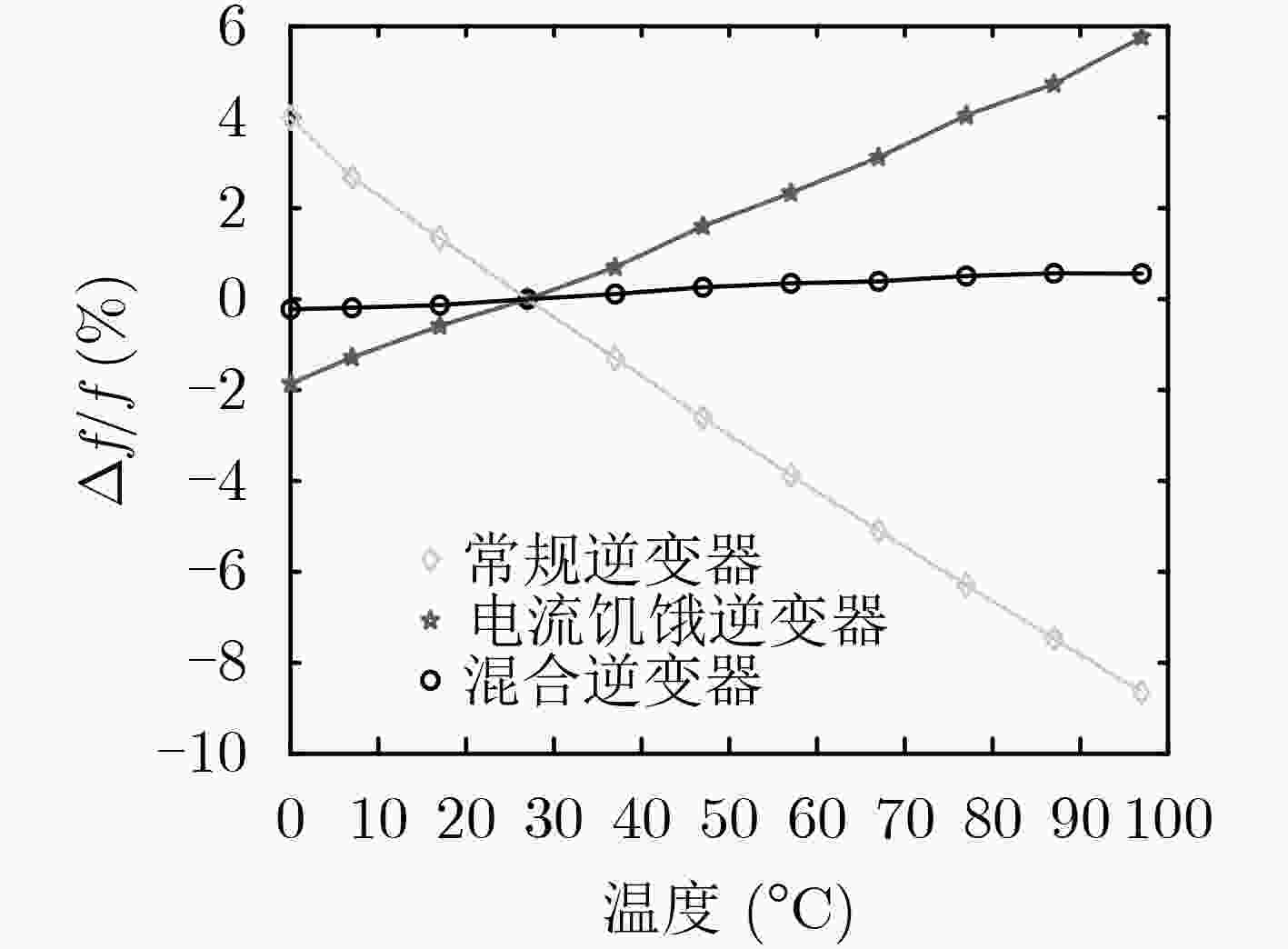

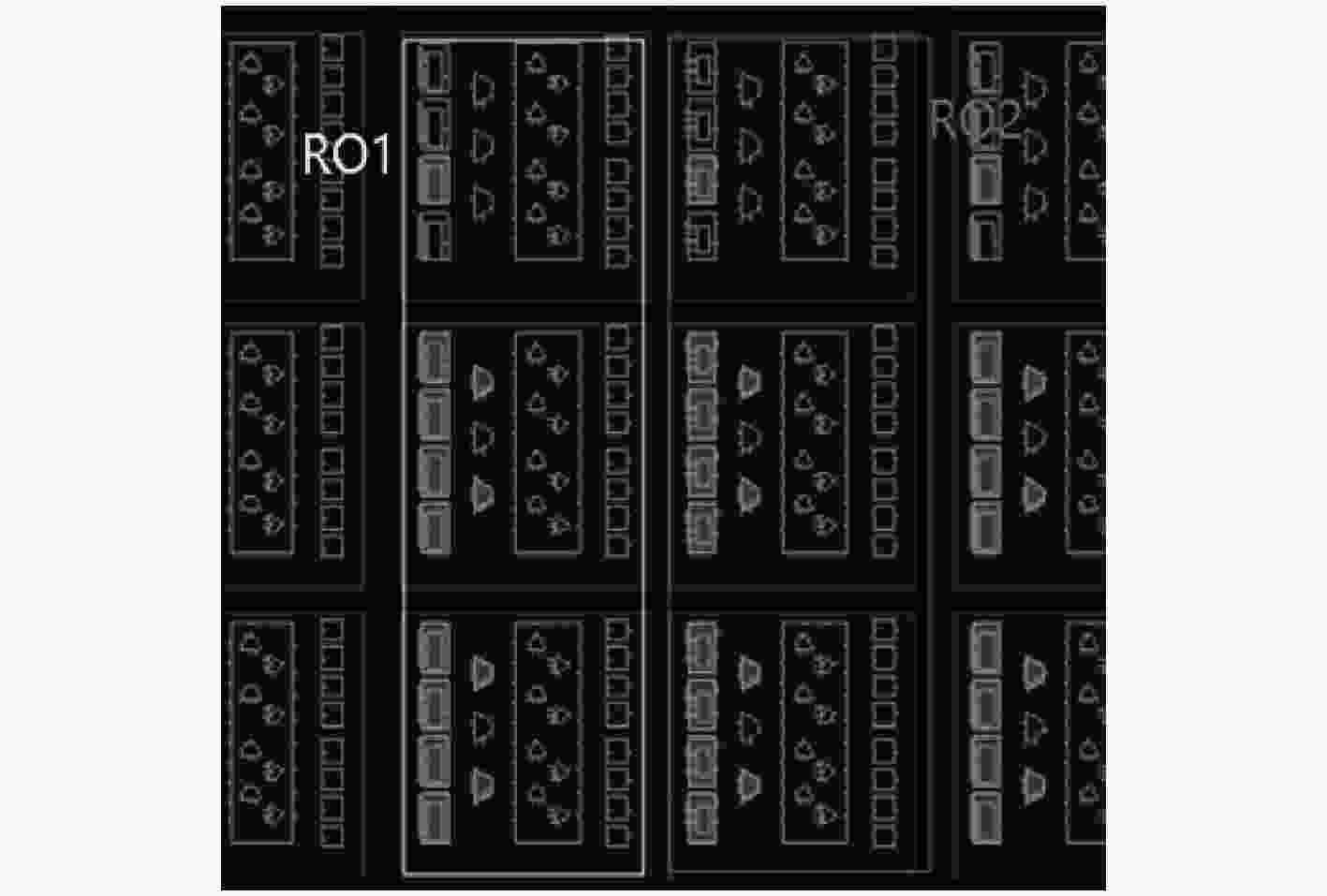

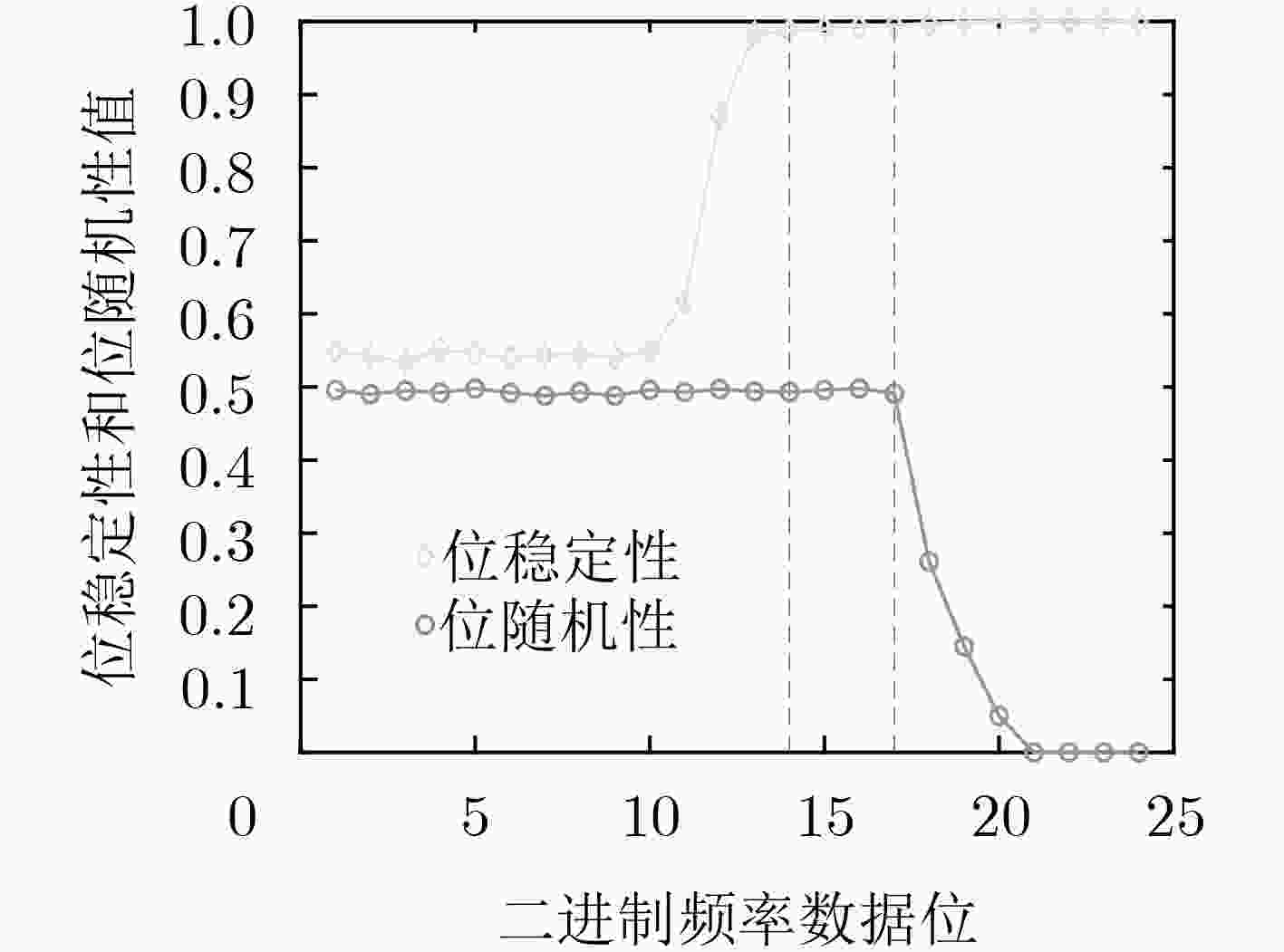

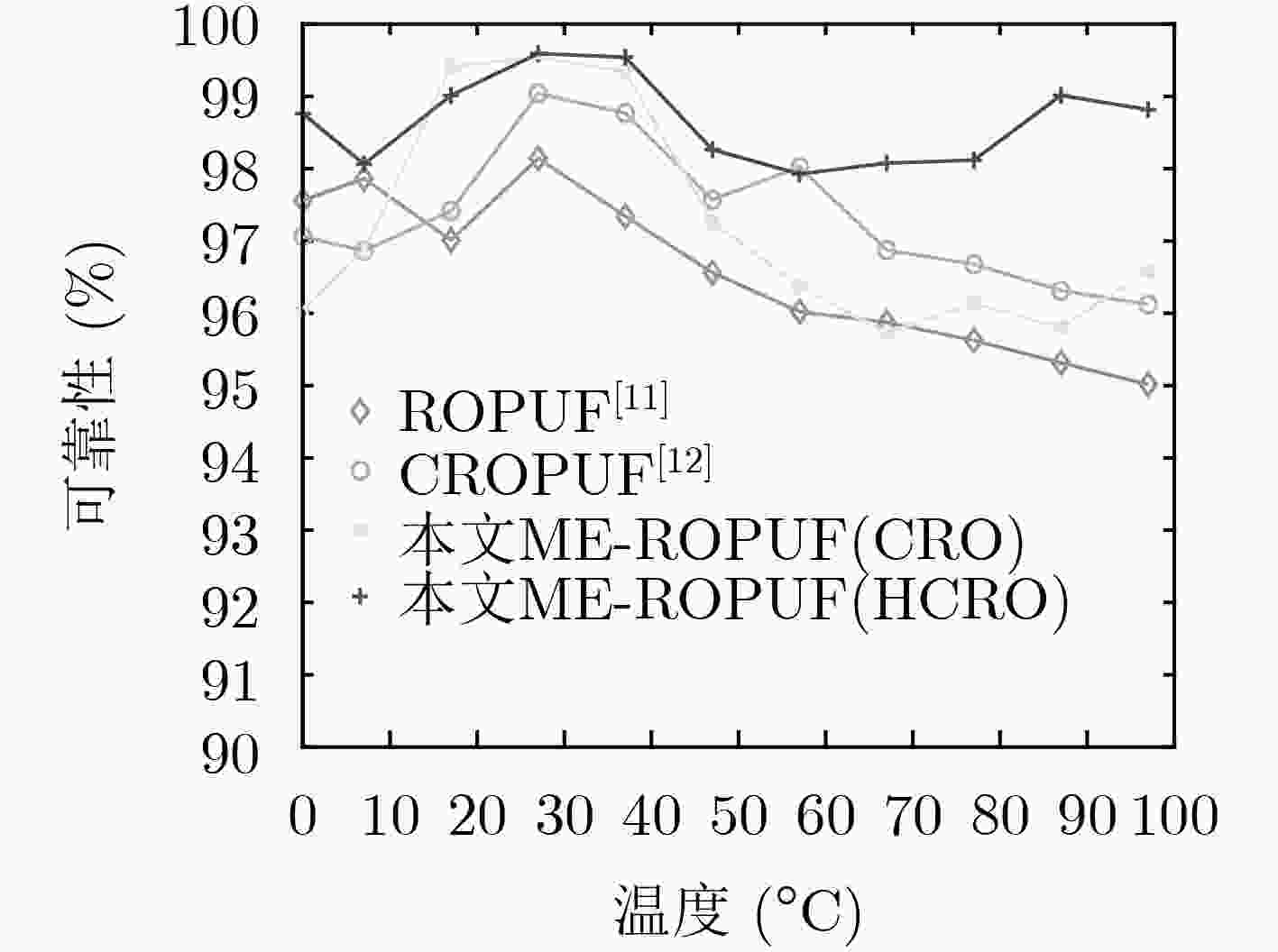

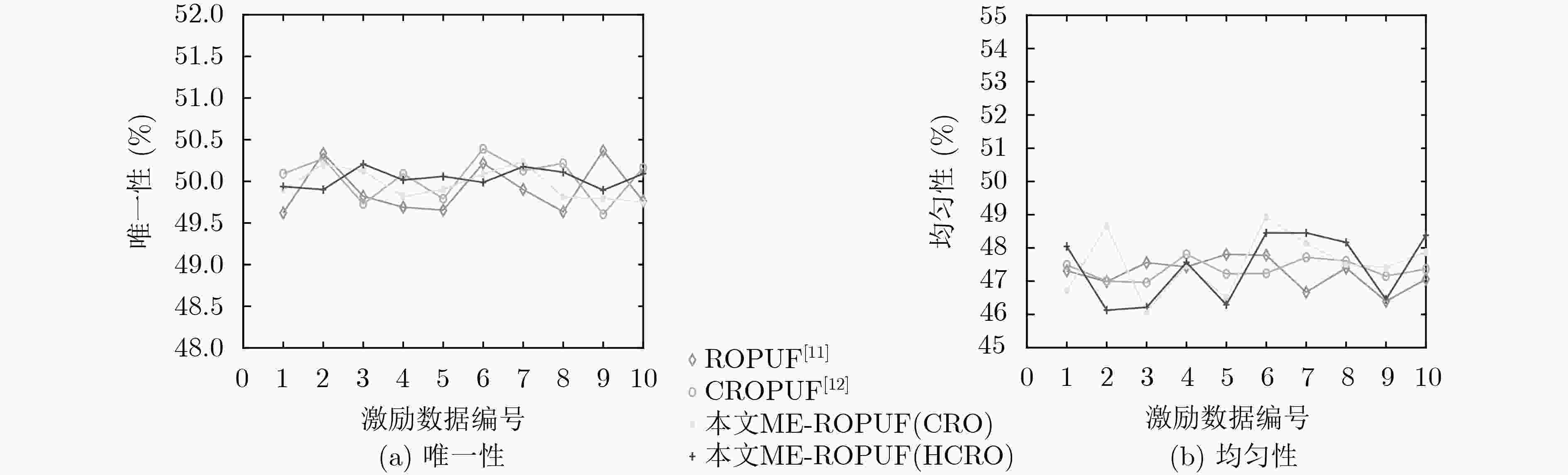

针对传统物理不可克隆函数(PUF)产生信息熵少、易受环境因素干扰等问题,该文设计一种产生多位稳定信息熵的PUF方案。该方案通过对FPGA上环形震荡器所产生频率数据的分析,从每个震荡环中提取能够代表震荡环特性的特征位作为信息熵。通过对逆变器温度特性的研究,利用电流饥饿逆变器和常规逆变器组成新的震荡环来降低温度对产生的信息熵的可靠性的影响。通过Cadence IC仿真和进行赛灵思zynq 7000系列FPGA开发平台上的实验,结果表明改进的PUF结构使用相同数量的震荡环产生更多的信息熵,并且其可靠性、唯一性均得到提升。

Abstract:Considering the problem of information entropy being low and easily disturbed by environmental factors in the traditional Physical Unclonable Function (PUF), a PUF scheme is designed to generate multiple stable information entropy. By analyzing the frequency data generated by the ring oscillator on the FPGA, the feature bits representing the characteristics of the ring are extracted from each ring as information entropy. By studying the temperature characteristics of the inverter, a new oscillating ring is formed by the current hungry inverter and the conventional inverter to reduce the influence of temperature on the reliability of the generated information entropy. Through Cadence IC simulation and experiments on zynq7000 series FPGA development platform, the results show that the improved PUF structure can generate more information entropy with the same number of oscillatory rings, and its reliability and uniqueness are improved.

-

Key words:

- FPGA /

- Physically Unclonable Function (PUF) /

- Ring oscillator /

- Information entropy /

- Inverter

-

表 1 预选区域性能指标

预选区域 (13, 17) (14, 17) (15, 17) (16, 17) (13, 16) (14, 16) (15, 16) (13, 15) (14, 15) ${S_{{\rm{puf}}}}$ 0.963 0.989 0.986 0.991 0.974 0.982 0.990 0.979 0.981 ${U_{_{{\rm{puf}}}}}$ 0.474 0.492 0.488 0.489 0.482 0.486 0.485 0.487 0.491 ${R_{_{{\rm{puf}}}}}$ 0.464 0.474 0.485 0.476 0.478 0.489 0.481 0.492 0.486 ${V_{_{{\rm{puf}}}}}$ 0.719 0.741 0.737 0.740 0.728 0.734 0.738 0.733 0.736 -

SAHOO S R, KUMAR K S, and MAHAPATRA K. A novel current controlled configurable RO PUF with improved security metrics[J]. Integration, 2017, 58: 401–410. doi: 10.1016/j.vlsi.2016.11.005 SANKARAN S, SHIVSHANKAR S, NIMMY K, et al. LHPUF: Lightweight hybrid PUF for enhanced security in internet of things[C]. 2018 IEEE International Symposium on Smart Electronic Systems (iSES) (Formerly iNiS), Hyderabad, India, 2018: 175–178. doi: 10.1109/iSES.2018.00066. GASSEND B, CLARKE D, VAN DIJK M, et al. Silicon physical random functions[C]. The 9th ACM Conference on Computer and Communications Security, Washington, USA, 2002. doi: 10.1145/586110.586132. 张跃军, 王佳伟, 潘钊, 等. 基于正交混淆的多硬件IP核安全防护设计[J]. 电子与信息学报, 2019, 41(8): 1847–1854. doi: 10.11999/JEIT180898ZHANG Yuejun, WANG Jiawei, PAN Zhao, et al. Hardware security for multi IPs protection based on orthogonal obfuscation[J]. Journal of Electronics &Information Technology, 2019, 41(8): 1847–1854. doi: 10.11999/JEIT180898 GAO Yansong, SU Yang, YANG Wei, et al. Building secure SRAM PUF key generators on resource constrained devices[C]. 2019 IEEE International Conference on Pervasive Computing and Communications Workshops (PerCom Workshops), Kyoto, Japan, 2019: 912–917. doi: 10.1109/PERCOMW.2019.8730781. KUMAR A, MISHRA R S, and KASHWAN K R. Challenge-response generation using RO-PUF with reduced hardware[C]. 2016 International Conference on Advances in Computing, Communications and Informatics (ICACCI), Jaipur, India, 2016: 1305–1308. doi: 10.1109/ICACCI.2016.7732227. SU Ying, HOLLEMAN J, OTIS B P, et al. A digital 1.6 pJ/bit chip identification circuit using process variations[J]. IEEE Journal of Solid-State Circuits, 2008, 43(1): 69–77. doi: 10.1109/JSSC.2007.910961 KUMAR S S, GUAJARDO J, MAES R, et al. Extended abstract: The butterfly PUF protecting IP on every FPGA[C]. 2008 IEEE International Workshop on Hardware-Oriented Security and Trust, Anaheim, USA, 2008: 67–70. doi: 10.1109/HST.2008.4559053. LEE J W, LIM D, GASSEND B, et al. A technique to build a secret key in integrated circuits for identification and authentication applications[C]. 2004 Symposium on VLSI Circuits. Digest of Technical Papers (IEEE Cat. No. 04CH37525), Honolulu, USA, 2004: 176–179. doi: 10.1109/VLSIC.2004.1346548. LIM D, LEE J W, GASSEND B, et al. Extracting secret keys from integrated circuits[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2005, 13(10): 1200–1205. doi: 10.1109/TVLSI.2005.859470 SUH G E and DEVADAS S. Physical unclonable functions for device authentication and secret key generation[C]. The 44th ACM/IEEE Design Automation Conference, San Diego, USA, 2007: 9–14. MAITI A and SCHAUMONT P. Improved ring oscillator PUF: An FPGA-friendly secure primitive[J]. Journal of Cryptology, 2011, 24(2): 375–397. doi: 10.1007/s00145-010-9088-4 CHEN B and WILLEMS F M J. Secret key generation over biased physical unclonable functions with polar codes[J]. IEEE Internet of Things Journal, 2019, 6(1): 435–445. doi: 10.1109/JIOT.2018.2864594 SUZUKI D and SHIMIZU K. The glitch PUF: A new Delay-PUF architecture exploiting glitch shapes[C]. The 12th International Workshop Cryptographic Hardware and Embedded Systems, Santa Barbara, USA, 2010: 366–382. doi: 10.1007/978-3-642-15031-9_25. USMANI M A, KESHAVARZ S, MATTHEWS E, et al. Efficient PUF-Based key generation in FPGAs using per-device configuration[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2019, 27(2): 364–375. doi: 10.1109/TVLSI.2018.2877438 CAO Yuan, ZHANG Le, CHEN Shoushun, et al. A low-power hybrid RO PUF with improved thermal stability for lightweight applications[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2015, 34(7): 1143–1147. doi: 10.1109/tcad.2015.2424955 LIU Weiqiang, YU Yifei, WANG Chenghua, et al. RO PUF design in FPGAs with new comparison strategies[C]. 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 2015: 77–80. doi: 10.1109/ISCAS.2015.7168574. 徐金甫, 吴缙. 一种基于动态环形振荡器物理不可克隆函数统计模型的频率排序算法[J]. 电子与信息学报, 2019, 41(3): 717–724. doi: 10.11999/JEIT180405XU Jinfu and WU Jin. Frequency sorting algorithm based on dynamic ring oscillator physical unclonable function statistical model[J]. Journal of Electronics &Information Technology, 2019, 41(3): 717–724. doi: 10.11999/JEIT180405 KUMAR R, PATIL V C, and KUNDU S. On design of temperature invariant physically unclonable functions based on ring oscillators[C]. 2012 IEEE Computer Society Annual Symposium on VLSI, Amherst, USA, 2012: 165–170. doi: 10.1109/ISVLSI.2012.66. SOCHER E, BEER S M, and NEMIROVSKY Y. Temperature sensitivity of SOI-CMOS transistors for use in uncooled thermal sensing[J]. IEEE Transactions on Electron Devices, 2005, 52(12): 2784–2790. doi: 10.1109/TED.2005.859664 KODÝTEK F, LÓRENCZ R, and BUČEK J. Improved ring oscillator PUF on FPGA and its properties[J]. Microprocessors and Microsystems, 2016, 47: 55–63. doi: 10.1016/j.micpro.2016.02.005 -

下载:

下载:

下载:

下载: