Determination and Properties Analysis of a Cubic Polynomial Chaotic Map

-

摘要:

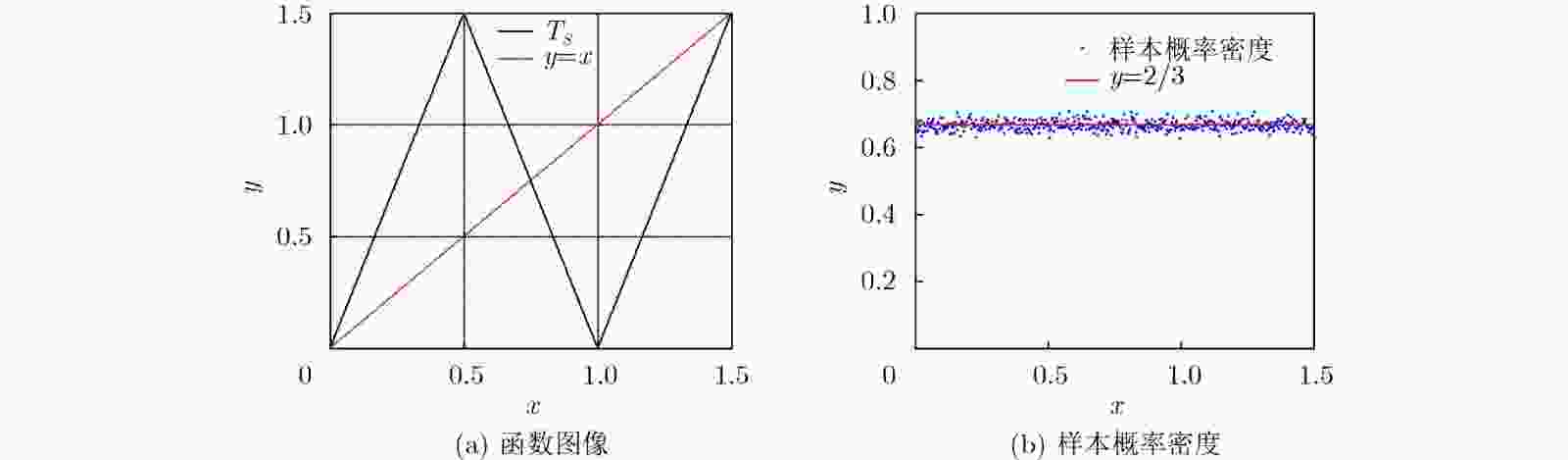

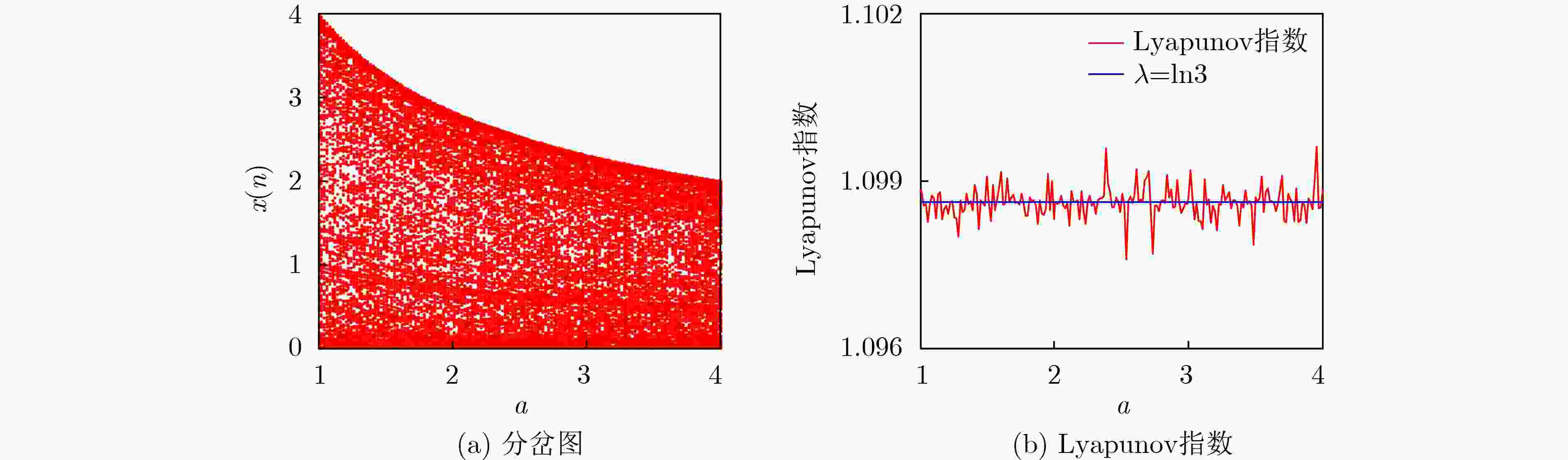

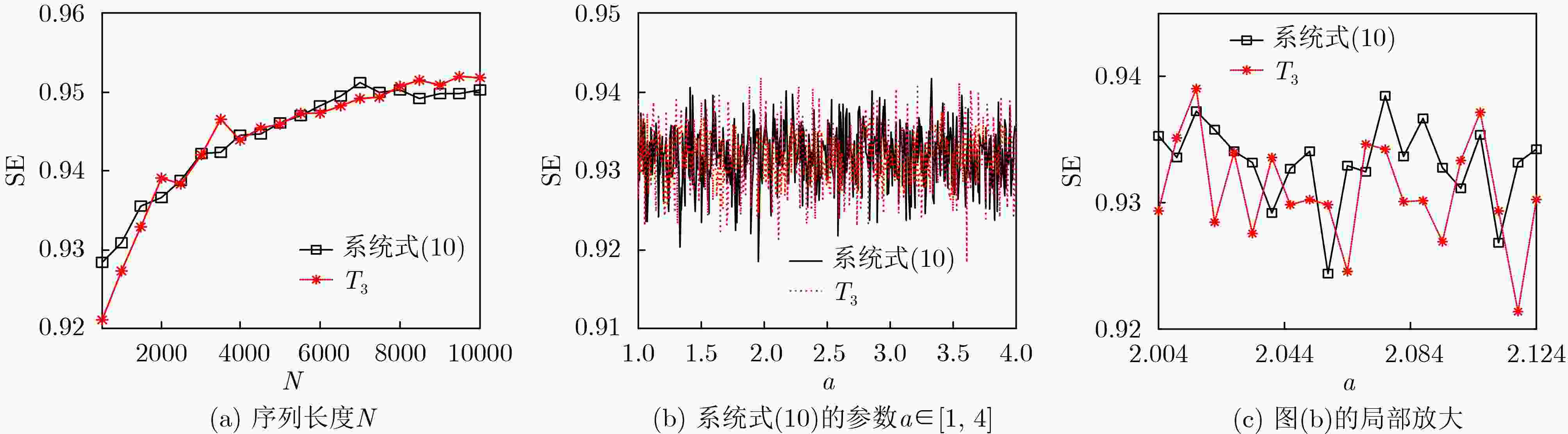

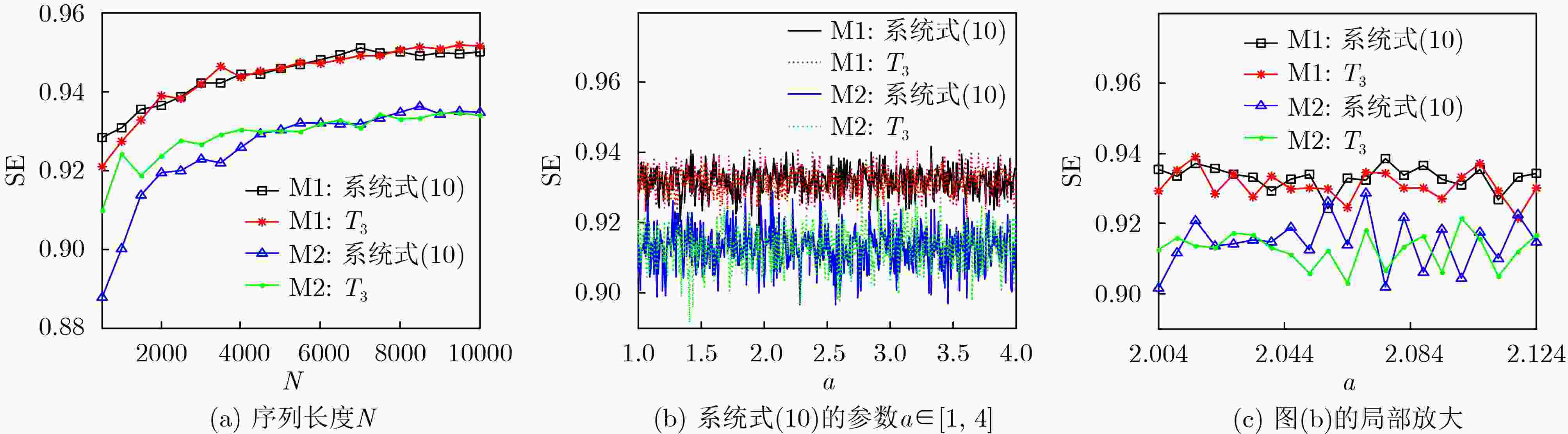

该文给出了一般3次多项式映射与分段线性混沌映射拓扑共轭的充分条件,从而间接地给出了一般3次多项式成为混沌系统的充分条件。进一步对拓扑共轭的分段线性映射和多项式映射的均匀性、结构复杂性和随机性进行了分析,结果显示分段线性映射的均匀性优于多项式映射,多项式映射的随机性优于分段线性映射,在结构复杂性方面,二者没有显著差异,但量化方法对二者的结构复杂性影响显著。

Abstract:This paper provides the sufficient conditions for topological conjugation between the general cubic polynomial maps and a piecewise linear chaotic map, then provides indirectly the sufficient conditions that make the cubic polynomial maps be chaotic. This paper analyzes further the uniformity, structural complexity and randomness of the piecewise linear map and cubic polynomial maps of topological conjugation. The results show that the uniformity of the piecewise linear map is better than the polynomial maps while the randomness of the polynomial maps is superior to the piecewise linear map. As for the structural complexity, there is no significant difference between the two kinds of systems, but it should be noted that the quantitative method makes a significant impact on the structure complexity of the systems.

-

Key words:

- Chaotic system /

- Polynomial maps /

- Topological conjugation /

- Complexity /

- Randomness

-

表 1 NIST SP800-22检测结果

序号 测试项 基于系统式(10)的PRNG 基于系统式(2)的PRNG 通过率 ${\rm{UP}}$值 结果 通过率 ${\rm{UP}}$值 结果 1 频率 0.9920 0.401199 通过 0.9880 0.890582 通过 2 块内频率 0.9880 0.275709 通过 0.6940 <10–4 失败 3 累积和1) 0.9930 0.157251 通过 0.9860 0.358641 通过 4 游程 0.9900 0.010834 通过 0.9850 0.741918 通过 5 块内最长游程 0.9870 0.818343 通过 0.0040 <10–4 失败 6 二元矩阵秩 0.9870 0.378705 通过 0.9880 0.520102 通过 7 离散傅里叶变换 0.9830 0.067300 通过 0.8490 <10–4 失败 8 非重叠模块匹配1) 0.9810 0.759756 通过 0.2950 <10–4 失败 9 重叠模块统计 0.9850 0.597620 通过 0.0600 <10–4 失败 10 全局通用统计 0.9940 0.289667 通过 0.9910 <10–4 失败 11 近似熵 0.9930 0.133404 通过 0.0000 <10–4 失败 12 随机偏移1) 0.9875 0.482338 通过 0.9806 0.083979 通过 13 随机偏移变量1) 0.9860 0.196836 通过 0.9838 0.592833 通过 14 序列1) 0.9840 0.775337 通过 0.0000 <10–4 失败 15 线性复杂度 0.9900 0.572847 通过 0.9910 0.811080 通过 测试项1):该测试项包含几个子模块,此处列出了其中最差的结果。

黑体表示通过率或${\rm{UP}}$值不在接受范围内,即未通过检测。 -

LI T Y and YORKE J A. Period three implies chaos[J]. The American Mathematical Monthly, 1975, 82(10): 985–992. doi: 10.2307/2318254 YANG Xiuping, MIN Lequan, and WANG Xue. A cubic map chaos criterion theorem with applications in generalized synchronization based pseudorandom number generator and image encryption[J]. Chaos: An Interdisciplinary Journal of Nonlinear Science, 2015, 25(5): 053104. doi: 10.1063/1.4917380 王传福, 丁群. 基于混沌系统的SM4密钥扩展算法[J]. 物理学报, 2017, 66(2): 020504. doi: 10.7498/aps.66.020504WANG Chuanfu and DING Qun. SM4 key scheme algorithm based on chaotic system[J]. Acta Physica Sinica, 2017, 66(2): 020504. doi: 10.7498/aps.66.020504 LIN Zhuosheng, YU Simin, FENG Xiutao, et al. Cryptanalysis of a chaotic stream cipher and its improved scheme[J]. International Journal of Bifurcation and Chaos, 2018, 28(7): 1850086. doi: 10.1142/S0218127418500864 XU Zhengguang, TIAN Qing, and TIAN Li. Theorem to generate independently and uniformly distributed chaotic key stream via topologically conjugated maps of tent map[J]. Mathematical Problems in Engineering, 2012, 2012: 619257. doi: 10.1155/2012/619257 DASTGHEIB M A and FARHANG M. A digital pseudo-random number generator based on sawtooth chaotic map with a guaranteed enhanced period[J]. Nonlinear Dynamics, 2017, 89(4): 2957–2966. doi: 10.1007/s11071-017-3638-3 梁涤青, 陈志刚, 邓小鸿. 基于小波包能量熵的混沌序列复杂度分析[J]. 电子学报, 2015, 43(10): 1971–1977. doi: 10.3969/j.issn.0372-2112.2015.10.014LIANG Diqing, CHEN Zhigang, and DENG Xiaohong. Analysis of chaotic sequence complexity based on wavelet packet energy entropy[J]. Acta Electronica Sinica, 2015, 43(10): 1971–1977. doi: 10.3969/j.issn.0372-2112.2015.10.014 MURILLO-ESCOBAR M A, CRUZ-HERNÁNDEZ C, CARDOZA-AVENDAÑO L, et al. A novel pseudorandom number generator based on pseudorandomly enhanced logistic map[J]. Nonlinear Dynamics, 2017, 87: 407–425. doi: 10.1007/s11071-016-3051-3 臧鸿雁, 黄慧芳, 柴宏玉. 一类2次多项式混沌系统的均匀化方法研究[J]. 电子与信息学报, 2019, 41(7): 1618–1624. doi: 10.11999/JEIT180735ZANG Hongyan, HUANG Huifang, and CHAI Hongyu. Homogenization method for the quadratic polynomial chaotic system[J]. Journal of Electronics &Information Technology, 2019, 41(7): 1618–1624. doi: 10.11999/JEIT180735 臧鸿雁, 柴宏玉. 一个二次多项式混沌系统的均匀化及其熵分析[J]. 物理学报, 2016, 65(3): 030504. doi: 10.7498/aps.65.030504ZANG Hongyan and CHAI Hongyu. Homogenization and entropy analysis of a quadratic polynomial chaotic system[J]. Acta Physica Sinica, 2016, 65(3): 030504. doi: 10.7498/aps.65.030504 徐正光, 田清, 田立. 一类可以产生独立同分布密钥流的混沌系统[J]. 物理学报, 2013, 62(13): 120501. doi: 10.7498/aps.62.120501XU Zhengguang, TIAN Qing, and TIAN Li. A class of topologically conjugated chaotic maps of tent map to generate independently and uniformly distributed chaotic key stream[J]. Acta Physica Sinica, 2013, 62(13): 120501. doi: 10.7498/aps.62.120501 LIU Lingfeng, MIAO Suoxia, HU Hanping, et al. N-phase logistic chaotic sequence and its application for image encryption[J]. IET Signal Processing, 2016, 10(9): 1096–1104. doi: 10.1049/iet-spr.2015.0522 TONG Xiaojun, CUI Minggen, and WANG Zhu. A new feedback image encryption scheme based on perturbation with dynamical compound chaotic sequence cipher generator[J]. Optics Communications, 2009, 282(14): 2722–2728. doi: 10.1016/j.optcom.2009.03.075 TONG Xiaojun, ZHANG Miao, WANG Zhu, et al. A image encryption scheme based on dynamical perturbation and linear feedback shift register[J]. Nonlinear Dynamics, 2014, 78(3): 2277–2291. doi: 10.1007/s11071-014-1564-1 HAO Bolin. Starting with Parabola: An Introduction to Chaotic Dynamics[M]. 2nd ed. Beijing: Peking University Press, 2013: 114–118. 孙克辉, 贺少波, 何毅, 等. 混沌伪随机序列的谱熵复杂性分析[J]. 物理学报, 2013, 62(1): 010501. doi: 10.7498/aps.62.010501SUN Kehui, HE Shaobo, HE Yi, et al. Complexity analysis of chaotic pseudo-random sequences based on spectral entropy algorithm[J]. Acta Physica Sinica, 2013, 62(1): 010501. doi: 10.7498/aps.62.010501 RUKHIN A, SOTO J, NECHVATAL J, et al. Special Publication 800-22 A statistical test suite for random and pseudorandom number generators for cryptographic applications[S]. U. S. Department of Commerce: National Institute of Standards and Technology, 2010. -

下载:

下载:

下载:

下载: