|

CHUA L. Memristor-The missing circuit element[J]. IEEE Transactions on Circuit Theory, 1971, 18(5): 507–519. doi: 10.1109/TCT.1971.1083337

|

|

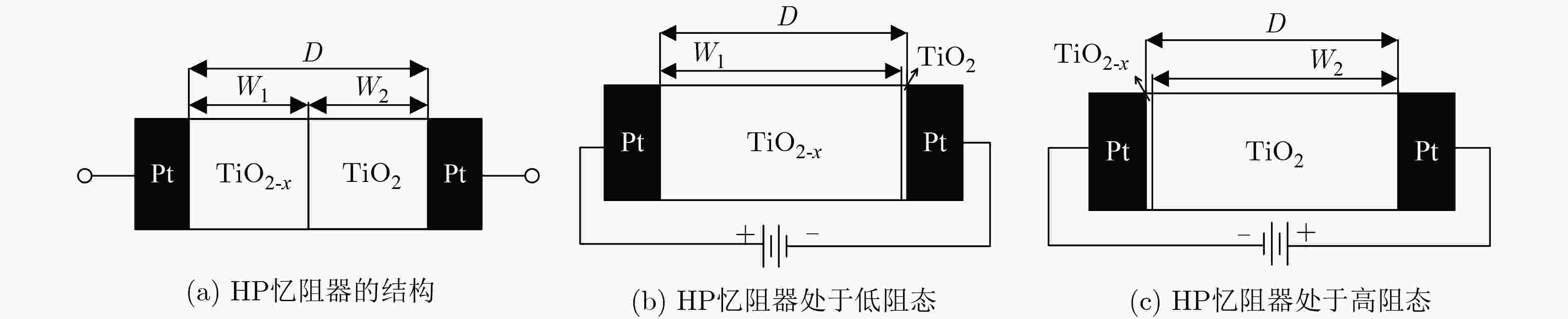

STRUKOV D B, SNIDER G S, STEWART D R, et al. The missing memristor found[J]. Nature, 2009, 453(7191): 80–83. doi: 10.1038/nature06932

|

|

PAL S, GUPTA V, KI W, et al. Design and development of memristor-based RRAM[J]. IET Circuits, Devices & Systems, 2019, 13(4): 548–557. doi: 10.1049/iet-cds.2018.5388

|

|

ZHANG Mengsi and WANG Dongshu. Robust dissipativity analysis for delayed memristor-based inertial neural network[J]. Neurocomputing, 2019, 366: 340–351. doi: 10.1016/j.neucom.2019.08.004

|

|

XIE Lei, CAI Hao, WANG Chao, et al. Towards an automated design flow for memristor based VLSI circuits[J]. Integration, 2020, 70: 21–31. doi: 10.1016/j.vlsi.2019.09.009

|

|

MIN Xiaotao, WANG Xiaoyuan, ZHOU Pengfei, et al. An optimized memristor-based hyperchaotic system with controlled hidden attractors[J]. IEEE Access, 2019, 7: 124641–124646. doi: 10.1109/ACCESS.2019.2938183

|

|

LASTRAS-MONTAÑO M A and CHENG K. Resistive random-access memory based on ratioed memristors[J]. Nature Electronics, 2018, 1(8): 466–472. doi: 10.1038/s41928-018-0115-z

|

|

PAL S, BOSE S, KI W H, et al. Design of power- and variability-aware nonvolatile RRAM cell using memristor as a memory element[J]. IEEE Journal of the Electron Devices Society, 2019, 7: 701–709. doi: 10.1109/JEDS.2019.2928830

|

|

SHARIF K F and BISWAS S N. 6 Transistors and 1 memristor based memory cell[J]. International Journal of Reconfigurable and Embedded Systems, 2020, 9(1): 42–51. doi: 10.11591/ijres.v9.i1.pp42-51

|

|

BISWAS B R and HARUN-UR-RASHID A B M. A data erasing writing technique based 1t1m quaternary memory circuit design[C]. The 10th International Conference on Electrical and Computer Engineering, Dhaka, Bangladesh, 2018: 317–320. doi: 10.1109/ICECE.2018.8636774.

|

|

SAH M P, KIM H, and CHUA L O. Brains are made of memristors[J]. IEEE Circuits and Systems Magazine, 2014, 14(1): 12–36. doi: 10.1109/MCAS.2013.2296414

|

|

LINN E, ROSEZIN R, TAPPERTZHOFEN S, et al. Beyond von Neumann-logic operations in passive crossbar arrays alongside memory operations[J]. Nanotechnology, 2012, 23(30): 305205. doi: 10.1088/0957-4484/23/30/305205

|

|

GHOSE S, BOROUMAND A, KIM J S, et al. Processing-in-memory: A workload-driven perspective[J]. IBM Journal of Research and Development, 2019, 63(6): 3: 1-3: 19. doi: 10.1147/JRD.2019.2934048.

|

|

WHITEHEAD A N and RUSSELL B. Principia Mathematica[M]. Cambridge: Cambridge University Press, 1912.

|

|

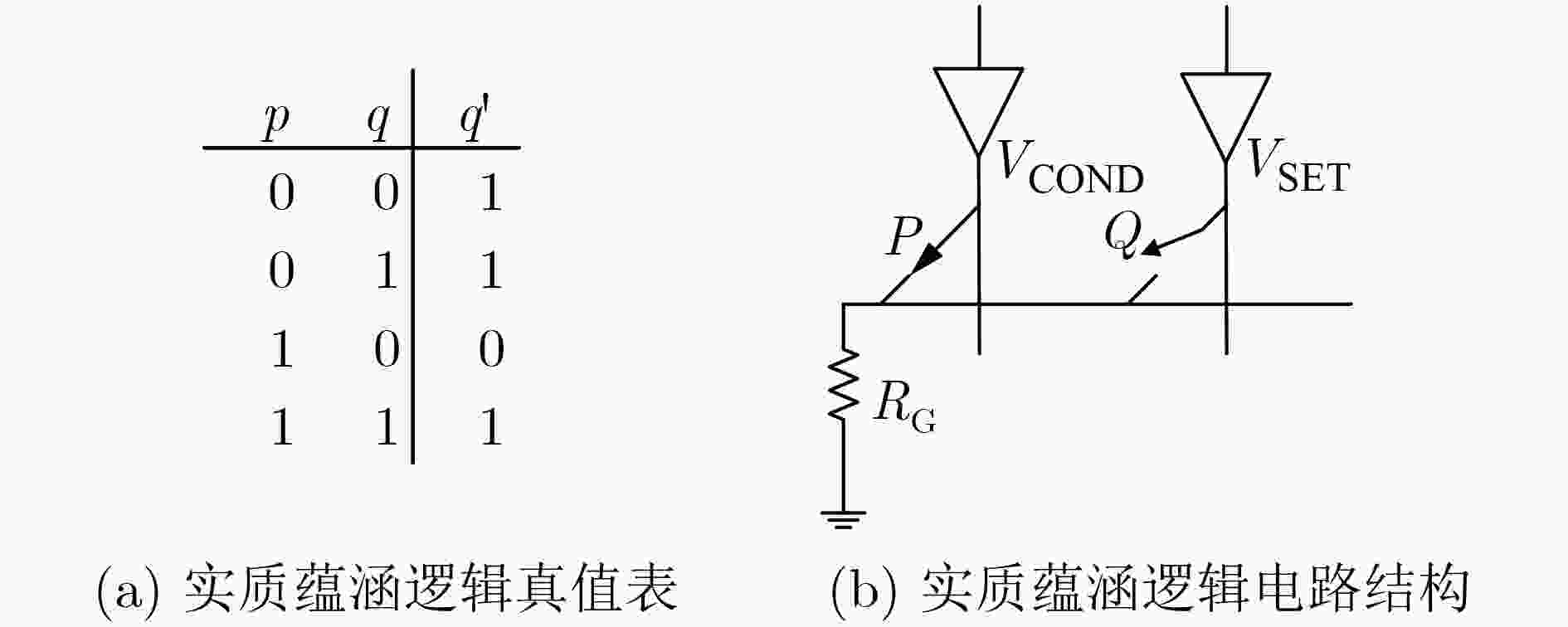

KUEKES P. Material implication: Digital logic with memristors[C]. The Memristor and Memristive Systems Symposium, Berkeley, USA, 2008.

|

|

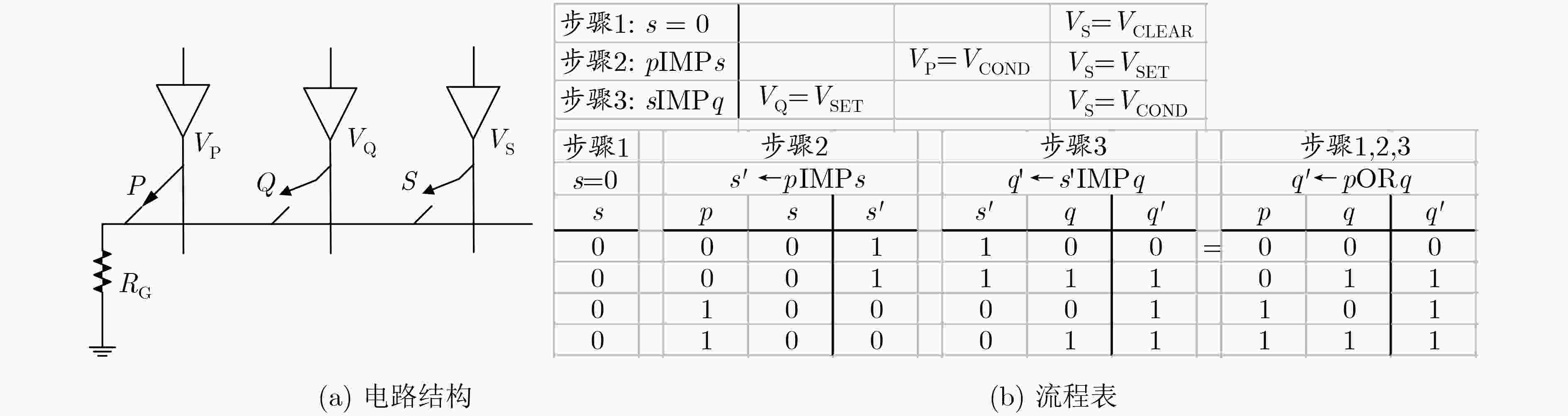

BORGHETTI J, SNIDER G S, KUEKES P J, et al. ‘Memristive’ switches enable ‘Stateful’ logic operations via material implication[J]. Nature, 2010, 464(7290): 873–876. doi: 10.1038/nature08940

|

|

LEHTONEN E, POIKONEN J, and LAIHO M. Implication logic synthesis methods for memristors[C]. 2012 IEEE International Symposium on Circuits and Systems, Seoul, South Korea, 2012: 2441–2444. doi: 10.1109/ISCAS.2012.6271792.

|

|

LEHTONEN E, TISSARI J, POIKONEN J, et al. A cellular computing architecture for parallel memristive stateful logic[J]. Microelectronics Journal, 2014, 45(11): 1438–1449. doi: 10.1016/j.mejo.2014.09.005

|

|

MANE P, TALATI N, RISWADKAR A, et al. Implementation of NOR logic based on material implication on CMOL FPGA architecture[C]. The 28th International Conference on VLSI Design, Bangalore, India, 2015: 523–528. doi: 10.1109/VLSID.2015.94.

|

|

YANG Yuanfan, MATHEW J, PONTARELLI S, et al. Complementary resistive switch-based arithmetic logic implementations using material implication[J]. IEEE Transactions on Nanotechnology, 2016, 15(1): 94–108. doi: 10.1109/TNANO.2015.2504841

|

|

CHEN Qiao, WANG Xiaoping, WAN Haibo, et al. A logic circuit design for perfecting memristor-based material implication[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2017, 36(2): 279–284. doi: 10.1109/TCAD.2016.2578881

|

|

MANE P, TALATI N, RISWADKAR A, et al. Reconfiguration on nanocrossbar using material implication[J]. Sādhanā, 2017, 42(1): 33–44. doi: 10.1007/s12046-016-0582-8

|

|

GUCKERT L and SWARTZLANDER E E. MAD gates-memristor logic design using driver circuitry[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2017, 64(2): 171–175. doi: 10.1109/TCSII.2016.2551554

|

|

GUCKERT L and SWARTZLANDER E E. Optimized memristor-based multipliers[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2017, 64(2): 373–385. doi: 10.1109/TCSI.2016.2606433

|

|

REVANNA N and SWARTZLANDER E E. Memristor based high fan-out logic gates[C]. 2016 IEEE Dallas Circuits and Systems Conference, Arlington, USA, 2016: 1–4. doi: 10.1109/DCAS.2016.7791136.

|

|

MARRANGHELLO F S, CALLEGARO V, MARTINS M G A, et al. Improved logic synthesis for memristive stateful logic using multi-memristor implication[C]. 2015 IEEE International Symposium on Circuits and Systems, Lisbon, Portugal, 2015: 181–184. doi: 10.1109/ISCAS.2015.7168600.

|

|

MARRANGHELLO F S, CALLEGARO V, MARTINS M G A, et al. Factored forms for memristive material implication stateful logic[J]. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2015, 5(2): 267–278. doi: 10.1109/JETCAS.2015.2426511

|

|

MARRANGHELLO F S, CALLEGARO V, REIS A I, et al. SOP based logic synthesis for memristive IMPLY stateful logic[C]. The 33rd IEEE International Conference on Computer Design, New York, USA, 2015: 228–235. doi: 10.1109/ICCD.2015.7357108.

|

|

LALCHHANDAMA F, SAPUI B G, and DATTA K. An improved approach for the synthesis of Boolean functions using memristor based IMPLY and INVERSE-IMPLY gates[C]. 2016 IEEE Computer Society Annual Symposium on VLSI, Pittsburgh, USA, 2016: 319–324. doi: 10.1109/ISVLSI.2016.61.

|

|

WANG Xiaoxiao, TAN R, and PERKOWSKI M. Synthesis of memristive circuits based on stateful IMPLY gates using an evolutionary algorithm with a correction function[C]. 2016 IEEE/ACM International Symposium on Nanoscale Architectures, Beijing, China, 2016: 97–102. doi: 10.1145/2950067.2950087.

|

|

MARRANGHELLO F S, CALLEGARO V, REIS A I, et al. Four-level forms for memristive material implication logic[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2019, 27(5): 1228–1232. doi: 10.1109/TVLSI.2019.2890843

|

|

KVATINSKY S, SATAT G, WALD N, et al. Memristor-based material implication (IMPLY) logic: Design principles and methodologies[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22(10): 2054–2066. doi: 10.1109/TVLSI.2013.2282132

|

|

TEIMOORY M, AMIRSOLEIMANI A, AHMADI A, et al. Memristor-based linear feedback shift register based on material implication logic[C]. 2015 European Conference on Circuit Theory and Design, Trondheim, Norway, 2015: 1–4. doi: 10.1109/ECCTD.2015.7300100.

|

|

CHAKRABORTY A and RAHAMAN H. Implementation of combinational circuits via material implication using memristors[C]. 2016 IEEE Distributed Computing, VLSI, Electrical Circuits and Robotics, Mangalore, India, 2016: 67–72. doi: 10.1109/DISCOVER.2016.7806227.

|

|

CHAKRABORTY A, DHARA A, and RAHAMAN H. Design of memristor-based up-down counter using material implication logic[C]. 2016 International Conference on Advances in Computing, Communications and Informatics, Jaipur, India, 2016: 269–274. doi: 10.1109/ICACCI.2016.7732058.

|

|

REVANNA N and SWARTZLANDER E E. Memristor based adder circuit design[C]. The 50th Asilomar Conference on Signals, Systems and Computers, Pacific Grove, USA, 2016: 162–166. doi: 10.1109/ACSSC.2016.7869016.

|

|

BANERJEE A, PAL S, BHATTACHARYYA S, et al. Memristor based modulo multiplier design for (2n – 1) and 2n radix[C]. 2017 Devices for Integrated Circuit, Kalyani, India, 2017: 20–24. doi: 10.1109/DEVIC.2017.8073898.

|

|

HAGHIRI S, NEMATI A, FEIZI S, et al. A memristor based binary multiplier[C]. The 2017 IEEE 30th Canadian Conference on Electrical and Computer Engineering, Windsor, Canada, 2017: 1–4. doi: 10.1109/CCECE.2017.7946783.

|

|

ROHANI S G and TAHERINEJAD N. An improved algorithm for IMPLY logic based memristive full-adder[C]. The 30th IEEE Canadian Conference on Electrical and Computer Engineering, Windsor, Canada, 2017: 1–4. doi: 10.1109/CCECE.2017.7946813.

|

|

HARON A, MAHDZAIR F, LUQMAN A, et al. Implementation of digital equality comparator circuit on memristive memory crossbar array using material implication logic[J]. IOP Conference Series: Materials Science and Engineering, 2018, 341(1): 012025. doi: 10.1088/1757-899X/341/1/012025

|

|

LI Mengting, SUN Wenhao, LU Zhimin, et al. Memristor-based material implication logic design for full adders[C]. The 12th IEEE International Conference on ASIC, Guiyang, China, 2017: 271–274. doi: 10.1109/ASICON.2017.8252465.

|

|

WANG Xiaoping, WU Qian, CHEN Qiao, et al. A novel design for Memristor-based multiplexer via NOT-material implication[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2018, 37(7): 1436–1444. doi: 10.1109/TCAD.2017.2753204

|

|

KARIMI A and REZAI A. Novel design for a memristor-based full adder using a new IMPLY logic approach[J]. Journal of Computational Electronics, 2018, 17(3): 1303–1314. doi: 10.1007/s10825-018-1198-5

|

|

KARIMI A and REZAI A. Novel design for Memristor-based n to 1 multiplexer using new IMPLY logic approach[J]. IET Circuits, Devices & Systems, 2019, 13(5): 647–655. doi: 10.1049/iet-cds.2018.5090

|

|

KVATINSKY S, WALD N, SATAT G, et al. MRL-Memristor ratioed logic[C]. The 13th International Workshop on Cellular Nanoscale Networks and their Applications, Turin, Italy, 2012: 1–6. doi: 10.1109/CNNA.2012.6331426.

|

|

TEIMOORI M, AHMADI A, ALIREZAEE S, et al. A novel hybrid CMOS-memristor logic circuit using Memristor Ratioed Logic[C]. 2016 IEEE Canadian Conference on Electrical and Computer Engineering, Vancouver, Canada, 2016: 1–4. doi: 10.1109/CCECE.2016.7726661.

|

|

TEIMOORY M, AMIRSOLEIMANI A, AHMADI A, et al. A hybrid memristor-CMOS multiplier design based on memristive universal logic gates[C]. The 60th IEEE International Midwest Symposium on Circuits and Systems, Boston, USA, 2017: 1422–1425. doi: 10.1109/MWSCAS.2017.8053199.

|

|

XU Xiaoyan, CUI Xiaole, LUO Mengying, et al. Design of hybrid memristor-MOS XOR and XNOR logic gates[C]. 2017 International Conference on Electron Devices and Solid-State Circuits, Hsinchu, China, 2017: 1–2. doi: 10.1109/EDSSC.2017.8126414.

|

|

LIU Bosheng, WANG Ying, YOU Zhiqiang, et al. A signal degradation reduction method for memristor ratioed logic (MRL) gates[J]. IEICE Electronics Express, 2015, 12(8): 20150062. doi: 10.1587/elex.12.20150062

|

|

MIRZAIE N, ALZAHMI A, SHAMSI H, et al. Three-dimensional pipeline ADC utilizing TSV/design optimization and memristor ratioed logic[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018, 26(12): 2619–2627. doi: 10.1109/TVLSI.2018.2810782

|

|

LIU Gongzhi, ZHENG Lijing, WANG Guangyi, et al. A carry lookahead adder based on hybrid CMOS-memristor logic circuit[J]. IEEE Access, 2019, 7: 43691–43696. doi: 10.1109/ACCESS.2019.2907976

|

|

KVATINSKY S, BELOUSOV D, LIMAN S, et al. MAGIC-Memristor-aided logic[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2014, 61(11): 895–899. doi: 10.1109/TCSII.2014.2357292

|

|

TALATI N, GUPTA S, MANE P, et al. Logic design within memristive memories using memristor-aided loGIC (MAGIC)[J]. IEEE Transactions on Nanotechnology, 2016, 15(4): 635–650. doi: 10.1109/TNANO.2016.2570248

|

|

HUR R B and KVATINSKY S. Memory processing unit for in-memory processing[C]. 2016 IEEE/ACM International Symposium on Nanoscale Architectures, Beijing, China, 2016: 171–172. doi: 10.1145/2950067.2950086.

|

|

THANGKHIEW P L, GHARPINDE R, YADAV D N, et al. Efficient implementation of adder circuits in memristive crossbar array[C]. TENCON 2017-2017 IEEE Region 10 Conference, Penang, Malaysia, 2017: 207–212. doi: 10.1109/TENCON.2017.8227863.

|

|

HUR R B, WALD N, TALATI N, et al. SIMPLE MAGIC: Synthesis and in-memory mapping of logic execution for memristor-aided logic[C]. 2017 IEEE/ACM International Conference on Computer-Aided Design, Irvine, USA, 2017: 225–232.

|

|

HAJ-ALI A, BEN-HUR R, WALD N, et al. Efficient algorithms for in-memory fixed point multiplication using magic[C]. 2018 IEEE International Symposium on Circuits and Systems, Florence, Italy, 2018: 1–5. doi: 10.1109/ISCAS.2018.8351561.

|

|

THANGKHIEW P L, GHARPINDE R, CHOWDHARY P V, et al. Area efficient implementation of ripple carry adder using memristor crossbar arrays[C]. The 11th International Design & Test Symposium, Hammamet, Tunisia, 2016: 142–147. doi: 10.1109/IDT.2016.7843030.

|

|

THANGKHIEW P L and DATTA K. Scalable in-memory mapping of boolean functions in memristive crossbar array using simulated annealing[J]. Journal of Systems Architecture, 2018, 89: 49–59. doi: 10.1016/j.sysarc.2018.07.002

|

|

THANGKHIEW P L, GHARPINDE R, and DATTA K. Efficient mapping of Boolean functions to memristor crossbar using MAGIC NOR gates[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2018, 65(8): 2466–2476. doi: 10.1109/TCSI.2018.2792474

|

|

THANGKHIEW P L and DATTA K. Fast in-memory computation of Boolean functions in memristive crossbar array[C]. The 8th International Symposium on Embedded Computing and System Design, Cochin, India, 2018: 105–109. doi: 10.1109/ISED.2018.8703986.

|

|

WALD N and KVATINSKY S. Understanding the influence of device, circuit and environmental variations on real processing in memristive memory using Memristor Aided Logic[J]. Microelectronics Journal, 2019, 86: 22–33. doi: 10.1016/j.mejo.2019.02.013

|

|

CHAKRABORTY A, SAURABH V, GUPTA P S, et al. In-memory designing of Delay and Toggle flip-flops utilizing Memristor Aided loGIC (MAGIC)[J]. Integration, 2019, 66: 24–34. doi: 10.1016/j.vlsi.2018.12.005

|

|

CHEN Lin, HE Zhong, WANG Xiaoping, et al. Several logic gates extended from magic-memristor-aided logic[C]. The 14th International Symposium on Neural Networks, Hokkaido, Japan, 2017: 170–179. doi: 10.1007/978-3-319-59072-1_21.

|

|

G N M, LALCHHANDAMA F, DATTA K, et al. Modelling and simulation of non-ideal MAGIC NOR Gates on memristor crossbar[C]. The 8th International Symposium on Embedded Computing and System Design, Cochin, India, 2018: 124–128. doi: 10.1109/ISED.2018.8704015.

|

|

WANG Xiaoping, YANG Yuanyuan, CHEN Lin, et al. A non-volatile comparator based on 1T1M crossbar arrays using memristor-aided logic[C]. The IECON 2017-43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 2017: 5685–5689. doi: 10.1109/IECON.2017.8216986.

|

|

BEIU V, QUINTANA J M, and AVEDILLO M J. VLSI implementations of threshold logic-a comprehensive survey[J]. IEEE Transactions on Neural Networks, 2003, 14(5): 1217–1243. doi: 10.1109/TNN.2003.816365

|

|

RAJENDRAN J, MANEM H, KARRI R, et al. Memristor based programmable threshold logic array[C]. 2010 IEEE/ACM International Symposium on Nanoscale Architectures, Anaheim, USA, 2010: 5–10. doi: 10.1109/NANOARCH.2010.5510933.

|

|

GAO Ligang, ALIBART F, and STRUKOV D B. Programmable CMOS/memristor threshold logic[J]. IEEE Transactions on Nanotechnology, 2013, 12(2): 115–119. doi: 10.1109/TNANO.2013.2241075

|

|

XIE Lei. Hybrid threshold-Boolean logic mapped on memristor crossbar[C]. The 12th Conference on Ph.D. Research in Microelectronics and Electronics, Lisbon, Portugal, 2016: 1–4. doi: 10.1109/PRIME.2016.7519462.

|

|

JAMES A P, KUMAR D S, and AJAYAN A. Threshold logic computing: Memristive-cmos circuits for fast fourier transform and vedic multiplication[J]. IEEE Transactions on Very Large scale Integration (VLSI) Systems, 2015, 23(11): 2690–2694. doi: 10.1109/TVLSI.2014.2371857

|

|

MAAN A K and JAMES A P. Voltage controlled memristor threshold logic gates[C]. 2016 IEEE Asia Pacific Conference on Circuits and Systems, Jeju, South Korea, 2016: 376–379. doi: 10.1109/APCCAS.2016.7803980.

|

|

MAAN A K, JAYADEVI D A, and JAMES A P. A survey of memristive threshold logic circuits[J]. IEEE Transactions on Neural Networks and Learning Systems, 2017, 28(8): 1734–1746. doi: 10.1109/TNNLS.2016.2547842

|

|

PAPANDROULIDAKIS G, KHIAT A, SERB A, et al. Metal oxide-enabled reconfigurable memristive threshold logic gates[C]. 2018 IEEE International Symposium on Circuits and Systems, Florence, Italy, 2018: 1–5. doi: 10.1109/ISCAS.2018.8351192.

|

|

MOZAFFARI S N and TRAGOUDAS S. Maximizing the number of threshold logic functions using resistive memory[J]. IEEE Transactions on Nanotechnology, 2018, 17(5): 897–905. doi: 10.1109/TNANO.2018.2822285

|

|

PAPANDROULIDAKIS G, SERB A, KHIAT A, et al. Practical implementation of memristor-based threshold logic gates[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2019, 66(8): 3041–3051. doi: 10.1109/TCSI.2019.2902475

|

|

DANABOINA Y K Y, SAMANTA P, DATTA K, et al. Design and implementation of threshold logic functions using memristors[C]. The 32nd International Conference on VLSI Design and 2019 18th International Conference on Embedded Systems, Delhi, India, 2019: 518–519. doi: 10.1109/VLSID.2019.00115.

|

|

VOURKAS I and SIRAKOULIS G C. A novel design and modeling paradigm for memristor-based crossbar circuits[J]. IEEE Transactions on Nanotechnology, 2012, 11(6): 1151–1159. doi: 10.1109/TNANO.2012.2217153

|

|

VOURKAS I and SIRAKOULIS G C. Memristor-based combinational circuits: A design methodology for encoders/decoders[J]. Microelectronics Journal, 2014, 45(1): 59–70. doi: 10.1016/j.mejo.2013.10.001

|

|

VOURKAS I and SIRAKOULIS G C. Employing threshold‐based behavior and network dynamics for the creation of memristive logic circuits and architectures[J]. Physica Status Solidi (C) , 2015, 12(1/2): 168–174. doi: 10.1002/pssc.201400161

|

|

PAPANDROULIDAKIS G, VOURKAS I, VASILEIADIS N, et al. Boolean logic operations and computing circuits based on memristors[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2014, 61(12): 972–976. doi: 10.1109/TCSII.2014.2357351

|

|

KHALID M and SINGH J. Memristor based unbalanced ternary logic gates[J]. Analog Integrated Circuits and Signal Processing, 2016, 87(3): 399–406. doi: 10.1007/s10470-016-0733-1

|

|

SOLIMAN N S, FOUDA M E, and RADWAN A G. Memristor-CNTFET based ternary logic gates[J]. Microelectronics Journal, 2018, 72: 74–85. doi: 10.1016/j.mejo.2017.12.008

|

|

MOHAMMED M U, VIJJAPURAM R, and CHOWDHURY M H. Novel CNTFET and memristor based unbalanced ternary logic gate[C]. The 61st IEEE International Midwest Symposium on Circuits and Systems, Windsor, Canada, 2018: 1106–1109. doi: 10.1109/MWSCAS.2018.8623845.

|

|

SOLIMAN N S, FOUDA M E, SAID L A, et al. Memristor-CNTFET based ternary comparator unit[C]. The 30th International Conference on Microelectronics, Sousse, Tunisia, 2018: 148–151. doi: 10.1109/ICM.2018.8704010.

|

|

SOLIMAN N, FOUDA M E, ALHURBI A G, et al. Ternary functions design using memristive threshold logic[J]. IEEE Access, 2019, 7: 48371–48381. doi: 10.1109/ACCESS.2019.2909500

|

|

EBRAHIMI S, SABBAGHI-NADOOSHAN R, and TAVAKOLI M B. Design of a ternary logical circuit using the Au-DNA-Ag memristor[J]. Journal of Electronic Materials, 2019, 48(10): 6261–6268. doi: 10.1007/s11664-019-07413-1

|

|

CHEN Qilai, LIU Gang, TANG Minghua, et al. A univariate ternary logic and three-valued multiplier implemented in a nano-columnar crystalline zinc oxide memristor[J]. RSC Advances, 2019, 9(42): 24595–24602. doi: 10.1039/C9RA04119B

|

|

FAROOQ U and ASLAM M H. Design and implementation of basic building blocks of FPGA using memristor-transistor hybrid approach[C]. The 5th International Conference on the Innovative Computing Technology, Pontevedra, Spain, 2015: 142–147. doi: 10.1109/INTECH.2015.7173484.

|

|

SAMPATH M, MANE P S, and RAMESHA C K. Hybrid CMOS-memristor based FPGA architecture[C]. 2015 International Conference on VLSI Systems, Architecture, Technology and Applications, Bangalore, India, 2015: 1–6. doi: 10.1109/VLSI-SATA.2015.7050461.

|

|

FAROOQ U, BHATTI M K, and ASLAM M H. A novel heterogeneous FPGA architecture based on memristor-transistor hybrid approach[C]. 2016 International Conference on Design and Technology of Integrated Systems in Nanoscale Era, Istanbul, Turkey, 2016: 1–6. doi: 10.1109/DTIS.2016.7483890.

|

|

ASLAM M H, FAROOQ U, AWAIS M N, et al. Exploring the effect of LUT size on the area and power consumption of a novel memristor-transistor hybrid FPGA architecture[J]. Arabian Journal for Science and Engineering, 2016, 41(8): 3035–3049. doi: 10.1007/s13369-016-2068-8

|

|

XIE Lei, DU NGUYEN H A D, TAOUIL M, et al. Non-volatile look-up table based FPGA implementations[C]. The 11th International Design & Test Symposium, Hammamet, Tunisia, 2016: 165–170. doi: 10.1109/IDT.2016.7843034.

|

|

WANG Xiaoping, CHEN Lin, SHEN Yi, et al. A novel circuit design for complementary resistive switch-based stateful logic operations[J]. Chinese Physics B, 2016, 25(5): 058502. doi: 10.1088/1674-1056/25/5/058502

|

|

WANG Xiaoping, CHEN Kai, FENG Wei, et al. A neotype implemention method for CRS-based logic gates in crossbar array[C]. The 35th Chinese Control Conference, Chengdu, China, 2016: 5835–5840. doi: 10.1109/ChiCC.2016.7554270.

|

下载:

下载:

下载:

下载: