4.5 bit Sub-stage Circuit for 14 bit 210 MS/s Charge-domain ADC

-

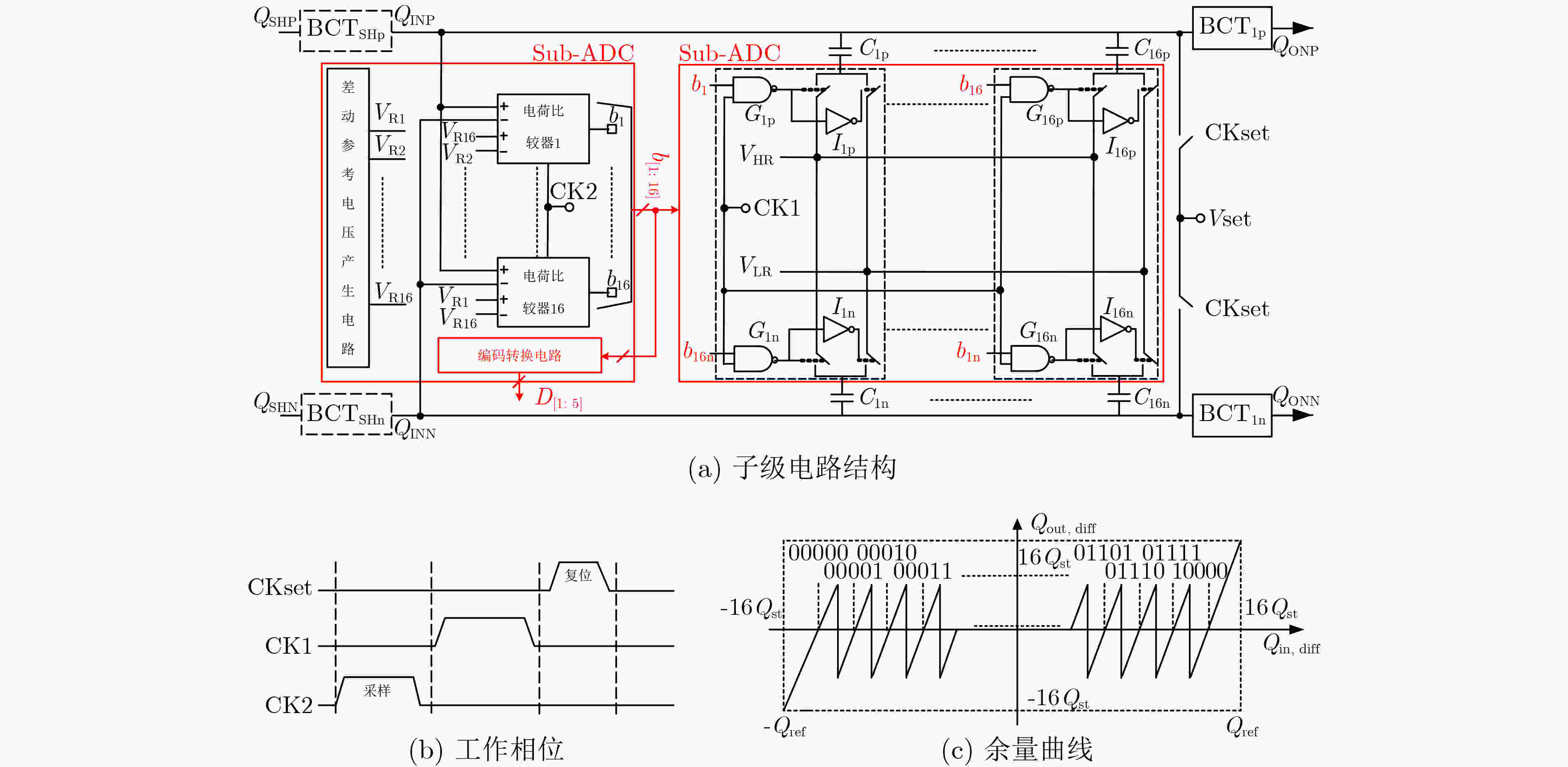

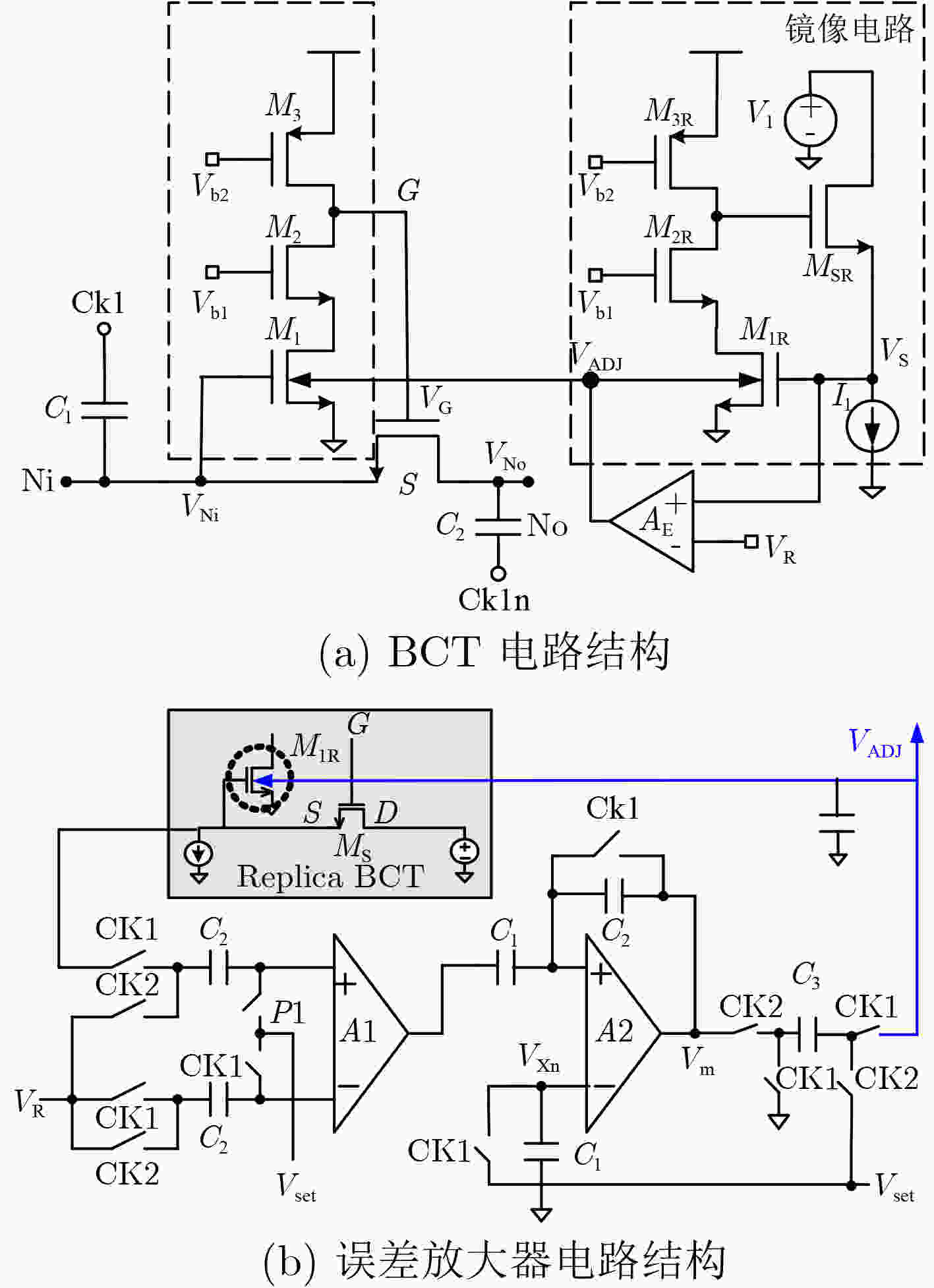

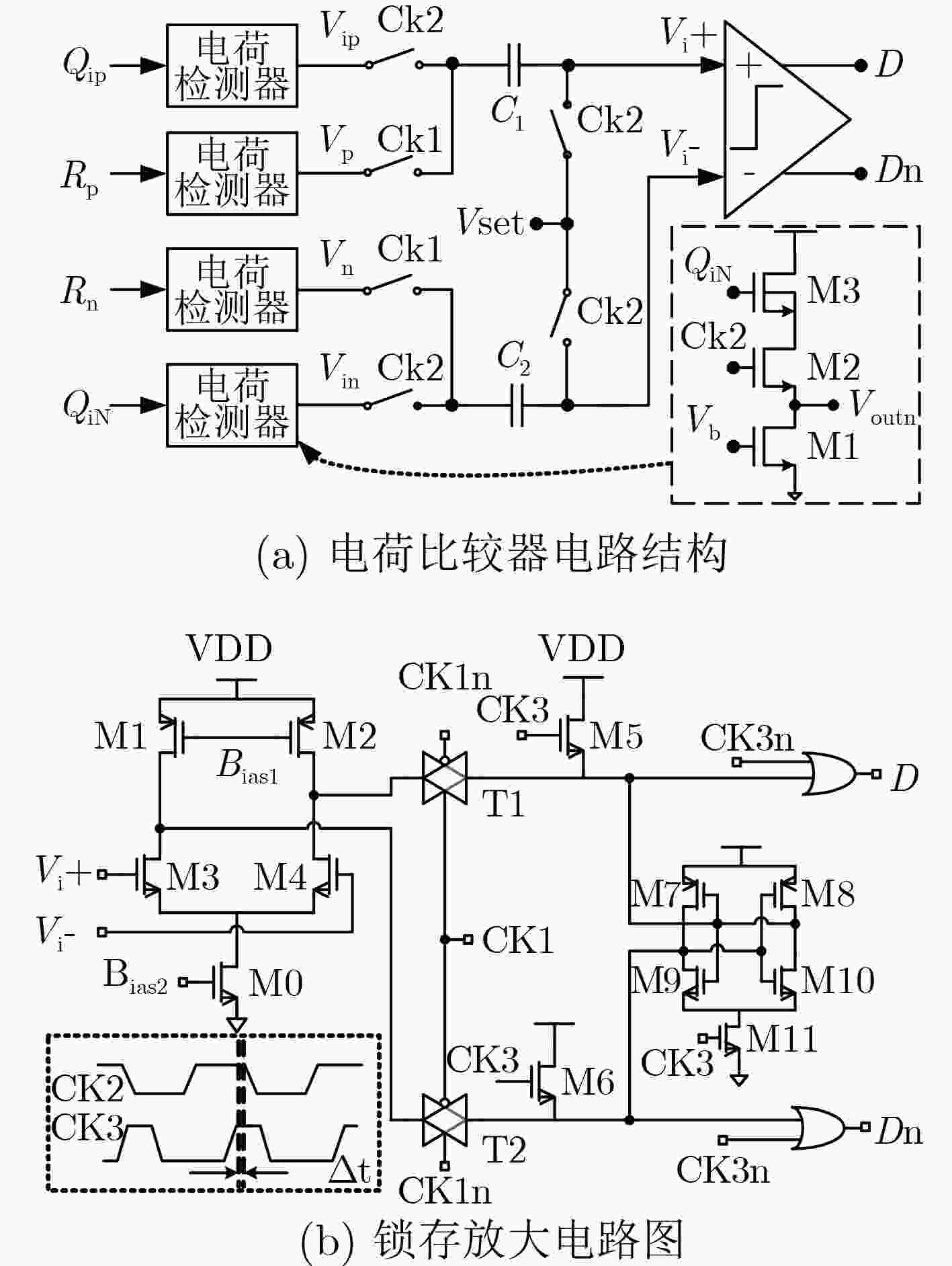

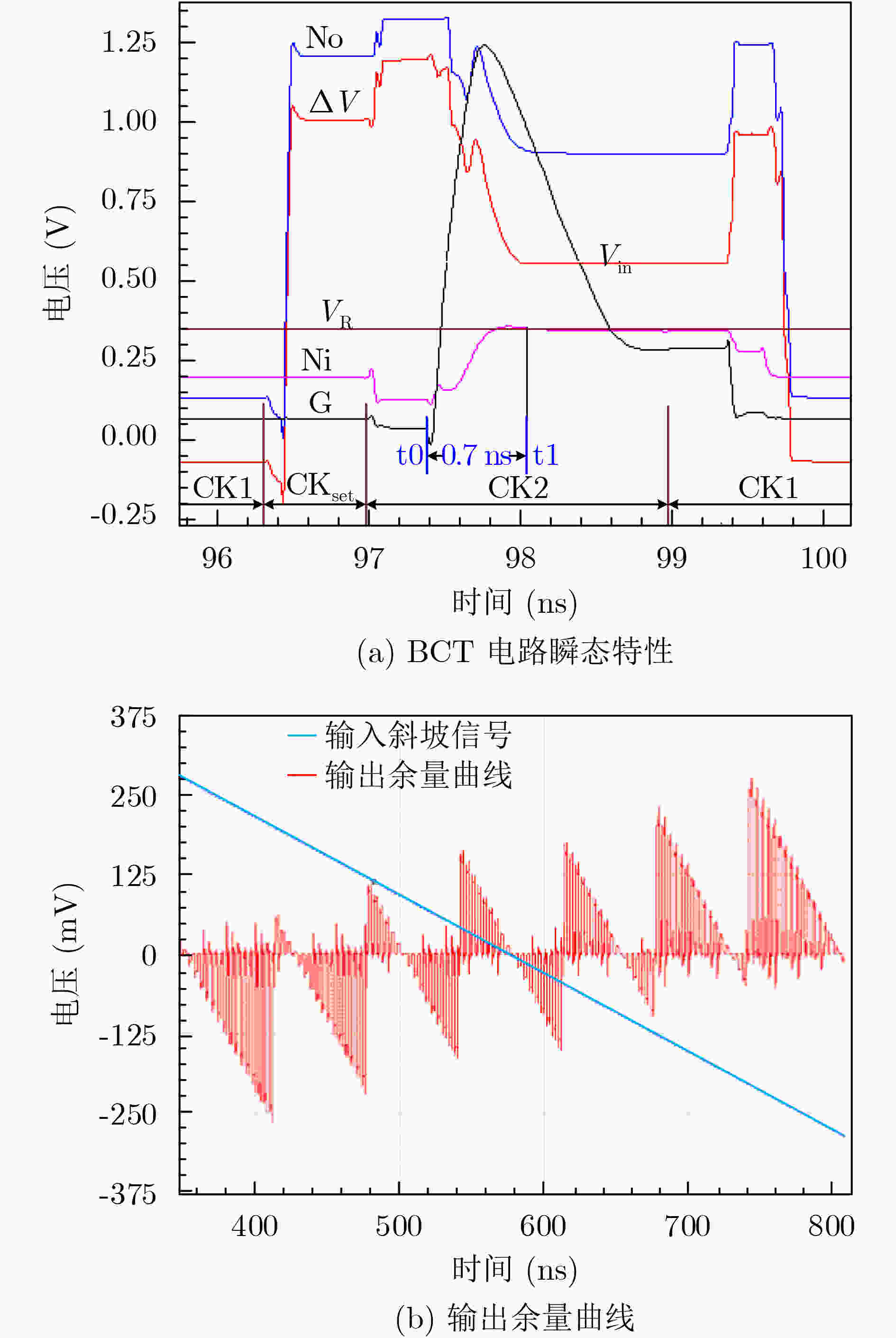

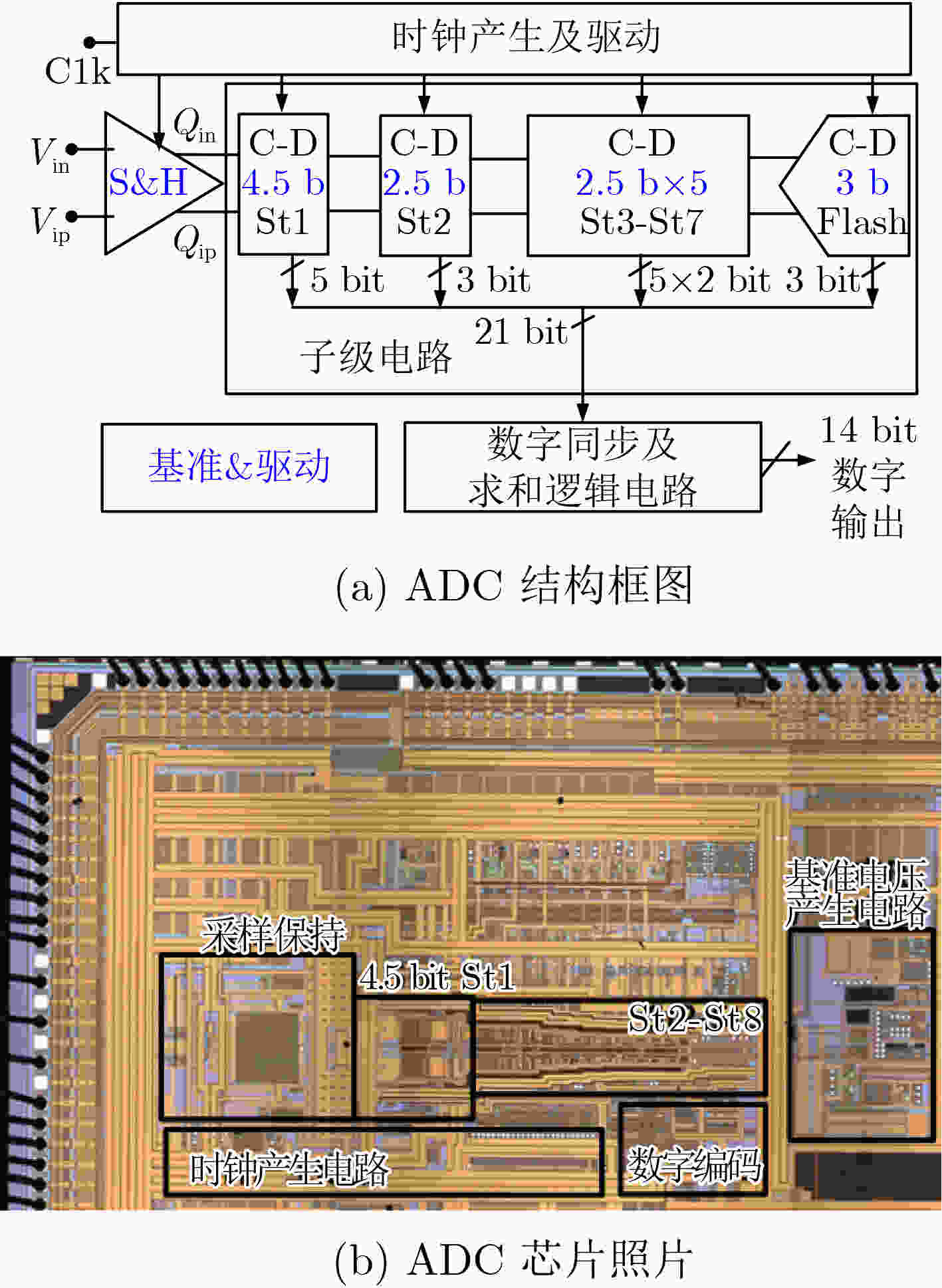

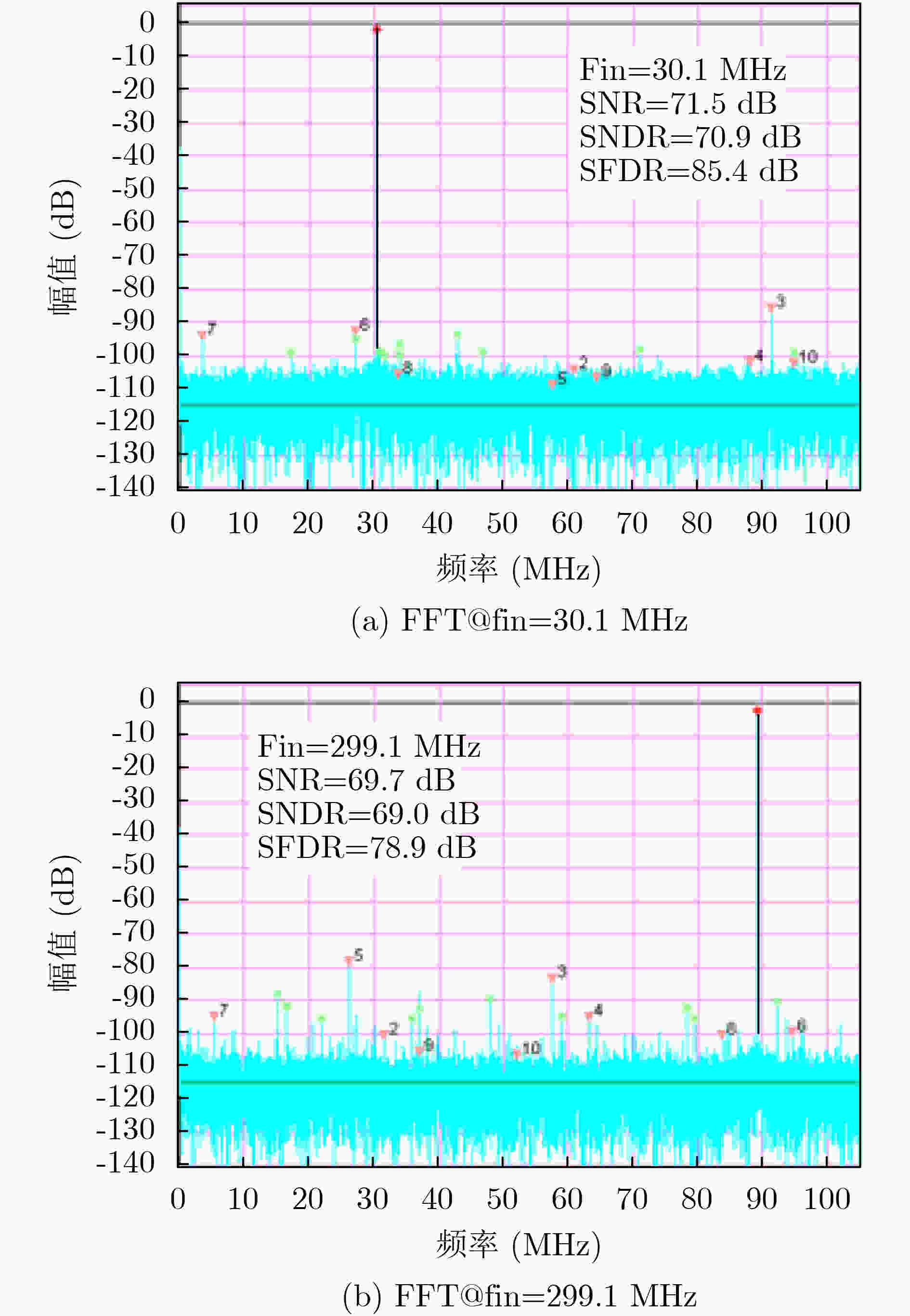

摘要: 该文提出了一种用于高速高精度电荷域流水线模数转换器(ADC)的电荷域4.5位前端子级电路。该4.5位子级电路使用增强型电荷传输(BCT)电路替代传统开关电容技术流水线ADC中的高增益带宽积运放来实现电荷信号传输和余量处理,从而实现超低功耗。所提4.5位子级电路被运用于一款14位210 MS/s电荷域ADC中作为前端第1级子级电路,并在1P6M 0.18 μm CMOS工艺下实现。测试结果显示,该14位ADC电路在210 MS/s条件下对于30.1 MHz单音正弦输入信号得到的无杂散动态范围为85.4 dBc,信噪比为71.5 dBFS, ADC内核面积为3.2 mm2,功耗仅为205 mW。Abstract: A 4.5 bit sub-stage circuit for high speed high precision charge domain pipelined Analog-to-Digital Converter (ADC) is proposed. Instead of the high-performance opamps used in traditional switched-capacitor pipelined ADCs, charge transfer and residue charge calculation is realized with Boosted Charge Transfer (BCT) circuit in the proposed 4.5 bit sub-stage. Therefore, the power consumption of the 4.5 bit sub-stage circuit can be reduced remarkably. The proposed 4.5 bit sub-stage circuit is used as the 1st stage circuit for a 14 bit 210 MS/s charge domain pipelined ADC and realized in a 1P6M 0.18 μm CMOS process. Test results show the 14 bit 210 MS/s ADC achieves the signal-to-noise ratio of 71.5 dBFS and the spurious free dynamic range of 85.4 dB, with 30.1 MHz input single tone signal at 210 MS/s, while the ADC core consumes the power consumption of 205 mW and occupies an area of 3.2 mm2.

-

表 1 本电路部分关键实测数据

测试电路 精度(bit) 输入信号(MHz) 采样率(MS/s) 温度(°C) SNR(dB) SFDR(dB) 内核电流(mA) 内核功耗(mW) 电路1 14 30.1 210 –40 68.3 80.2 109 197 25 71. 5 85.4 114 205 85 71.3 83.6 119 214 电路2 14 30.1 210 –40 68.1 79.8 108 194 25 71.4 85.2 113 203 85 71.1 83.2 117 211 表 2 ADC性能对比

技术指标 精度

(bit)采样率

(MS/s)SNR

(dB)SFDR

(dB)电源电压

(V)工艺

(nm)内核功耗

(mW)内核面积

(mm2)FOM(pJ/step)功耗/

(2ENOB·fclk)文献[4] 14 500 64.8 92.7 1.8/3.3 180 550 2.5* 0.71 文献[5] 14 1000 69 86 1.2/2.5 65 1200 5 0.55 文献[14] 14 200 68.5 88.5 1.8 180 460 22.5** 1.07 文献[15] 14 250 68.5 94.7 1.8 180 300 3.6 0.57 本文 14 210 71.5 85.4 1.8 180 205 3.2 0.39 注:*采用SiGe BiCMOS工艺;**采用时间交织结构。 -

李光祚, 默迪, 王宁, 等. 一种新的高重频宽带相干激光雷达系统研究[J]. 电子与信息学报, 2018, 40(3): 525–531. doi: 10.11999/JEIT170479LI Guangzuo, MO Di, WANG Ning, et al. A novel coherent ladar system with high repetition frequency and wide bandwidth[J]. Journal of Electronics &Information Technology, 2018, 40(3): 525–531. doi: 10.11999/JEIT170479 陈珍海, 魏敬和, 钱宏文, 等. 用于14位210 MS/s电荷域ADC的采样保持前端电路[J]. 电子与信息学报, 2019, 41(3): 732–738. doi: 10.11999/JEIT180337CHEN Zhenhai, WEI Jinghe, QIAN Hongwen, et al. Sample and hold front-end circuit for 14-bit 210 MS/s charge-domain ADC[J]. Journal of Electronics &Information Technology, 2019, 41(3): 732–738. doi: 10.11999/JEIT180337 景国彬, 孙光才, 邢孟道, 等. 一种新的步进频MIMO-SAR带宽合成的处理方法[J]. 西安电子科技大学学报: 自然科学版, 2018, 45(2): 148–153, 159. doi: 10.3969/j.issn.1001-2400.2018.02.025JING Guobin, SUN Guangcai, XING Mengdao, et al. Novel two-step method of bandwidth synthesis for SF-MIMO-SAR[J]. Journal of Xidian University, 2018, 45(2): 148–153, 159. doi: 10.3969/j.issn.1001-2400.2018.02.025 EL-CHAMMAS M, LI Xiaopeng, KIMURA S, et al. 15.8 90 dB-SFDR 14b 500 MS/s BiCMOS switched-current pipelined ADC[C]. 2015 IEEE International Solid-State Circuits Conference, San Francisco, USA, 2015: 286–287. doi: 10.1109/ISSCC.2015.7063038. ALI A M A, DINC H, BHORASKAR P, et al. A 14 Bit 1 GS/s RF sampling pipelined ADC with background calibration[J]. IEEE Journal of Solid-State Circuits, 2014, 49(12): 2857–2867. doi: 10.1109/JSSC.2014.2361339 ALI A M A, DINC H, BHORASKAR P, et al. A 14-bit 2.5 GS/s and 5 GS/s RF sampling ADC with background calibration and Dither[C]. 2016 IEEE Symposium on VLSI Circuits, Honolulu, USA, 2016: 1–2. doi: 10.1109/VLSIC.2016.7573537. WU Jiangfeng, CHOU A, LI Tianwei, et al. 26.7 A 4 GS/s 13b pipelined ADC with capacitor and amplifier sharing in 16 nm CMOS[C]. 2016 IEEE International Solid-State Circuits Conference, San Francisco, USA, 2016: 466–468. doi: 10.1109/ISSCC.2016.7418109. ANTHONY M, KOHLER E, KURTZE J, et al. A process-scalable low-power charge-domain 13-bit pipeline ADC[C]. 2008 IEEE Symposium on VLSI Circuits, Honolulu, USA, 2008: 222–223. doi: 10.1109/VLSIC.2008.4586015. CHEN Zhenhai, YU Zongguang, HUANG Songren, et al. A PVT Insensitive boosted charge transfer for high speed charge-domain pipelined ADCs[J]. IEICE Electronics Express, 2012, 9(6): 565–571. doi: 10.1587/elex.9.565 CHEN Zhenhai, HUANG Songren, ZHANG Hong, et al. A 27-mW 10-bit 125-MSPS charge domain pipelined ADC with a PVT insensitive boosted charge transfer circuit[J]. Journal of Semiconductors, 2013, 34(3): 035009. doi: 10.1088/1674-4926/34/3/035009 HUANG Songren, ZHANG Hong, CHEN Zhenhai, et al. A 10-bit 250 MSPS charge-domain pipelined ADC with replica controlled PVT insensitive BCT circuit[J]. Journal of Semiconductors, 2015, 36(5): 055012. doi: 10.1088/1674-4926/36/5/055012 YU Zongguang, SU Xiaobo, CHEN Zhenhai, et al. A 12-bit 250-MS/s charge-domain pipelined analog-to-digital converter with feed-forward common-mode charge control[J]. Tsinghua Science and Technology, 2018, 23(1): 87–94. doi: 10.26599/TST.2018.9010030 陈珍海, 魏敬和, 苏小波, 等. 低功耗时间交织12位500 MS/s电荷域ADC[J]. 西安电子科技大学学报: 自然科学版, 2017, 44(6): 109–115, 137. doi: 10.3969/j.issn.1001-2400.2017.06.020CHEN Zhenhai, WEI Jinghe, SU Xiaobo, et al. Low power time-interleaved 12-bit 500 MS/s charge-domain ADC[J]. Journal of Xidian University, 2017, 44(6): 109–115, 137. doi: 10.3969/j.issn.1001-2400.2017.06.020 ZHANG Yiwen, CHEN Chixiao, YU Bei, et al. A 14-bit 200-MS/s time-interleaved ADC with sample-time error calibration[J]. Journal of Semiconductors, 2012, 33(10): 105010. doi: 10.1088/1674-4926/33/10/105010 ZHENG Xuqiang, WANG Zhijun, LI Fule, et al. A 14-bit 250 MS/s IF sampling pipelined ADC in 180 nm CMOS process[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2016, 63(9): 1381–1392. doi: 10.1109/TCSI.2016.2580703 -

下载:

下载:

下载:

下载: