High Resolution Digital Pulse Width Modulation Design for Digital DC-DC Converter

-

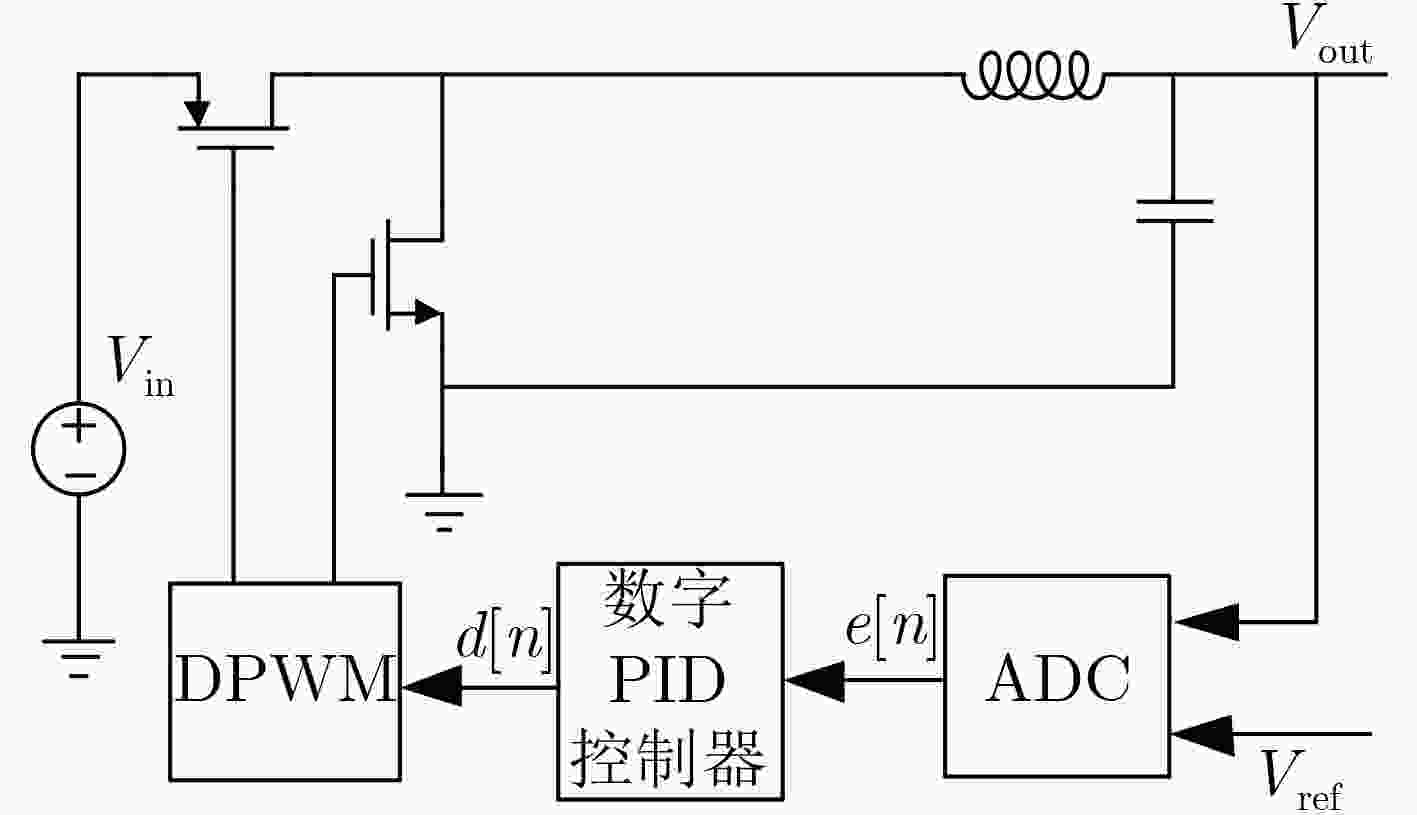

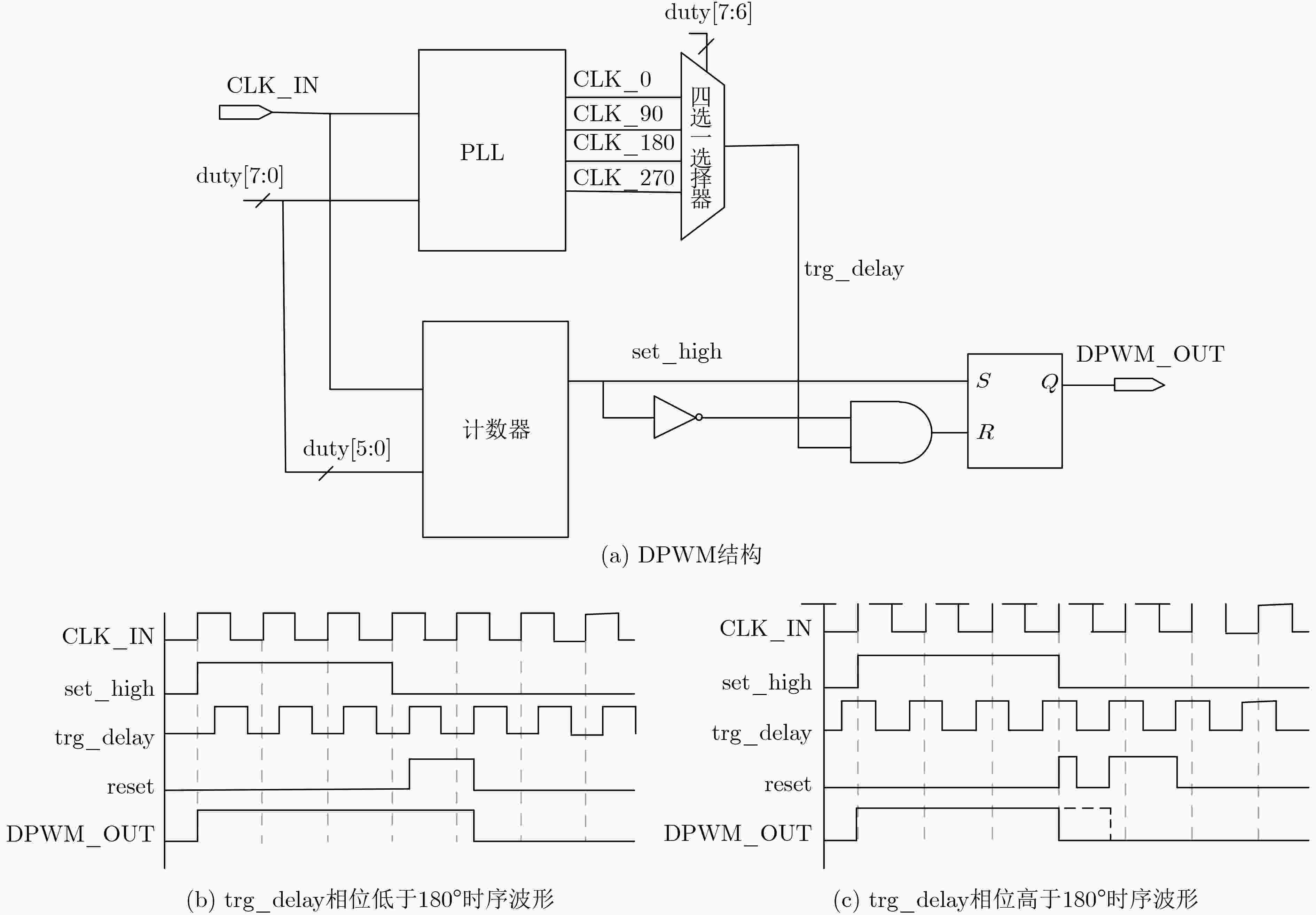

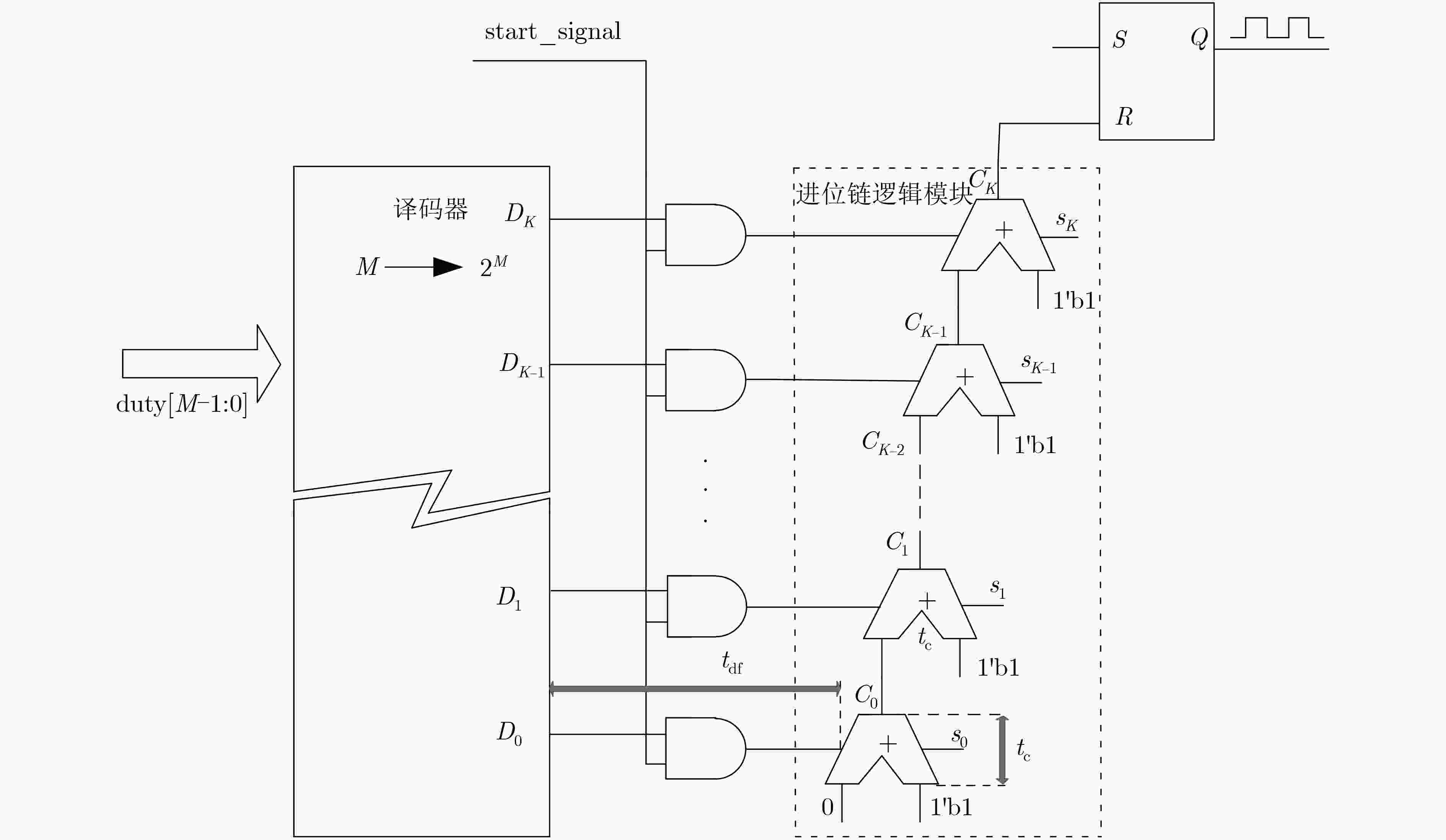

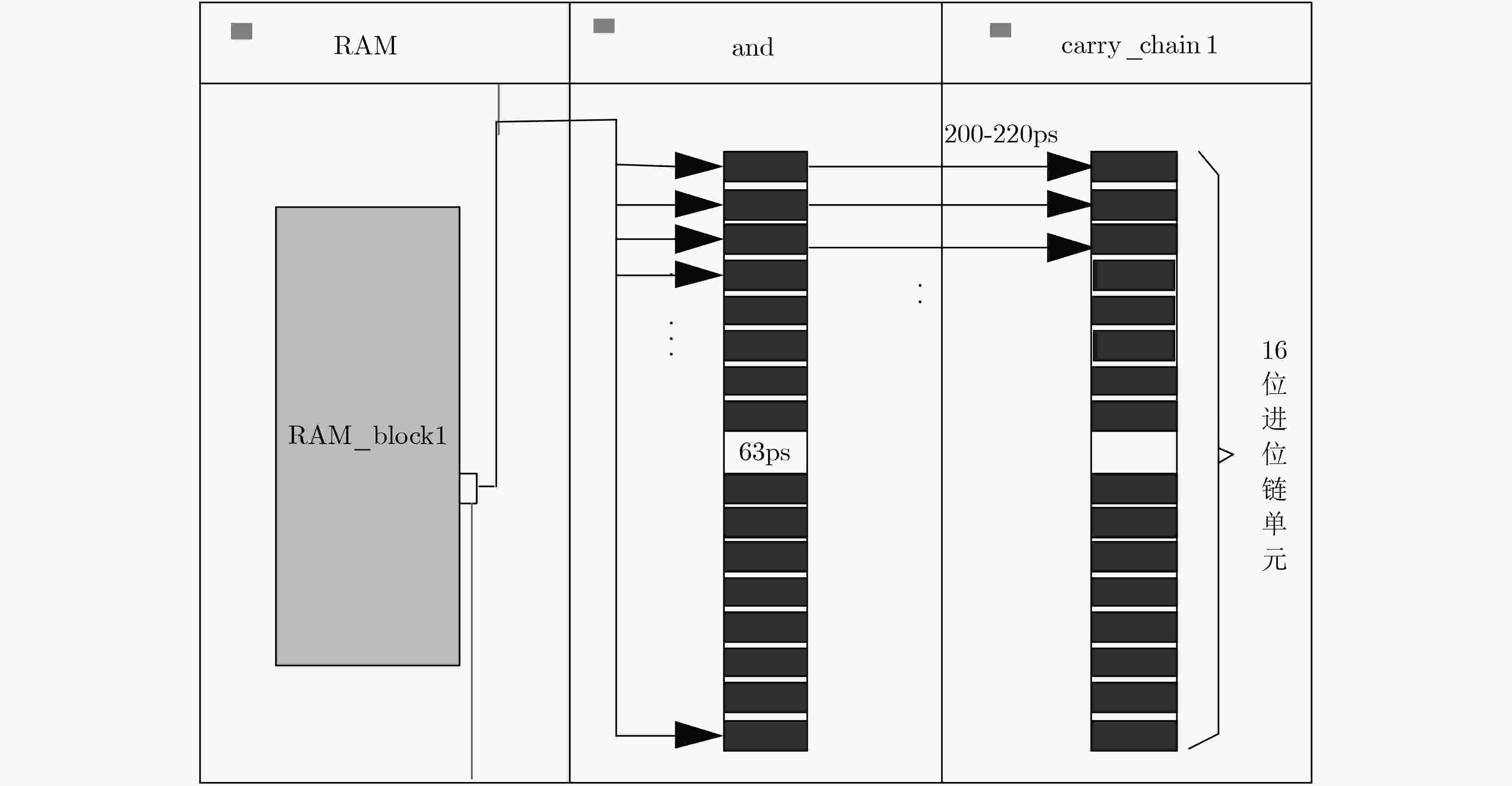

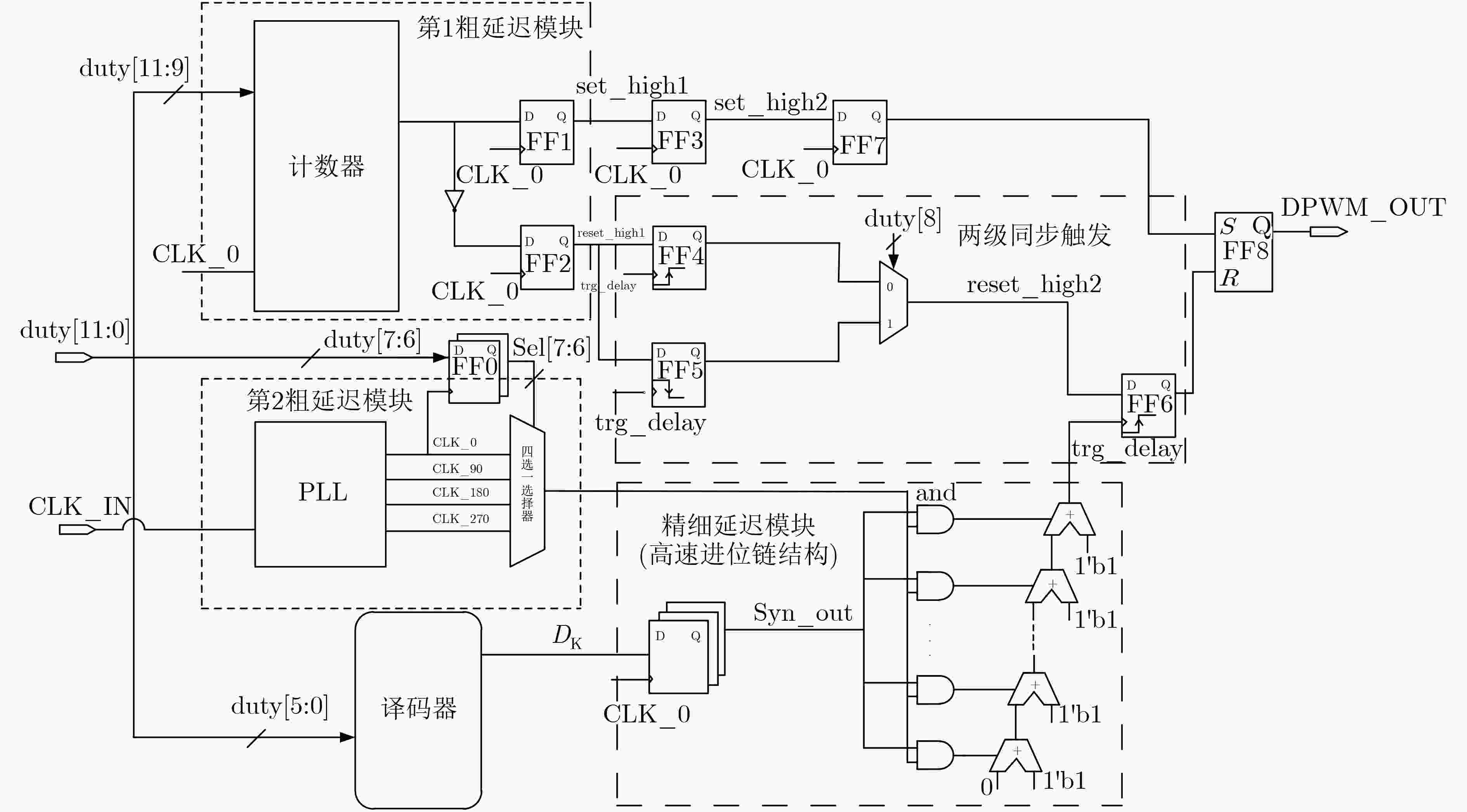

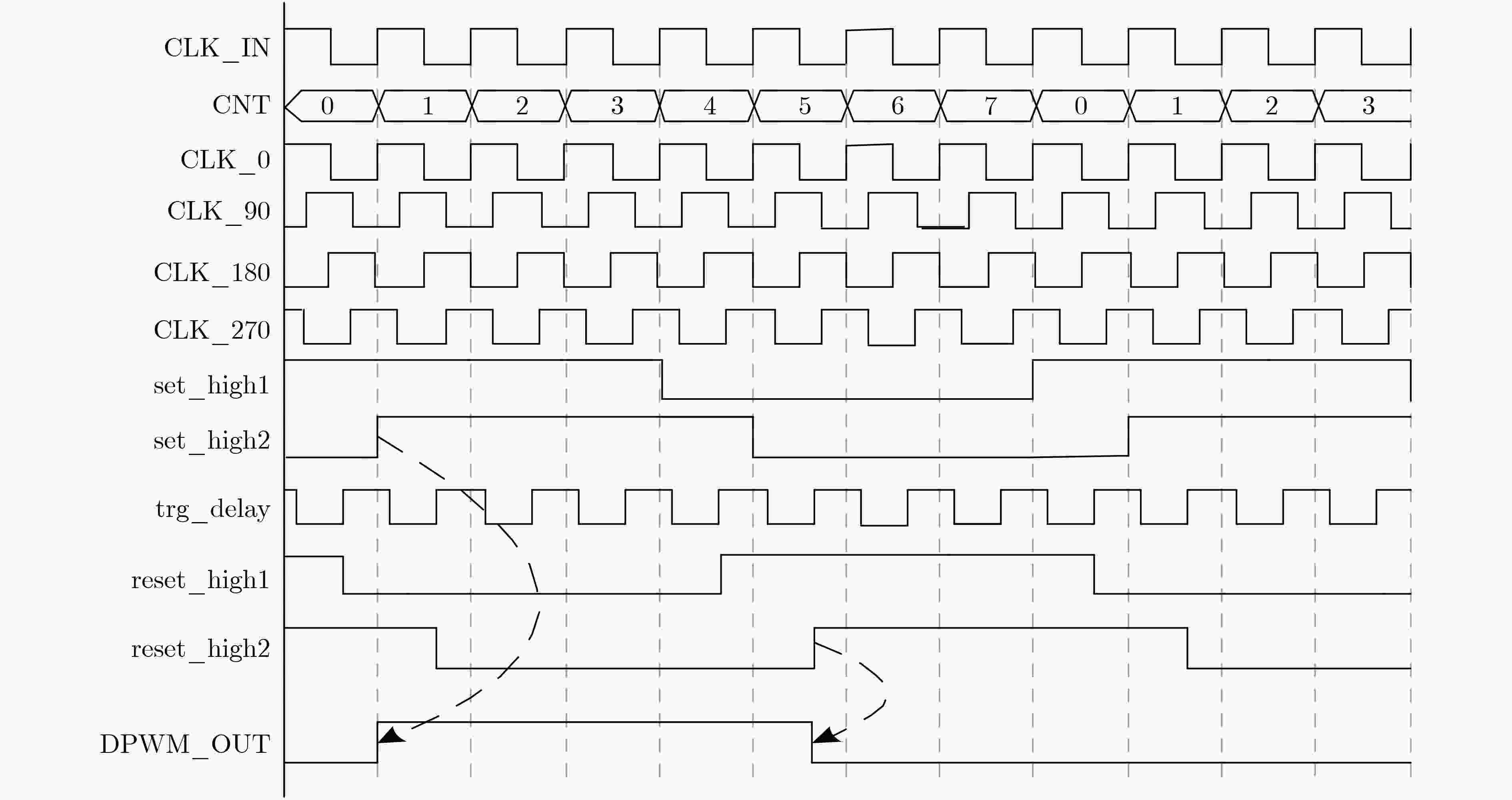

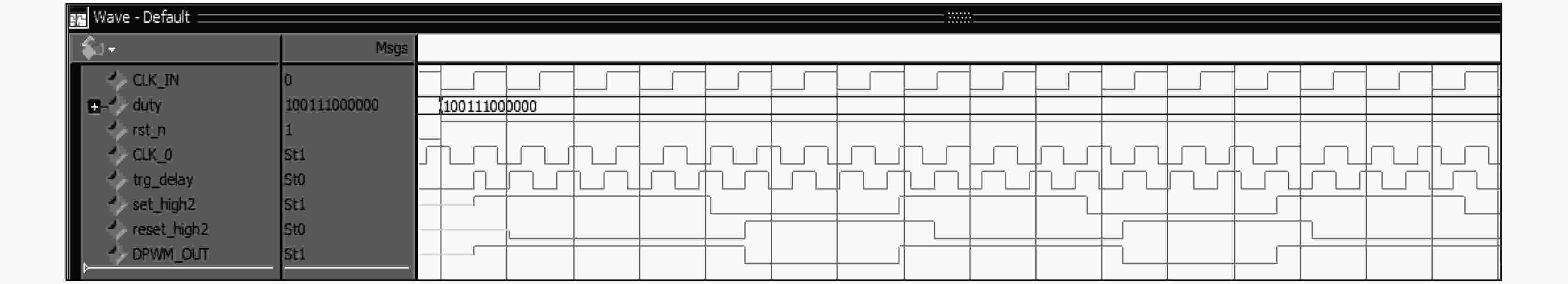

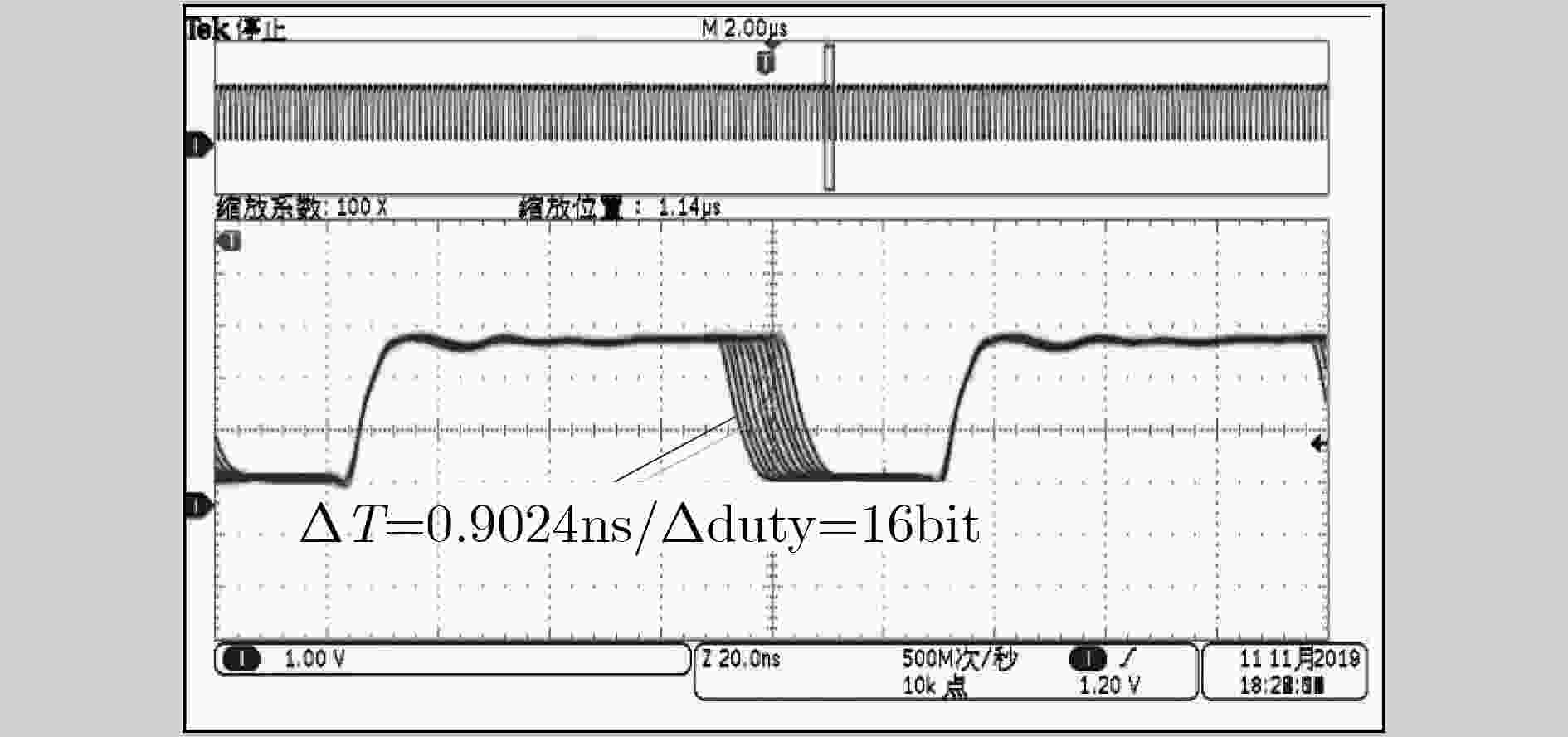

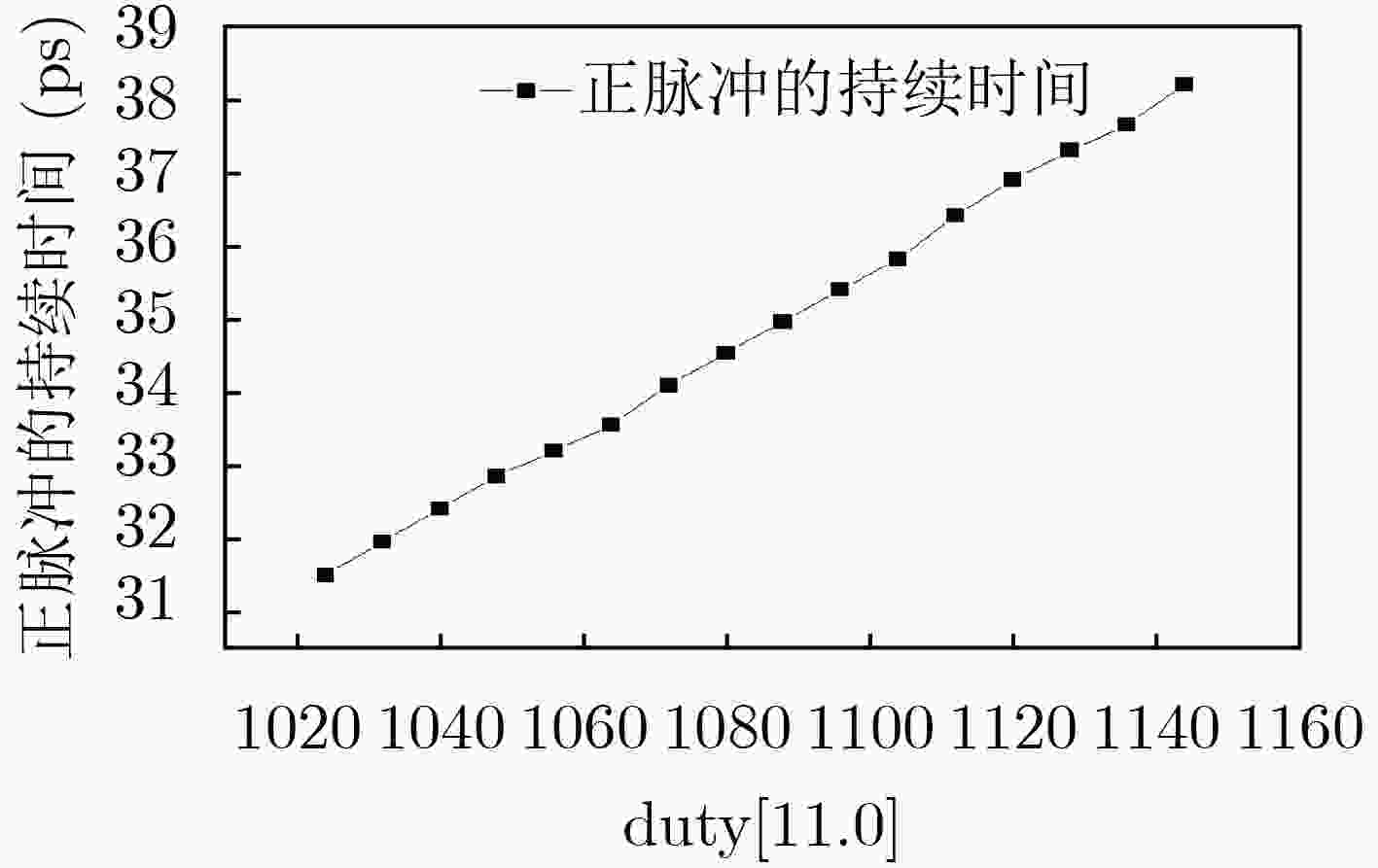

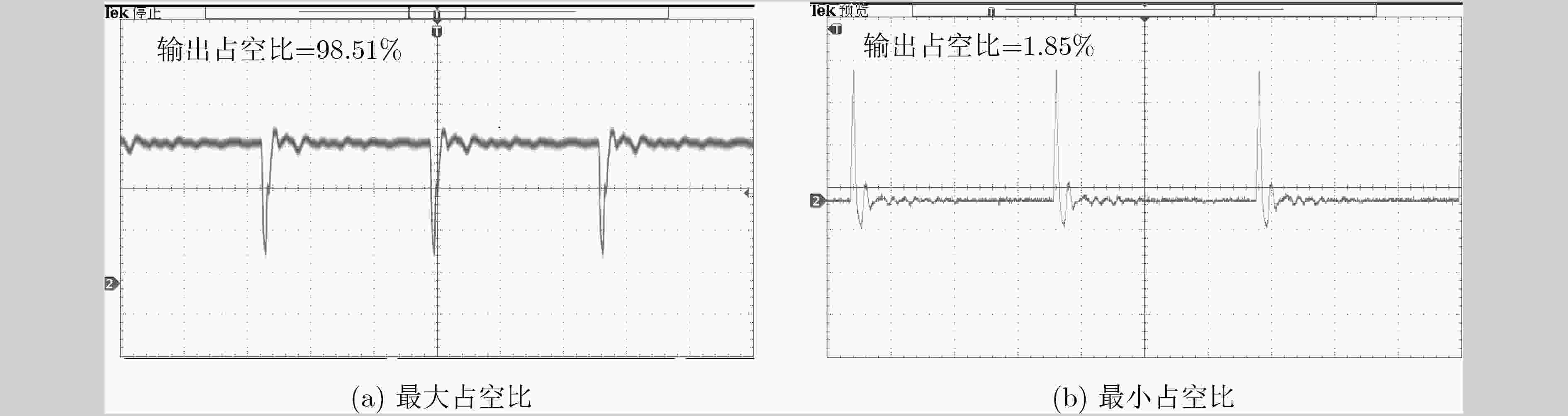

摘要: 数字控制在电力电子领域的优势使得数字脉冲宽度调制的使用日益增加,然而其分辨率不足一直是制约开关电源领域中数字控制技术发展的主要因素之一。针对高分辨率数字脉冲宽度调制的应用需求,该文提出一种基于高速进位链结构的高分辨率数字脉冲宽度调制电路。该电路采用计数器、比较器、固定相移锁相环单元及高速进位链的混合结构,有效地提高了分辨率,并在Altera的Cyclone IV低成本现场可编程门阵列器件上实现。实验结果显示,当输入参考时钟工作频率为70 MHz时,该结构的分辨率可达到56 ps。此外,该电路还具有较宽的开关频率调节范围及较好的线性度等优点。Abstract: The advantages of digital control in the field of power electronics lead to an increasing use of Digital Pulse Width Modulation (DPWM). However, the insufficient resolution of DPWM is one of the main factors that constrain the development of digital control technology in the field of switch mode power supplies. For the application requirements of high-resolution DPWM, this paper proposes a high-resolution DPWM circuit based on high-speed carry chain structure. The circuit comprises of counters, comparators, fixed phase shift PLL units and high-speed carry chains, which can effectively increase resolution. The circuit is also implemented on Altera’s Cyclone IV low-cost Field-Programmable Gate Array (FPGA) devices. The experimental results show that the resolution of the structure can reach 56 ps with 70 MHz input reference clock. In addition, the circuit also has wide switching frequency adjustment range and good linearity.

-

表 1 输入数据流信号duty对应的输出理想延迟时间和输出占空比命令

${\bf{duty}}\left( {{{M}} - {\bf{1:0}}} \right)$ $ {{t}}_{\bf{D}} $ ${{D} }_{{K} }{{D} }_{ { {{K} }{\rm{-} }1} }···{{D} }_{\bf{1} }{{D} }_{\bf{0} }$ 00···000 0 10000···00 00···001 $ {t}_{\rm{c}} $ $ 01000···00 $ 00···010 $ 2{t}_{\rm{c}} $ $ 00100···00 $ $. $ $. $ $. $ $. $ $. $ $. $ $. $ $. $ $. $ 11···111 $ K{t}_{\rm{c}} $ $ 00000···01 $ -

LIU Fangcheng, XIN Kai, and LIU Yunfeng. An adaptive Discontinuous Pulse Width Modulation (DPWM) method for three phase inverter[C]. 2017 IEEE Applied Power Electronics Conference and Exposition, Tampa, USA, 2017: 1467–1472. doi: 10.1109/APEC.2017.7930892. KIM S Y, PARK Y J, ALI I, et al. Design of a high efficiency DC–DC buck converter with two-step digital PWM and low power self-tracking zero current detector for IoT applications[J]. IEEE Transactions on Power Electronics, 2018, 33(2): 1428–1439. doi: 10.1109/TPEL.2017.2688387 FURUKAWA Y, NAKAMURA H, ETO H, et al. Fine resolution DPWM circuit for high frequency digital control DC-DC converter[C]. 2018 International Symposium on Power Electronics, Electrical Drives, Automation and Motion, Amalfi, Italy, 2018: 491–496. doi: 10.1109/SPEEDAM.2018.8445336. RADHIKA V and BASKARAN K. FPGA based DPWM/DPFM architecture for digitally controlled dc-dc converters[C]. 2016 IEEE Uttar Pradesh Section International Conference on Electrical, Computer and Electronics Engineering, Varanasi, India, 2016: 78–82. doi: 10.1109/UPCON.2016.7894628. CROVETTI P S. All-digital high resolution D/A Conversion by dyadic digital pulse modulation[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2017, 64(3): 573–584. doi: 10.1109/TCSI.2016.2614231 KAPAT S. Sampling-induced border collision bifurcation in a voltage-mode DPWM synchronous buck converter[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2019, 66(6): 1048–1052. doi: 10.1109/TCSII.2018.2866520 LUCÍA O, BURDÍO J M, BARRAGÁN L A, et al. Series-resonant multiinverter for multiple induction heaters[J]. IEEE Transactions on Power Electronics, 2010, 25(11): 2860–2868. doi: 10.1109/TPEL.2010.2051041 SONG Hu, JIANG Naiti, HU Shanshan, et al. FPGA-based high resolution DPWM control circuit[J]. Journal of Systems Engineering and Electronics, 2018, 29(6): 1136–1141. doi: 10.21629/JSEE.2018.06.03 NAVARRO D, LUCÍA O, BARRAGÁN L A, et al. Synchronous FPGA-based high-resolution implementations of digital pulse-width modulators[J]. IEEE Transactions on Power Electronics, 2012, 27(5): 2515–2525. doi: 10.1109/TPEL.2011.2173702 FURUKAWA Y, NAKAMURA H, ETO H, et al. A novel high resolution DPWM circuit for high frequency digitally controlled DC-DC converter[C]. 2018 IEEE Energy Conversion Congress and Exposition, Portland, USA, 2018: 1396–1400. doi: 10.1109/ECCE.2018.8557826. LAN P H, TSENG C Y, YEH F C, et al. A multi-mode digital controller with windowed ADC and self-calibrated DPWM for slew-enhanced switching converter[C]. 2010 IEEE Asian Solid-State Circuits Conference, Beijing, China, 2010: 1–4. doi: 10.1109/ASSCC.2010.5716556. SCHARRER M, HALTON M, SCANLAN T, et al. FPGA-based multi-phase digital pulse width modulator with dual-edge modulation[C]. The 25th Annual IEEE Applied Power Electronics Conference and Exposition, Palm Springs, USA, 2010: 1075–1080. doi: 10.1109/APEC.2010.5433371. PENG Hao, PRODIC A, ALARCON E, et al. Modeling of quantization effects in digitally controlled DC-DC converters[J]. IEEE Transactions on Power Electronics, 2007, 22(1): 208–215. doi: 10.1109/TPEL.2006.886602 NAVARRO D, BARRAGÁN L A, ARTIGAS J I, et al. FPGA-based high resolution synchronous digital pulse width modulator[C]. 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 2010: 2771–2776. doi: 10.1109/ISIE.2010.5636571. SALOMON L, MORENO R, and PIMENTA T. Implementation of a 17 bits pulse width modulation circuit using FPGA[C]. 2015 International Conference on Microelectronics, Casablanca, Morocco, 2015: 206–209. doi: 10.1109/ICM.2015.7438024. GE Lusheng, CHEN Zongxiang, CHEN Zhijie, et al. Design and implementation of a high resolution DPWM based on a low-cost FPGA[C]. 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, USA, 2010: 2306–2311. doi: 10.1109/ECCE.2010.5617866. COSTINETT D, RODRIGUEZ M, and MAKSIMOVIC D. Simple digital pulse width modulator under 100 ps resolution using general-purpose FPGAs[J]. IEEE Transactions on Power Electronics, 2013, 28(10): 4466–4472. doi: 10.1109/TPEL.2012.2233218 CHENG Xin, SONG Ruifeng, XIE Guangjun, et al. A new FPGA-based segmented delay-line DPWM with compensation for critical path delays[J]. IEEE Transactions on Power Electronics, 2018, 33(12): 10794–10802. doi: 10.1109/TPEL.2017.2763750 -

下载:

下载:

下载:

下载: