Research into Low Thermal Gradient Oriented 3D FPGA Interconnect Channel Architecture Design

-

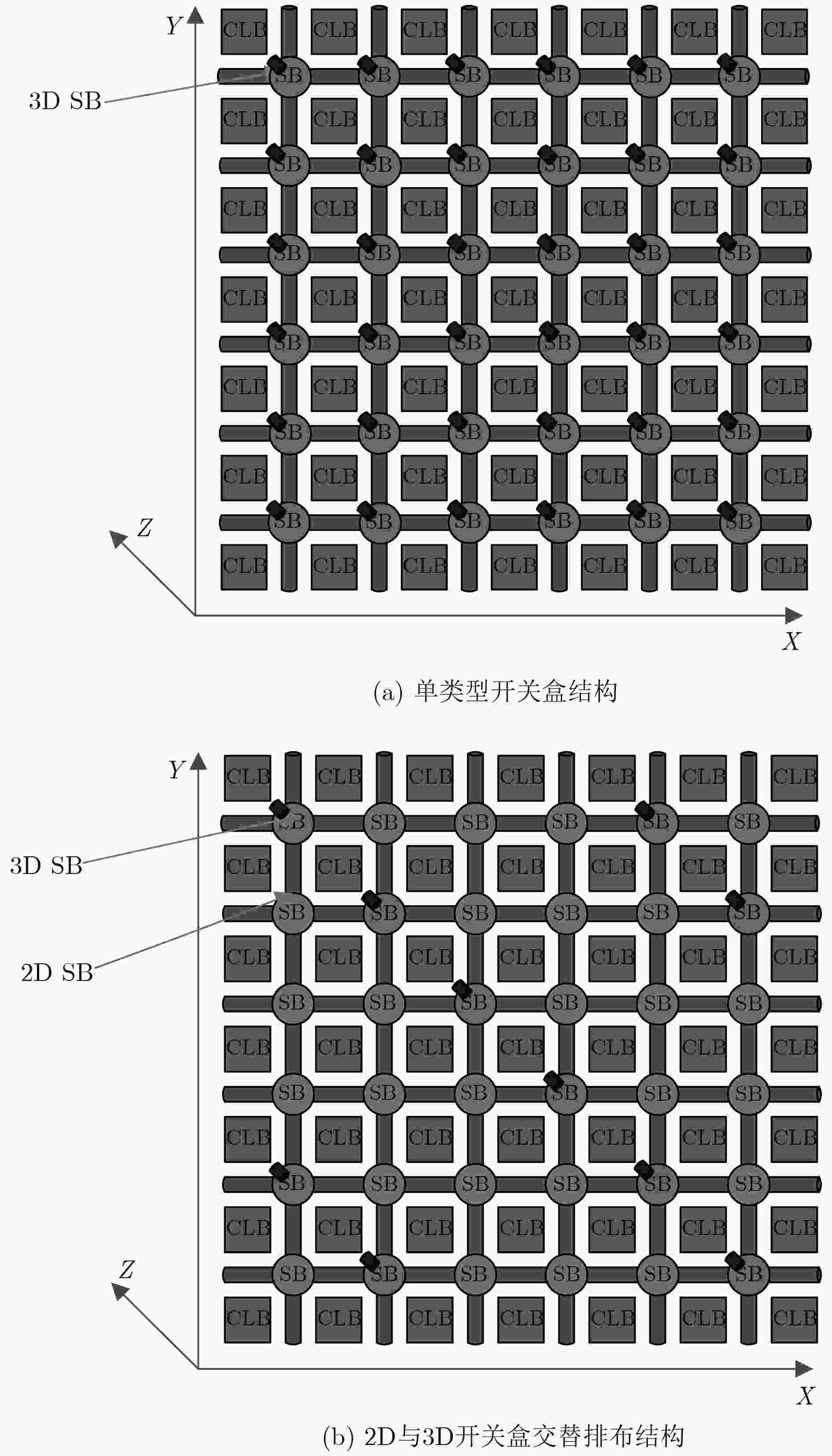

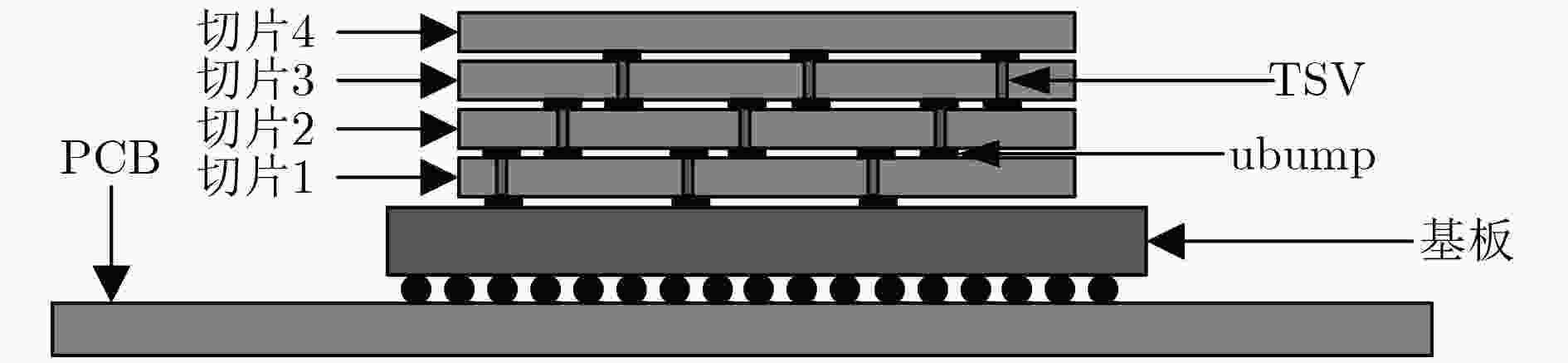

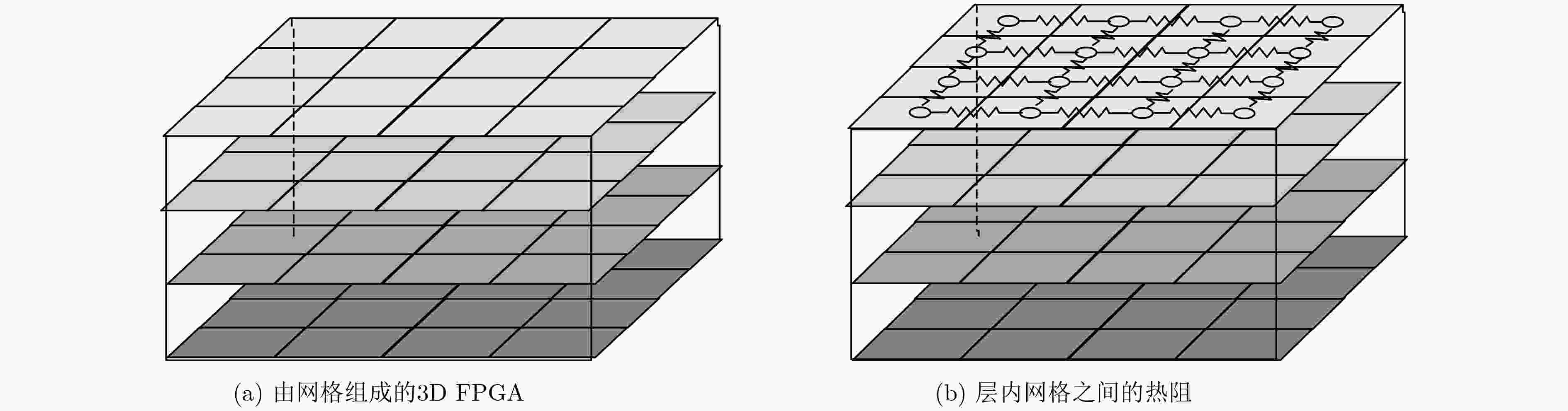

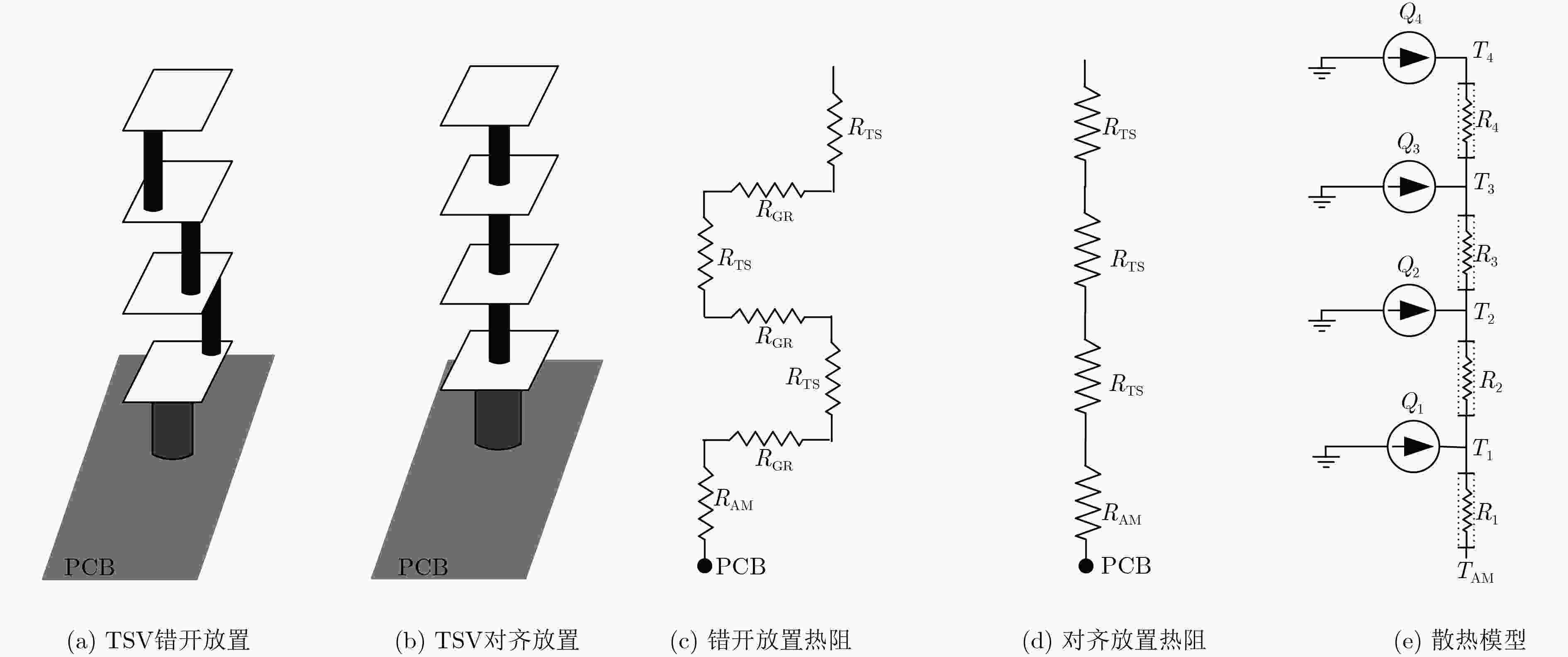

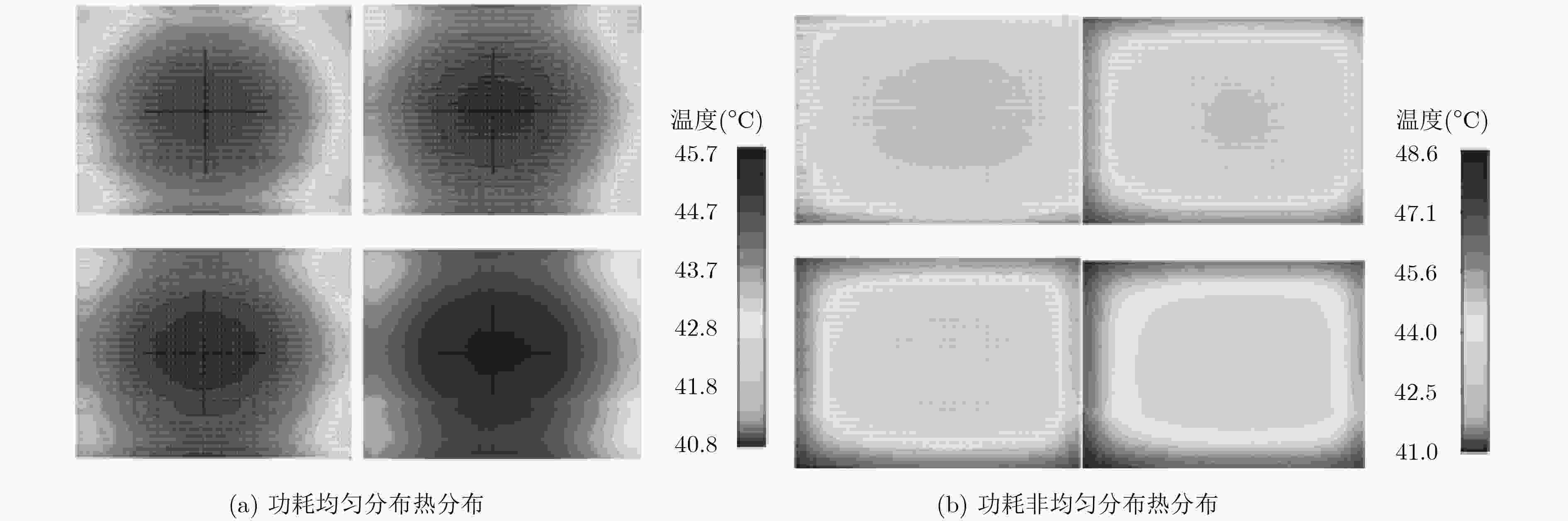

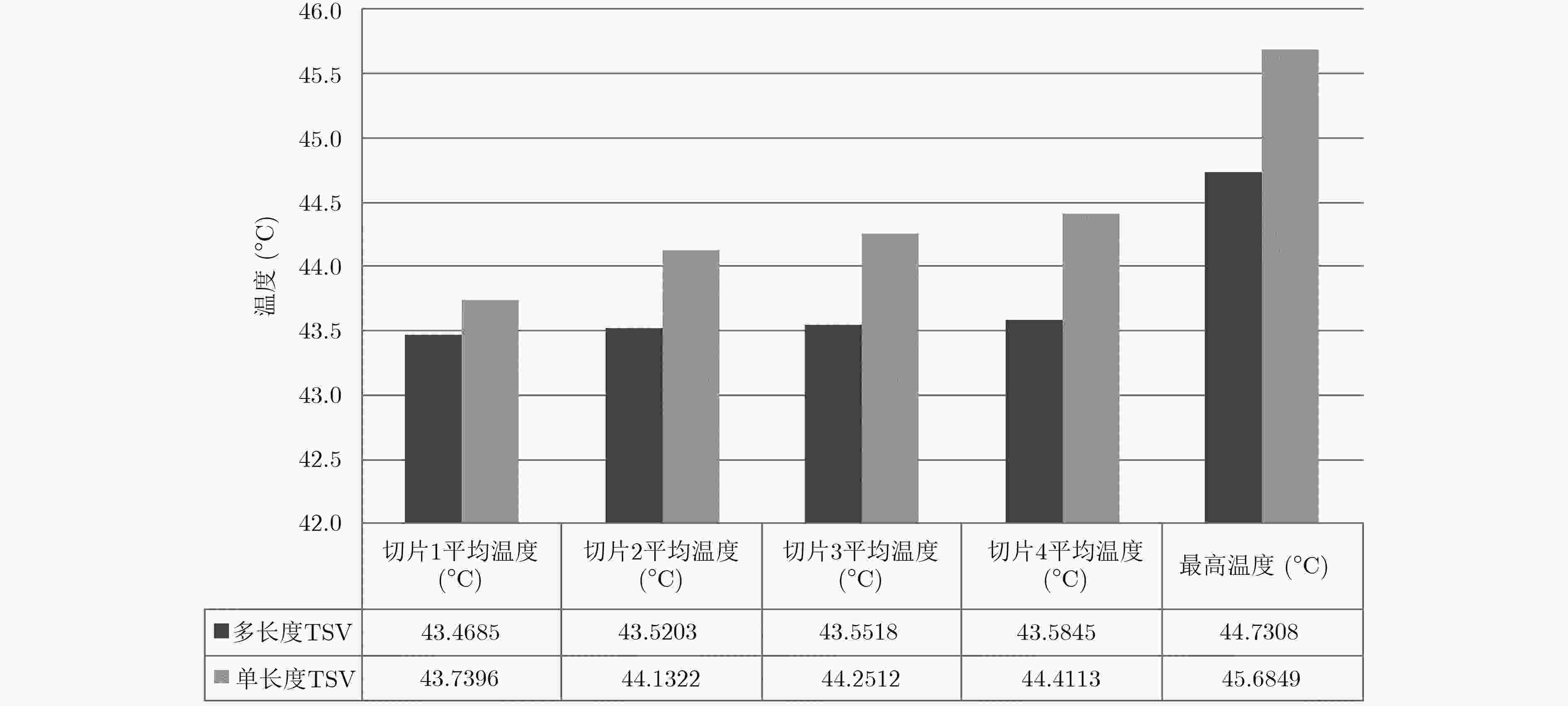

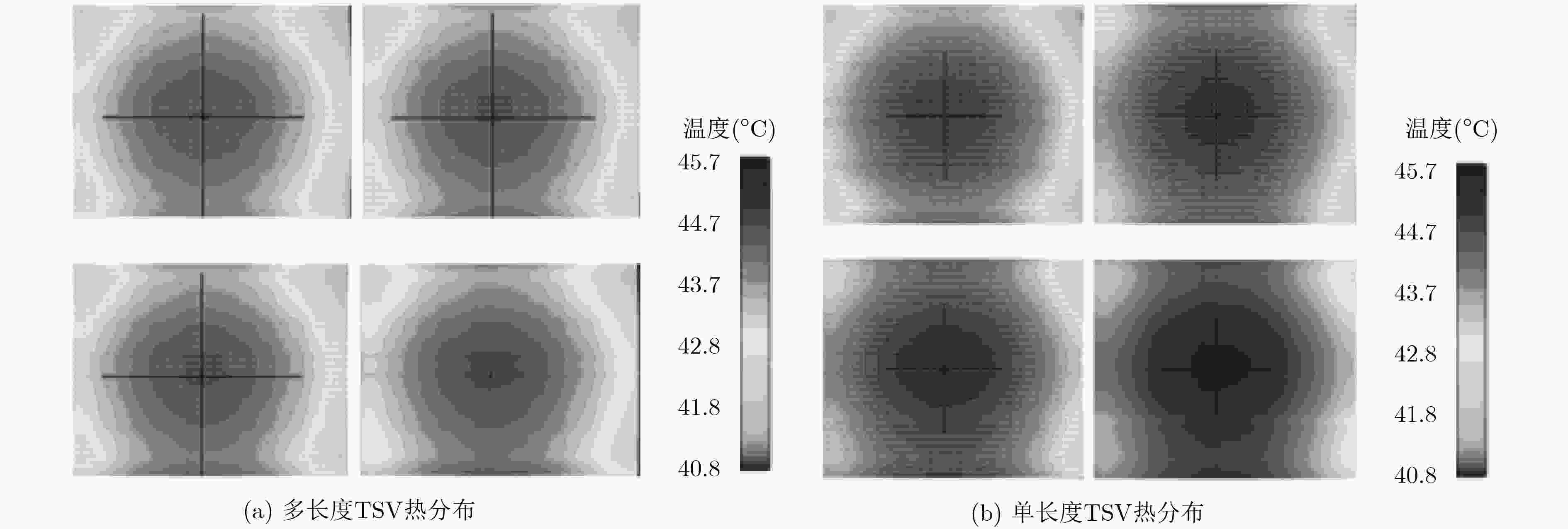

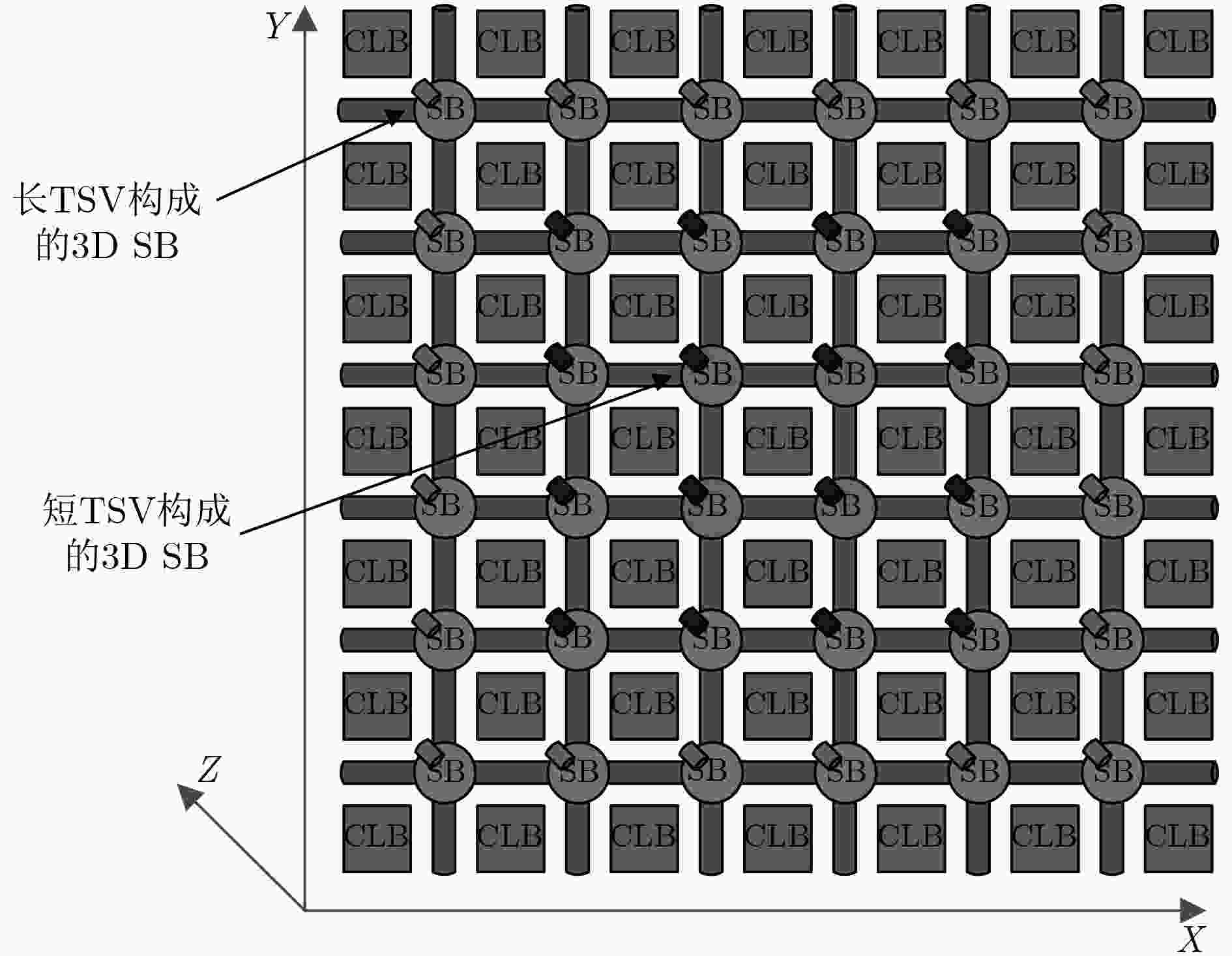

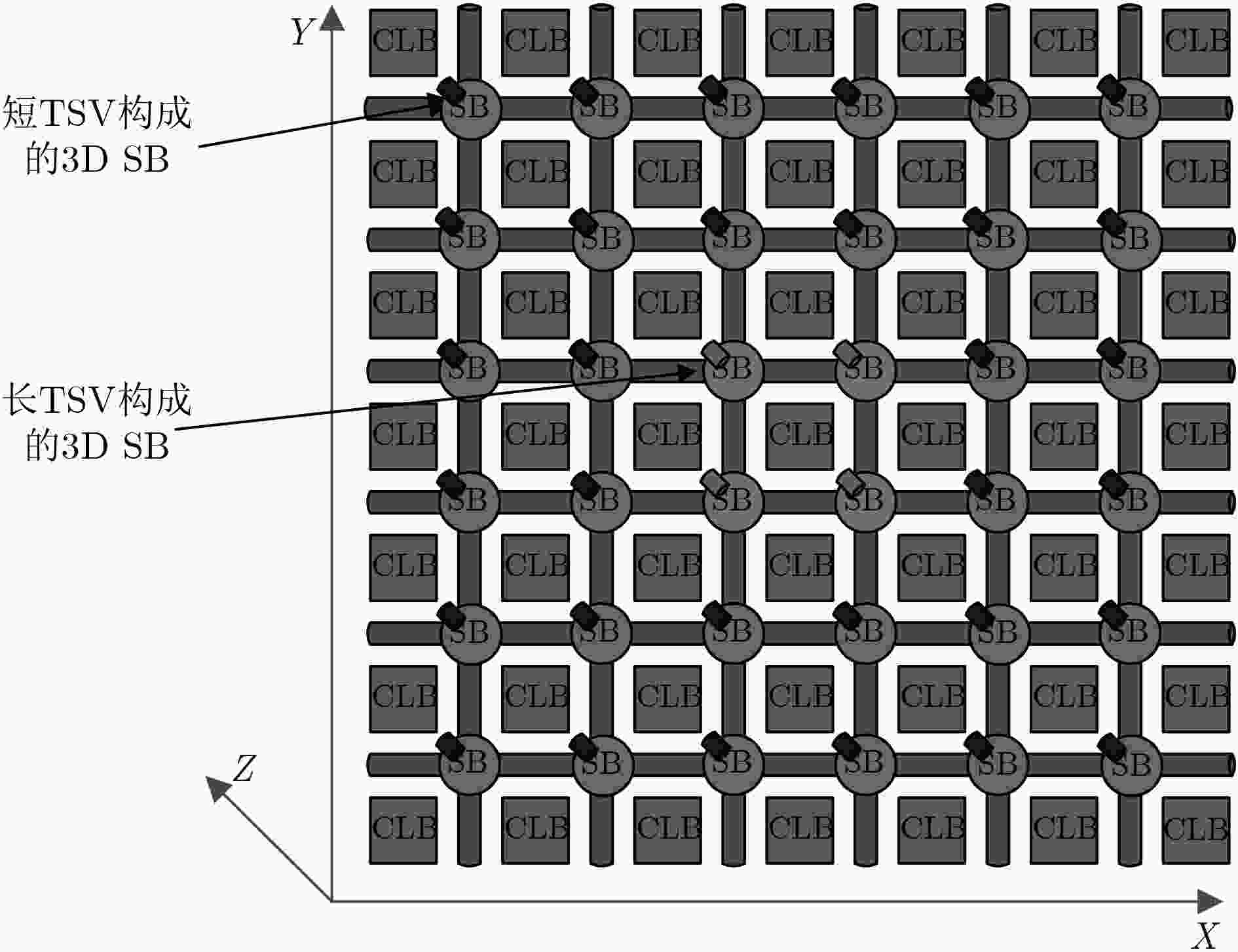

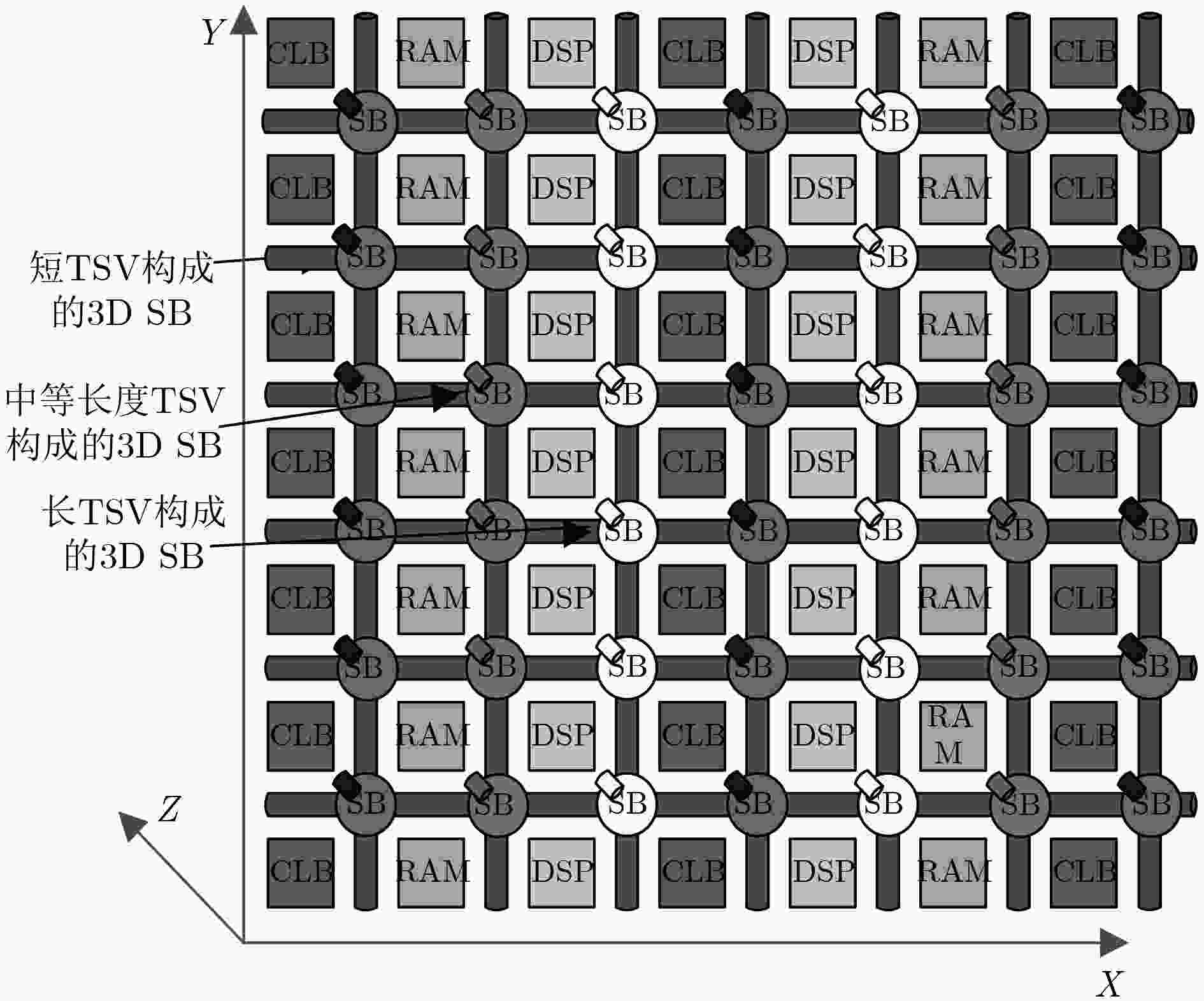

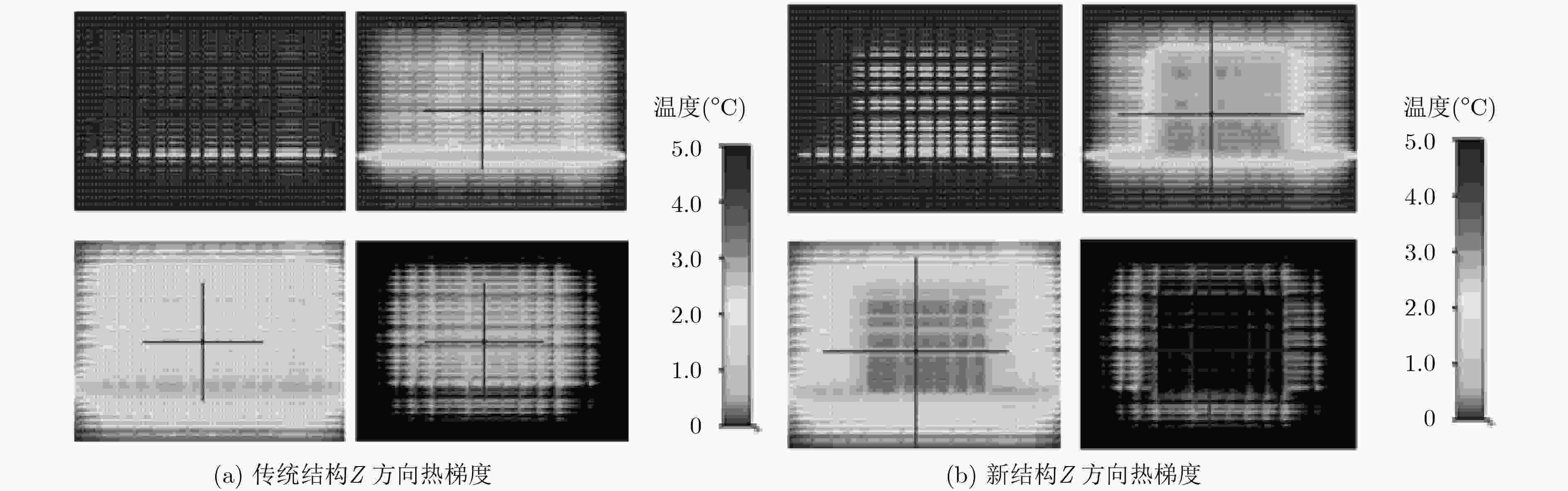

摘要: 该文针对3维FPGA (3D FPGA)芯片存在的散热问题,提出具有低热梯度特征的互连网络通道结构,力图解决传统FPGA匀称互连通道设计在芯片堆叠实现上产生的温度非平衡现象。该文建立了3D FPGA的热阻网络模型;对不同类型的通道线对3D FPGA的热分布影响进行了理论分析和热仿真;提出了垂直方向通道网络非均匀分布的3D FPGA通道结构,实验表明,与给定传统FPGA互连通道结构相比,采用所提方法实现的3D FPGA设计架构能够降低76.8%的层间最高温度梯度,10.4%的层内温度梯度。

-

关键词:

- 3维现场可编程门阵列 /

- 非均匀通道结构 /

- 热分布

Abstract: To solve the problem of heat dissipation in Three Dimensional Field Programmable Gate Array Technology (3D FPGA), an interconnect channel architectural design method with low thermal gradient feature is proposed. A thermal resistance network model is established for the 3D FPGA, and theoretical studies and thermal simulation experiments are carried out on the influence of different types of channels on the thermal performance of 3D FPGA. Further, non-uniform vertical direction channel structures of 3D FPGA are proposed. Experiments indicate that 3D FPGA designed using the method proposed can reduce the maximum temperature gradient between different layers by 76.8% and the temperature gradient within the same layer by 10.4% compared with the traditional channel structure of 3D FPGA. -

表 1 两种情况的热阻值

热阻 错开放置 对齐放置 R1 RTS+RGR RTS R2 RTS+RGR RTS R3 RTS+RGR RTS R4 RAM RAM 表 2 封装材料设置

部件 材料 尺寸 切片 Si 8 mm×6 mm TSV Cu 直径:20 μm,高度:50 μm Micro-Bump (微凸块) Cu 高度:20 μm Ceramic substrate (陶瓷衬底) 氧化铝 30 mm×30 mm BGA solder ball (BGA焊球) Sn63/Pb37 直径:0.6 mm,中心距:1 mm PCB motherboard (PCB板) FR4 30 mm×30 mm 表 3 新结构热分析统计结果

最低温度(°C) 最高温度(°C) 平均温度(°C) 切片1 40.9203 45.1598 43.6753 切片2 41.7091 45.2051 43.9975 切片3 42.1229 45.2337 44.1000 切片4 42.3739 45.2715 44.2322 表 4 层间热梯度改善情况

最低温度梯度

(°C)最高温度梯度

(°C)平均温度梯度

(°C)传统结构 1.4601 0.4824 0.6717 新结构 1.4536 0.1117 0.5569 改善比例(%) 0.4 76.8 17.1 表 5 层内热梯度改善情况

切片1 切片2 切片3 切片4 传统结构温度差(°C) 4.2112 3.6969 3.3647 3.2335 新结构温度差(°C) 4.2395 3.4960 3.1108 2.8976 改善比例(%) –0.60 5.40 7.50 10.40 -

TRIMBERGER S M. Three ages of FPGAs: A retrospective on the first thirty years of FPGA technology[J]. Proceedings of the IEEE, 2015, 103(3): 318–331. doi: 10.1109/JPROC.2015.2392104 YANG Haigang. Overview: Emerging technologies on giga-scale FPGA implementat[C]. 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 2010: 1428–1431. ZHANG Zhiping, LIAUW Y Y, CHEN Chen, et al. Monolithic 3-D FPGAs[J]. Proceedings of the IEEE, 2015, 103(7): 1197–1210. doi: 10.1109/JPROC.2015.2433954 ABABEI C, MOGAL H, and BAZARGAN K. Three-dimensional place and route for FPGAs[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006, 25(6): 1132–1140. doi: 10.1109/TCAD.2005.855945 SIOZIOS K, SOTIRIADIS K, PAVLIDIS V F, et al. A software-supported methodology for designing high-performance 3D FPGA architectures[C]. 2007 IFIP International Conference on Very Large Scale Integration, Atlanta, GA, USA, 2007: 54–59. XILINX Corporation. Xilinx stacked silicon interconnect technology delivers breakthrough FPGA capacity, bandwidth, and power efficiency[EB/OL]. http://www.xilinx.com/technology/roadmap/ssi-technology, 2012: 1–10. Intel Corporation. Intel stratix 10 GX/SX device overview[EB/OL]. http://www.intel.com/content/www/us/en/programmable/documentation/joc1442261161666.html, 2018: 3–37. SALAH K. Survey on 3D-ICs thermal modeling, analysis, and management techniques[C]. The 19th IEEE Electronics Packaging Technology Conference, Singapore, 2017: 1–4. ZHAO Yi, HAO Cong, and YOSHIMURA T. TSV assignment of thermal and wirelength optimization for 3D-IC routing[C]. The 28th International Symposium on Power and Timing Modeling, Optimization and Simulation, Platja d’Aro, Spain, 2018: 155–162. CONG J and ZHANG Yan. Thermal via planning for 3-D ICs[C]. 2005 IEEE/ACM International Conference on Computer-Aided Design, San Jose, USA, 2005: 745–752. GOPLEN B and SAPATNEKAR S S. Placement of thermal vias in 3-D ICs using various thermal objectives[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006, 25(4): 692–709. doi: 10.1109/TCAD.2006.870069 HSU P Y, CHEN H T, and HWANG T T. Stacking signal TSV for thermal dissipation in global routing for 3-D IC[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2014, 33(7): 1031–1042. doi: 10.1109/TCAD.2014.2307488 ABABEI C, MOGAL H, and BAZARGAN K. Three-dimensional place and route for FPGAs[C]. 2005 Asia and South Pacific Design Automation Conference, Shanghai, China, 2005: 773–778. PANGRACIOUS V, MEHREZ H, and MARAKCHI Z. TSV count minimization and thermal analysis for 3D tree-based FPGA[C]. 2013 International Conference on IC Design & Technology, Pavia, Italy, 2013: 223–226. PAVLIDIS V F and FRIEDMAN E G, 著. 三维集成电路设计[M]. 缪旻, 于民, 金玉丰, 译. 北京: 机械工业出版社, 2013: 1–209.PAVLIDIS V F and FRIEDMAN E G. Three-Dimensional Integrated Circuit Design[M]. MU Min, YU Min, JIN Yufeng, Translation. Beijing: Machinery Industry Press, 2013: 1–209. -

下载:

下载:

下载:

下载: