A Capacitor-less Low Dropout Regulator with Fast Response

-

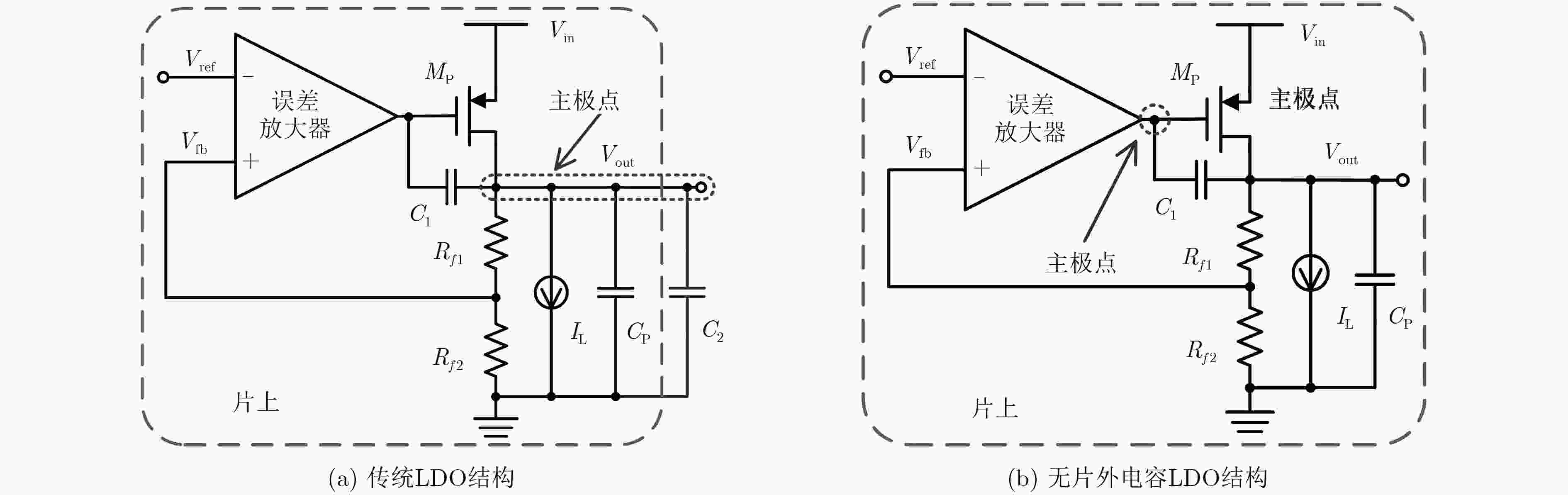

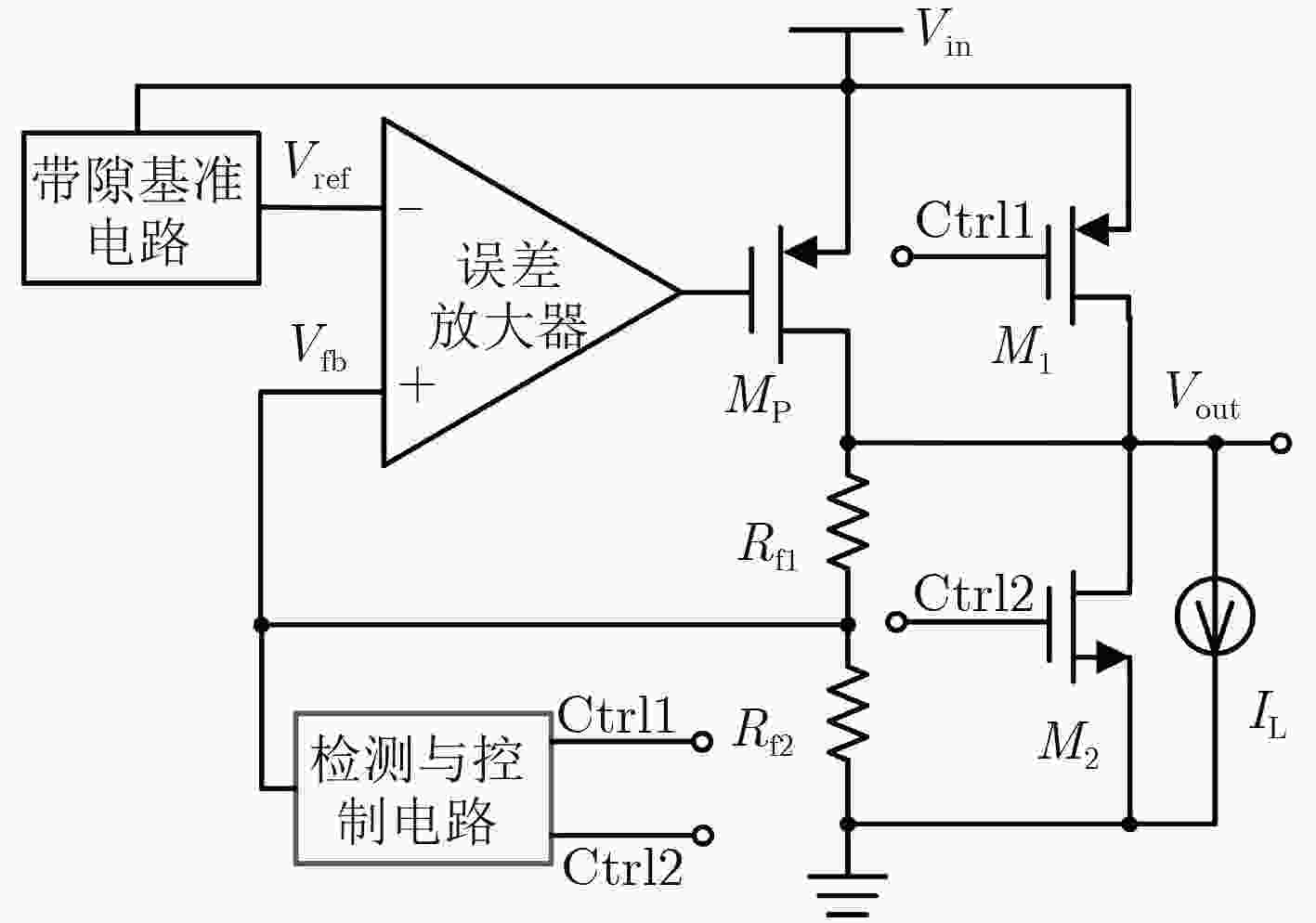

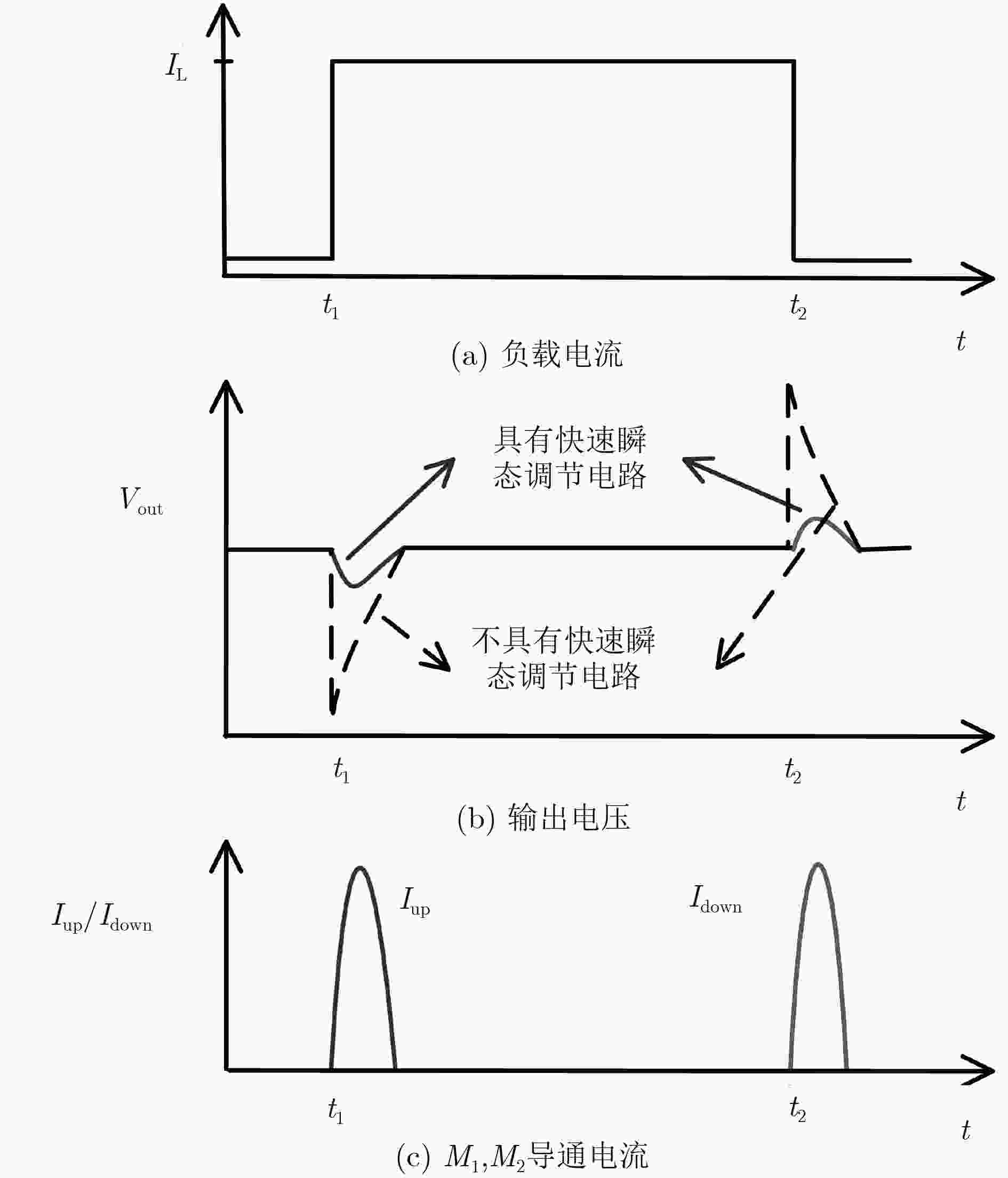

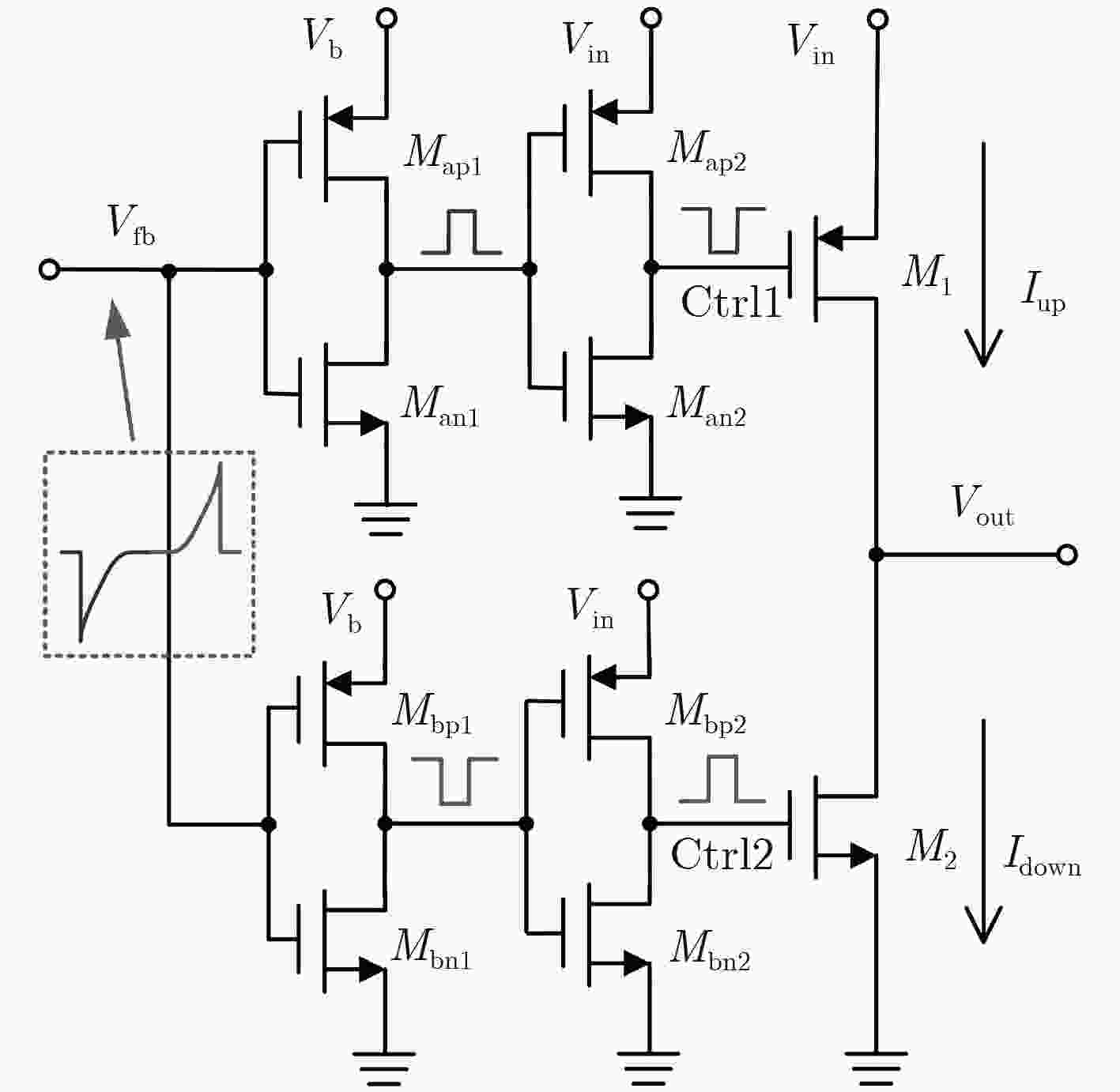

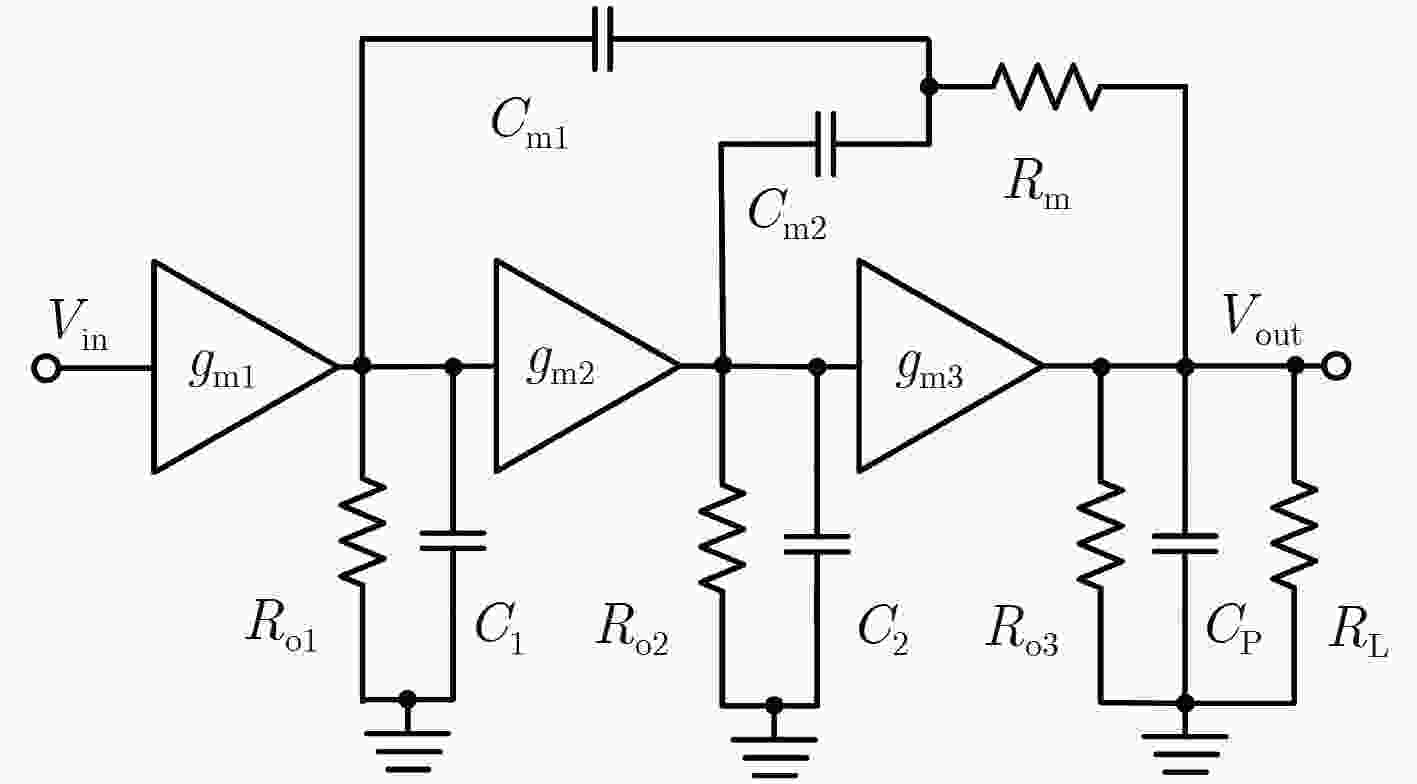

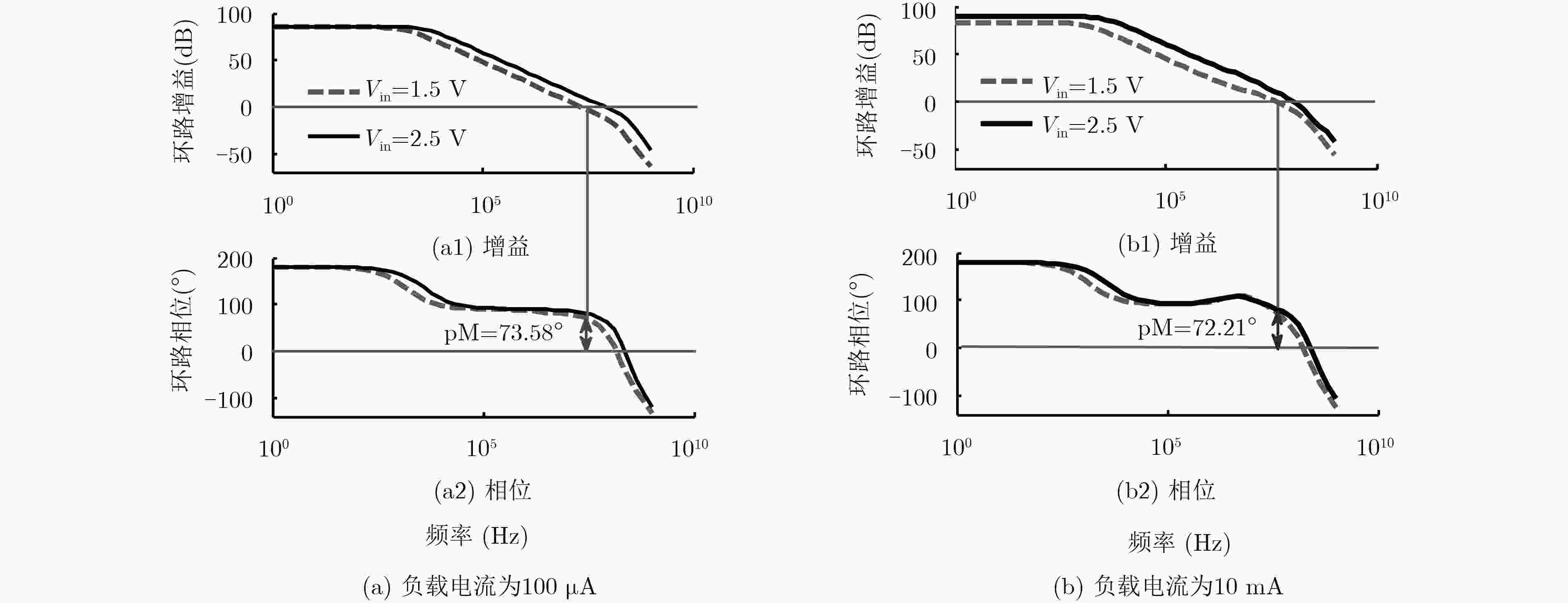

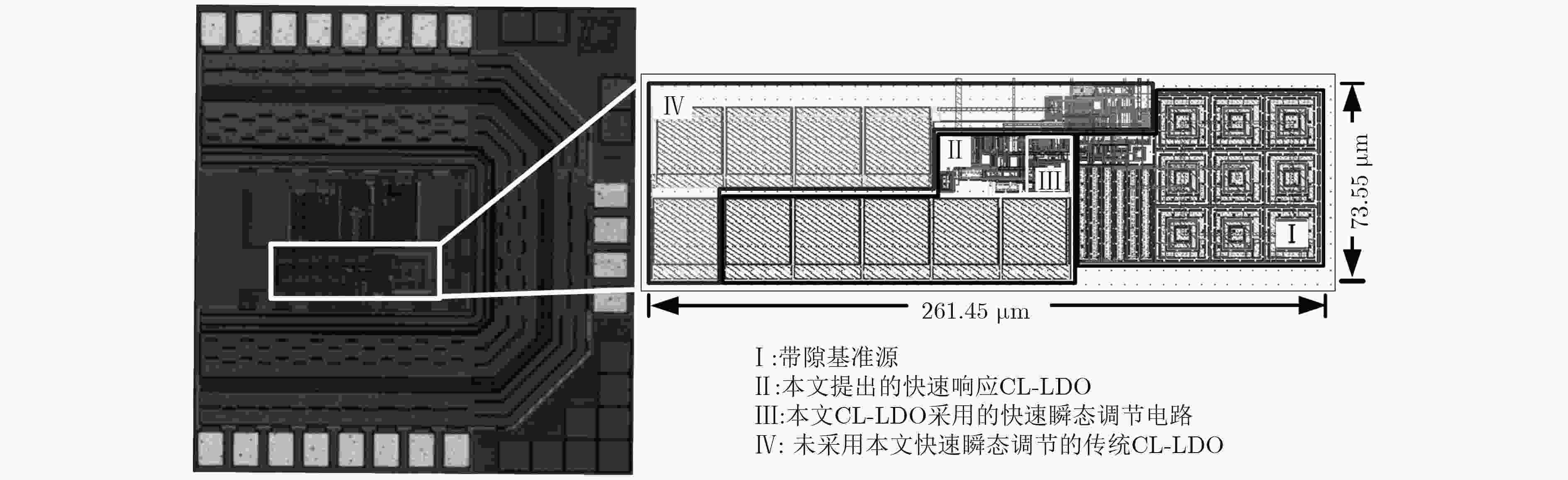

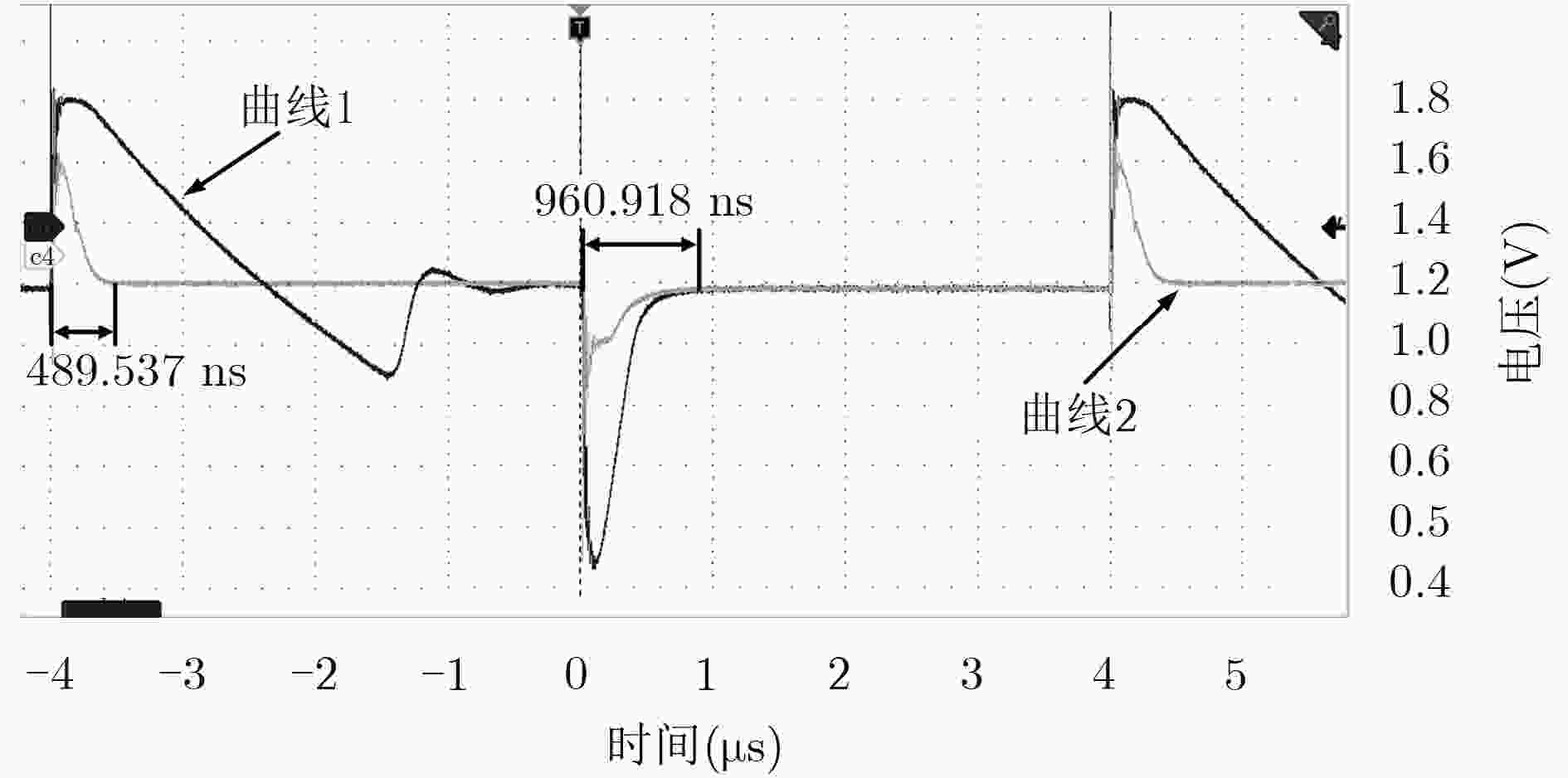

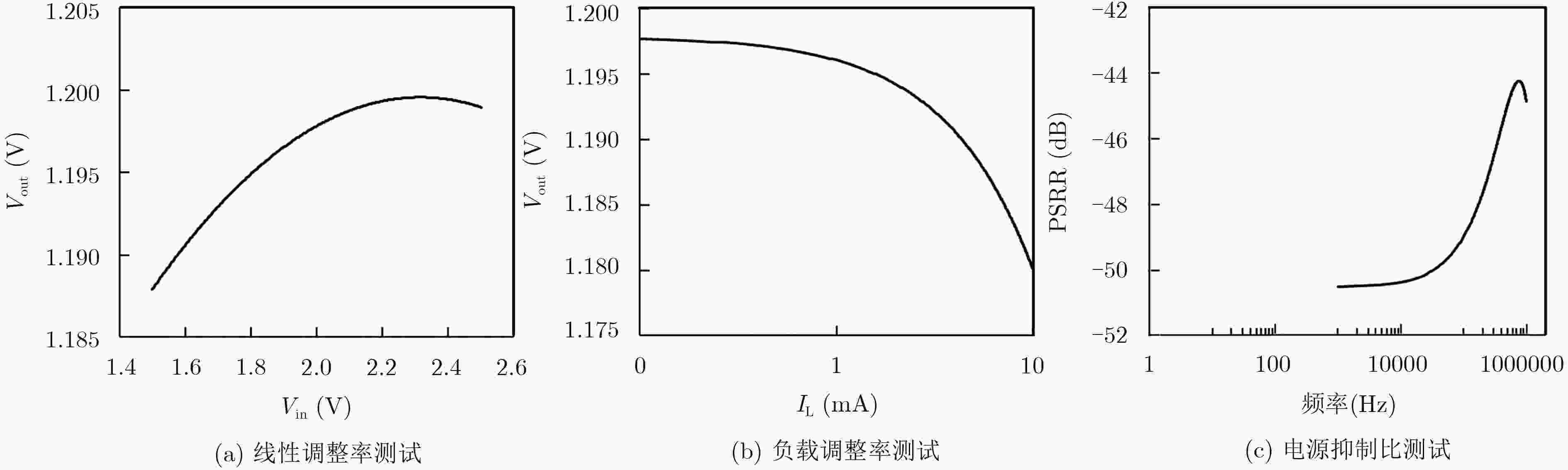

摘要: 为了改善负载跳变对低压差线性稳压器(LDO)的影响,该文提出一种用于无片外电容LDO(CL-LDO)的新型快速响应技术。通过增加一条额外的快速通路,实现CL-LDO的快速瞬态响应,并且能够减小LDO输出过冲和下冲的幅度。该文电路基于0.18 μm CMOS工艺设计实现,面积为0.00529 mm2。流片测试结果表明,当输入电压范围为1.5~2.5 V时,输出电压为1.194 V;当负载电流以 1 μs的上升时间和下降时间在 100 μA~10 mA之间变化时,CL-LDO的过冲恢复时间为489.537 ns,下冲恢复为960.918 ns;相比未采用该技术的传统CL-LDO,响应速度能够提高7.41倍,输出过冲和下冲的电压幅值能够分别下降35.3%和78.1%。Abstract: A novel technique for increasing the load response speed of Capacitor-Less Low-DropOut linear regulator (CL-LDO) is proposed to improve the transient response of CL-LDO when its load current changes. With an additional fast signal feedback path, the CL-LDO can achieve fast transient response so that the overshoot and undershoot of its output voltage can be dramatically reduced. A CL-LDO with fast response is realized in 0.18 μm CMOS and occupies an active area of 0.00529 mm2. The CL-LDO has an output voltage of 1.194 V when the input supply voltage ranges from 1.5 V to 2.5 V. When the load current changes from 100 μA to 10 mA with the rise and fall time of 1 μs, the output of LDO can be recovered from its overshoot and undershoot to a stable voltage within 489.537 ns and 960.918 ns, respectively. Compared with a traditional CL-LDO without this proposed technique, the transient response speed of this CL-LDO is increased by 7.41 times. The overshoot and undershoot of the output voltage is decreased by 35.3% and 78.1%, respectively.

-

Key words:

- Low-DropOut (LDO) regulator /

- Capacitor-less /

- Fast transient response /

- Small area

-

表 1 控制信号Ctrl1和Ctrl2的工作原理

IL Vfb Ctrl1 Ctrl2 M1 M2 升高 下冲/<0.70 V 低电平 低电平 导通 关断 降低 过冲/>0.90 V 高电平 高电平 关断 导通 稳定 稳定/=0.80 V 高电平 低电平 关断 关断 表 2 本文设计的CL-LDO与其它文献的CL-LDO性能比较

参数 文献[13]* 文献[14] 文献[15] 文献[16] 本文 W/O W 工艺 (nm) 180 65 180 130 180 Vin (V) 1.2 1.2 1.2~1.8 1~1.4 1.5~2.5 Vout (V) 1 1 0.8~1.6 0.8 1.2 IL (mA) 100 0.1~25 1-100 0.12~25 0.1~10 过冲/下冲 (mV) 220 225 200 284 597/946 386/207 环路增益 (dB) – – >59.8 75 85~87 85~87 负载调整率 (mV/mA) 0.023 0.042 0.081 0.173 0.97 0.96 线性调整率 (mV/V) 0.69 3.8 – 2.25 11.3 10.0 恢复时间 (μs) 3.6* 1.3† 0.22† 0.19# 3.624* 0.489* 电源抑制比 (dB) 49.6 52 – 57 50.2 面积 (mm2) 0.022 0.087 0.031 0.008 0.00529 *考虑寄生参数的电路后仿真数据;*电流阶跃变化的上升时间和下降时间为1 μs;†电流阶跃变化的上升时间和下降时间约为300 ps;#电流阶跃变化的上升时间和下降时间约为100 ns。 -

MILLIKEN R J, SILVA-MARTINEZ J, and SANCHEZ-SINENCIO E. Full on-chip CMOS low-dropout voltage regulator[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2007, 54(9): 1879–1890. doi: 10.1109/TCSI.2007.902615 YEO J, JAVED K, LEE J, et al. A capacitorless low-dropout regulator with enhanced slew rate and 4.5-μA quiescent current[J]. Analog Integrated Circuits and Signal Processing, 2017, 90(1): 227–235. doi: 10.1007/s10470-016-0869-z TONG Xingyuan and SUN Tiantian. A programmable multi-output technique in LDO regulator for multi-reference SAR ADC application[J]. International Journal of Electronics, 2017, 104(3): 528–538. doi: 10.1080/00207217.2016.1218069 HUANG W J, LU S H, and LIU Shenluan. A capacitor-free CMOS low dropout regulator with slew rate enhancement[C]. Proceedings of 2006 International Symposium on VLSI Design, Automation and Test, Hsinchu, China, 2006: 1–4. LIU Nanqi, JOHNSON B, NADIG V, et al. A transient-enhanced fully-integrated LDO regulator for SoC application[C]. Proceedings of 2018 IEEE International Symposium on Circuits and Systems, Florence, Italy, 2018: 1–5. LEUNG K N and NG Y S. A CMOS low-dropout regulator with a momentarily current-boosting voltage buffer[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2010, 57(9): 2312–2319. doi: 10.1109/TCSI.2010.2043171 AL-SHYOUKH M, LEE H, and PEREZ R. A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation[J]. IEEE Journal of Solid-State Circuits, 2007, 42(8): 1732–1742. doi: 10.1109/JSSC.2007.900281 TONG Xingyuan and WEI Kangkang. A fully integrated fast-response LDO voltage regulator with adaptive transient current distribution[C]. Proceedings of 2017 IEEE Computer Society Annual Symposium on VLSI, Bochum, Germany, 2017: 651–654. MARANO D, GRASSO A D, PALUMBO G, et al. Optimized active single-miller capacitor compensation with inner half-feedforward stage for very high-load three-stage OTAs[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2016, 63(9): 1349–1359. doi: 10.1109/TCSI.2016.2573920 ZENG Yanhan, LI Yuao, ZHANG Xin, et al. A push-pulled FVF based output-capacitorless LDO with adaptive power transistors[J]. Microelectronics Journal, 2017, 64: 69–77. doi: 10.1016/j.mejo.2017.04.008 LEUNG K N and MOK P K T. Analysis of multistage amplifier-frequency compensation[J]. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 2001, 48(9): 1041–1056. doi: 10.1109/81.948432 AAMIR S A, HARIKUMAR P, and WIKNER J J. Frequency compensation of high-speed, low-voltage CMOS multistage amplifiers[C]. Proceedings of 2013 IEEE International Symposium on Circuits and Systems, Beijing, China, 2013: 381–384. SHIRMOHAMMADLI V, SABERKARI A, MARTINEZ-GARCIA H, et al. Low power output-capacitorless class-AB CMOS LDO regulator[C]. Proceedings of 2017 IEEE International Symposium on Circuits and Systems, Baltimore, USA, 2017: 1–4. LIM Y, LEE J, PARK S, et al. An external capacitorless low-dropout regulator with high PSR at all frequencies from 10 kHz to 1 GHz using an adaptive supply-ripple cancellation technique[J]. IEEE Journal of Solid-State Circuits, 2018, 53(9): 2675–2685. doi: 10.1109/JSSC.2018.2841984 TANG Jun, LEE J, and ROH J. Low-power fast-transient capacitor-less LDO regulator with high slew-rate Class-AB amplifier[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2019, 66(3): 462–466. doi: 10.1109/TCSII.2018.2865254 BU Shi, GUO Jianping, and LEUNG K N. A 200-ps-response-time output-capacitorless low-dropout regulator with unity-gain bandwidth >100 MHz in 130-nm CMOS[J]. IEEE Transactions on Power Electronics, 2018, 33(4): 3232–3246. doi: 10.1109/TPEL.2017.2711017 -

下载:

下载:

下载:

下载: