A Low-latency Depth Modelling Mode-1 Encoder in 3D-high Efficiency Video Coding Standard

-

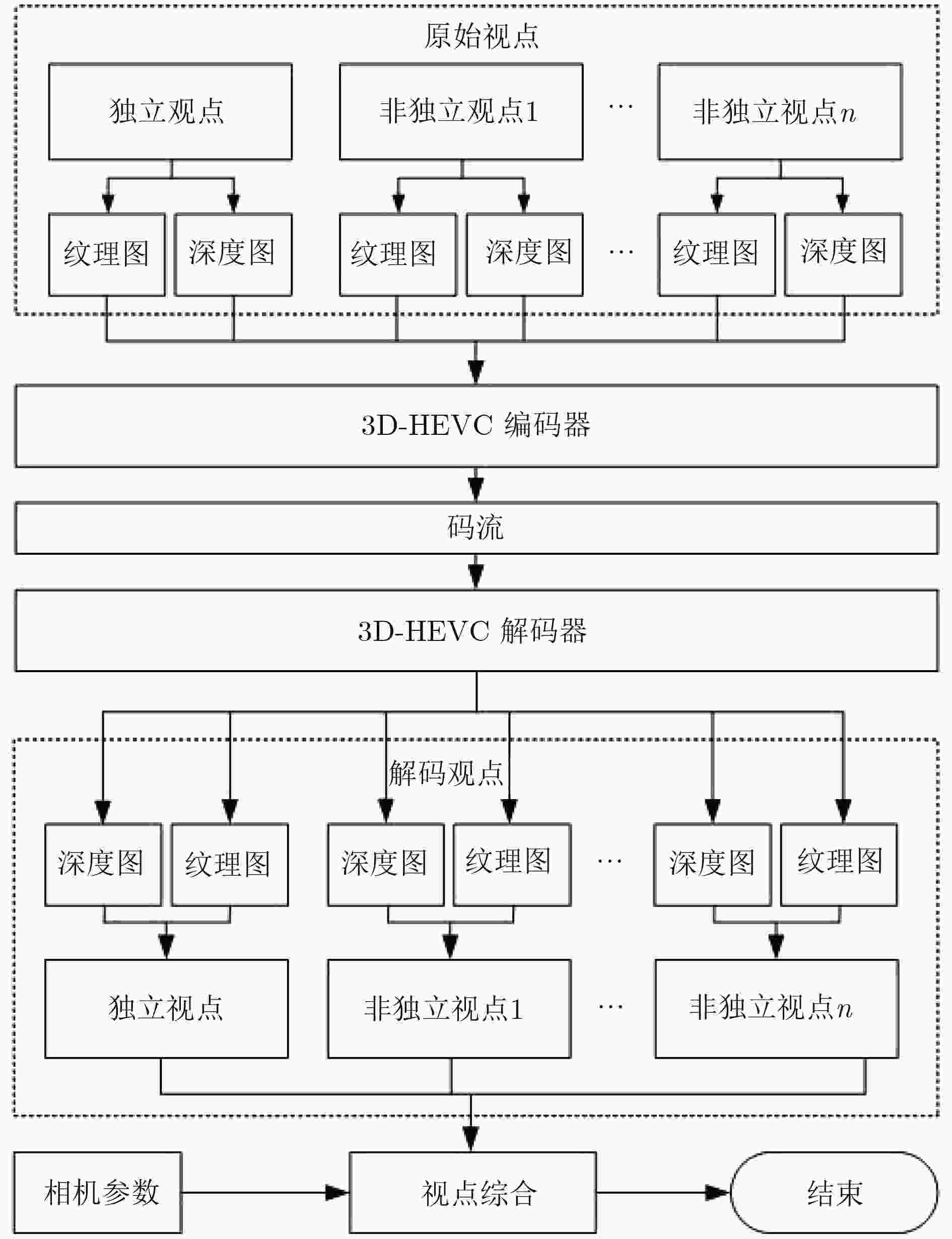

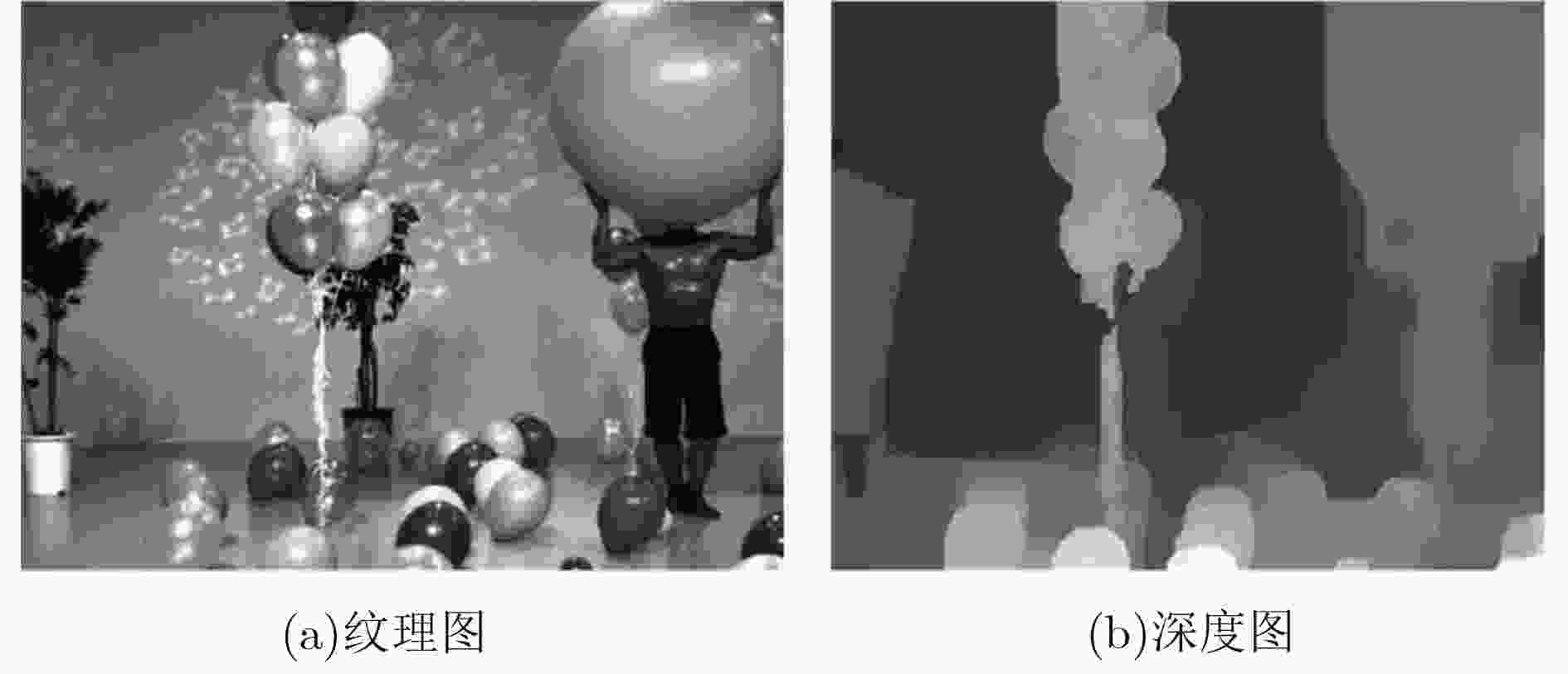

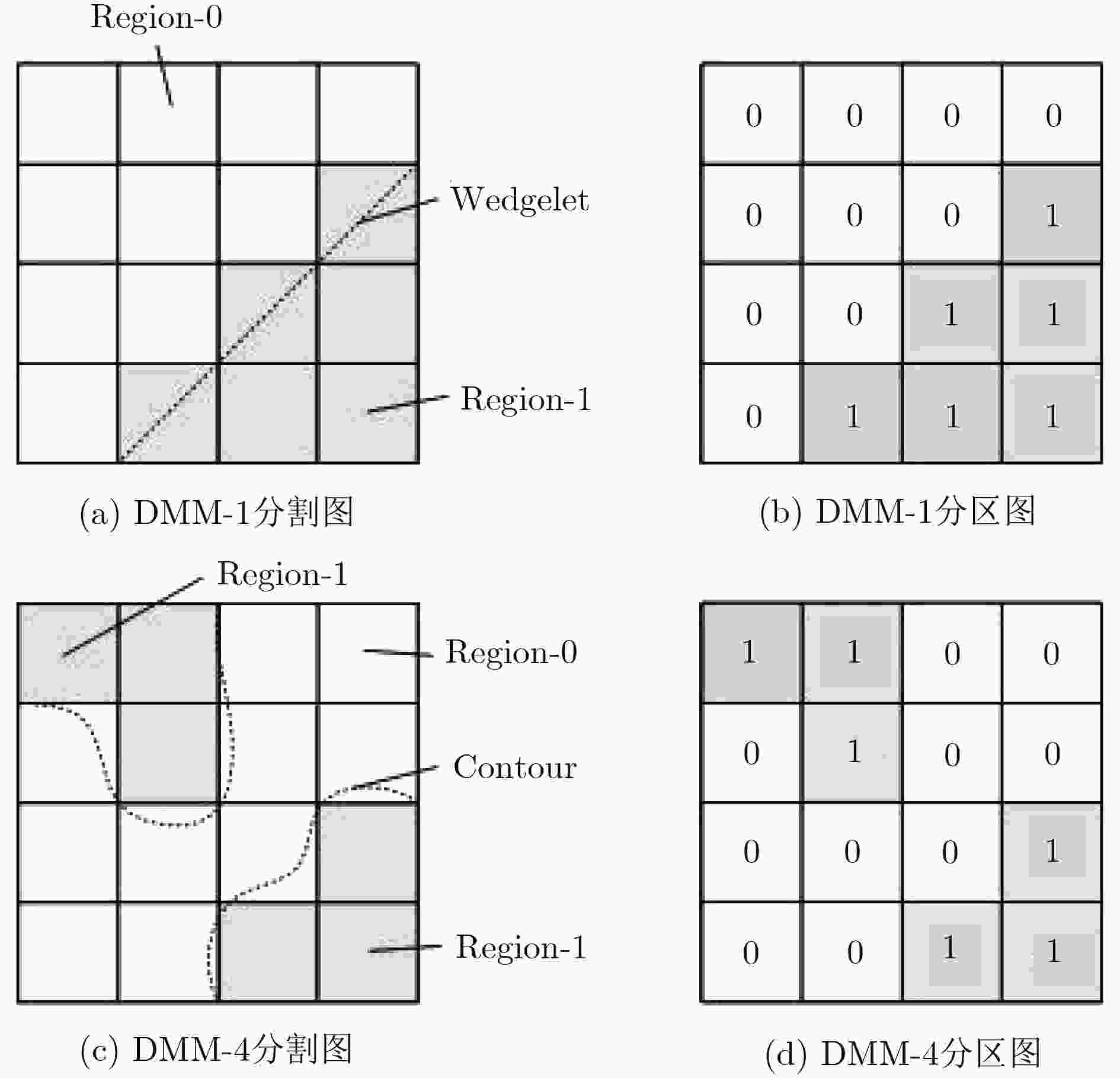

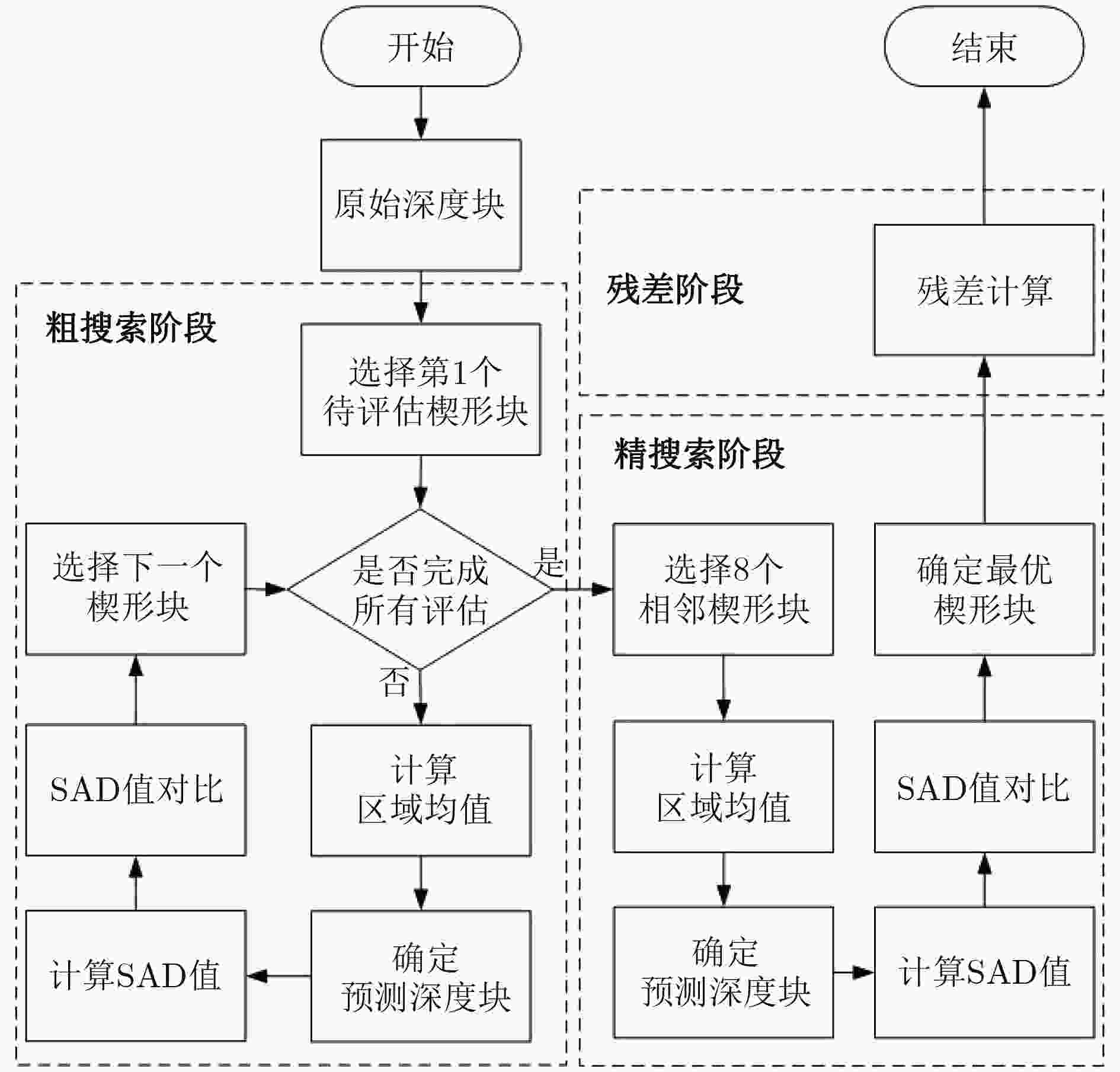

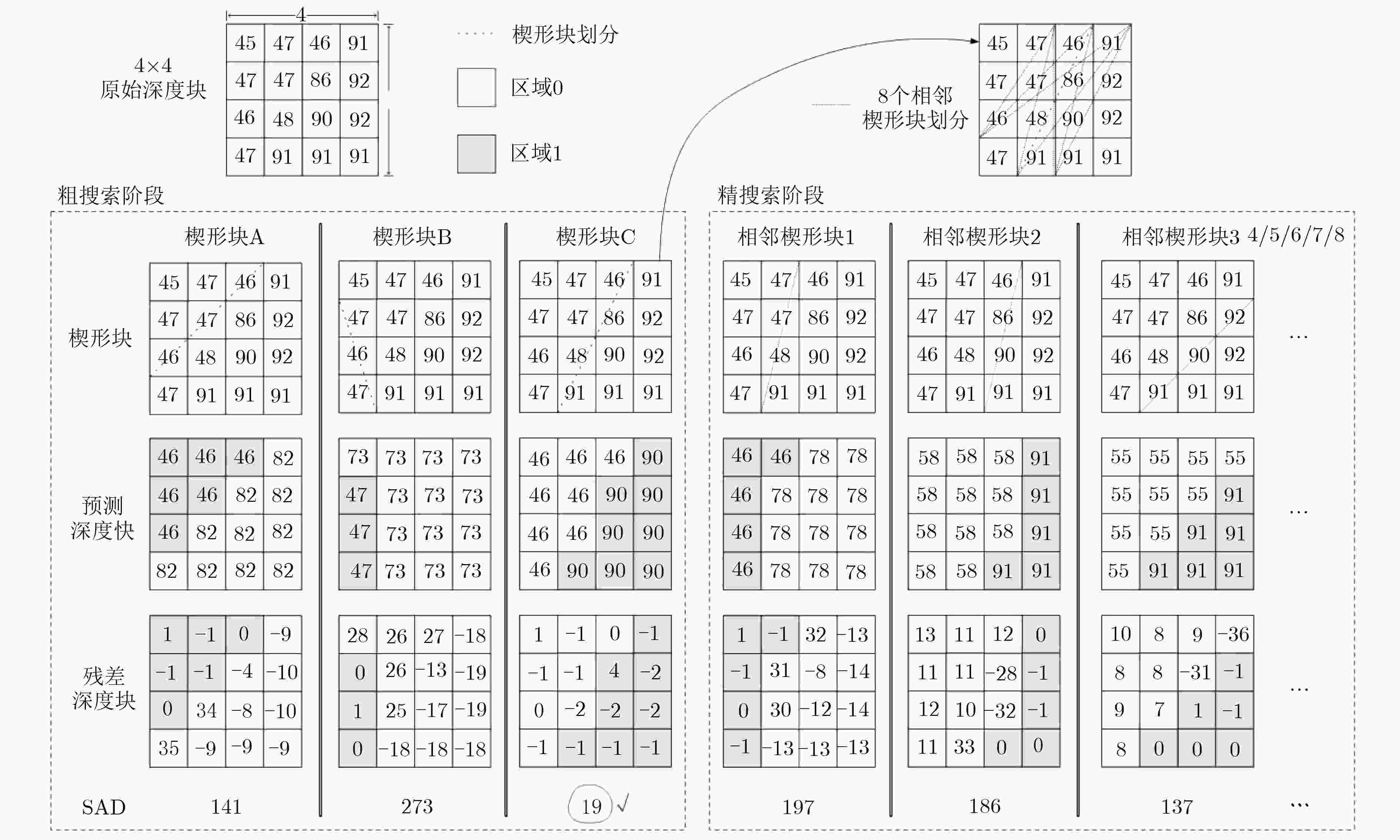

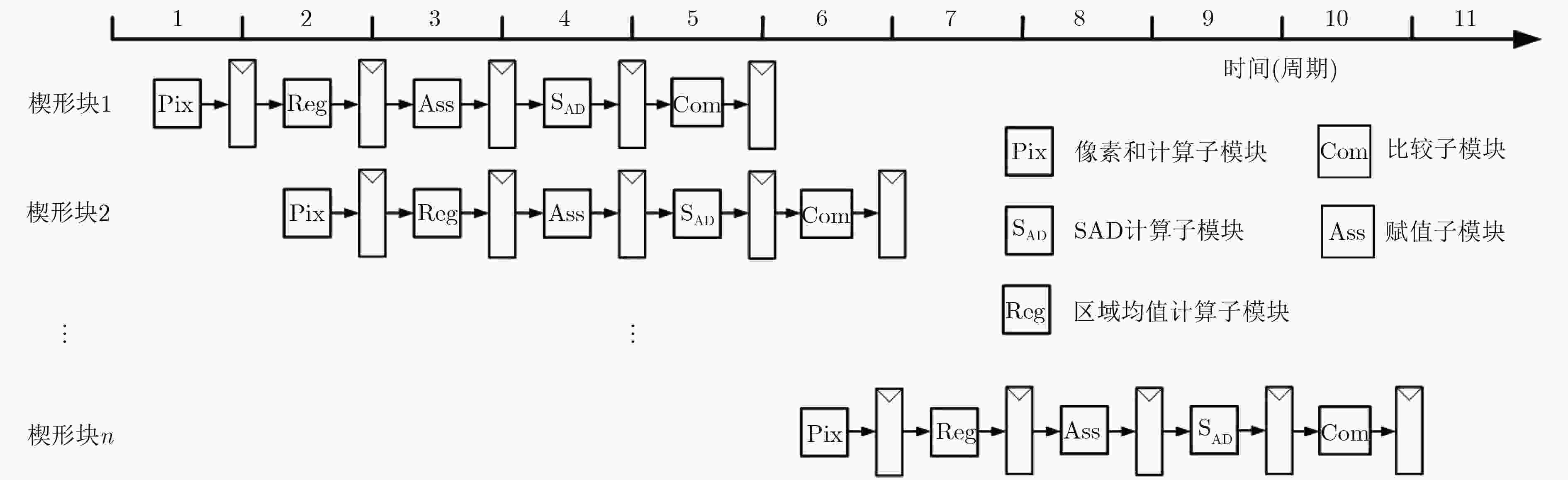

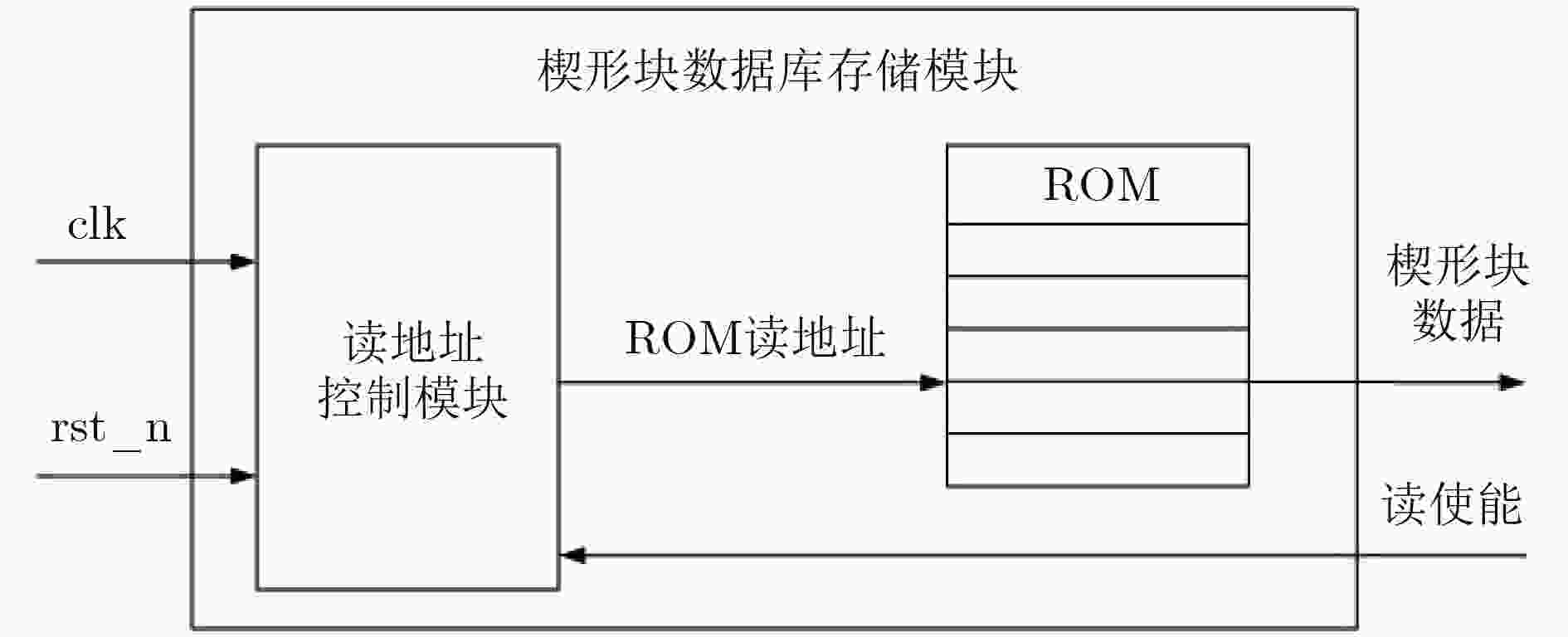

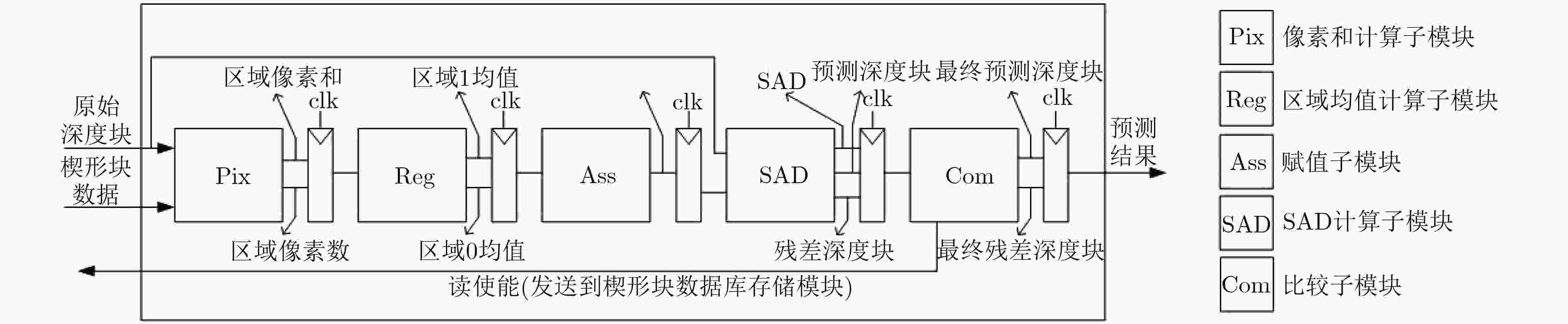

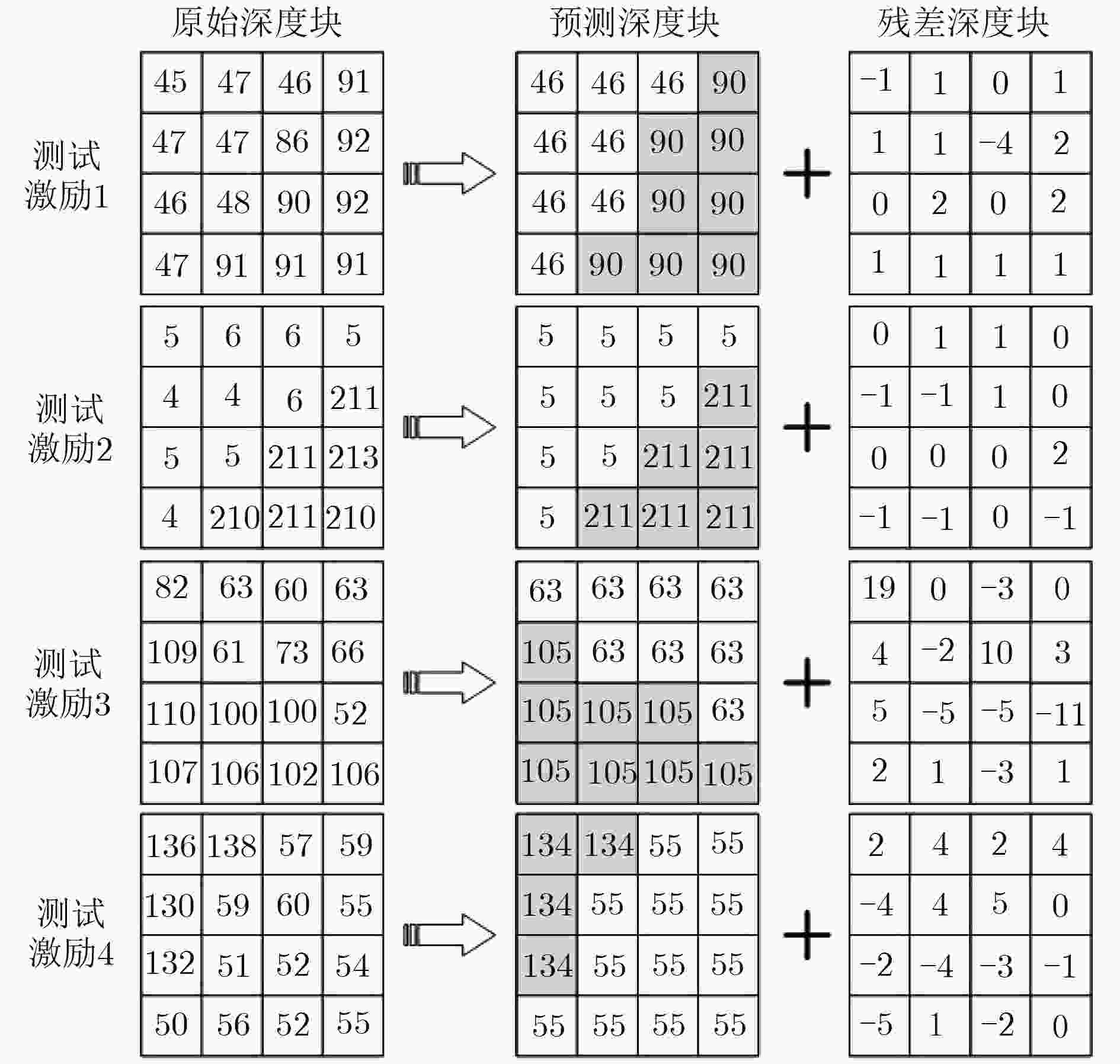

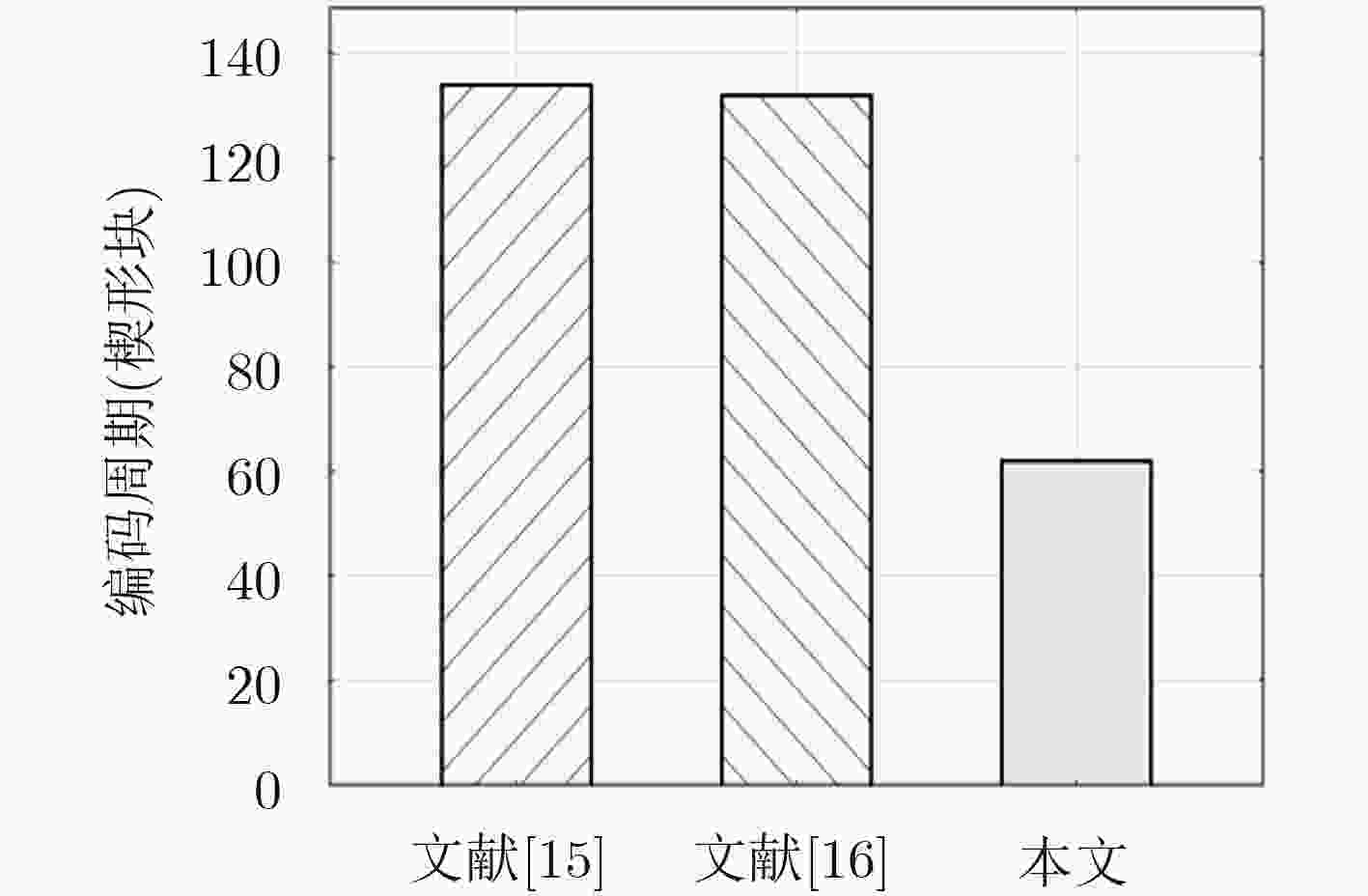

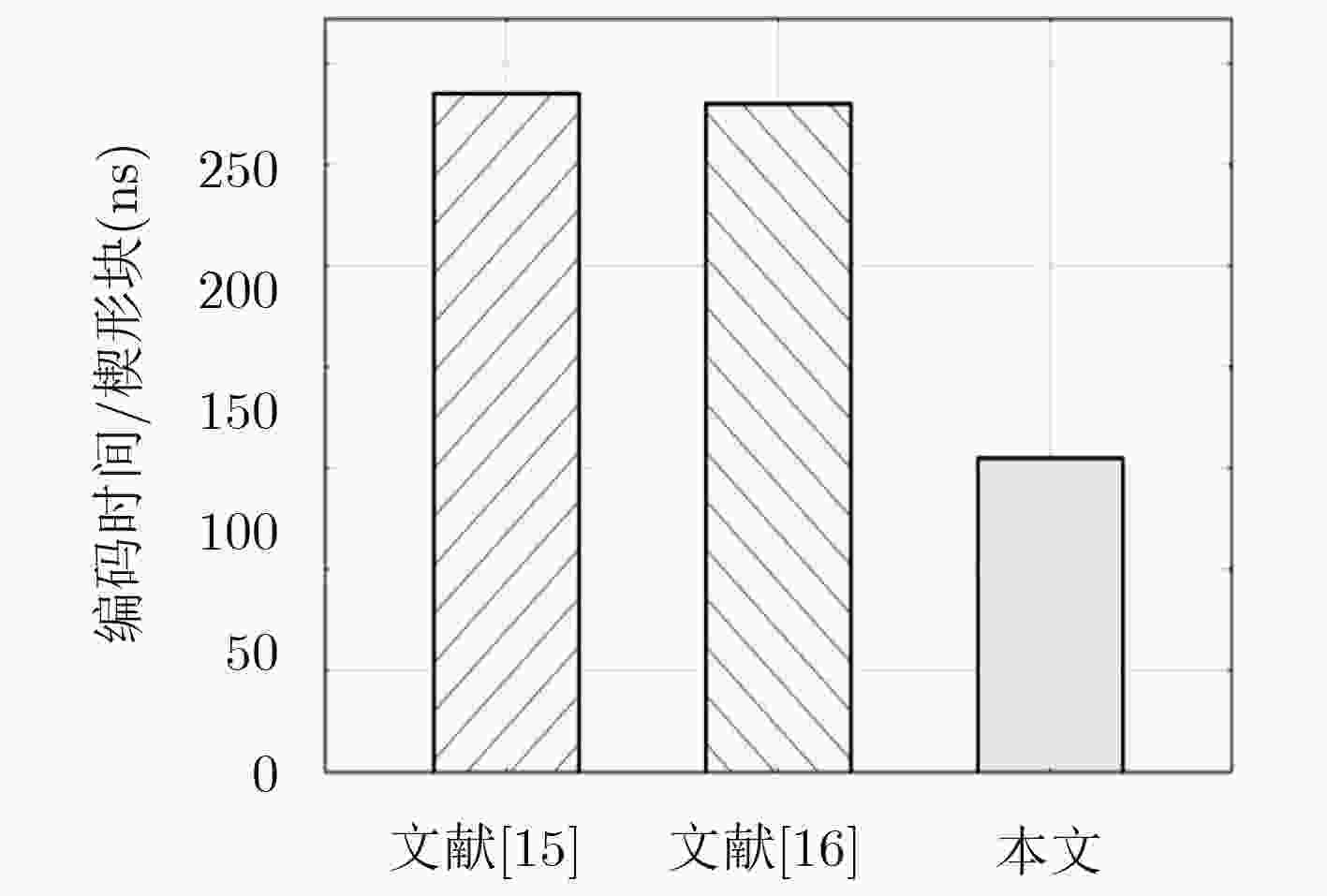

摘要: 为了更好地对3D视频中深度图进行编码,该文将3维高效视频编码(3D-HEVC)标准新引入了深度建模模式(DMMs),新模式在提高了编码质量的同时改进了原有算法的复杂度。在设计DMM-1编码器电路时,传统架构电路的编码周期均较长,只能满足较低分辨率和帧率的视频实时编码要求。为了进一步提高3D-HEVC中DMM-1编码器的性能,该文对DMM-1算法架构进行了研究,针对其中楔形块评估无数据相关性的特点,提出了一种5级流水线架构的DMM-1编码器硬件电路,以期能够降低一个深度块编码所需的编码周期,并使用Verilog HDL进行实现。实验表明:该架构与Sanchez等人(2017年)的工作相比,以电路门数增加约1568门为代价,可减少至少52.3%的编码周期。Abstract: In order to encode better the depth maps in 3D video, the 3D-High Efficiency Video Coding (3D-HEVC) standard is introduced in Depth Modeling Modes(DMMs), which increase the quality of original algorithm while improving the encoding complexity. The traditional architecture of DMM-1 encoder circuit has a longer coding period and can only meet real-time coding requirements of lower resolution and frame rate. In order to improve the performance of DMM-1 encoder, the structure of DMM-1 algorithm is researched and a five-stage pipeline architecture of DMM-1 encoder is proposed. The pipeline architecture can reduce the coding cycles. The architecture is implemented by Verilog HDL. Experiments show that this architecture can reduce the coding cycle by at least 52.3%, at the cost of 1568 gates compared to previous work by Sanchez G. et al. (2017).

-

表 1 深度图帧内预测模式序号和名称

模式序号 模式名称 0 Planar 1 DC 2~34 Directional 35 DMM-1 36 DMM-4 -

LEE J Y, WEY H C, and PARK D S. A fast and efficient Multi-View depth image coding method based on temporal and Inter-View correlations of texture images[J]. IEEE Transactions on Circuits and Systems for Video Technology, 2011, 21(12): 1859–1868. doi: 10.1109/TCSVT.2011.2154730 SHEN Liquan, ZHANG Zhaoyang, and LIU Zhi. Inter mode selection for depth map coding in 3D video[J]. IEEE Transactions on Consumer Electronics, 2012, 58(3): 926–931. doi: 10.1109/TCE.2012.6311338 CERNIGLIARO G, JAUREGUIZAR F, CABRERA J, et al. Low complexity mode decision and motion estimation for H.264/AVC based depth maps encoding in free viewpoint video[J]. IEEE Transactions on Circuits and Systems for Video Technology, 2013, 23(5): 769–783. doi: 10.1109/TCSVT.2012.2223632 MÜLLER K, MERKLE P, TECH G, et al. 3D video coding with depth modeling modes and view synthesis optimization[C]. Proceedings of 2012 Asia Pacific Signal and Information Processing Association Annual Summit and Conference, Hollywood, USA, 2012: 1–4. ZHANG Qiuwen, LI Nana, HUANG Lixun, et al. Effective early termination algorithm for depth map intra coding in 3D-HEVC[J]. Electronics Letters, 2014, 50(14): 994–996. doi: 10.1049/el.2014.0065. GU Zhouye, ZHENG Jianhua, LING N, et al. Fast depth modeling mode selection for 3D HEVC depth intra coding[C]. Proceedings of 2013 IEEE International Conference on Multimedia and Expo Workshops, San Jose, USA, 2013: 1–4. GU Zhouye, ZHENG Jianhua, LING N, et al. " 3D-CE5.h related: Fast intra prediction mode selection for intra depth map coding[C]. Proceedings of the 5th Meeting of Joint Collaborative Team on 3D Video Coding Extension Development (JCT-3V) of ITU-T SG 16 WP 3 and ISO/IEC JTC 1/SC 29/WG 11, Vienna, Austria, 2013: 3–5. GUO Ruixue, HE Gang, LI Yunsong, et al. Fast algorithm for prediction unit and mode decisions of intra depth coding in 3D-HEVC[C]. Proceedings of 2016 IEEE International Conference on Image Processing, Phoenix, Arizona, USA, 2016: 1121–1125. LI Kun. The research of intra mode coding for the depth maps[D]. [Master dissertation], Shenzhen University, 2016: 24–49. 粘春湄, 陈婧, 曾焕强. 纹理类型预判和SDC优化的3D-HEVC深度图帧内算法[J]. 计算机科学与探索, 2018, 12(6): 994–1003. doi: 10.3778/j.issn.1673-9418.1711040NIAN Chunmei, CHEN Jing, and ZENG Huanqiang. Depth map intra algorithm for 3D-HEVC by prejudging texture type and SDC optimization[J]. Journal of Frontiers of Computer Science and Technology, 2018, 12(6): 994–1003. doi: 10.3778/j.issn.1673-9418.1711040 SANCHEZ G, SALDANHA M, BALOTA G, et al. Complexity reduction for 3D-HEVC depth maps intra-frame prediction using simplified edge detector algorithm[C]. Proceedings of 2014 IEEE International Conference on Image Processing, Paris, France, 2014: 3209–3213. SANCHEZ G, SALDANHA M, BALOTA G, et al. A complexity reduction algorithm for depth maps intra prediction on the 3D-HEVC[C]. Proceedings of 2014 IEEE Visual Communications and Image Processing Conference, Valletta, Malta, 2014: 134–140. SANCHEZ G, SALDANHA M, ZATT B, et al. S-GMOF: A gradient-based complexity reduction algorithm for depth-maps intra prediction on 3D-HEVC[C]. Proceedings of the 6th Latin American Symposium on Circuits & Systems, Montevideo, Uruguay, 2015: 1–4. SALDANHA M, ZATT B, PORTO M, et al. Solutions for DMM-1 complexity reduction in 3D-HEVC based on gradient calculation[C]. Proceedings of the 7th Latin American Symposium on Circuits & Systems, Florianopolis, Brazil, 2016: 211–214. SANCHEZ G, MARCON C, and AGOSTINI L. Real-time scalable hardware architecture for 3D-HEVC bipartition modes[J]. Journal of Real-time Image Processing, 2017, 13(1): 71–83. doi: 10.1007/s11554-016-0609-8 SANCHEZ G, AGOSTINI L, MÓR F, et al. Low-area scalable hardware architecture for DMM-1 encoder of 3D-HEVC video coding standard[C]. Proceedings of the 30th Symposium on Integrated Circuits and Systems Design, Fortaleza, Brazil, 2017: 36–40. -

下载:

下载:

下载:

下载: