|

GHALLAB Y H and ISMAIL Y. CMOS based lab-on-a-chip: applications, challenges and future trends[J]. IEEE Circuits and Systems Magazine, 2014, 14(2): 27–47. doi: 10.1109/MCAS.2014.2314264

|

|

FANG Yuan, YU Ningmei, JIANG Yuquan, et al. High-precision lens-less flow cytometer on a chip[J]. Micromachines, 2018, 9(5): 227. doi: 10.3390/mi9050227

|

|

HUANG Xiwei, JIANG Yu, LIU Xu, et al. Machine learning based single-frame super-resolution processing for lensless blood cell counting[J]. Sensors, 2016, 16(11): E1836. doi: 10.3390/s16111836

|

|

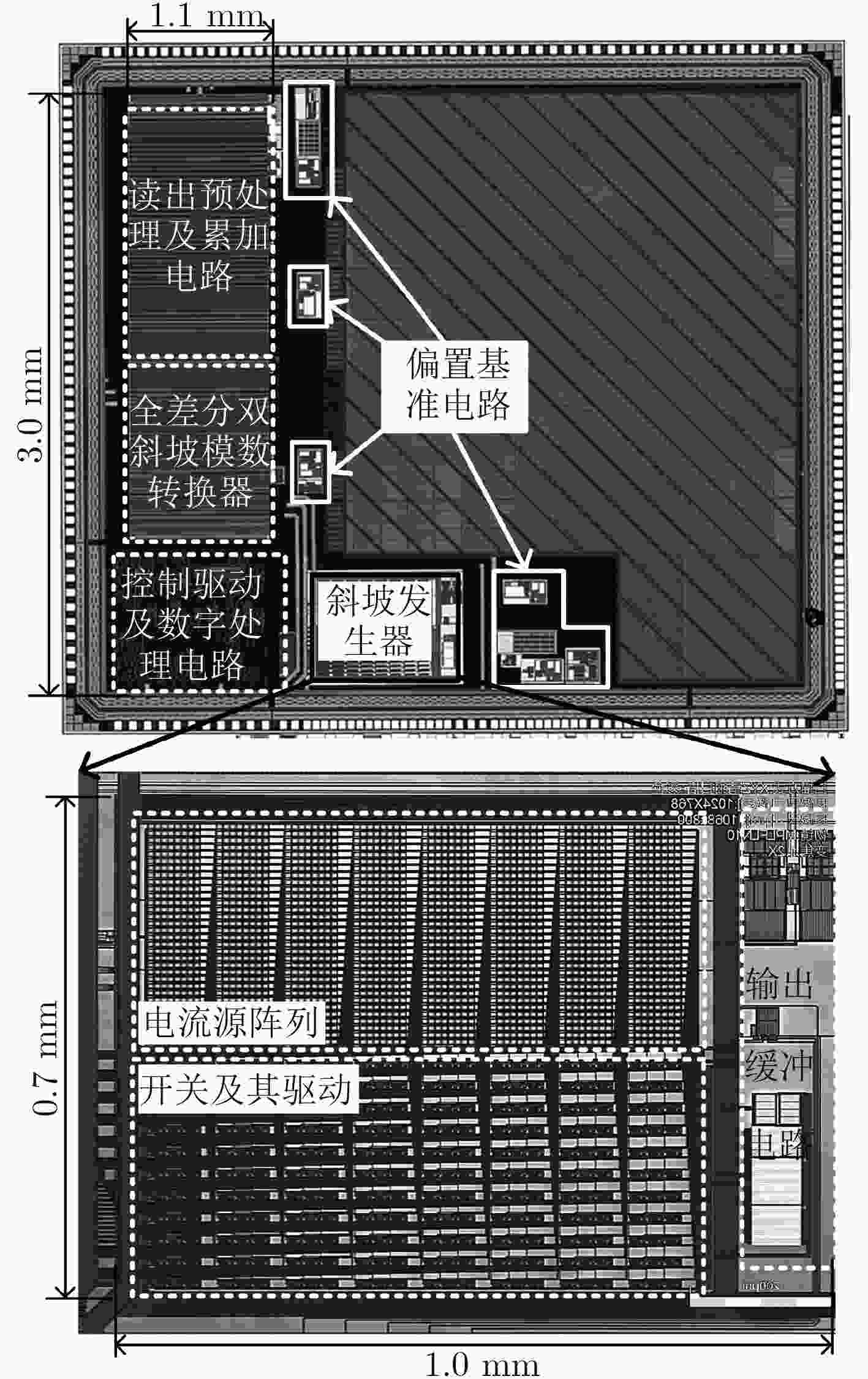

LIU Xu, HUANG Xiwei, JIANG Yu, et al. A microfluidic cytometer for complete blood count with a 3.2-Megapixel, 1.1-μm-Pitch super-resolution image sensor in 65-nm BSI CMOS[J]. IEEE Transactions on Biomedical Circuits and Systems, 2017, 11(4): 794–803. doi: 10.1109/TBCAS.2017.2697451

|

|

YIN C, LIAO Ting, LIU Kuanlin, et al. A 32-stage 15-b digital time-delay integration linear CMOS image sensor with data prediction switching technique[J]. IEEE Transactions on Electron Devices, 2017, 64(3): 1167–1173. doi: 10.1109/TED.2017.2655143

|

|

KIM D and SONG M. An enhanced dynamic-range CMOS image sensor using a digital logarithmic single-slope ADC[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2012, 59(10): 653–657. doi: 10.1109/TCSII.2012.2213359

|

|

JEON B K, HONG S K, and KWON O K. A low-power 10-bit single-slope ADC using power gating and multi-clocks for CMOS image sensors[C]. Proceedings of 2016 International SoC Design Conference, Jeju, South Korea, 2016: 257–258.

|

|

SNOEIJ M F, THEUWISSEN A J P, MAKINWA K A A, et al. Multiple-ramp column-parallel ADC architectures for CMOS image sensors[J]. IEEE Journal of Solid-State Circuits, 2007, 42(12): 2968–2977. doi: 10.1109/JSSC.2007.908720

|

|

PARK H, LEE J, KIM J, et al. High frame rate VGA CMOS image sensor using two-step single slope ADCs[C]. Proceedings of 2016 IEEE Asia Pacific Conference on Circuits and Systems, Jeju, South Korea, 2016: 571–572.

|

|

LYU Nan, YU Ningmei, and ZHANG Hejiu. A high-speed column-parallel time-digital single-slope ADC for CMOS image sensors[J]. IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 2016, E99-A(2): 555–559. doi: 10.1587/transfun.E99.A.555

|

|

KIM D, SONG M, CHOE B, et al. A multi-resolution mode CMOS image sensor with a novel two-step single-slope ADC for intelligent surveillance systems[J]. Sensors, 2017, 17(7): E1497. doi: 10.3390/s17071497

|

|

XIA Yu, NIE Kaiming, XU Jiangtao, et al. A two-step analog accumulator for CMOS TDI image sensor with temporal undersampling exposure method[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016, 24(3): 1104–1117. doi: 10.1109/TVLSI.2015.2439262

|

|

SHIRAI E. CMOS multistage preamplifier design for high-speed and high-resolution comparators[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2007, 54(2): 166–170. doi: 10.1109/TCSII.2006.883091

|

|

ZHU Y, CHAN C H, CHIO U F, et al. A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2010, 45(6): 1111–1121. doi: 10.1109/JSSC.2010.2048498

|

|

TANG Kai, MENG Qiao, WANG Zhigong, et al. A low power 20 GHz comparator in 90 nm COMS technology[J]. Journal of Semiconductors, 2014, 35(5): 055002. doi: 10.1088/1674-4926/35/5/055002

|

|

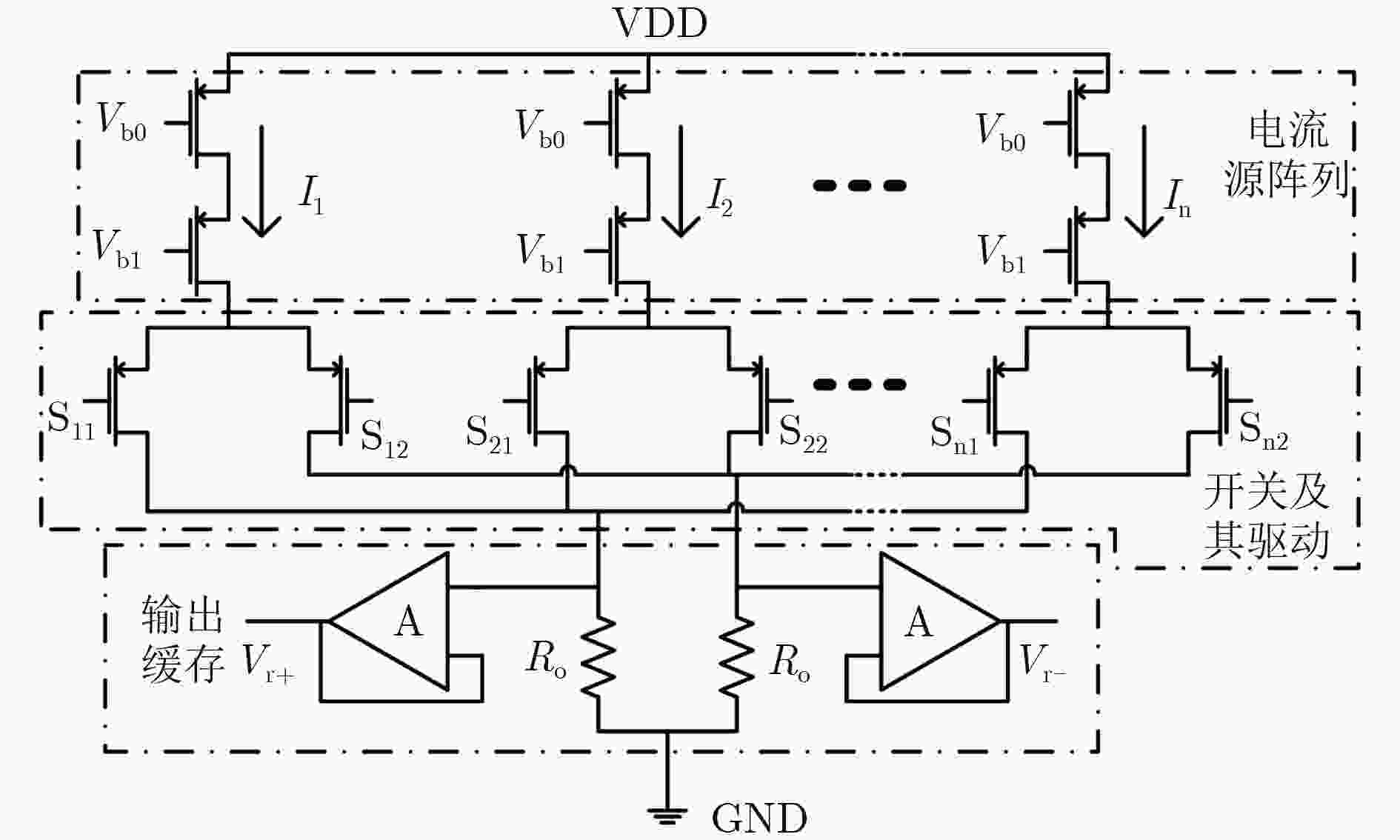

RAZAVI B. The current-steering DAC[J]. IEEE Solid-State Circuits Magazine, 2018, 10(1): 11–15. doi: 10.1109/MSSC.2017.2771102

|

|

MAO Wei, LI Yongfu, HENG C H, et al. High dynamic performance current-steering DAC design with nested-segment structure[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018, 26(5): 995–999. doi: 10.1109/TVLSI.2018.2791462

|

下载:

下载:

下载:

下载: