Sample and Hold Front-end Circuit for 14-bit 210 MS/s Charge-domain ADC

-

摘要:

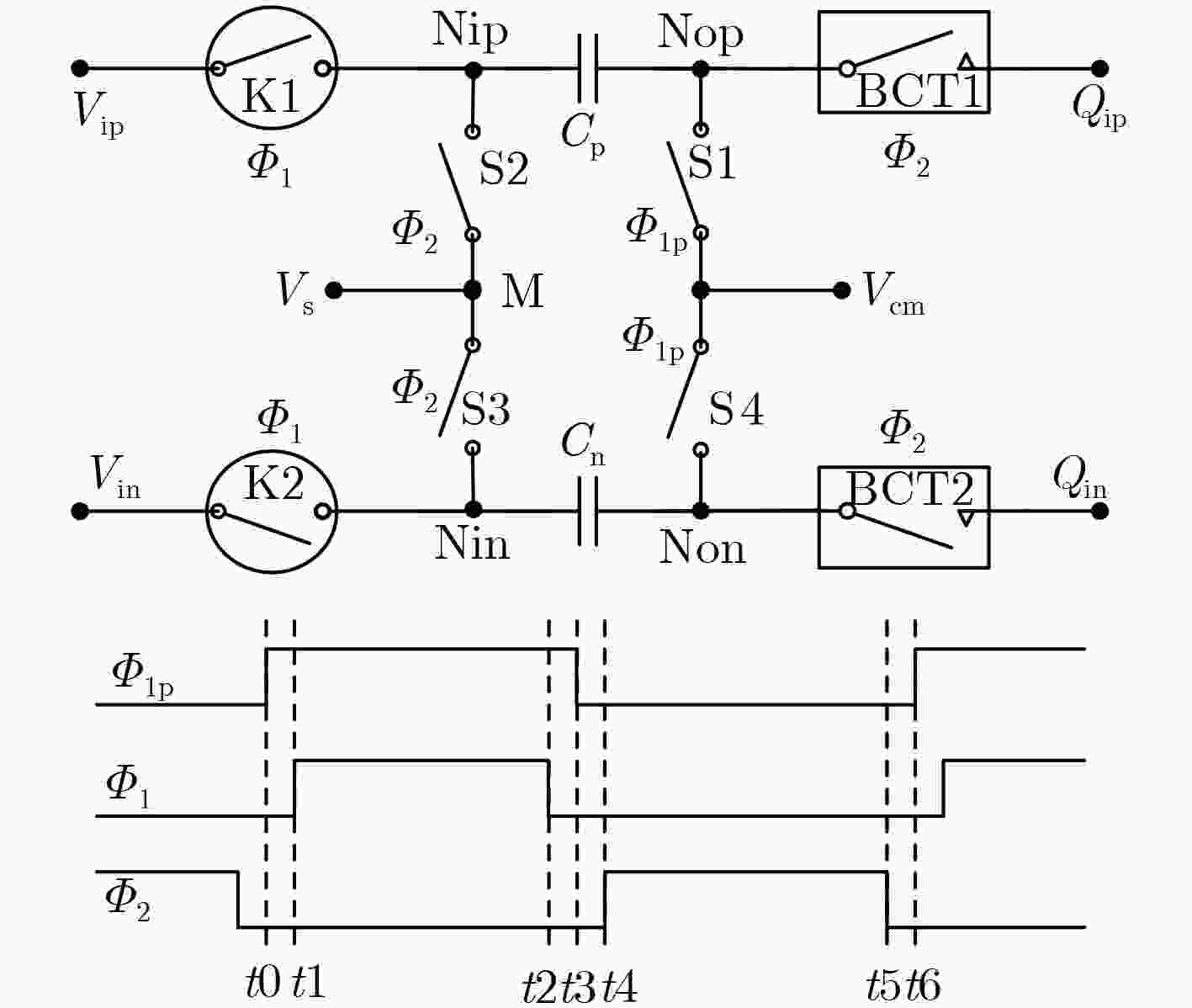

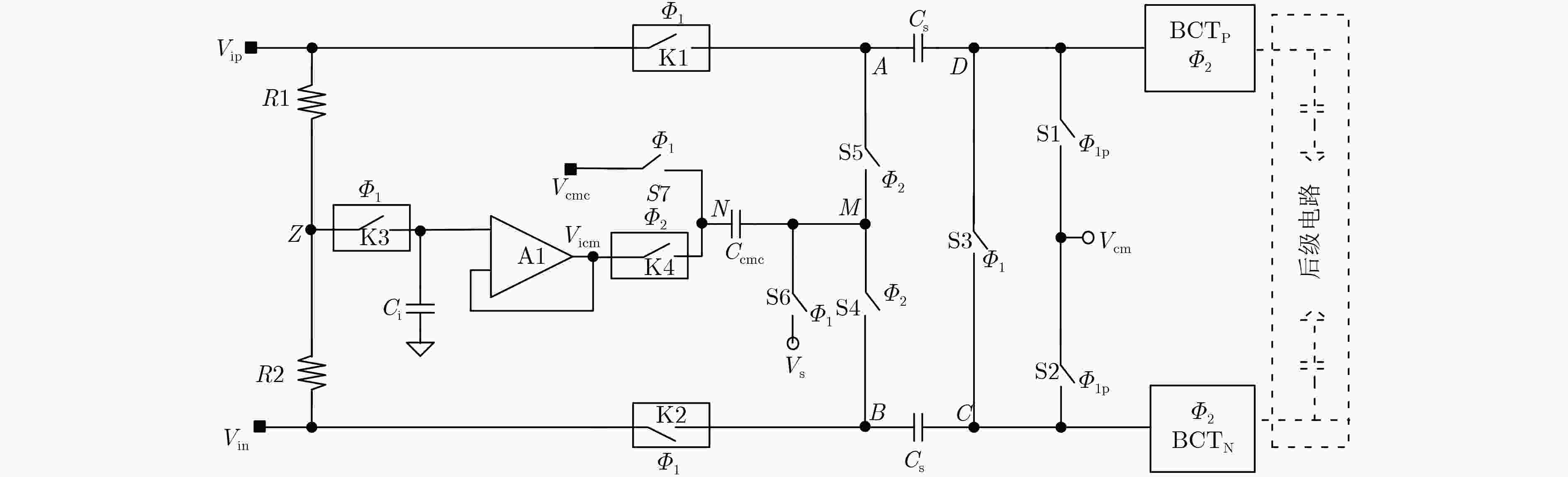

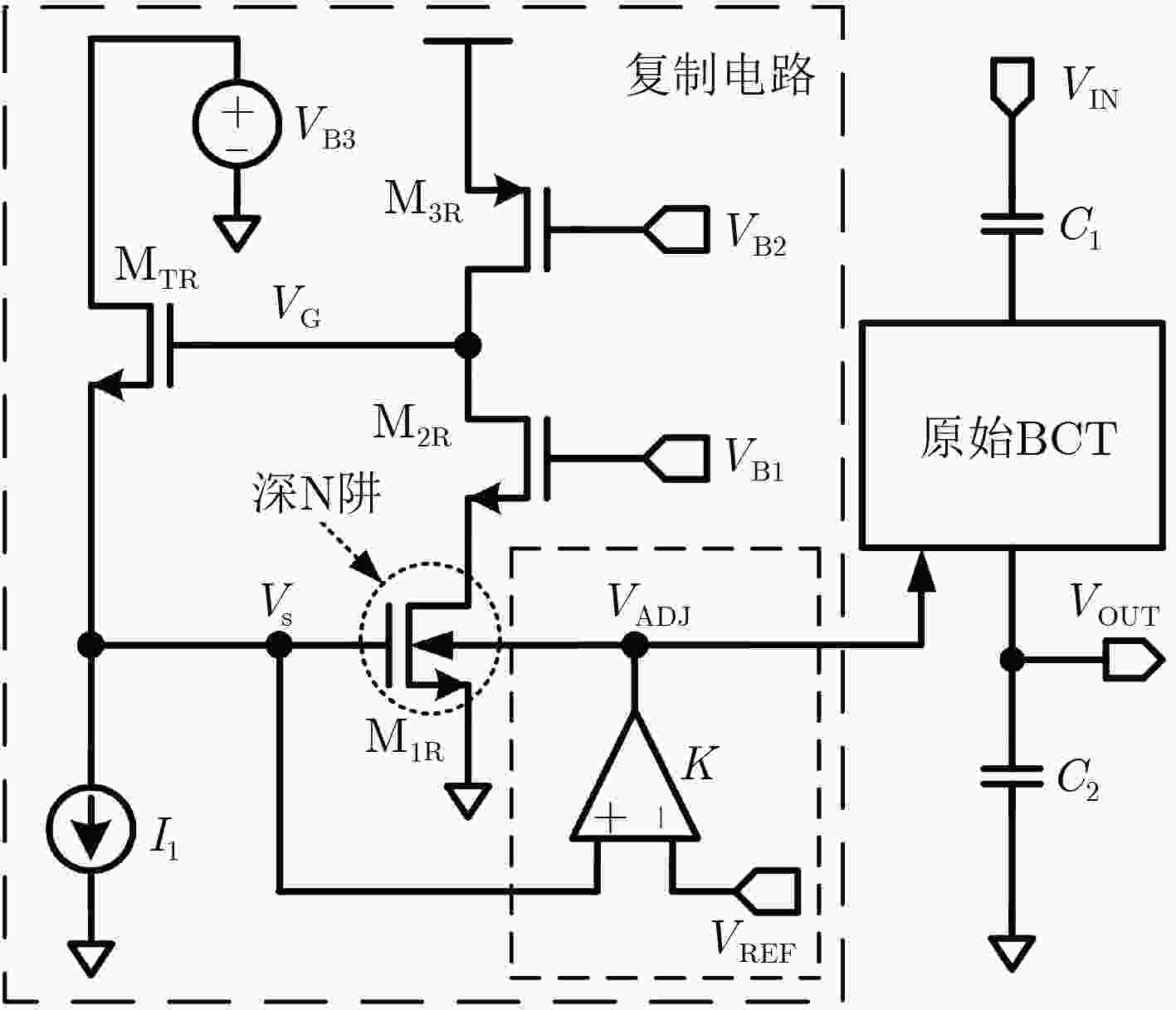

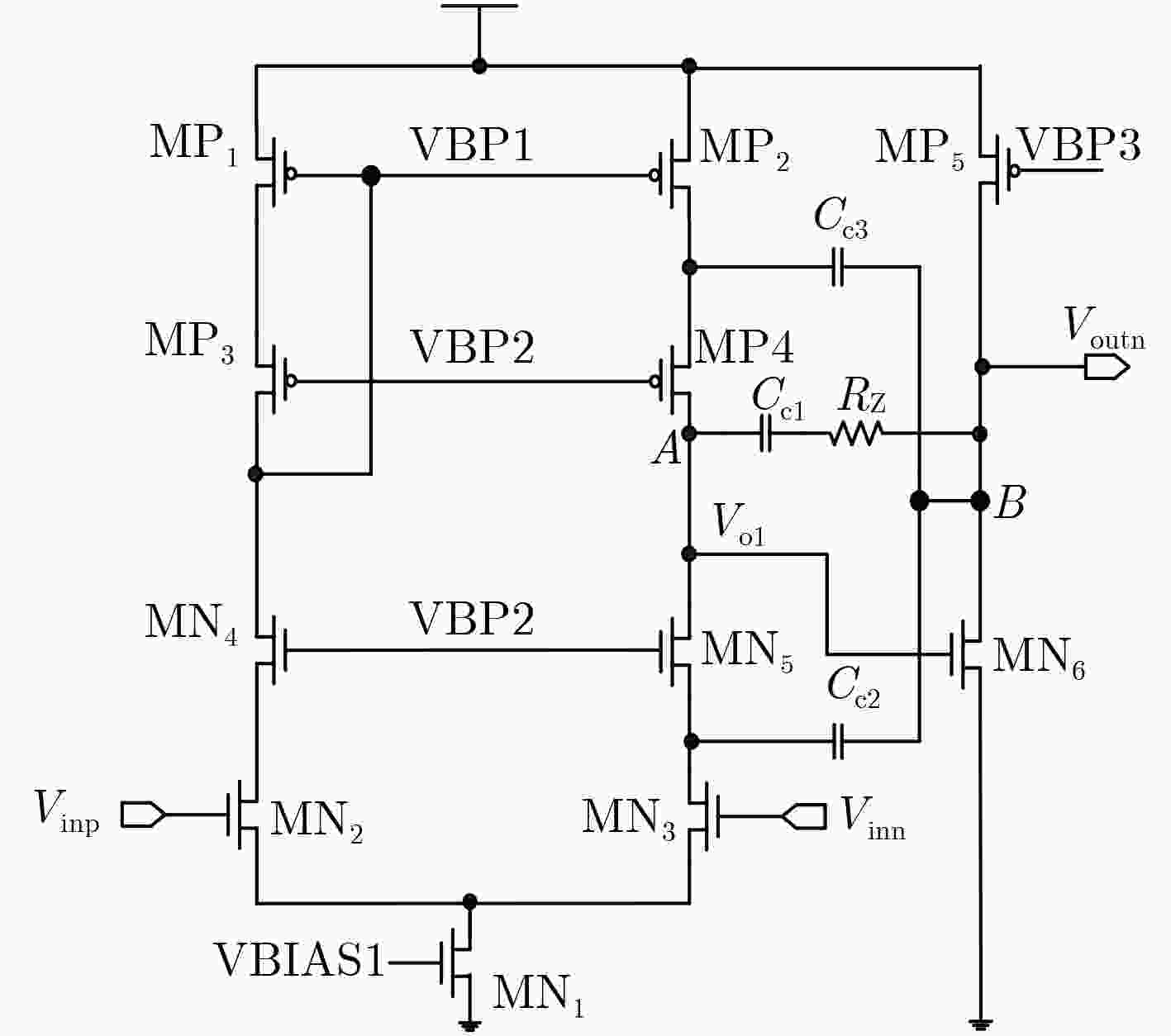

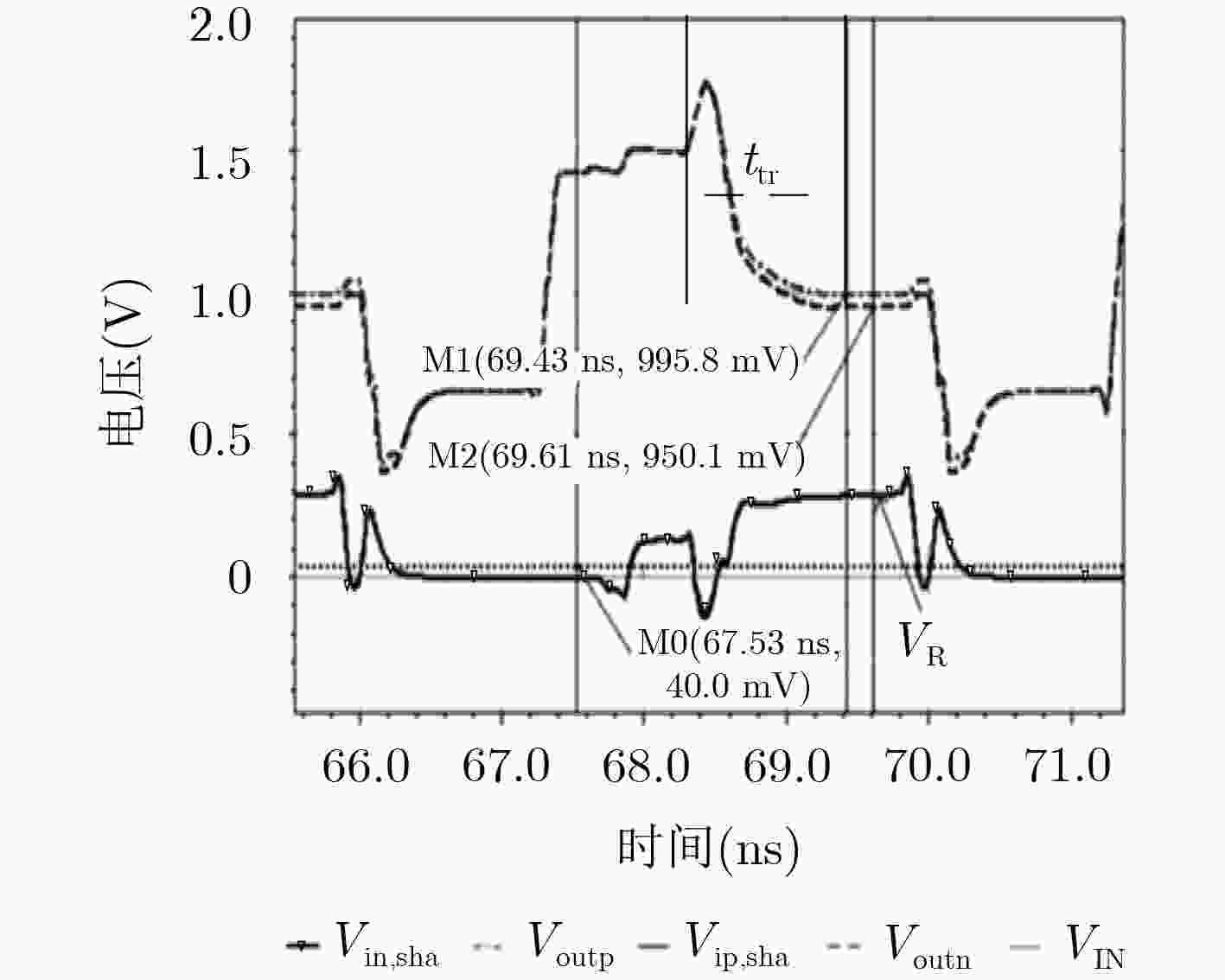

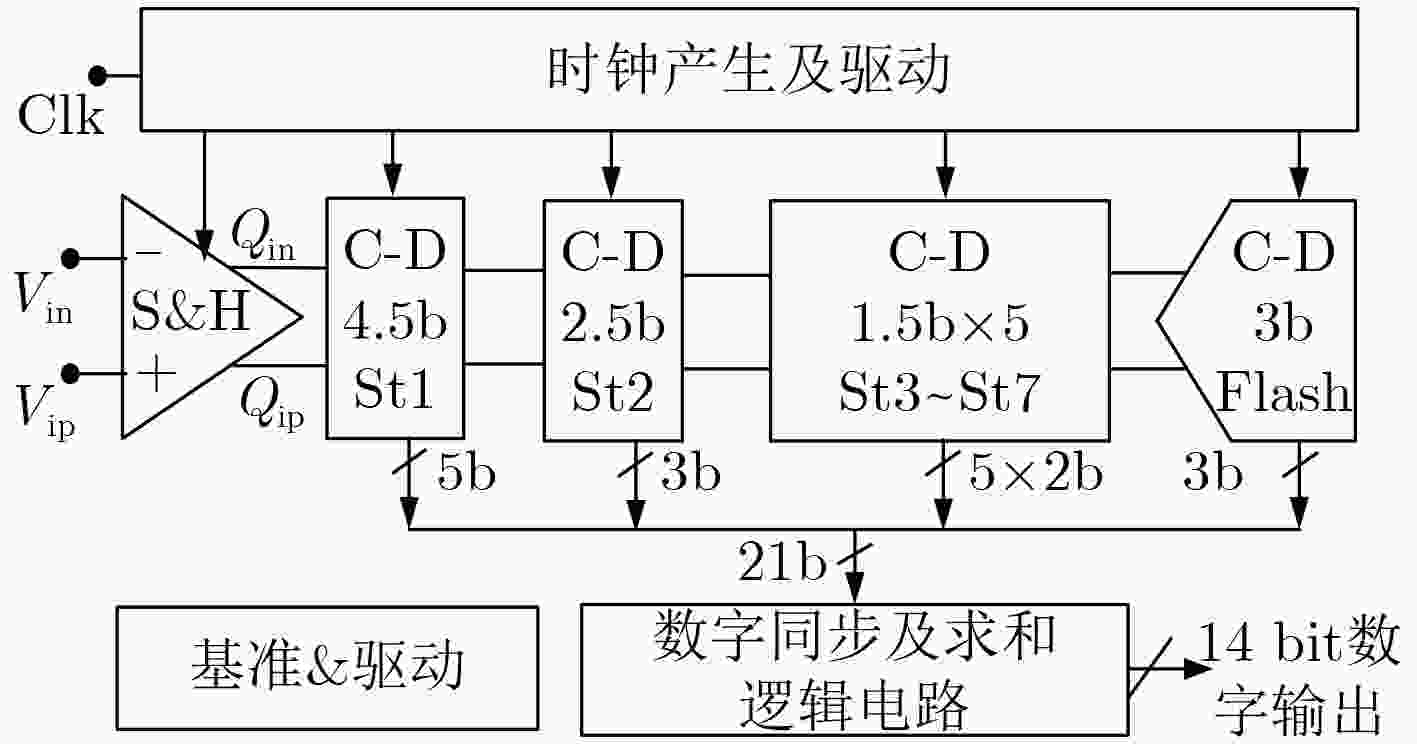

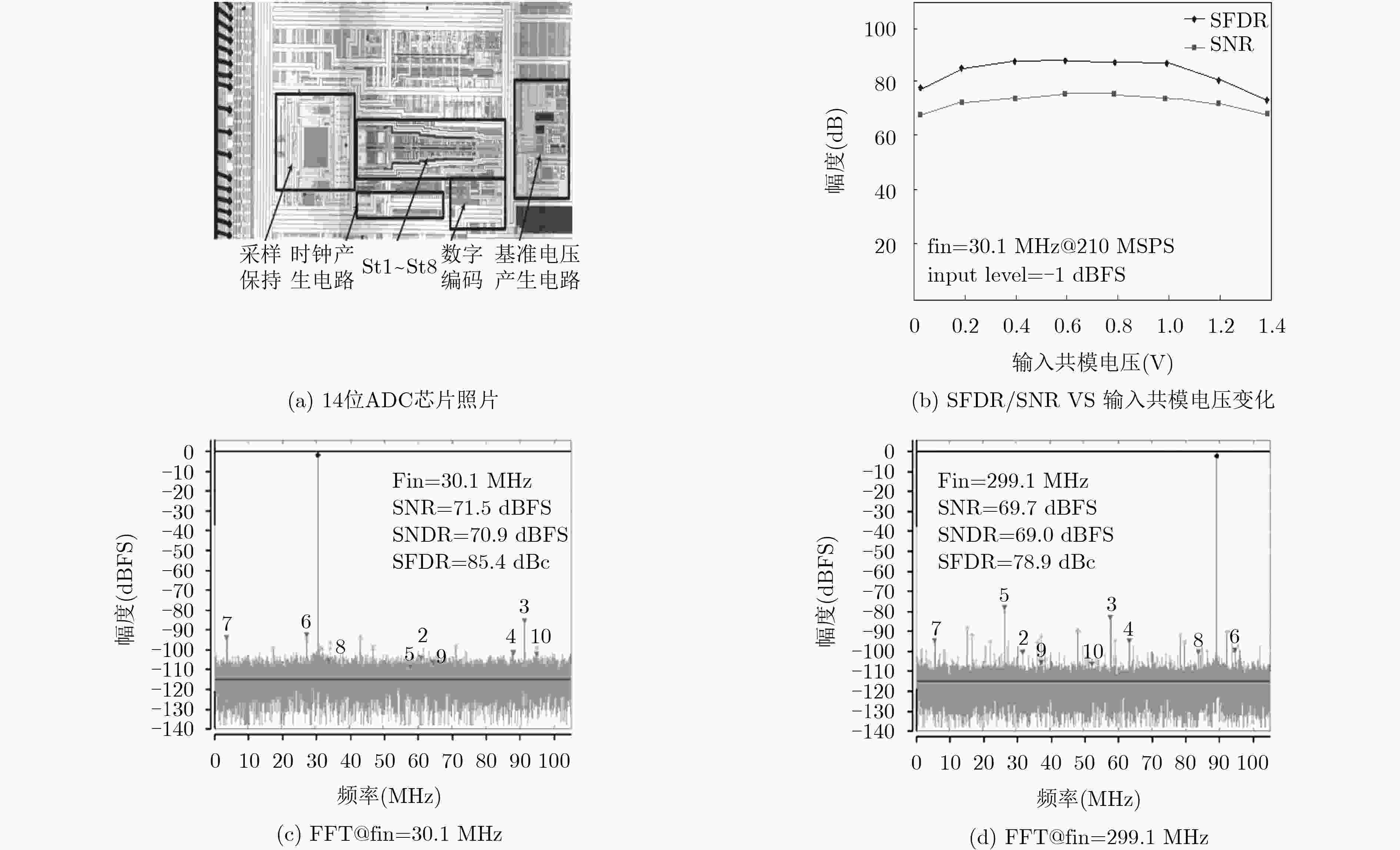

该文提出一种用于电荷域流水线模数转换器(ADC)的高精度输入共模电平不敏感采样保持前端电路。该采样保持电路可对电荷域流水线ADC中由输入共模电平误差引起的共模电荷误差进行补偿。所提出的高精度输入共模电平不敏感采样保持电路被运用于一款14位210 MS/s电荷域ADC中,并在1P6M 0.18 μm CMOS工艺下实现。测试结果显示,该14位ADC电路在210 MS/s条件下对于30.1 MHz单音正弦输入信号得到的无杂散动态范围为85.4 dBc,信噪比为71.5 dBFS,而ADC内核功耗仅为205 mW,面积为3.2 mm2。

Abstract:A high precision common mode level insensitive sample and hold front-end circuit for charge domain pipelined Analog-to-Digital Converter (ADC) is proposed. The sample and hold circuit can be used to compensate the common mode charge errors caused by the variation of input common mode level in charge domain pipelined ADCs. Based on the proposed sample and hold circuit, a 14-bit 210 MS/s charge domain pipelined ADC is designed and realized in a 1P6M 0.18 μm CMOS process. Test results show the 14-bit 210 MS/s ADC achieves the signal-to-noise ratio of 71.5 dBFS and the spurious free dynamic range of 85.4 dBc, with 30.1 MHz input single tone signal at 210 MS/s, while the ADC core consumes the power consumption of 205 mW and occupies an area of 3.2 mm2.

-

表 1 ADC性能对比

技术指标 精度

(bit)采样

(MS/s)SNR

(dB)SFDR

(dB)电源电压

(V)工艺

(nm)内核功耗

(mW)内核面积

(mm2)FOM(pJ/step)

功耗/(${{2}^{{\rm{ENOB}}}} \cdot {\rm{f}}$clk)文献[4] 14 500 64.8 92.7 1.8/3.3 180 550 2.5** 0.71 文献[5] 14 1000 69.0 86.0 1.2/2.5 65 1200 5.0 0.55 文献[15] 14 200 68.5 88.5 1.8 180 460 22.5* 1.07 文献[16] 14 250 68.5 94.7 1.8 180 300 3.6 0.57 本文 14 210 71.5 85.4 1.8 180 205 3.2 0.39 注:*该ADC为时间交织结构;**该ADC采用SiGe BiCMOS工艺 -

李光祚, 默迪, 王宁, 等. 一种新的高重频宽带相干激光雷达系统研究[J]. 电子与信息学报, 2018, 40(3): 525–531. doi: 10.11999/JEIT170479LI Guangzuo, MO Di, WANG Ning, et al. A novel coherent ladar system with high repetition frequency and wide bandwidth[J]. Journal of Electronics &Information Technology, 2018, 40(3): 525–531. doi: 10.11999/JEIT170479 陈珍海, 于宗光, 李现坤, 等. 用于16 bit 100 MS/s ADC的高精度参考电压产生电路[J]. 西安电子科技大学学报(自然科学版), 2017, 44(3): 127–132. doi: 10.3969/j.issn.1001-2400.2017.03.022CHEN Zhenhai, Yu Zongguang, LI Xiankun, et al. High precision voltage reference generator for 16-bit 100 MS/s ADC[J]. Journal of Xidian University, 2017, 44(3): 127–132. doi: 10.3969/j.issn.1001-2400.2017.03.022 杨贵德, 周渊平, 夏文龙. 协同信道空时优化MIMO无线传输系统[J]. 电子与信息学报, 2018, 40(1): 102–107. doi: 10.11999/JEIT170321YANG Guide, ZHOU Yuanping, and XIA Wenlong. Cooperative channel MIMO wireless transmission system with space-time optimization[J]. Journal of Electronics &Information Technology, 2018, 40(1): 102–107. doi: 10.11999/JEIT170321 MANAR E, LI XP, SHIGENOBU K, et al. A 90 dB SFDR 14-b 500 MS/s BiCMOS switched-current pipelined ADC[C]. IEEE Proceedings of International Solid-State Circuits Conference, San Francisco, USA, 2015: 286–287. doi: 10.1109/ISSCC.2015.7063038. ALI AMA, DINC H, BHORASKAR P, et al. A 14-b 1 GS/s RF sampling pipelined ADC with background calibration[J]. IEEE Journal of Solid-State Circuits, 2014, 49(12): 2857–2867. doi: 10.1109/JSSC.2014.2361339 ALI AMA, DINC H, BHORASKAR P, et al. A 14-bit 2.5 GS/s and 5 GS/s RF sampling ADC with background calibration and dither[C]. IEEE Proceedings of Symposium on VLSI Circuits, Honolulu, USA, 2016: 1–2. doi: 10.1109/VLSIC.2016.7573537. WU J F, CHOU A, LI T W, et al. A 4 GS/s 13b pipelined ADC with capacitor and amplifier sharing in 16 nm CMOS[C]. IEEE Proceedings of International Solid-State Circuits Conference, San Francisco, USA, 2016: 466–468. doi: 10.1109/ISSCC.2016.7418109. MICHAEL A, EDWARD K, JEFFREY K, et al. A process-scalable low-power charge-domain 13-bit pipeline ADC[C]. IEEE Proceedings of Symposium on VLSI Circuits, Honolulu, USA, 2008: 222–223. doi: 10.1109/VLSIC.2008.4586015. CHEN Z H, YU Z G, HUANG S R, et al. A PVT insensitive boosted charge transfer for high speed charge-domain pipelined ADCs[J]. IEICE Electronics Express, 2012, 9(6): 565–571. doi: 10.1587/elex.9.565 CHEN Zhenhai, HUANG Songren, ZHANG Hong, et al. A 27-mW 10-bit 125-MSPS charge-domain pipelined ADC with PVT insensitive boosted charge transfer[J]. Journal of Semiconductors, 2013, 34(3): 035009. doi: 10.1088/1674-4926/34/3/035009 陈珍海, 魏敬和, 苏小波, 等. 低功耗时间交织12位500 MS/s电荷域ADC[J]. 西安电子科技大学学报(自然科学版), 2017, 44(6): 119–126. doi: 10.3969/j.issn.1001-2400.2017.06.020CHEN Zhenhai, WEI Jinghe, SU Xiaobo, et al. Low power time-interleaved 12 bit 500 MS/s charge domain ADC[J]. Journal of Xidian University, 2017, 44(6): 119–126. doi: 10.3969/j.issn.1001-2400.2017.06.020 HUANG Songren, ZHANG Hong, CHEN Zhenhai, et al. A 10-bit 250 MS/s charge-domain pipelined ADC with replica controlled PVT insensitive BCT circuit[J]. Journal of Semiconductors, 2015, 36(5): 055012. doi: 10.1088/1674-4926/36/5/055012 陈珍海, 于宗光, 魏敬和, 等. 采用1.75 Gbps串行发送器的低功耗14位125 MSPS ADC[J]. 电子测量与仪器学报, 2017, 31(1): 132–138. doi: 10.13382/j.jemi.2017.01.019CHEN Zhenhai, YU Zongguang, WEI Jinghe, et al. Low power 14-bit 125 MSPS ADC with 1.75 Gbps serial transmitter[J]. Journal of Electronic Measurement and Instrument, 2017, 31(1): 132–138. doi: 10.13382/j.jemi.2017.01.019 YU Zongguang, SU Xiaobo, CHEN Zhenhai, et al. A 12-bit 250-MS/s charge-domain pipelined analog-to-digital converter with feed-forward common-mode charge control[J]. Tsinghua Science and Technology, 2018, 23(1): 87–94. doi: 10.26599/TST.2018.9010030 ZHANG Yiwen, CHEN Chixiao, YU Bei, et al. A 14-bit 200-MS/s time-interleaved ADC with sample-time error calibration[J]. Journal of Semiconductors, 2012, 33(10): 105010. doi: 10.1088/1674-4926/33/10/105010 ZHENG X Q, WANG Z J, LI F L, et al. A 14-bit 250 MS/s IF sampling pipelined ADC in 180 nm CMOS process[J]. IEEE Transactions on Circuits and Systems-I: Regular Papers, 2016, 63(9): 1381–1392. doi: 10.1109/TCSI.2016.2580703 -

下载:

下载:

下载:

下载: