Method for Compensating Distortion Created by Mismatch Errors in Time-interleaved ADCs Based on Offline Estimation and Online Correction

-

摘要:

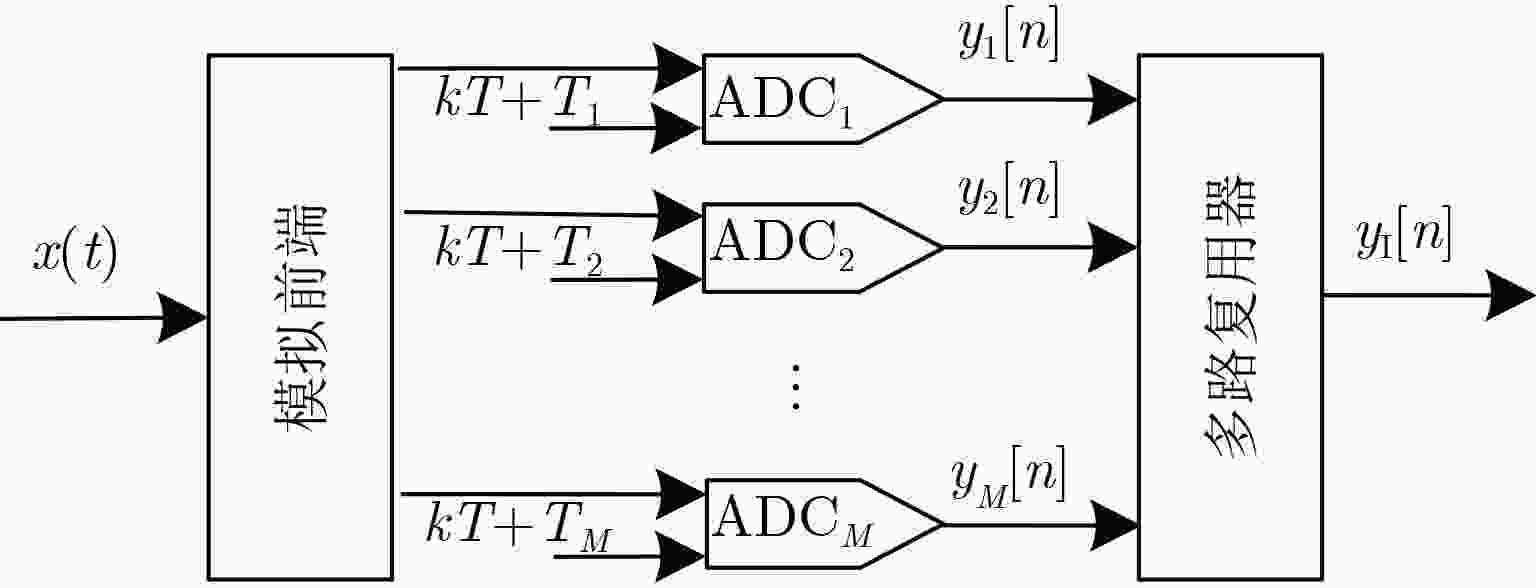

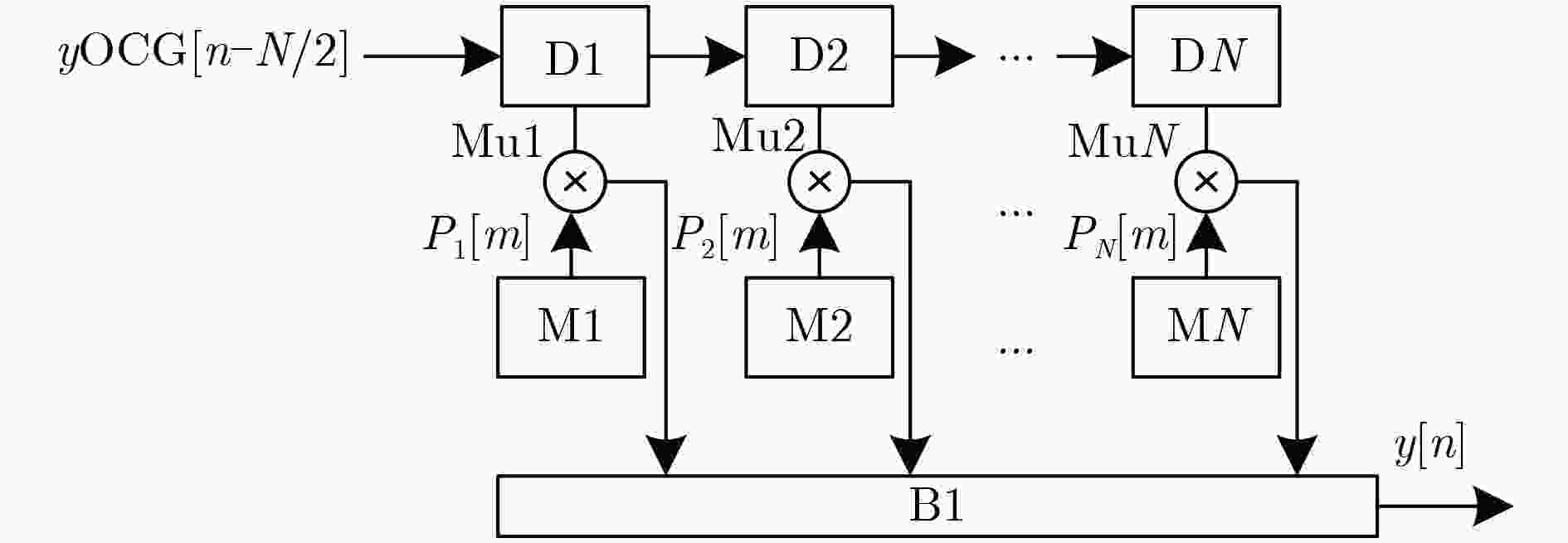

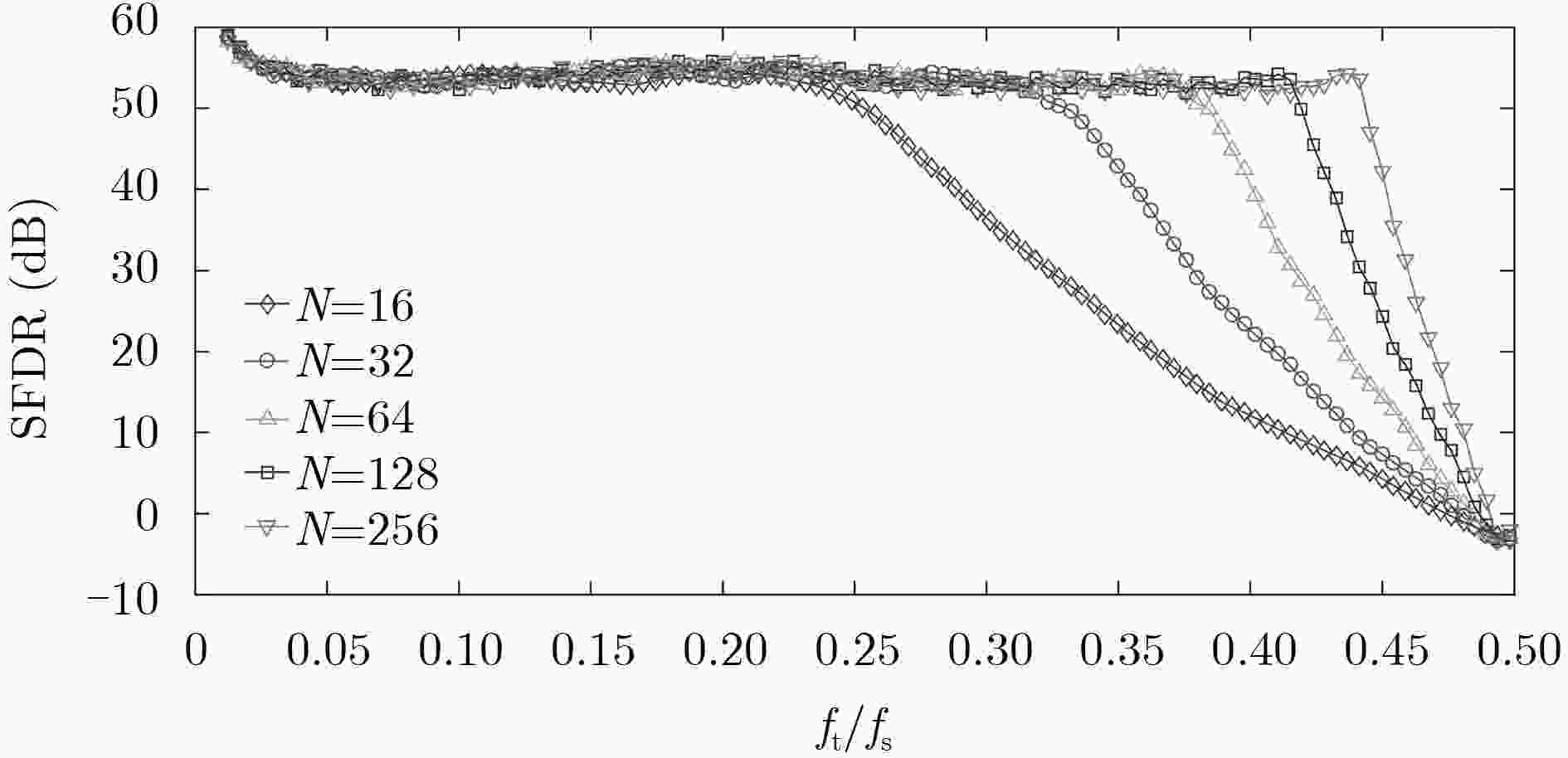

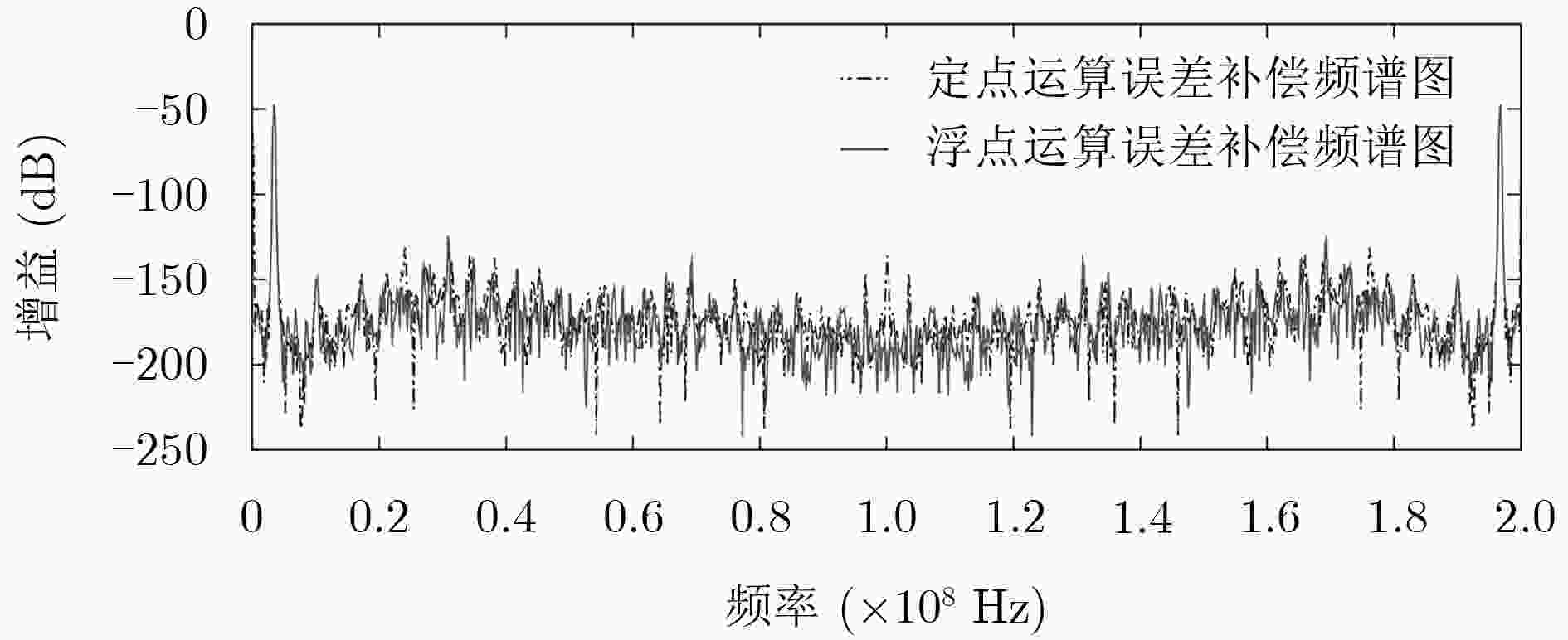

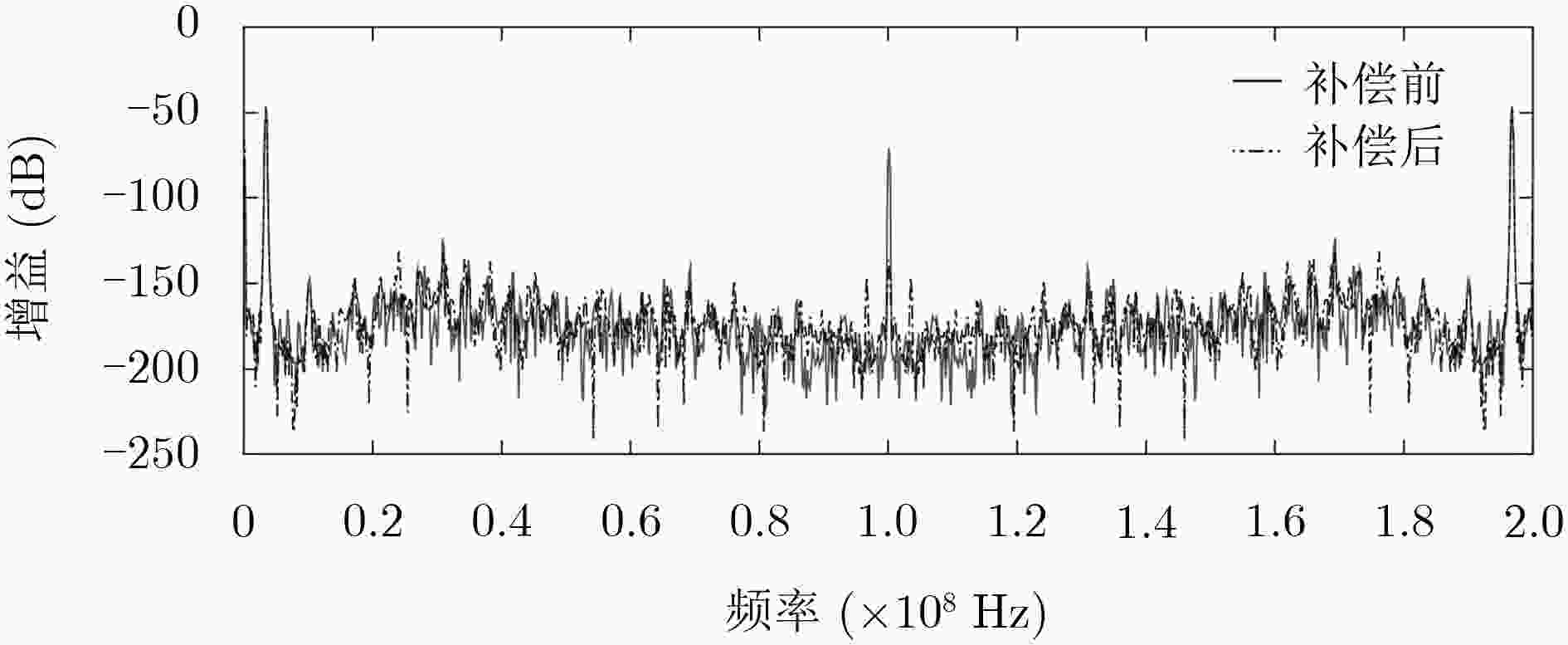

该文提出一种改进的时间交错采样模数转换器(TIADC)失配误差补偿方法。系统通过误差参数和简化的拉格朗日插值算法分别实现了对偏置、增益的失配误差补偿和采样时间的失配误差补偿。该补偿方法在FPGA中采用低复杂度的定点运算实现,在TIADC硬件平台中实现了对多通道ADC采样数据的线上校正。实验结果表明:所提改进方法在仿真环境下使无杂散动态范围提升了51 dB,并且在硬件实现过程中使SFDR优化达45 dB。在保持失配误差估计精度和补偿效果优良的前提下,该方法不仅降低了算法的计算复杂度,而且该补偿结构不受TIADC通道数目的限制。

Abstract:A improved method is proposed for compensating the distortion created by mismatches in Time-Interleaved Analog-to-Digital Converters (TI ADCs). The error compensation of offset and gain is realized by error parameters, and the error compensation of sampling time is realized by the simplified Lagrange interpolation algorithm. The compensation method is implemented in FPGA with the low complexity of fixed-point algorithm, and the online calibration of multi-channel ADC sampling data is implemented in the TIADC hardware platform. The experimental results show that the proposed method improves the Spurious-Free Dynamic Range (SFDR) of sampling data up to 51 dB in the simulation environment, and optimizes the SFDR up to 45 dB in the process of hardware implementation. Under the premise of maintaining the error estimation precision and compensation effect, this method not only reduces the computational complexity of the algorithm, but also the compensation structure is not limited by the number of TIADC channels.

-

表 1 失配误差的真实值与估计值

ADC通道 ADC1 ADC2 ADC3 ADC4 ADC5 ADC6 ADC7 ADC8 G 1.04440 0.95730 0.96170 1.02140 1.00460 0.97110 1.04570 1.02500 $\widehat G$ 1.04440 0.95723 0.96150 1.02137 1.00456 0.97081 1.04555 1.02493 O 0.02130 –0.01120 0.04290 0.02940 0.01250 0.02600 –0.03320 –0.03170 $\widehat O$ 0.02130 –0.01119 0.04292 0.02940 0.01251 0.02599 –0.03320 –0.03169 T (ps) 0 502 –877 324 –415 1109 757 –496 $\widehat T\; {\rm{(ps)}}$ 2 503 –879 324 –417 1112 758 –498 表 3 硬件补偿电路的FPGA片上逻辑资源消耗情况

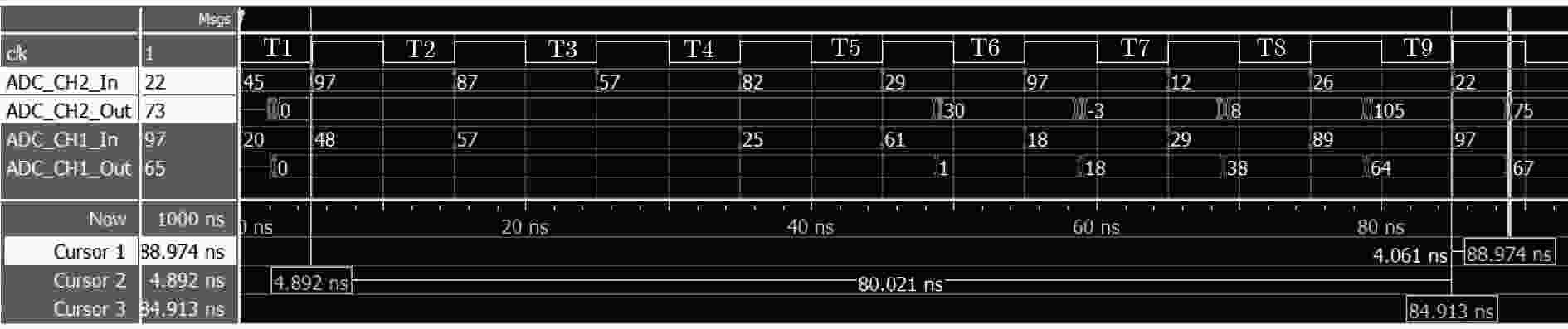

资源类型 总组合功能 专用逻辑寄存器 18 bit嵌入式乘法器 存储容量 资源消耗情况 111/8256 98/8256 5/18 0/165888 表 4 偏置、增益和采样时间失配误差估计值

ADC通道 ADC1 ADC2 $\widehat G$ 1.061100 1.061900 $\widehat O\;\left( {\rm{V}} \right)$ –0.057000 0.000053 $\widehat T\;\left( {\rm{ns}} \right)$ 1.191200 1.424300 -

BLACK W C and HODGES D A. Time interleaved converter arrays[J]. IEEE Journal of Solid-State Circuits, 1980, 15(6): 1022–1029. doi: 10.1109/JSSC.1980.1051512 PETRAGLIA A and MITRA S K. Analysis of mismatch effects among A/D converters in a time-interleaved waveform digitizer[J]. IEEE Transactions on Instrumentation and Measurement, 1991, 40(5): 831–835. doi: 10.1109/19.106306 KUIOSAWA N, KOBAYASHI H, MARUYAMA K, et al. Explicit analysis of channel mismatch effects in time-interleaved ADC systems[J]. IEEE Transactions on Circuits and Systems I, Fundamental Theory and Applications, 2001, 48(3): 261–271. doi: 10.1109/81.915383 VOGEL C. The impact of combined channel mismatch effects in time-interleaved ADCs[J]. IEEE Transactions on Instrumentation and Measurement, 2005, 54(1): 415–427. doi: 10.1109/TIM.2004.834046 LOONEY M. Advanced digital post-processing techniques enhance performance in time-interleaved ADC systems[OL]. http://www.analog.com/cn/analog-dialogue/articles/advanced-digital-post-processing-techniques.html, 2017.1. BONNETAT A, HODE J M, FERRE G, et al. An adaptive all-digital blind compensation of dual-TIADC frequency response mismatch based on complex signal correlations[J]. IEEE Transactions on Circuits and Systems II, Express Briefs, 2015, 62(9): 821–825. doi: 10.1109/TCSII.2015.2435611 BONNETAT A, HODE J M, FERRE G, et al. Correlation-based frequency-response mismatch compensation of quad-TIADC using real samples[J]. IEEE Transactions on Circuits and Systems II, Express Briefs, 2015, 62(8): 746–750. doi: 10.1109/TCSII.2015.2433472 ELBORNSSON J, GUSTAFSSON F, and EKLUND J E. Blind equalization of time errors in a time-interleaved ADC system[J]. IEEE Transactions on Signal Processing, 2005, 53(4): 1413–1424. doi: 10.1109/TSP.2005.843706 LIU Sujiang, CUI Jiashuai, MA Haixiao, et al. Blind timing error estimation based on the phasic relationship between nonoverlapping frequency points in time-interleaved ADCs[C]. IEEE International Conference on Solid-State and Integrated Circuit Technology, Guilin, China, 2014: 1–3. doi: 10.1109/ICSICT.2014.7021586. 张尚良, 邹月娴. TIADC高速数据捕获和时间失配补偿的FPGA实现[J]. 数据采集与处理, 2011, 26(5): 601–608. doi: 10.3969/j.issn.1004-9037.2011.05.019ZHANG Shangliang and ZOU Yuexian. FPGA implementation of data acquisition and timing mismatch compensation for TIADC system[J]. Journal of Data Acquisition &Processing, 2011, 26(5): 601–608. doi: 10.3969/j.issn.1004-9037.2011.05.019 刘洋, 刁节涛, 王义楠, 等. 交错采样技术中的失配误差建模与估计[J]. 仪表技术与传感器, 2015, 12: 132–135. doi: 10.3969/j.issn.1002-1841.2015.12.039LIU Yang, DIAO Jietao, WANG Yinan, et al. Modeling and identification of channel mismatches in time-interleaved technique[J]. Instrument Technique and Sensor, 2015, 12: 132–135. doi: 10.3969/j.issn.1002-1841.2015.12.039 SEO M, RODWELL M, and MADHOW U. Generalized blind mismatch correction for two-channel time-interleaved ADCs[C]. IEEE International Conference on Acoustics, Speech and Signal Processing, Honolulu, Hawaii, USA, 2007, vol. 3: 1505–1508. doi: 10.1109/ISCAS.2007.378233. SCHMIDT C A, COUSSEAU J E, FIGUEROA J L, et al. Efficient estimation and correction of mismatch errors in time-interleaved ADCs[J]. IEEE Transactions on Instrumentation and Measurement, 2016, 65(2): 243–254. doi: 10.1109/TIM.2015.2490378 ZOU Yuexian, ZHANG Shangliang, LIM Yongching, et al. Timing mismatch compensation in time-interleaved ADCs based on multichannel Lagrange Polynomial Interpolation[J]. IEEE Transactions on Instrumentation and Measurement, 2011, 60(4): 1123–1131. doi: 10.1109/TIM.2010.2085291 SINDHI S K and PRABHU K M M. Reconstruction of N-th order nonuniformly sampled bandlimited signals using digital filter banks[J]. Digital Signal Processing, 2013, 23(6): 1877–1886. doi: 10.1016/j.dsp.2013.06.004 -

下载:

下载:

下载:

下载: