-

图 1 均匀通道结构模型

Figure 1.

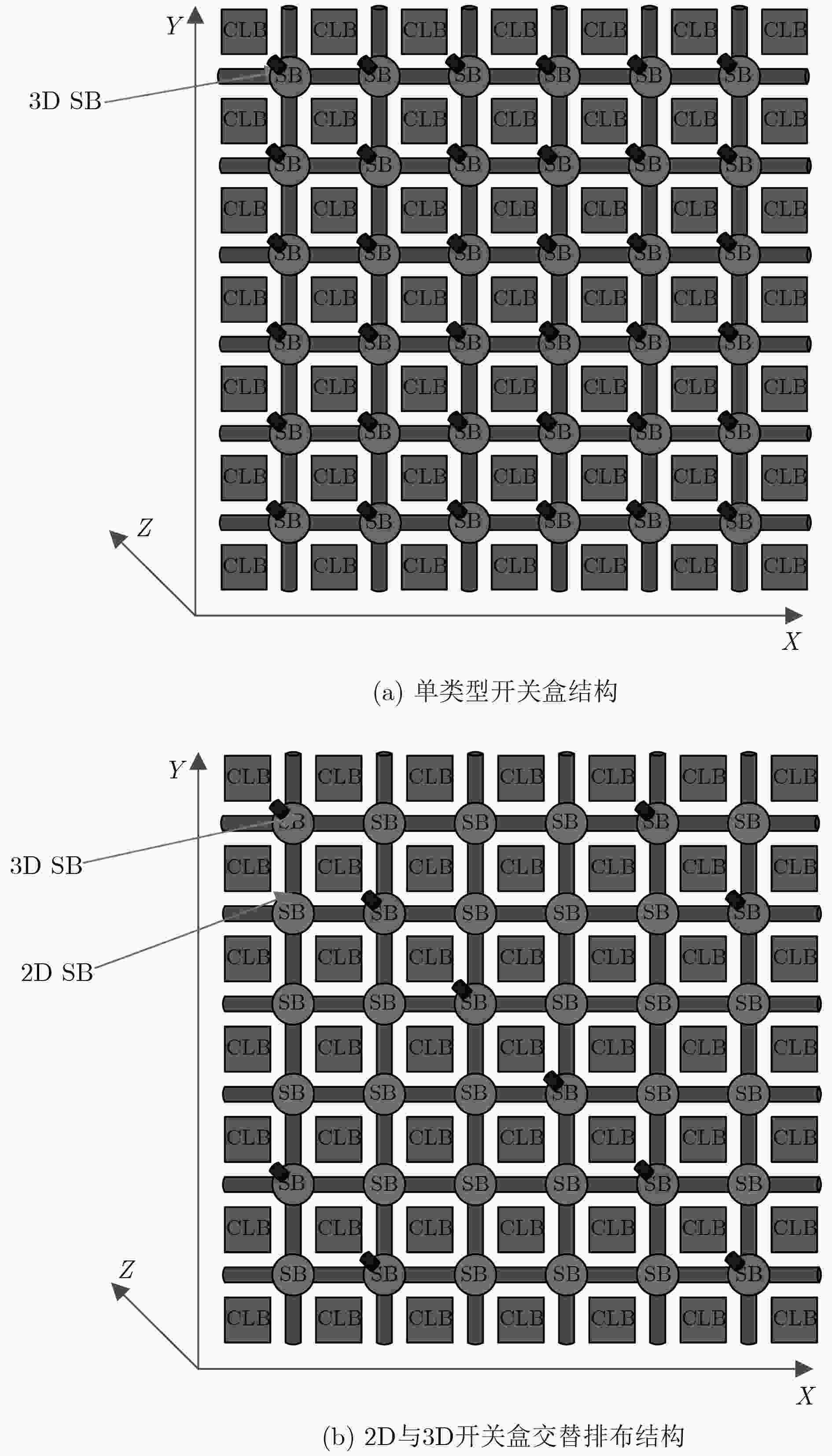

-

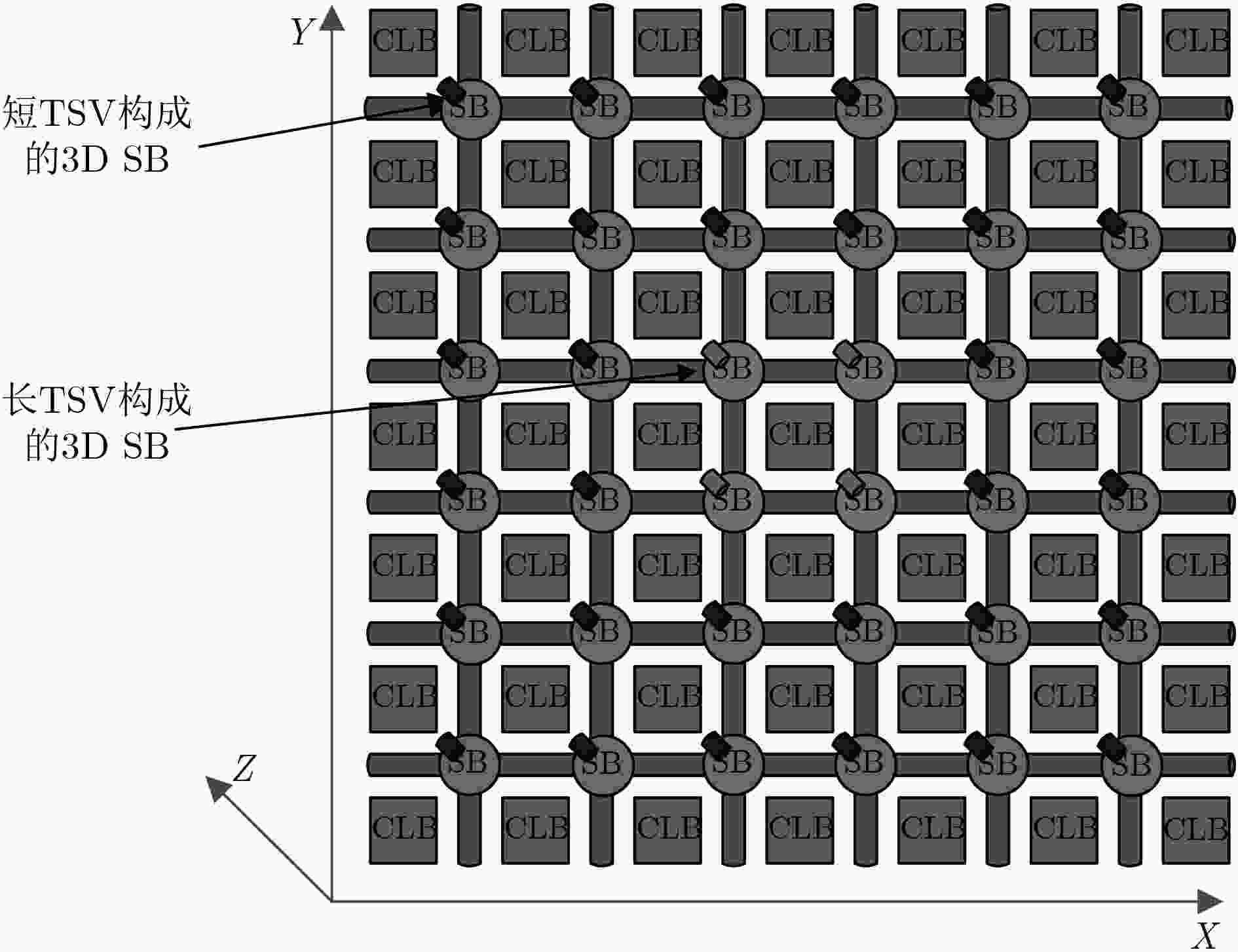

图 2 3D FPGA结构

Figure 2.

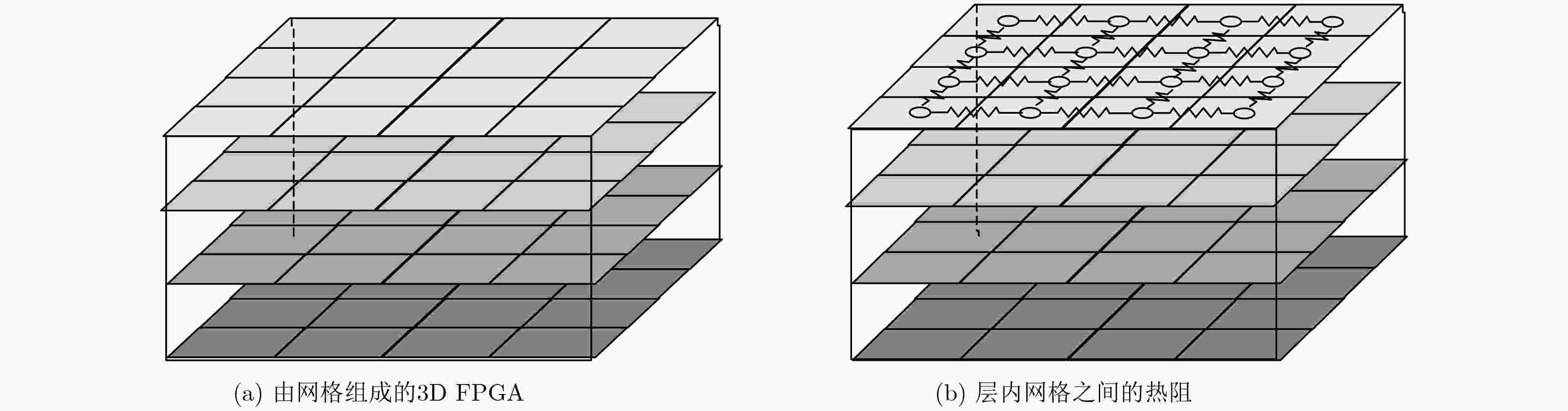

-

图 3 3D FPGA热阻网络模型

Figure 3.

-

图 4 3D最小网格散热分析模型

Figure 4.

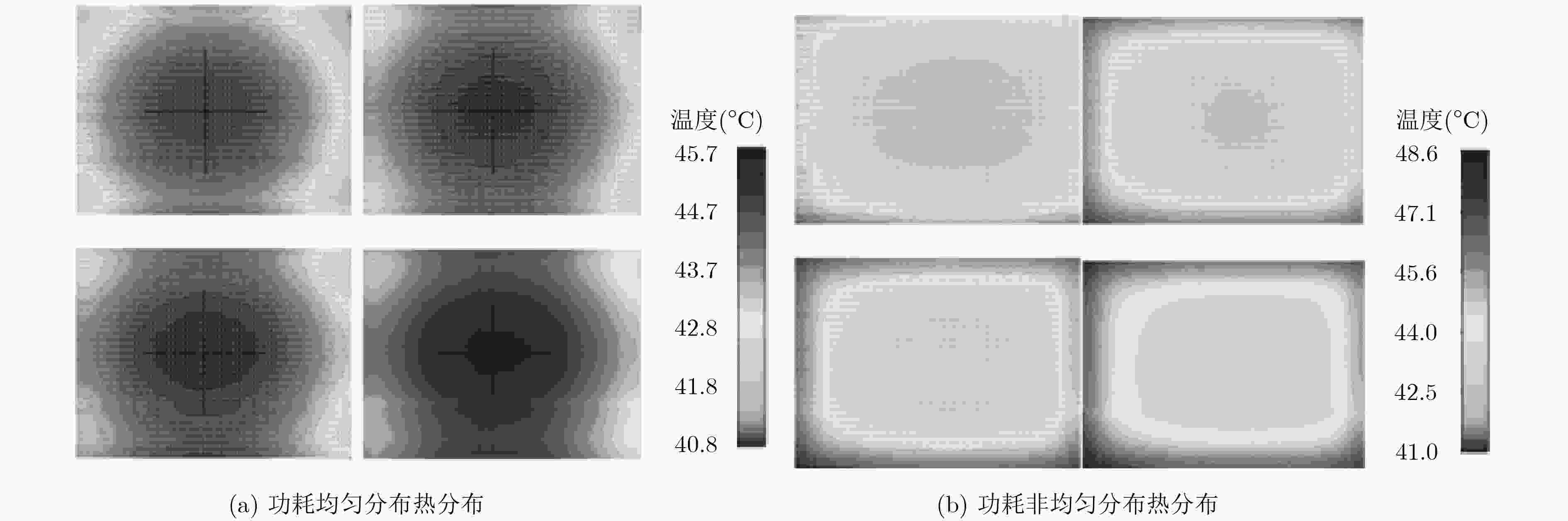

-

图 5 功耗不同分布热分布对比

Figure 5.

-

图 6 热分布统计直方图

Figure 6.

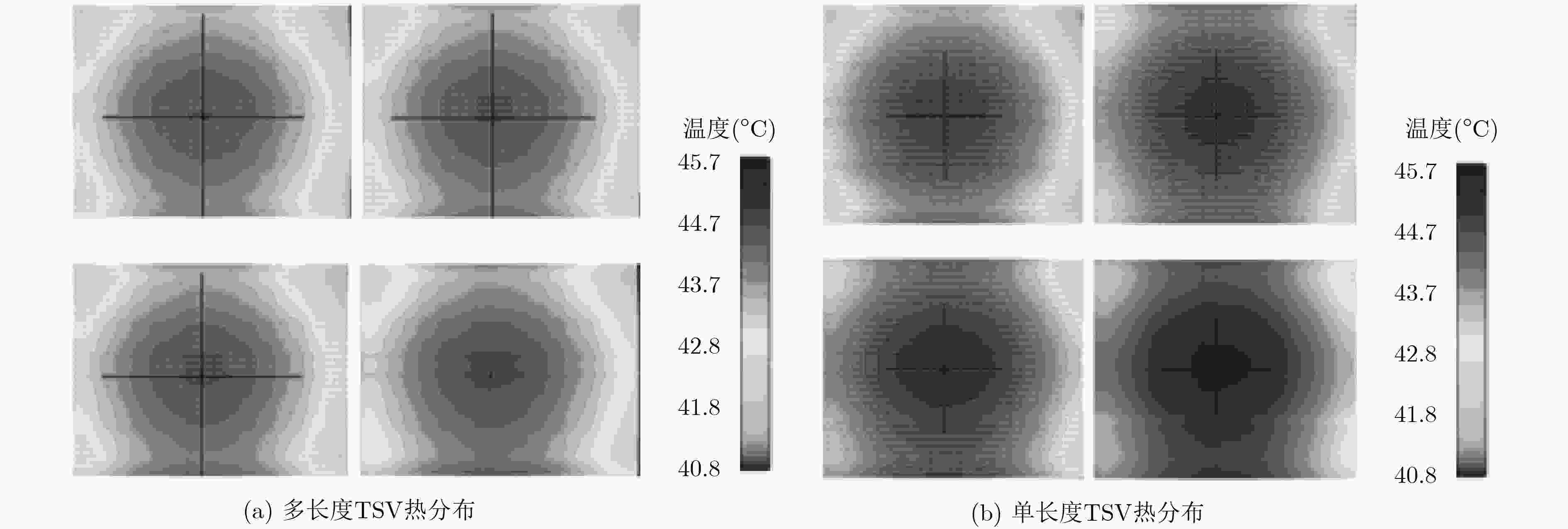

-

图 7 多长度与单长度TSV热分布对比

Figure 7.

-

图 8 非均匀分布结构1

Figure 8.

-

图 9 非均匀分布结构2

Figure 9.

-

图 10 异质结构分布

Figure 10.

-

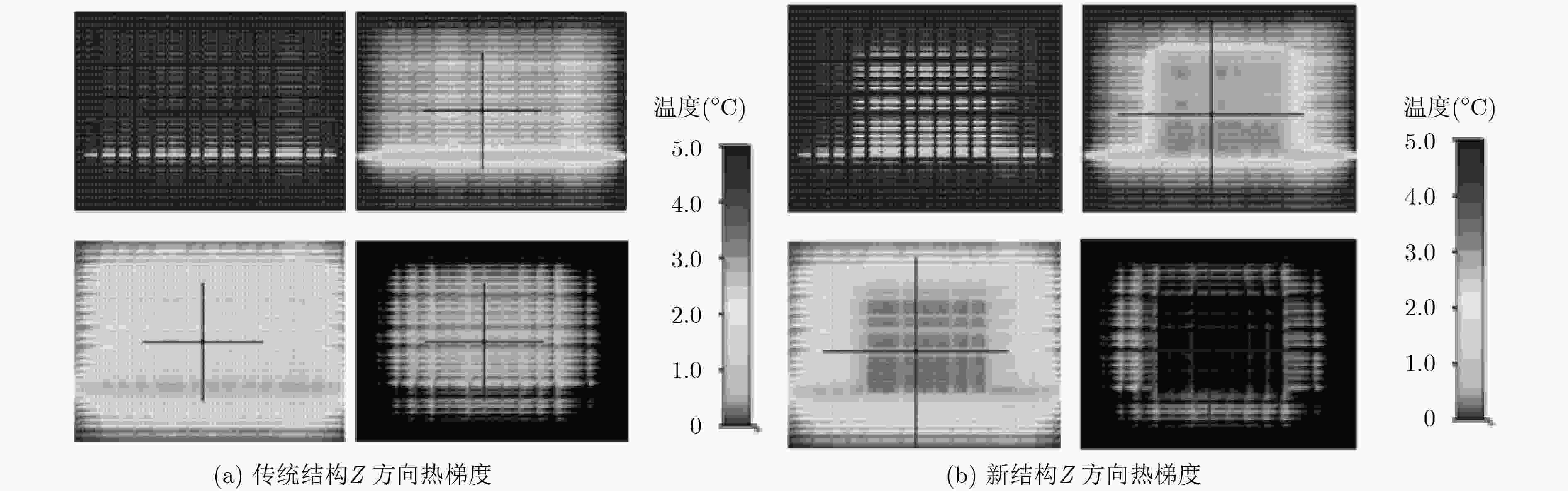

图 11 传统结构与新结构热梯度仿真结果

Figure 11.

-

热阻 错开放置 对齐放置 R1 RTS+RGR RTS R2 RTS+RGR RTS R3 RTS+RGR RTS R4 RAM RAM 表 1 两种情况的热阻值

-

部件 材料 尺寸 切片 Si 8 mm×6 mm TSV Cu 直径:20 μm,高度:50 μm Micro-Bump (微凸块) Cu 高度:20 μm Ceramic substrate (陶瓷衬底) 氧化铝 30 mm×30 mm BGA solder ball (BGA焊球) Sn63/Pb37 直径:0.6 mm,中心距:1 mm PCB motherboard (PCB板) FR4 30 mm×30 mm 表 2 封装材料设置

-

最低温度(°C) 最高温度(°C) 平均温度(°C) 切片1 40.9203 45.1598 43.6753 切片2 41.7091 45.2051 43.9975 切片3 42.1229 45.2337 44.1000 切片4 42.3739 45.2715 44.2322 表 3 新结构热分析统计结果

-

最低温度梯度

(°C)最高温度梯度

(°C)平均温度梯度

(°C)传统结构 1.4601 0.4824 0.6717 新结构 1.4536 0.1117 0.5569 改善比例(%) 0.4 76.8 17.1 表 4 层间热梯度改善情况

-

切片1 切片2 切片3 切片4 传统结构温度差(°C) 4.2112 3.6969 3.3647 3.2335 新结构温度差(°C) 4.2395 3.4960 3.1108 2.8976 改善比例(%) –0.60 5.40 7.50 10.40 表 5 层内热梯度改善情况

-

表 6 与其它方法的对比

图共

11 个 表共

6 个