-

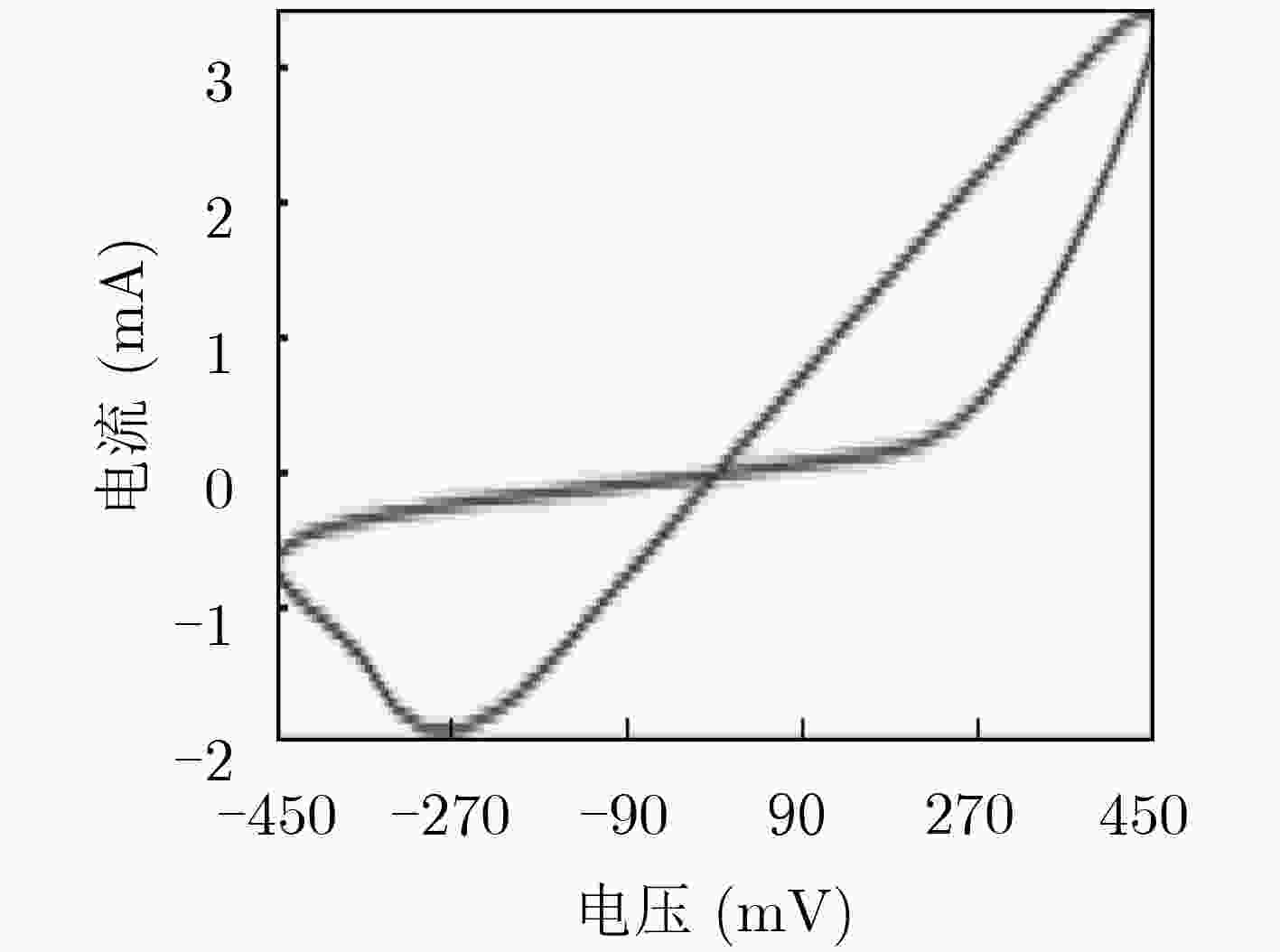

图 1 忆阻器的I-V 滞回曲线图

Figure 1.

-

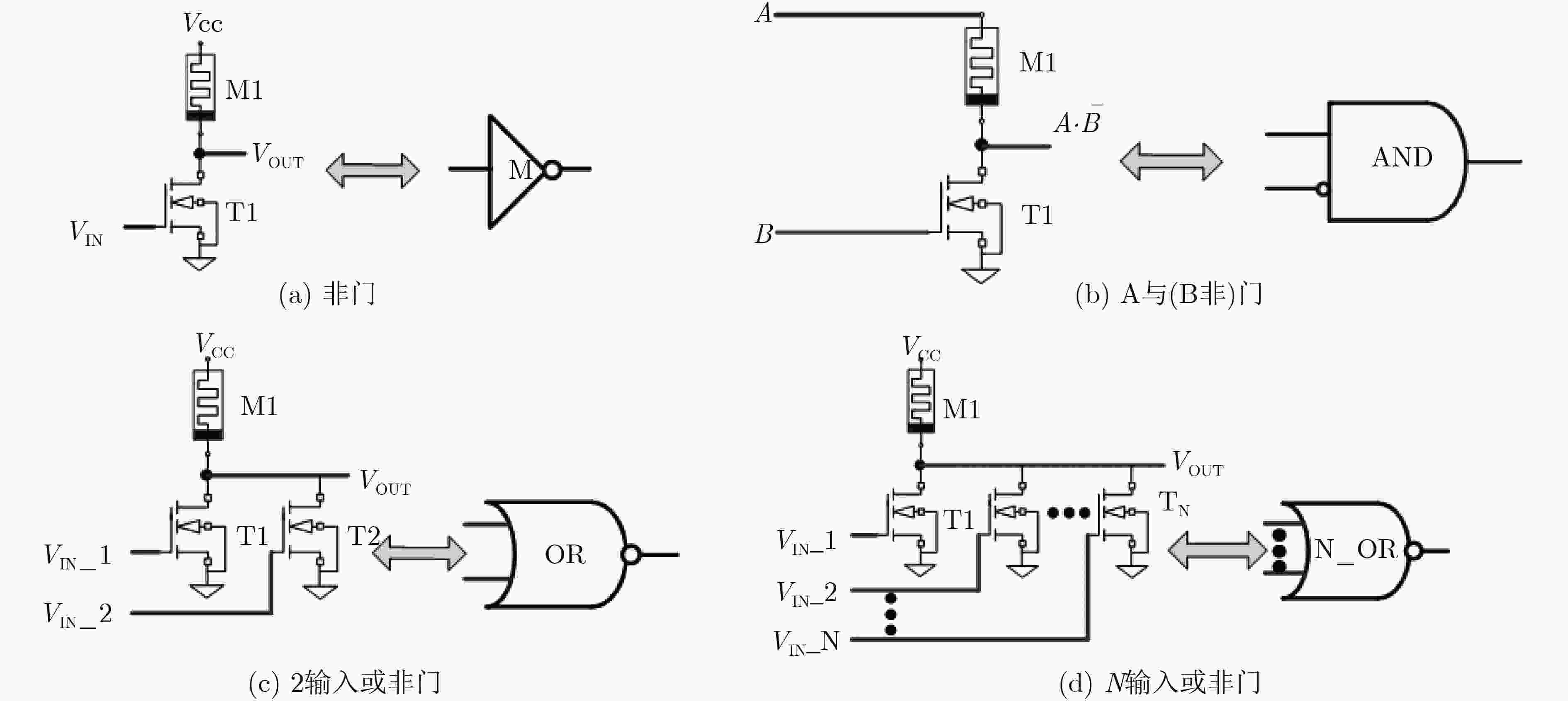

图 2 忆阻器构建的“或”、“与”、“或非”、“与非”门

Figure 2.

-

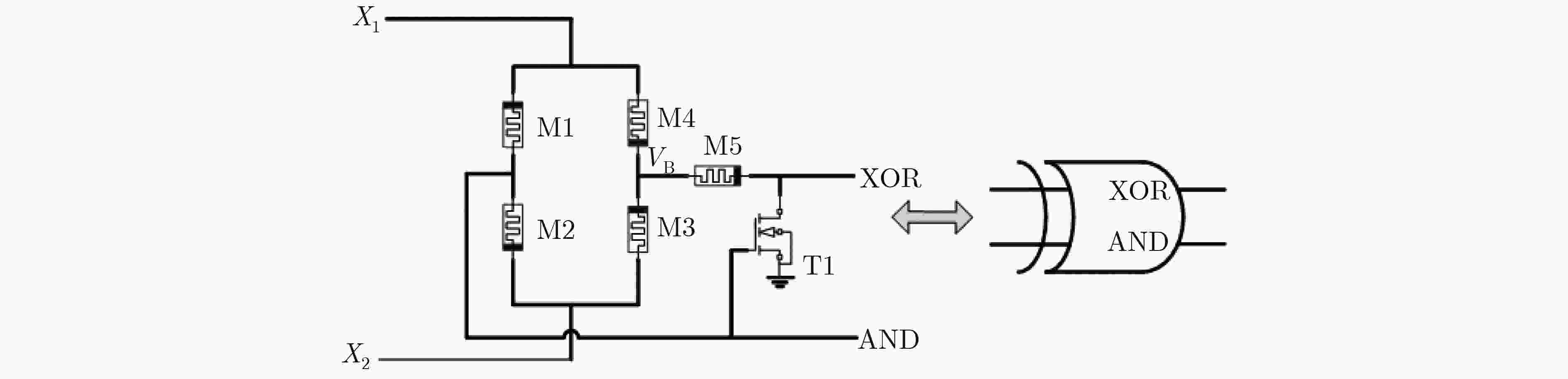

图 3 基于忆阻器比例逻辑的新型基础逻辑电路

Figure 3.

-

图 4 “异或”及“与”多功能逻辑模块

Figure 4.

-

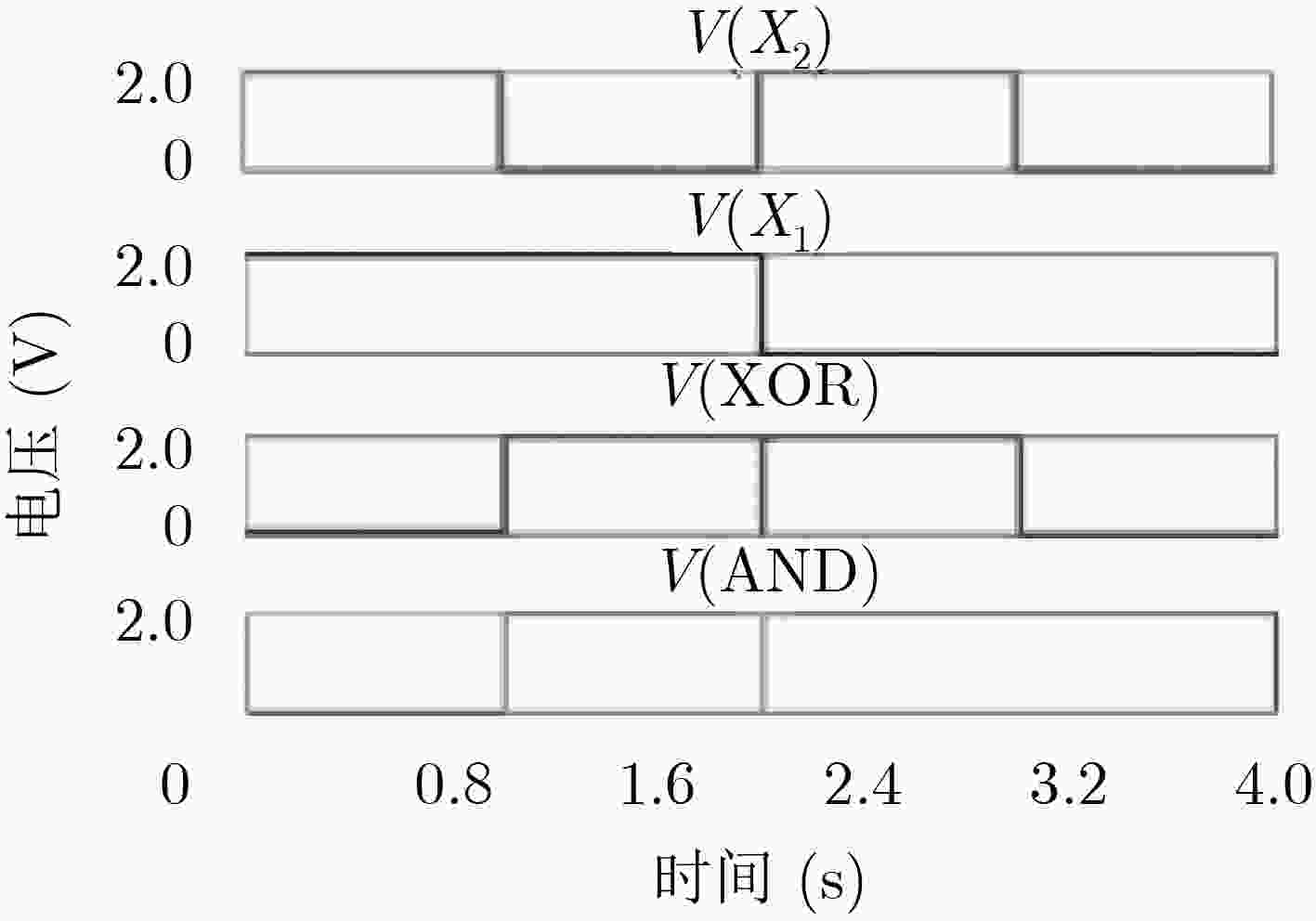

图 5 “异或”及“与”多功能逻辑模块仿真图

Figure 5.

-

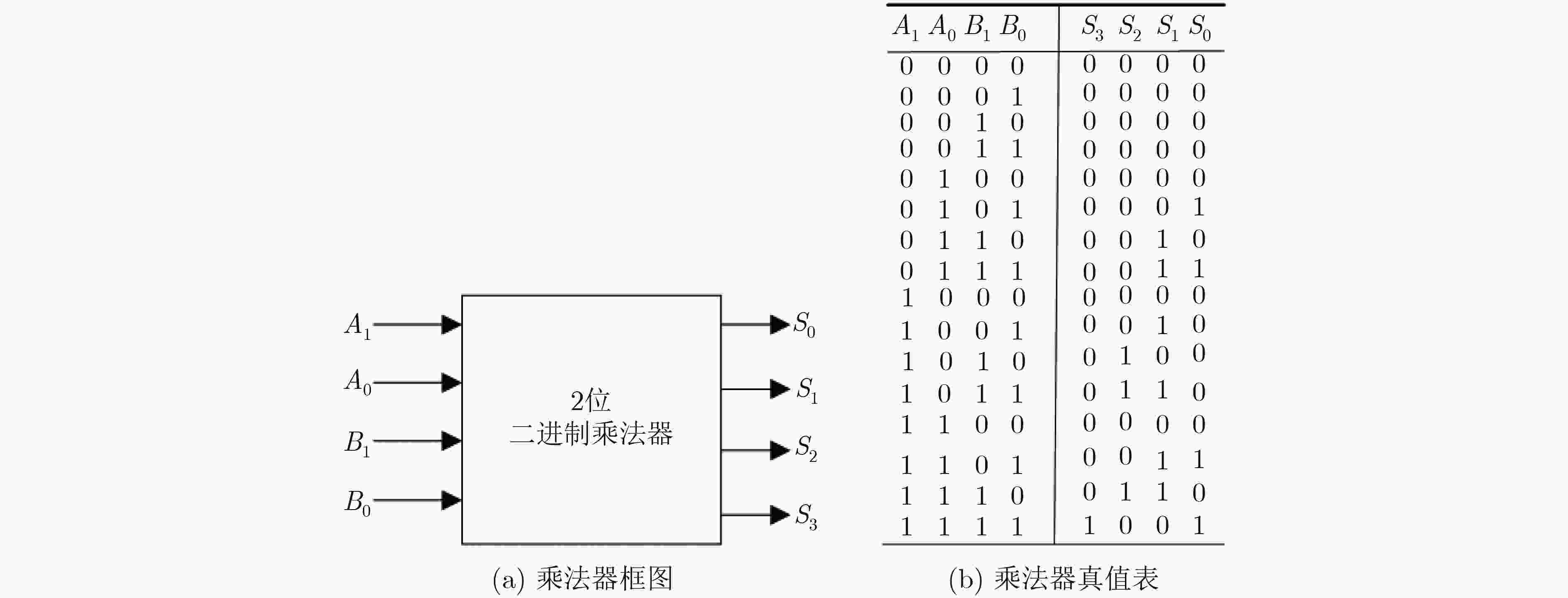

图 6 2位二进制乘法器器框图和真值表

Figure 6.

-

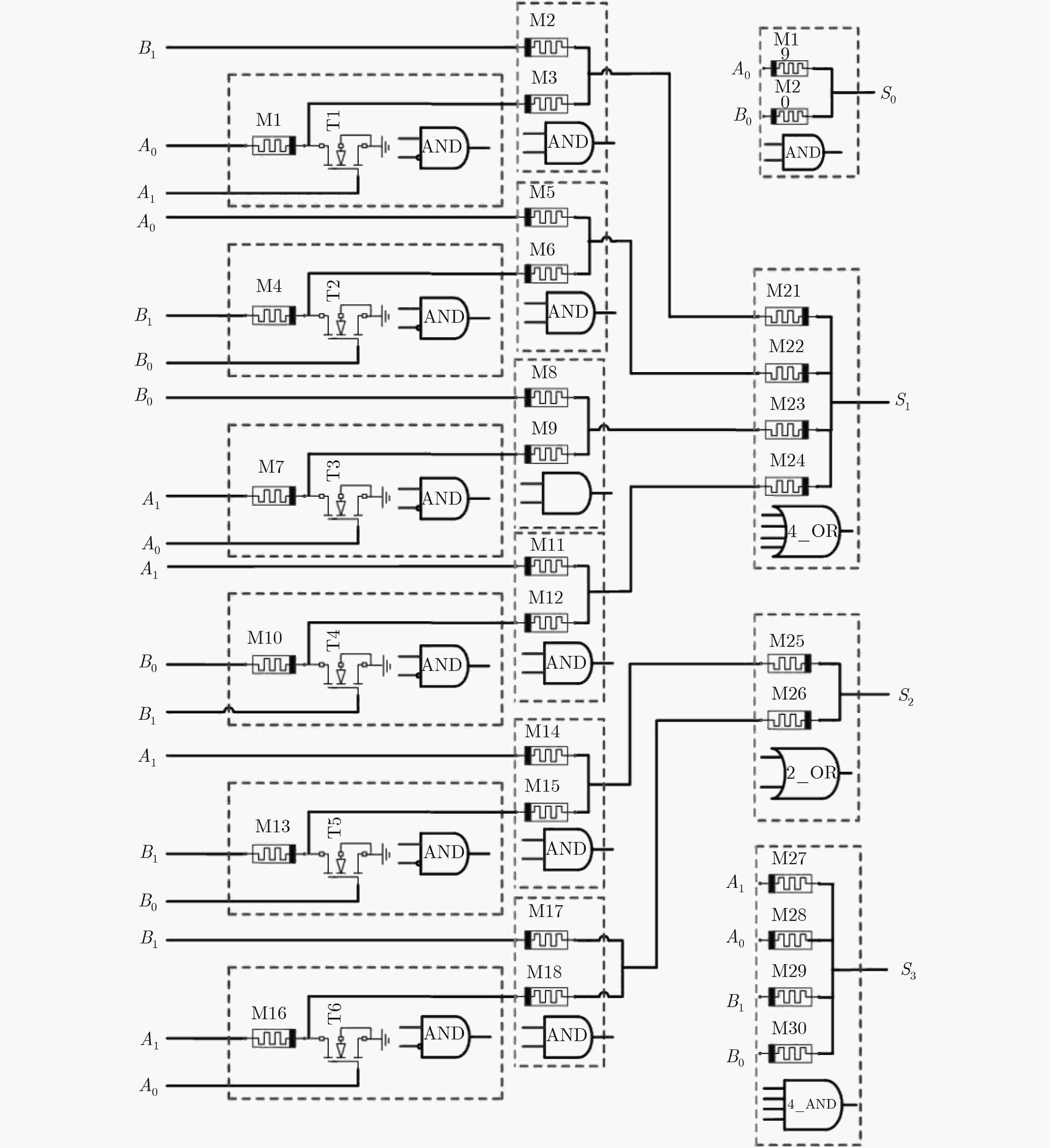

图 7 基于新型比例逻辑的2位二进制乘法器

Figure 7.

-

图 8 基于多功能模块的2位二进制乘法器

Figure 8.

-

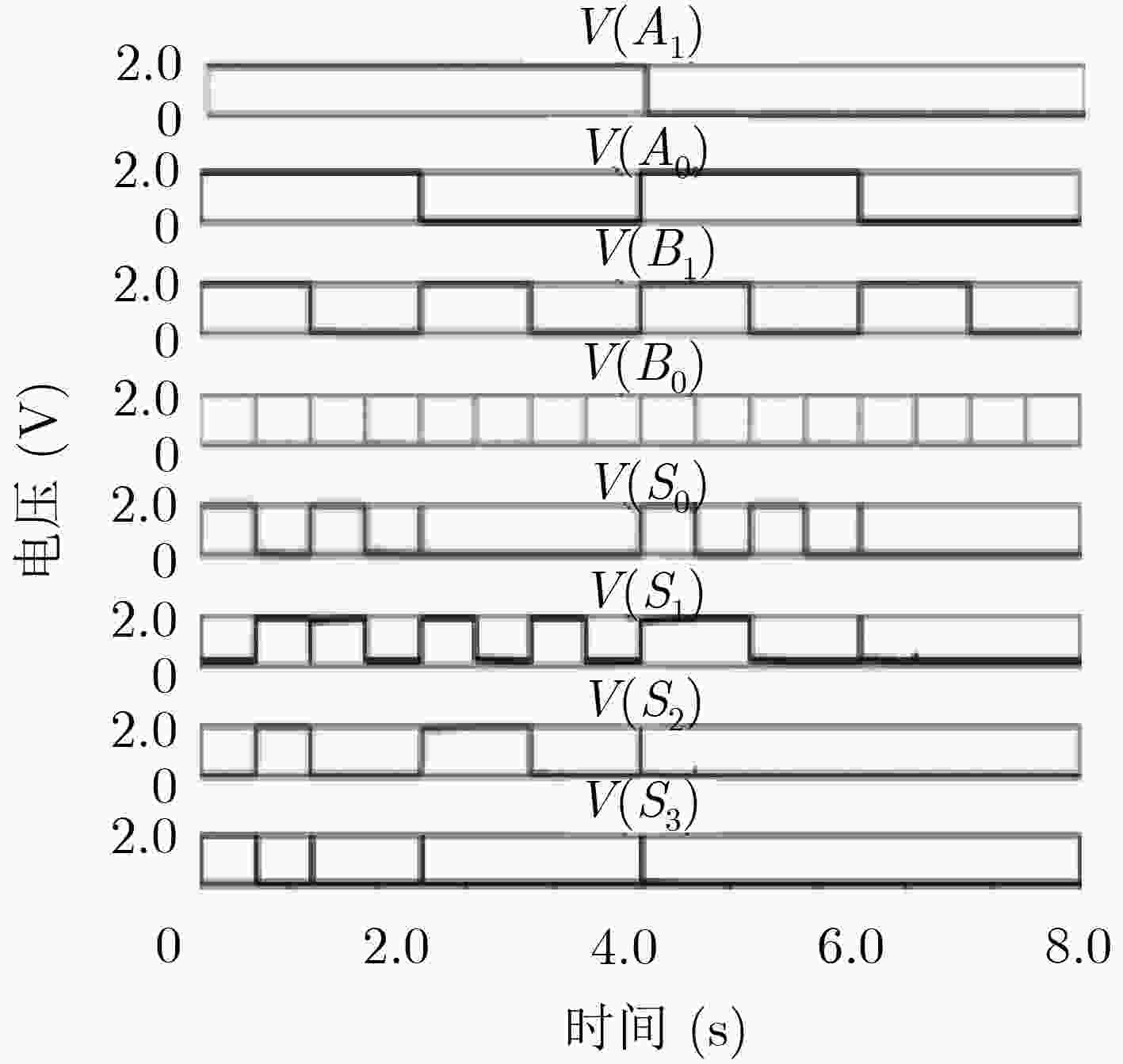

图 9 基于新比例逻辑的2位二进制乘法器仿真结果

Figure 9.

-

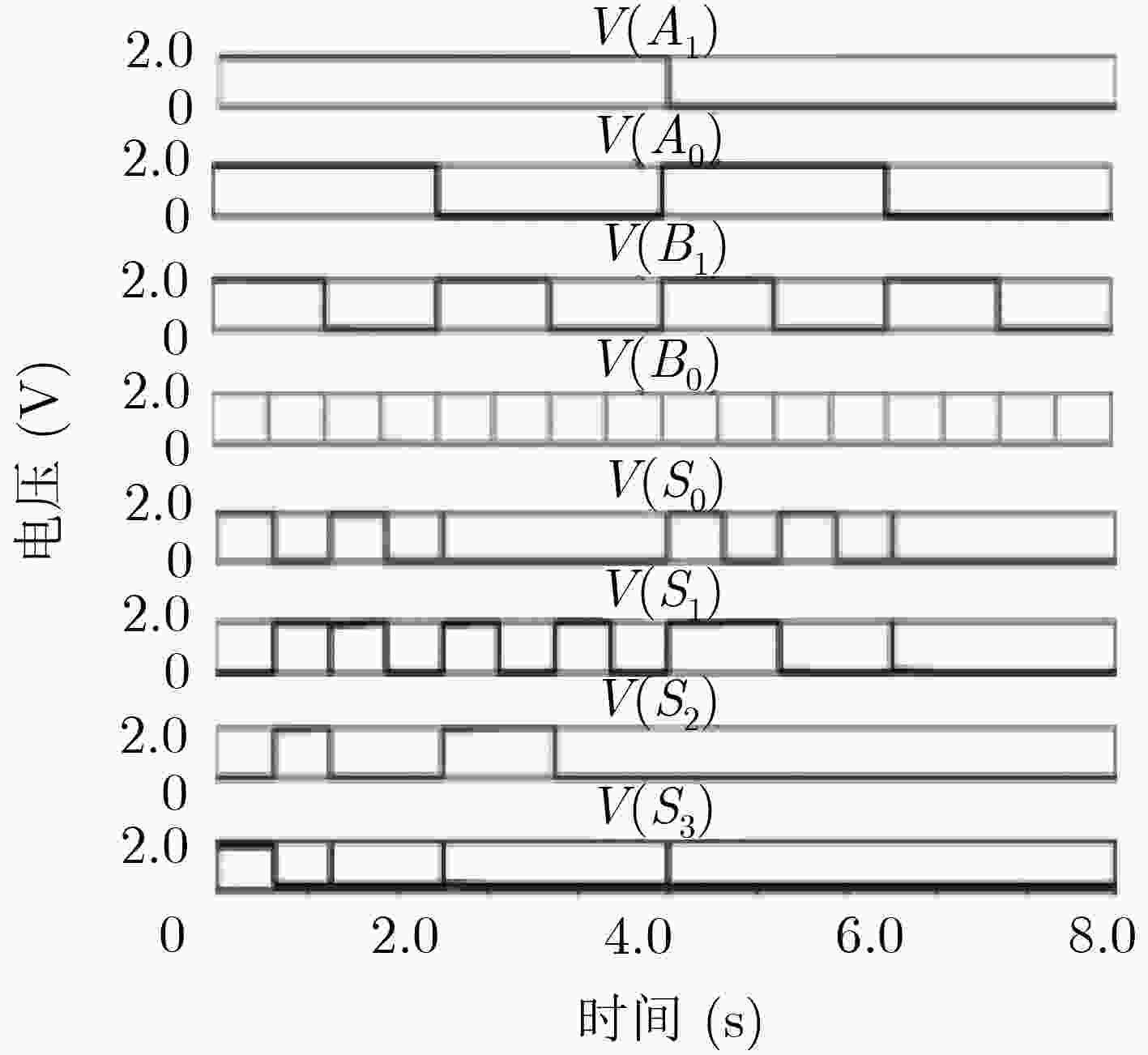

图 10 基于多功能模块的2位二进制乘法器仿真结果

Figure 10.

-

表 1 不同“异或门”之间的元器件使用数量比较

-

表 2 2位二进制乘法器元器件使用数量

图共

10 个 表共

2 个