-

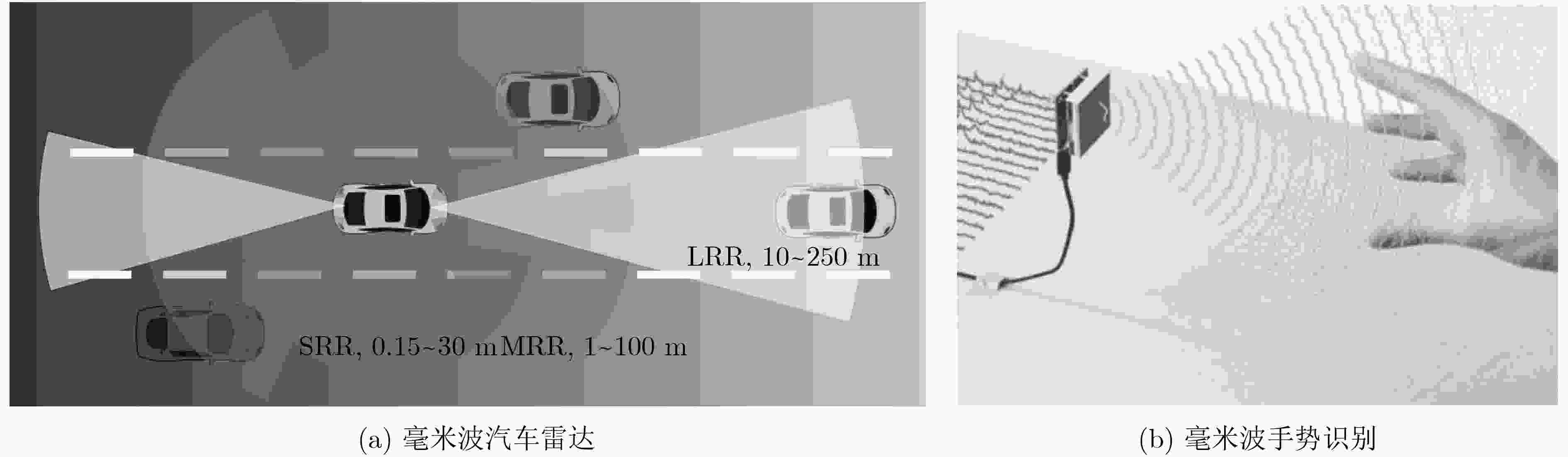

图 1 毫米波汽车雷达和谷歌Soli项目[14]

Figure 1.

-

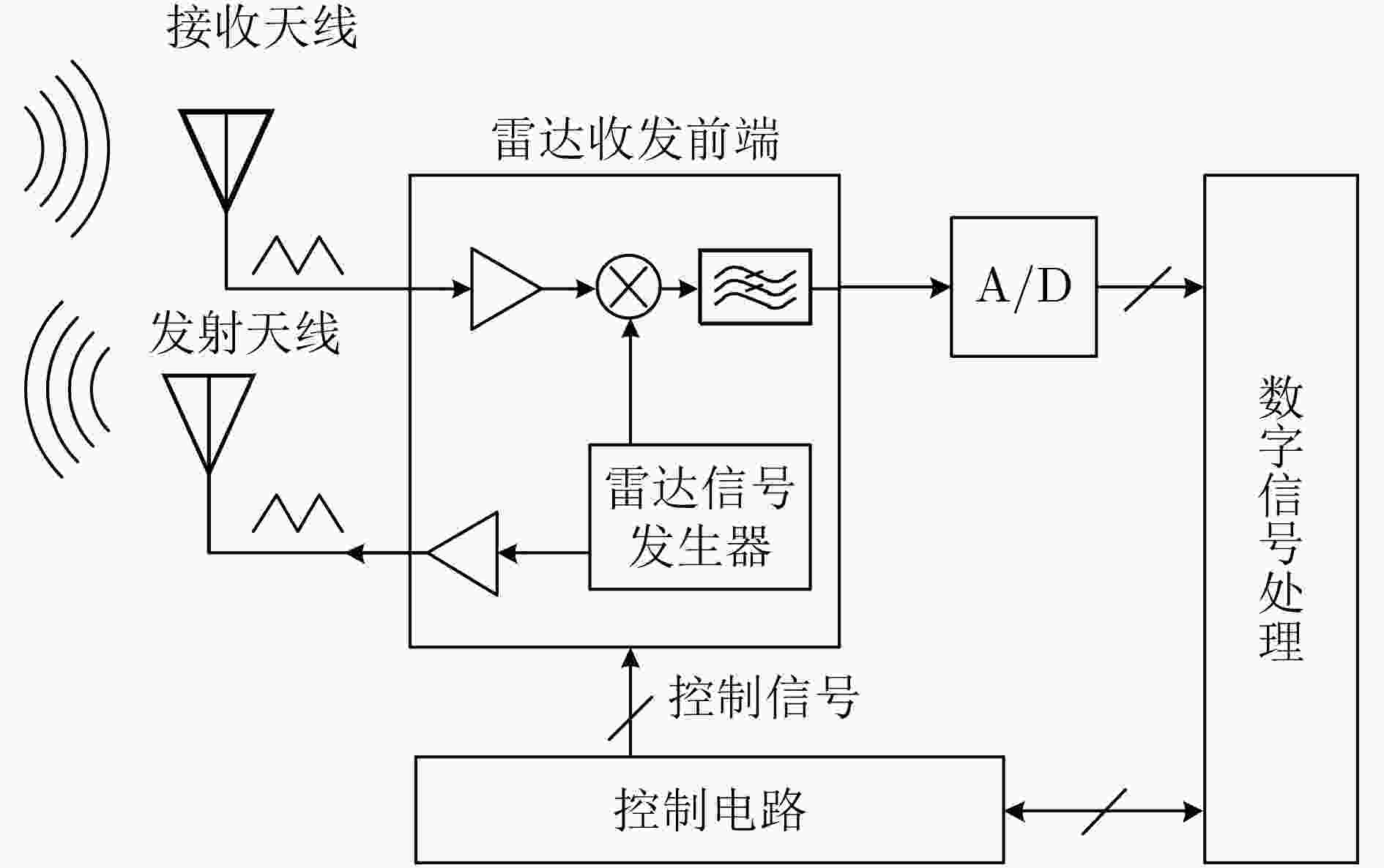

图 2 毫米波雷达系统基本结构

Figure 2.

-

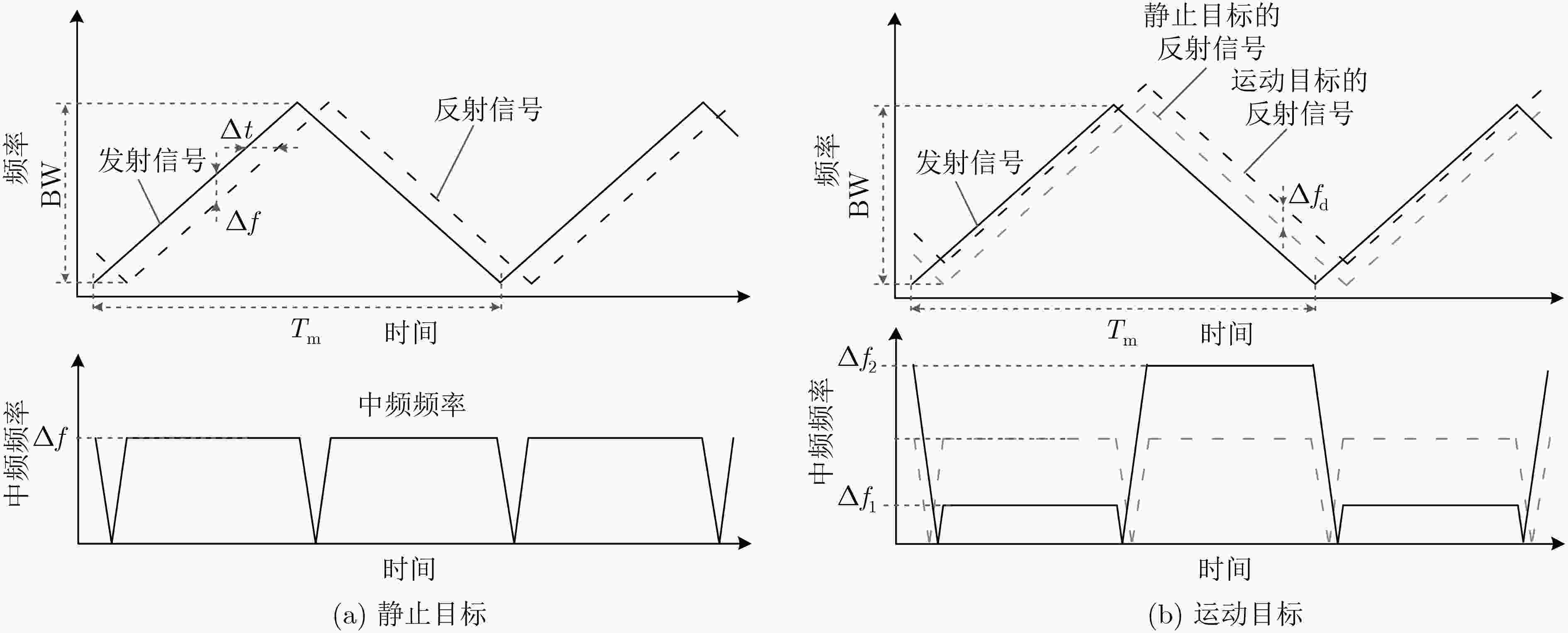

图 3 FMCW雷达探测静止目标和运动目标的原理示意图

Figure 3.

-

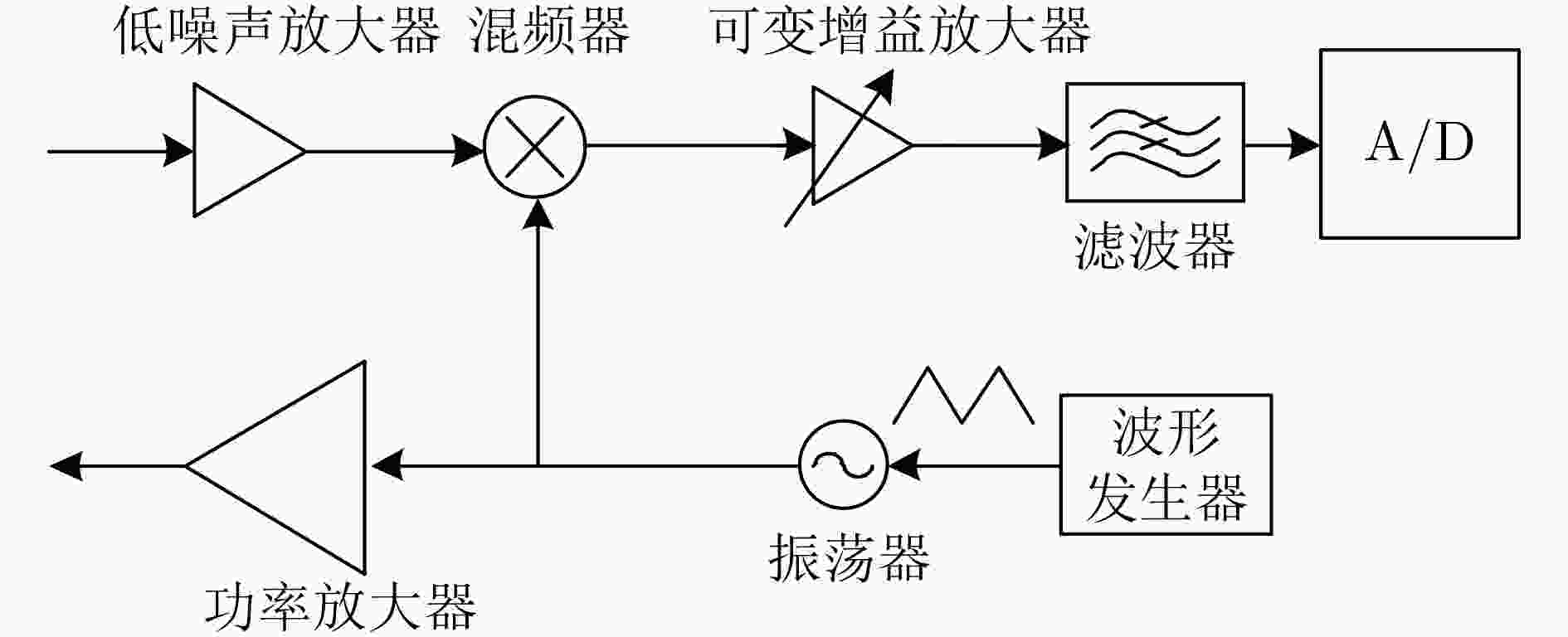

图 4 基本FMCW毫米波雷达收发机前端芯片结构图

Figure 4.

-

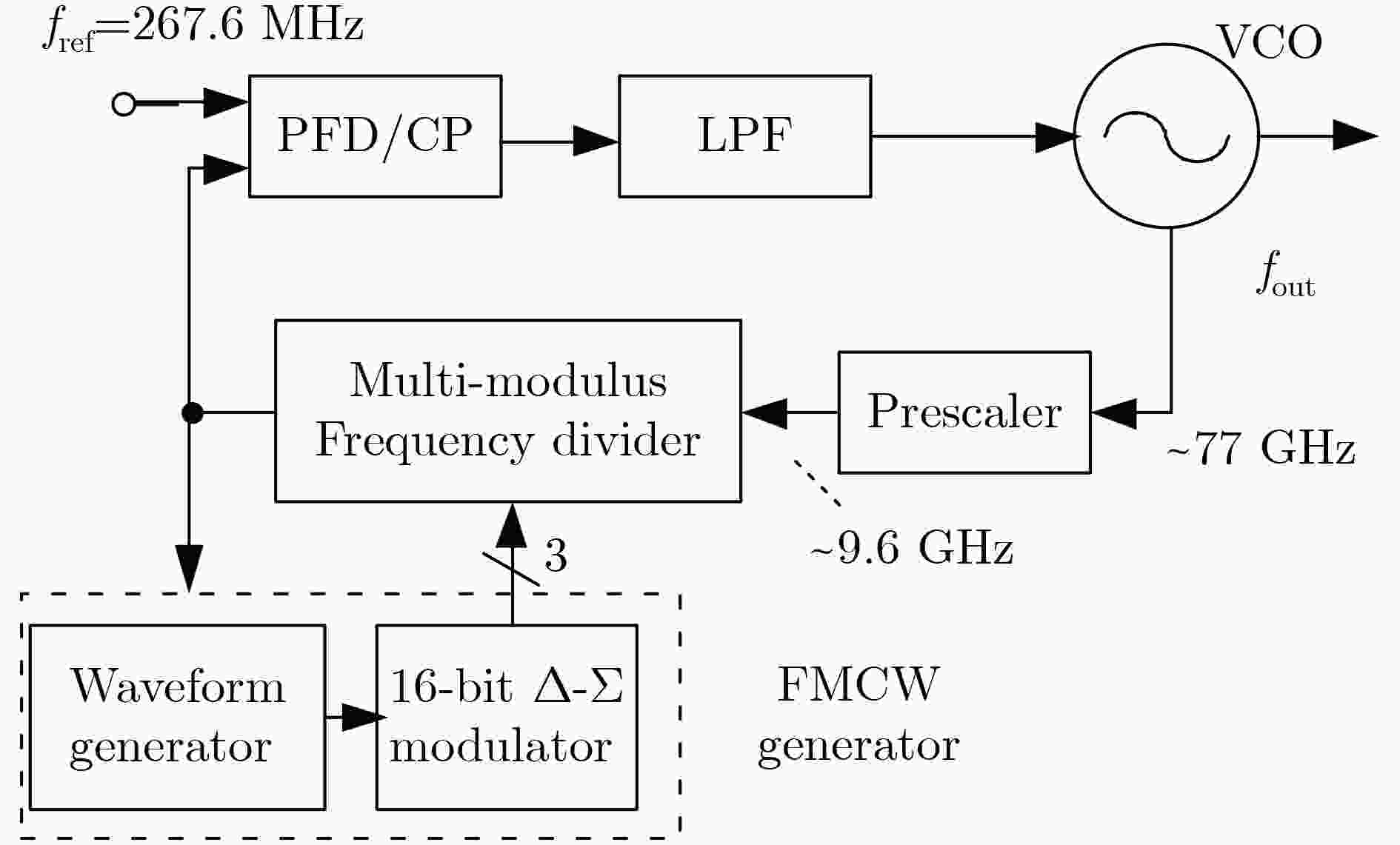

图 5 文献[34]中基于DSM小数型锁相环的FMCW信号发生器

Figure 5.

-

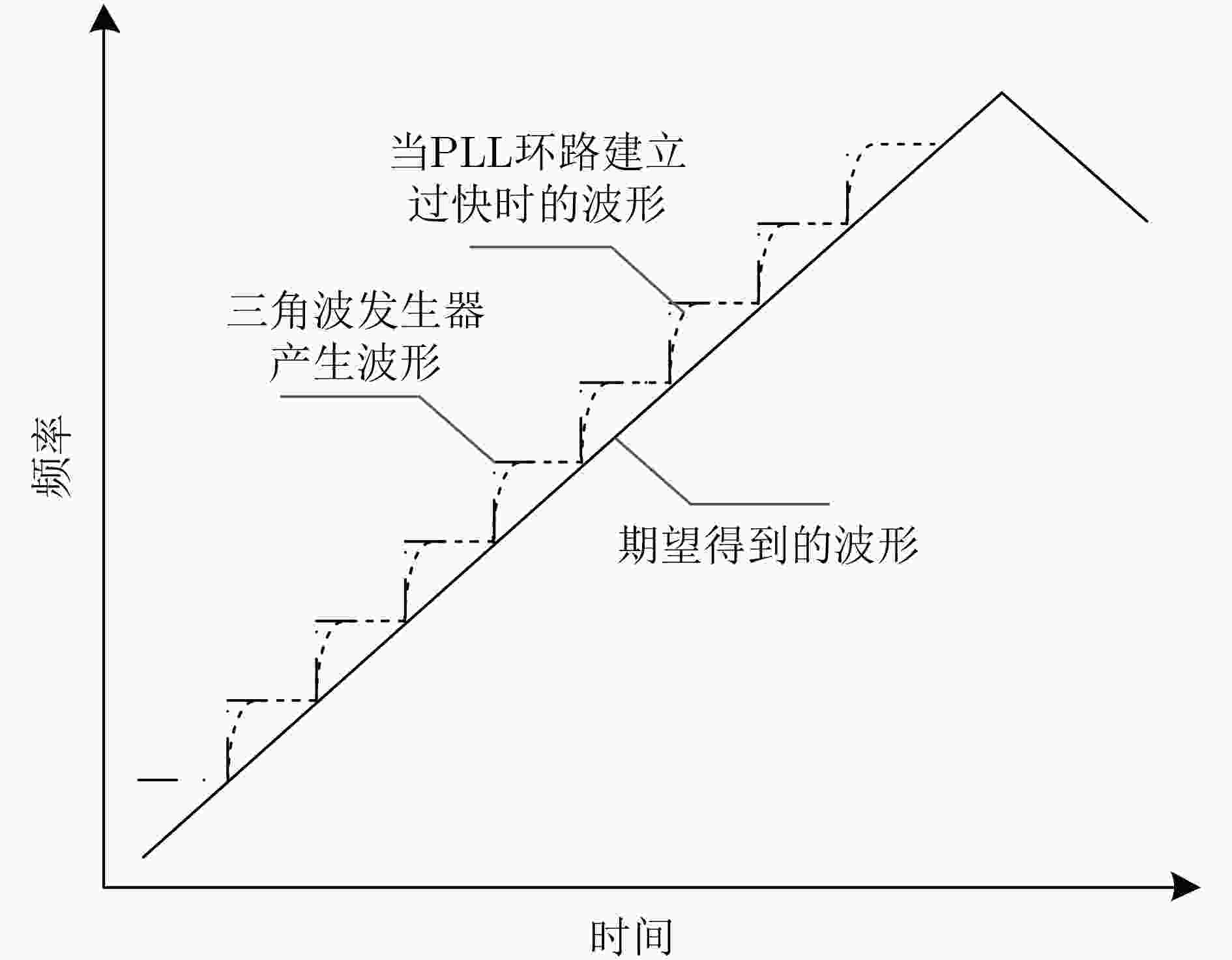

图 6 当锁相环建立时间过快时的输出FMCW频率波形

Figure 6.

-

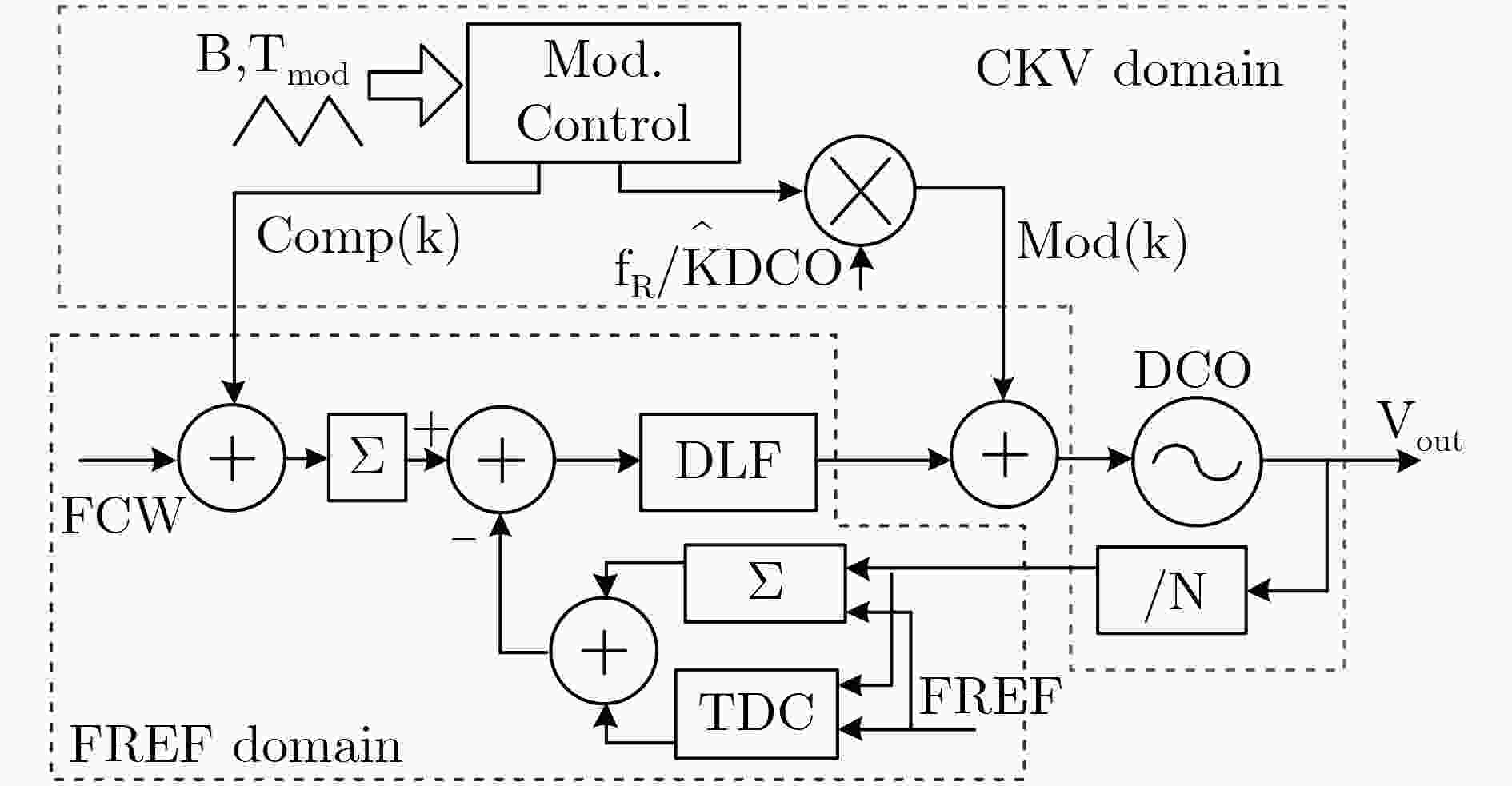

图 7 全数字锁相环用于毫米波FMCW信号产生[37]

Figure 7.

-

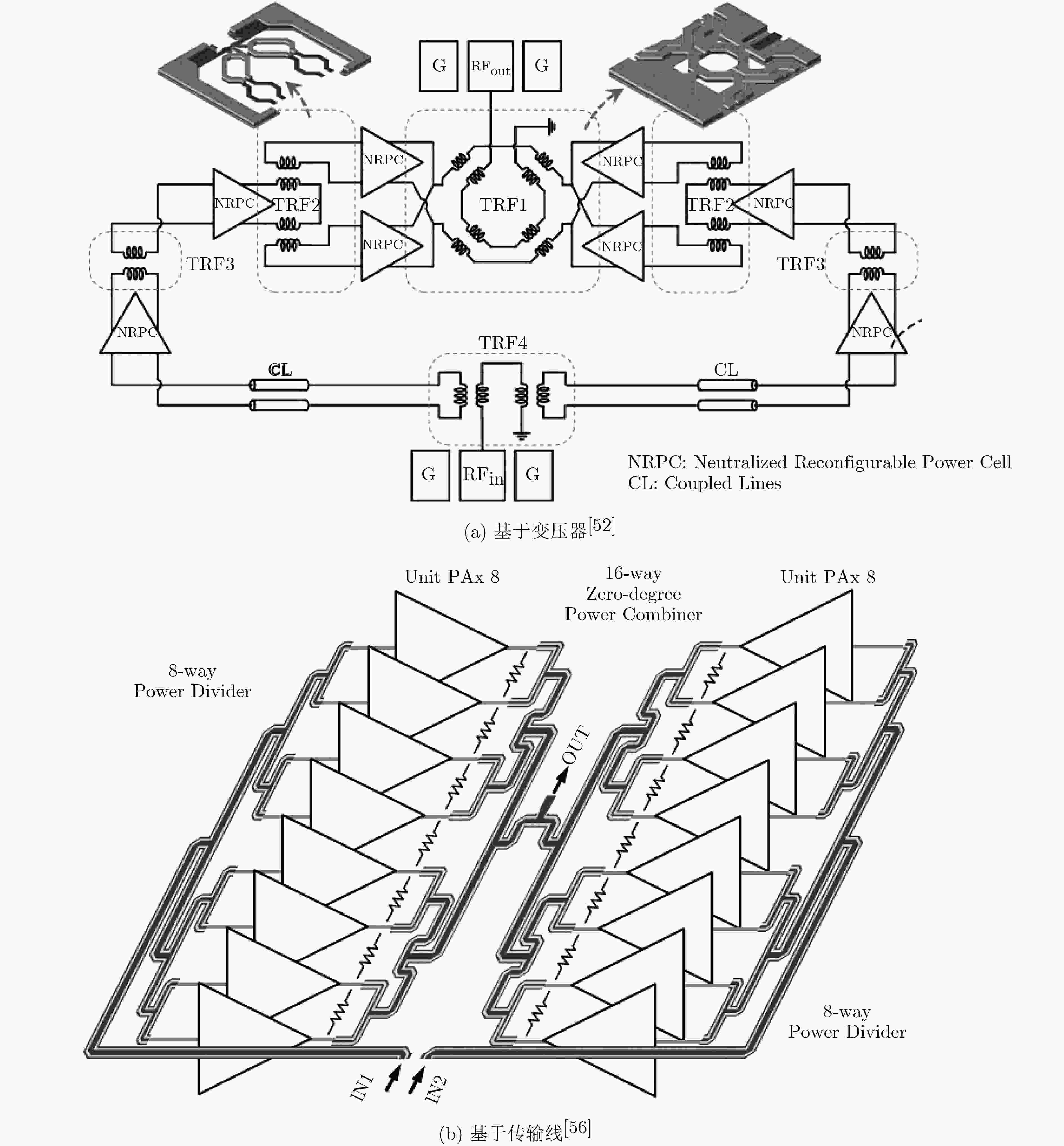

图 8 合成型功率放大器

Figure 8.

-

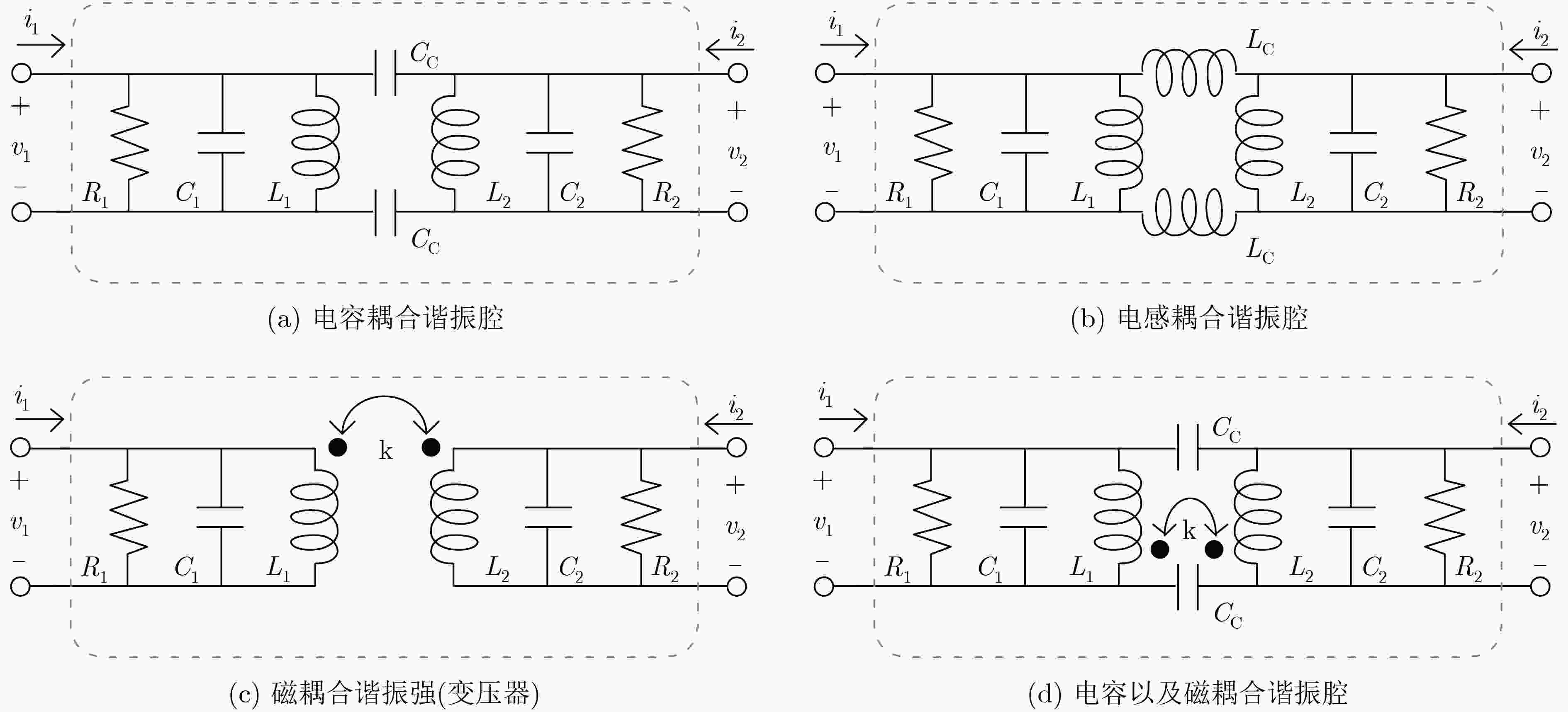

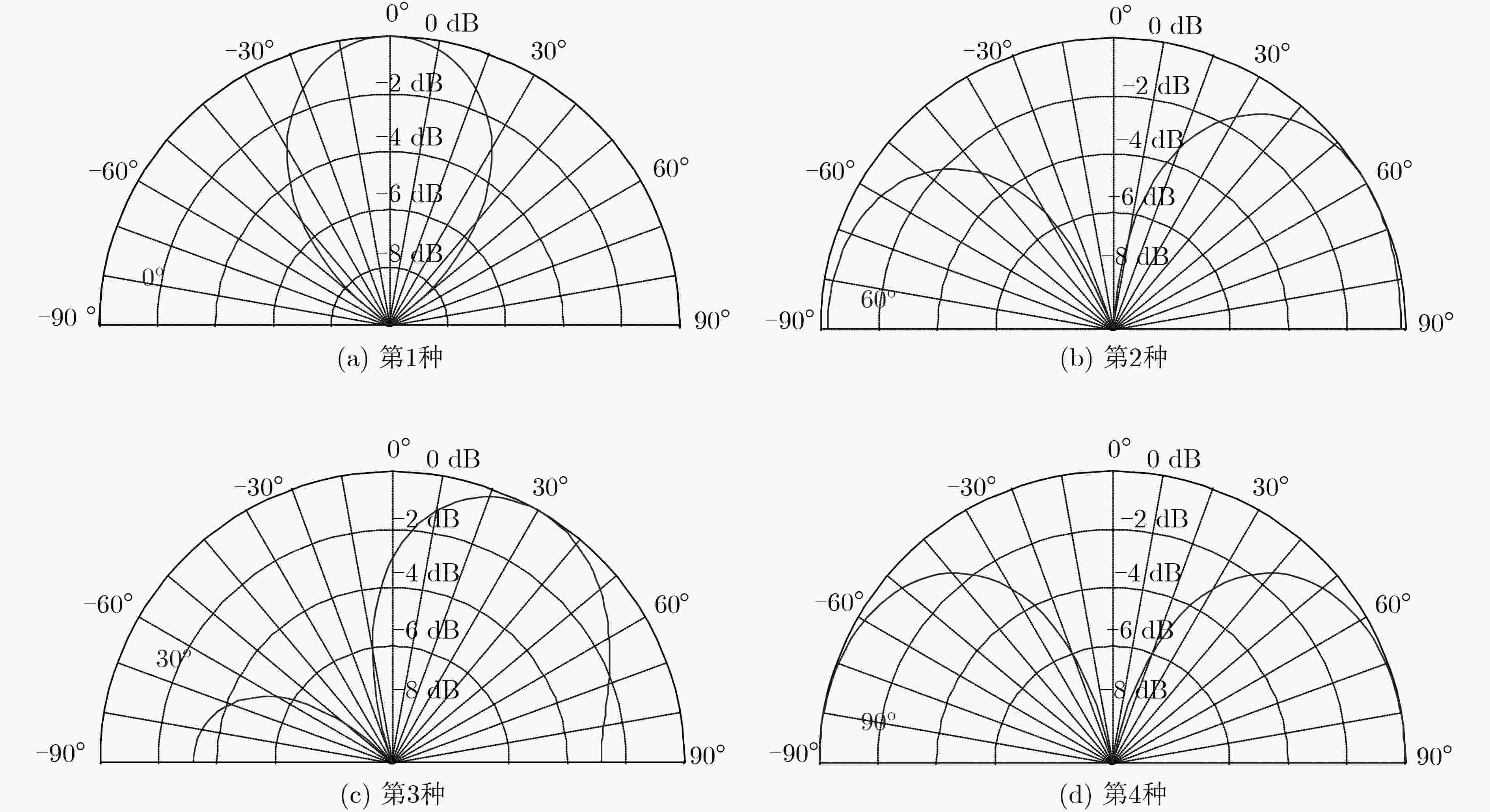

图 9 4种4阶匹配网络[66]

Figure 9.

-

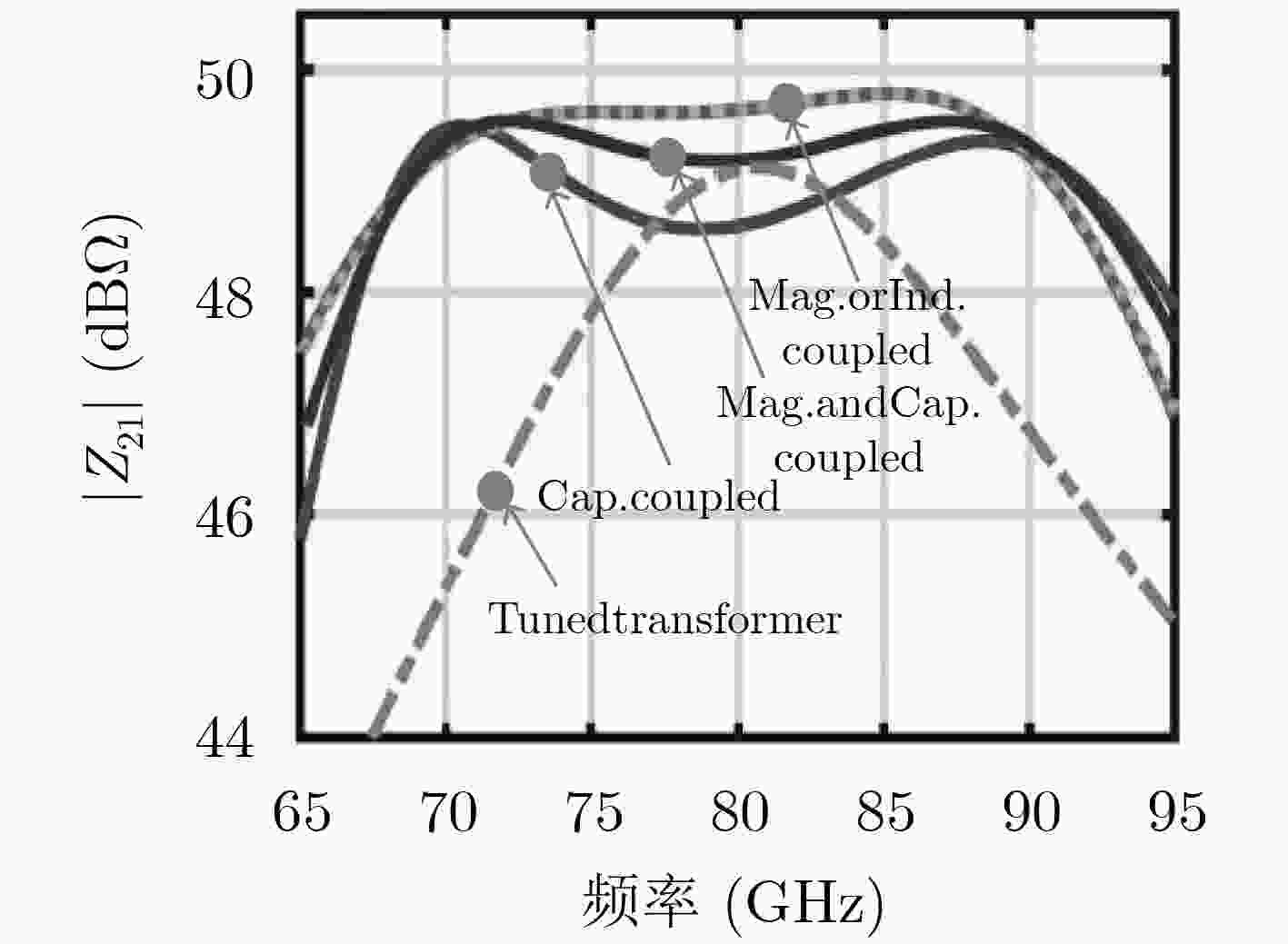

图 10 4种4阶匹配网络的频率响应对比[66]

Figure 10.

-

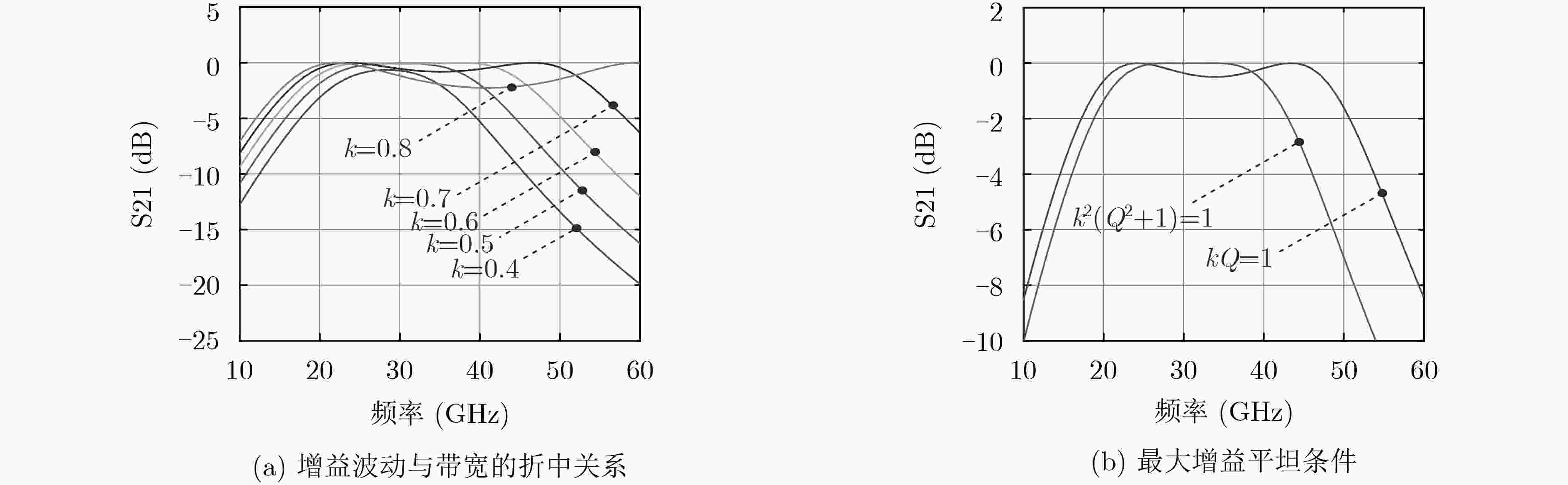

图 11 基于变压器耦合谐振腔的特性[67]

Figure 11.

-

图 12 理想两单元相控阵不同波束指向的雷达方向图

Figure 12.

-

图 13 片上传输线与键合线协同设计以提高其带宽[81]

Figure 13.

-

图 14 工作在60 GHz的键合线天线,增益为4 dBi[80]

Figure 14.

-

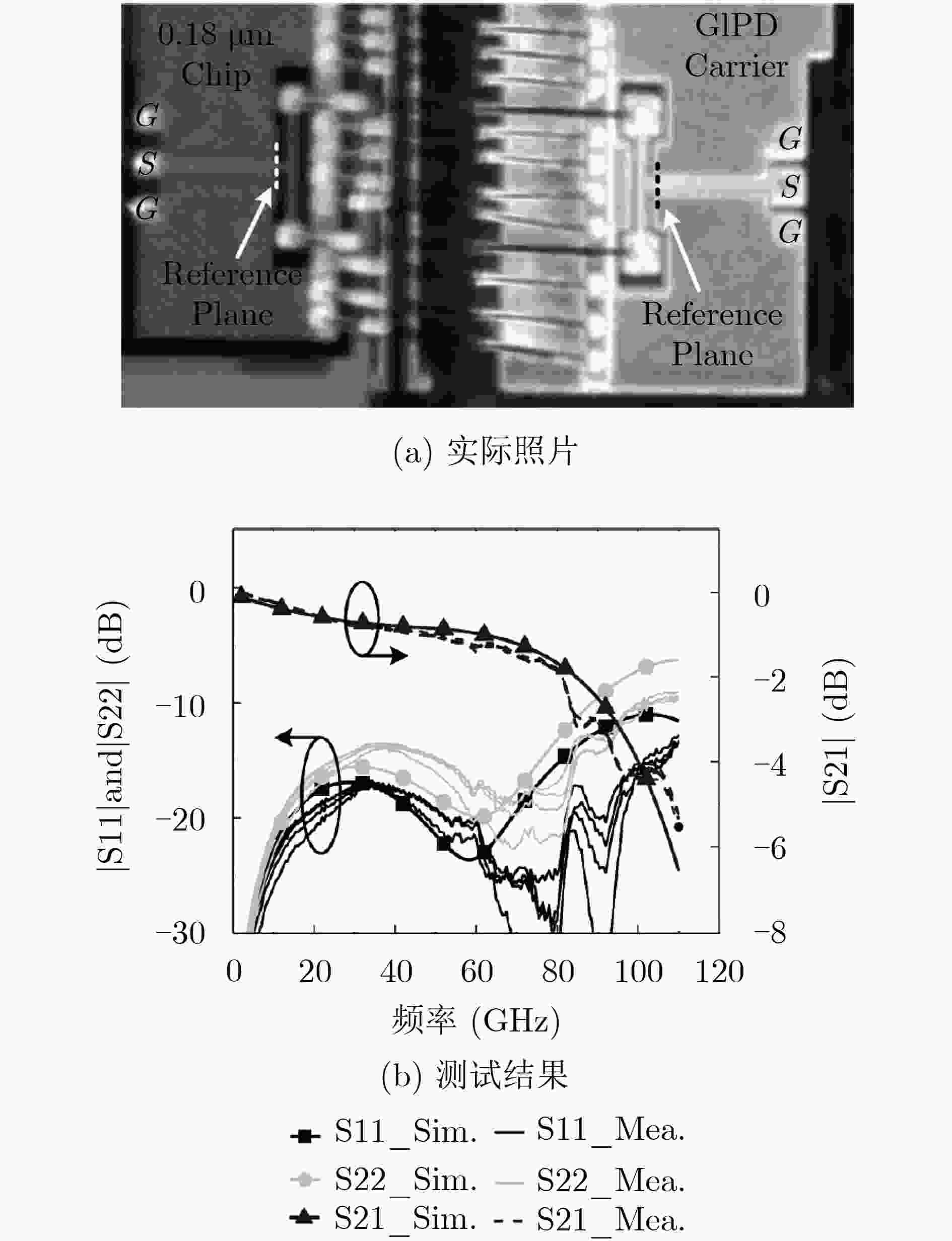

图 15 文献[82]倒封装

Figure 15.

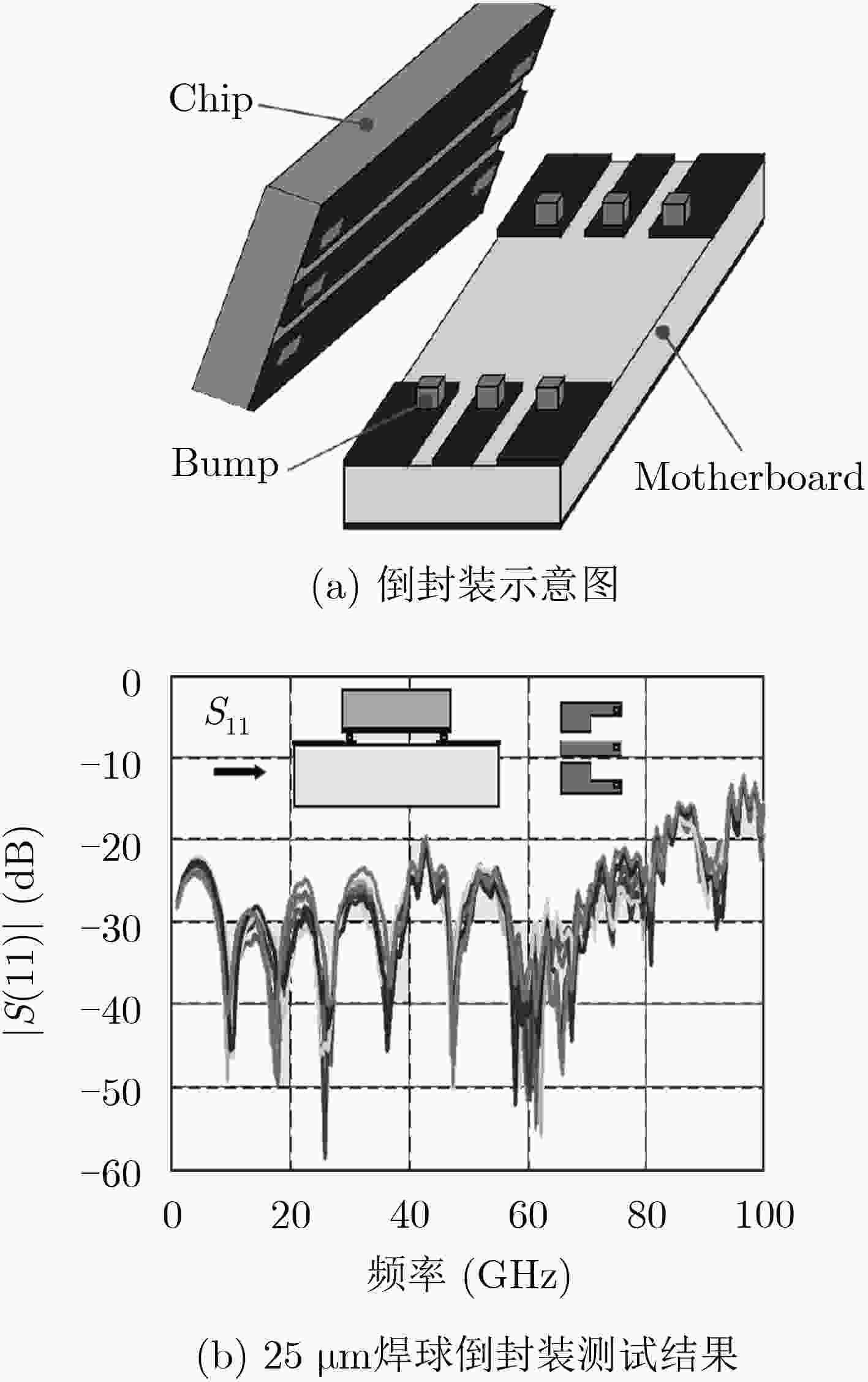

-

图 16 封装天线示意图[84]

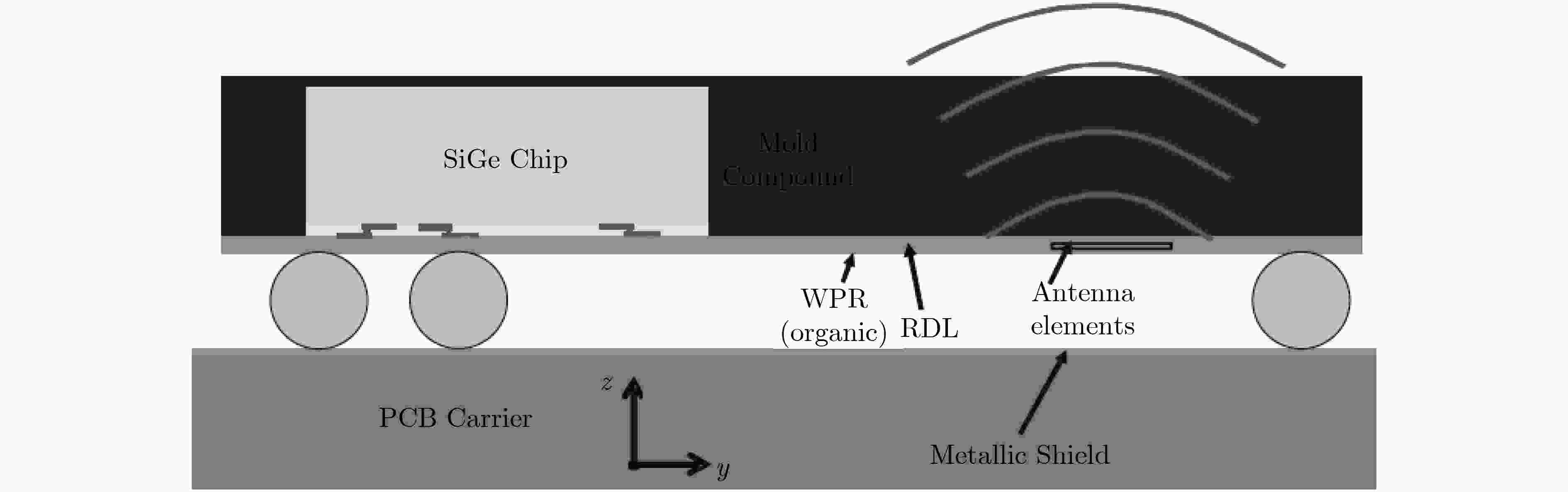

Figure 16.

-

图 17 在封装中集成了2×2的接收天线阵列以及1×2的发射天线阵列[13]

Figure 17.

-

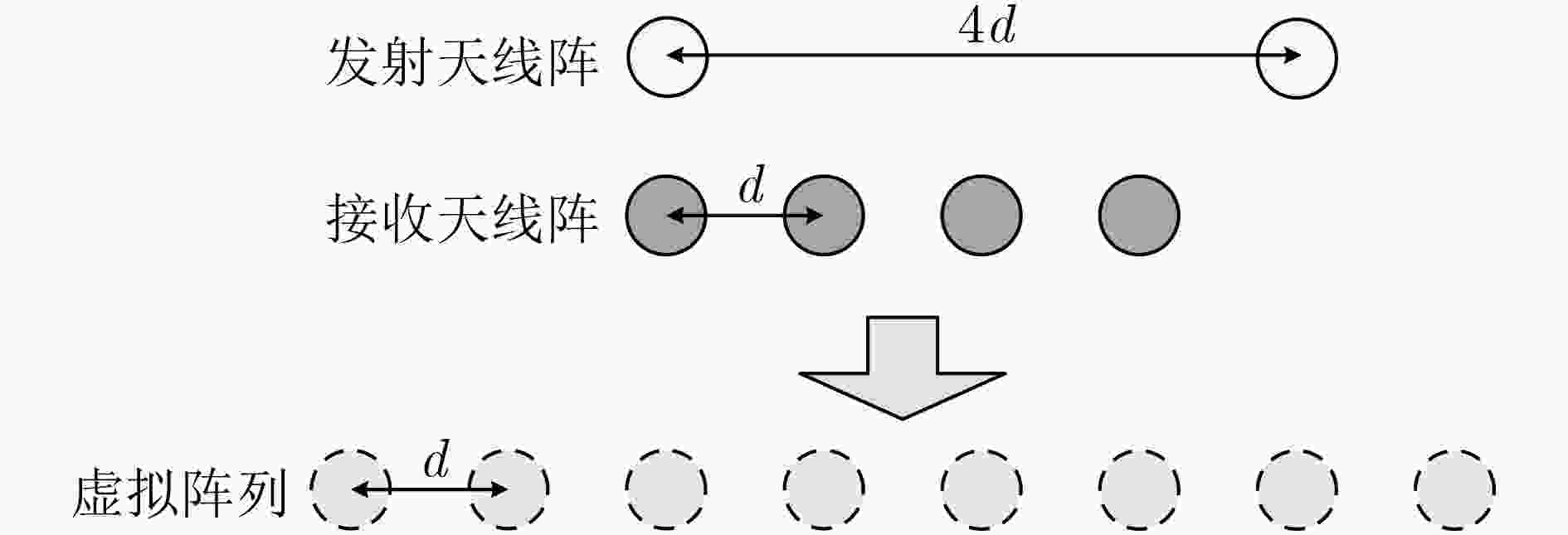

图 18 MIMO天线阵列配置示意图

Figure 18.

-

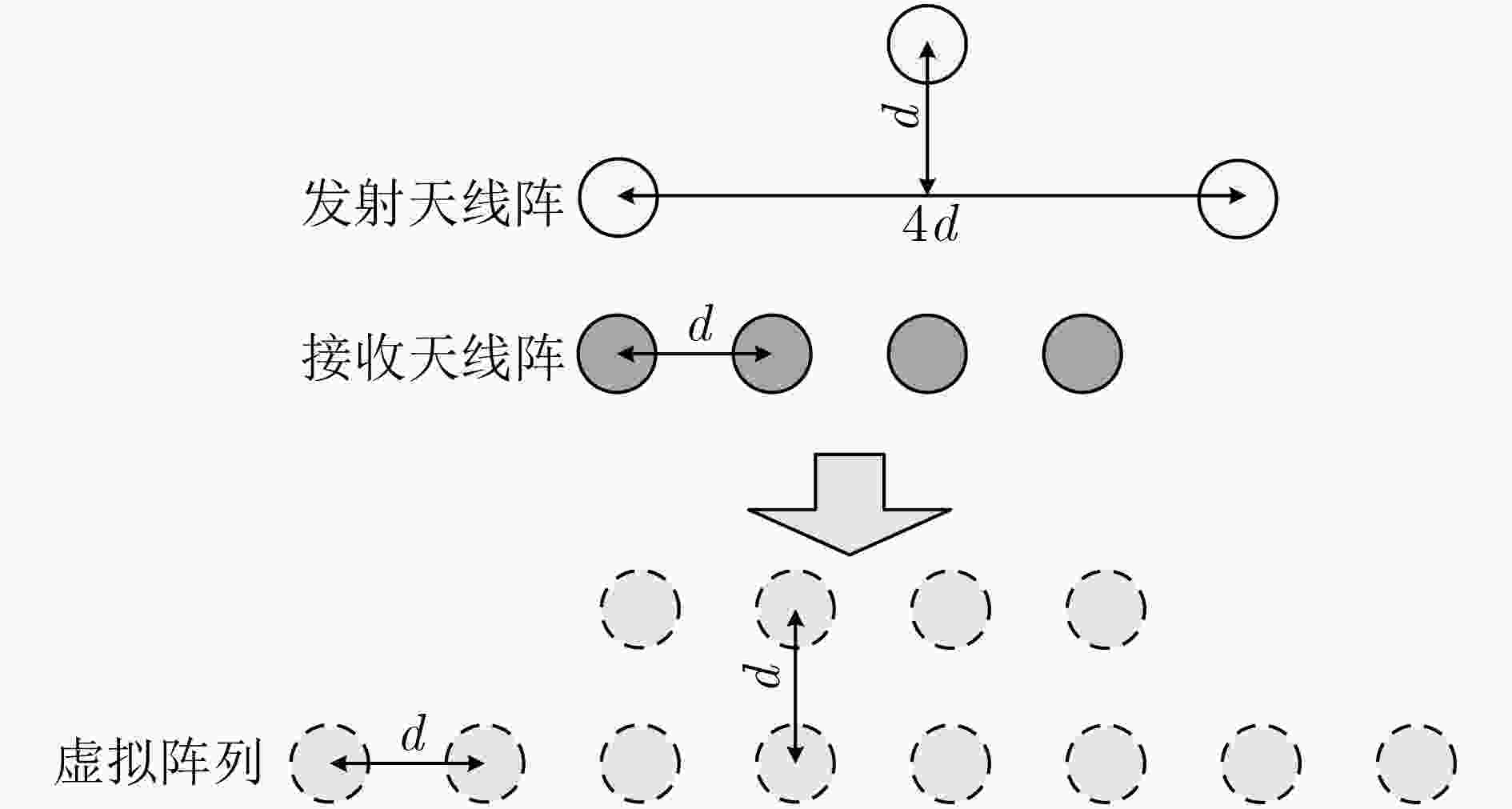

图 19 2维MIMO天线阵列配置示意图

Figure 19.

-

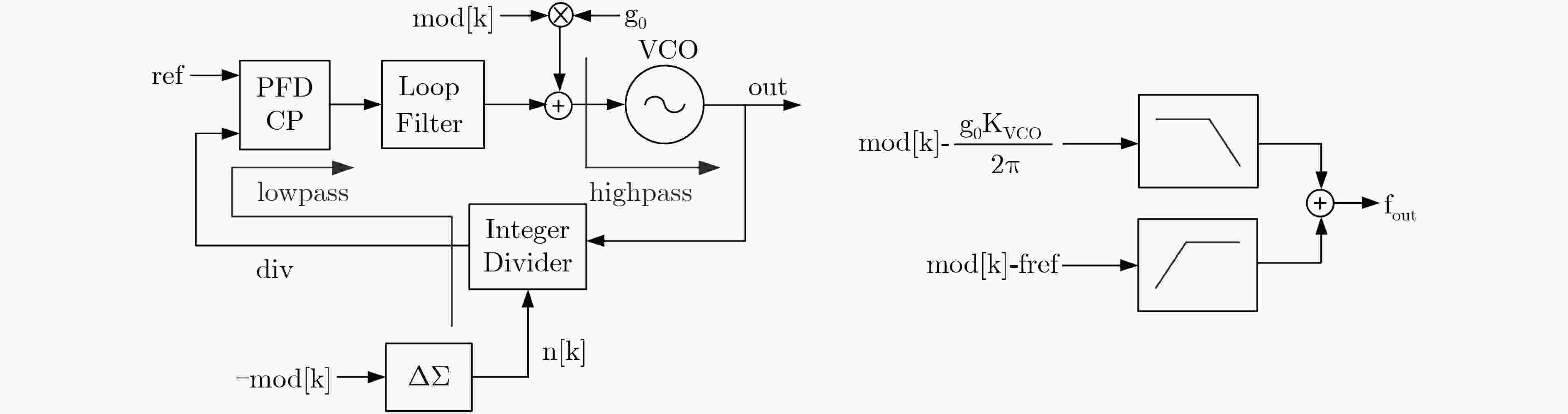

图 20 两点调制基本原理[39]

Figure 20.

-

图 21 采用LMS相关算法校准高通支路与低通支路的匹配[39]

Figure 21.

-

文献编号 [5] [27] [28] [33] [34] [37] [42] [43] 工艺 65 nm CMOS, 65 nm CMOS, 65 nm CMOS, 90 nm CMOS, 65 nm CMOS, 65 nm CMOS, 65 nm CMOS, 40 nm CMOS, 结构 DSM小数环 DSM小数环 DSM小数环 DDFS整数环 DSM小数环 全数字小数环 混合信号小数环 CTDSM小数环 频率(GHz) 76.0 76~81 77 77 76 60 83 37 扫频带宽(GHz) 0.700 0.500 1.930 0.614 0.700 1.220 1.500 0.500 RMS频差(kHz) 64 ±961 674 >1000 <73 117 <180 820 功耗(mW) 73.0 320.0 N/A 101.0 51.4 48.0 152.0 68.0 面积(mm2) N/A 2.74 0.44 ~0.50 0.29 0.72 1.70 0.18 表 1 FMCW信号发生器性能汇总

-

文献编号 [49] [50] [51] [52] [53] [54] [55] [56] [57] 工艺 45 nm

CMOS SOI45 nm

CMOS SOI65 nm

CMOS28 nm

UTBB

FD-SOI40 nm

CMOS65 nm

CMOS40 nm

CMOS0.13 μm

SiGe

BiCMOS45 nm

CMOS

SOI结构 堆叠 堆叠 堆叠 功率合成 功率合成 功率合成 功率合成 功率合成 功率合成 频率(GHz) 41.0 45.0 60.0 60.0 60.0 60.0 70.3~85.5 42.0 60.0 电源电压(V) 5.0 2.7 2.5 1.0 1.0 1.0 0.9 4.0/2.4 2.2 PSAT(dBm) 21.6 18.6~19.4 17.6 18.9 17.4 17.7 20.9 28.4 30.1 PAEMAX(%) 25.1 32.0~33.9 20.4 17.7 28.5 11.1 22.3 10.0 20.8 增益(dB) 8.9 9.5 23.5 35.0 21.2 19.2 18.1 18.5 24.7 面积(mm2) 0.300 0.300 0.240 0.162 0.074 0.830 0.190 5.550 6.600 表 2 硅基毫米波功率放大器性能汇总

图共

21 个 表共

2 个