-

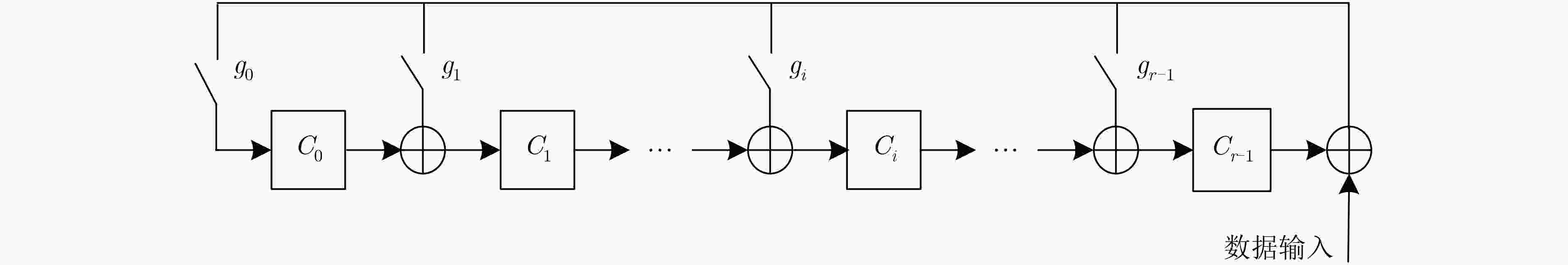

图 1 LFSR实现的串行编解码结构

Figure 1.

-

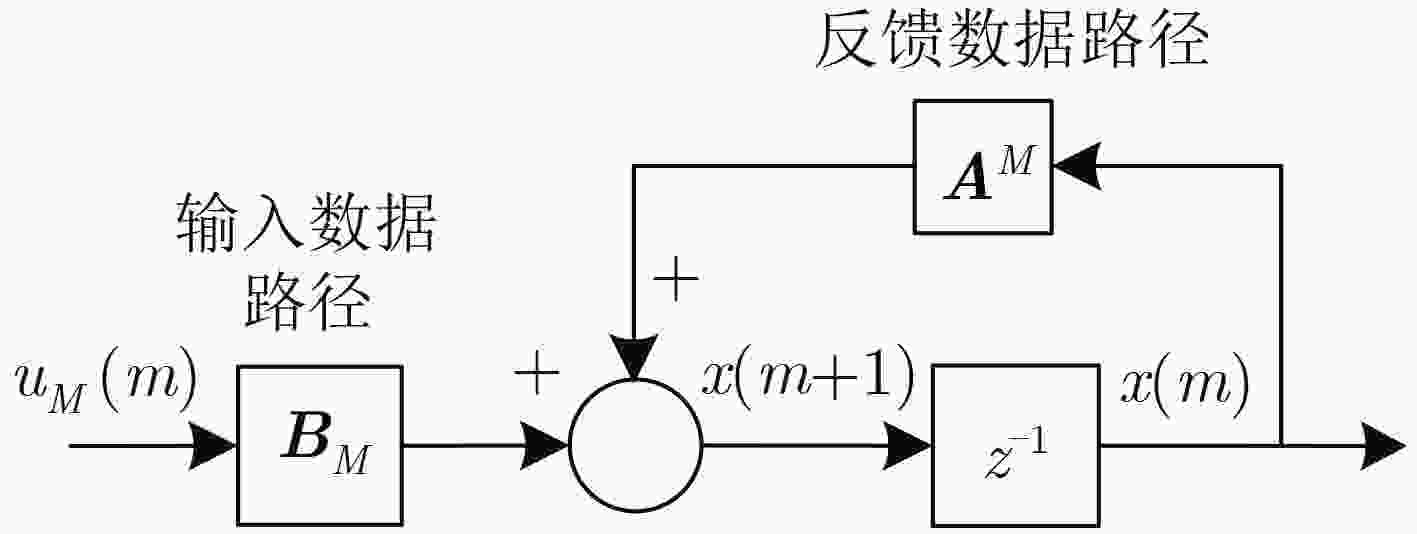

图 2 公式递推法M位并行CRC计算

Figure 2.

-

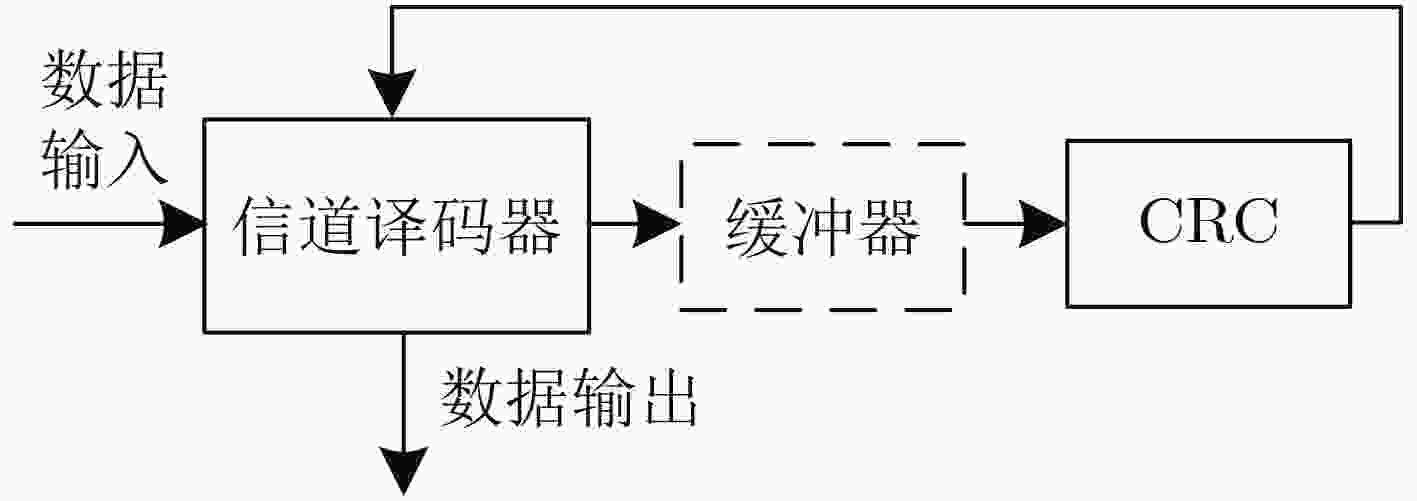

图 3 CRC与信道译码的级联使用

Figure 3.

-

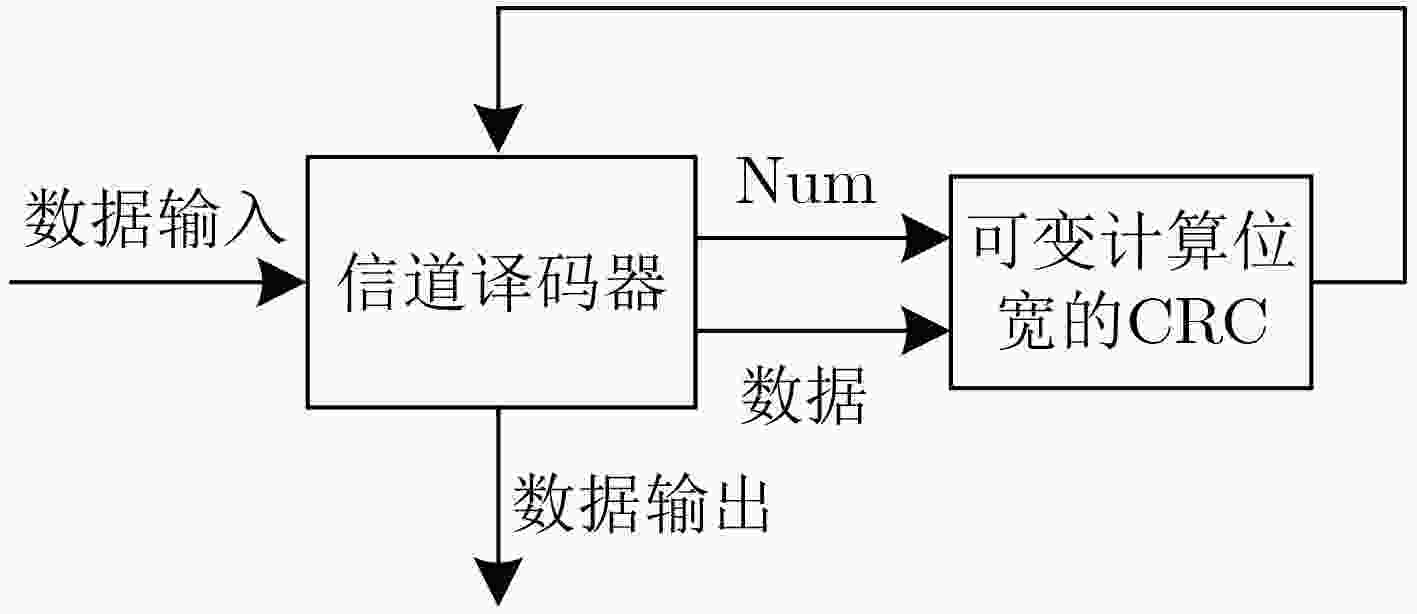

图 4 可变计算位宽的CRC级联系统

Figure 4.

-

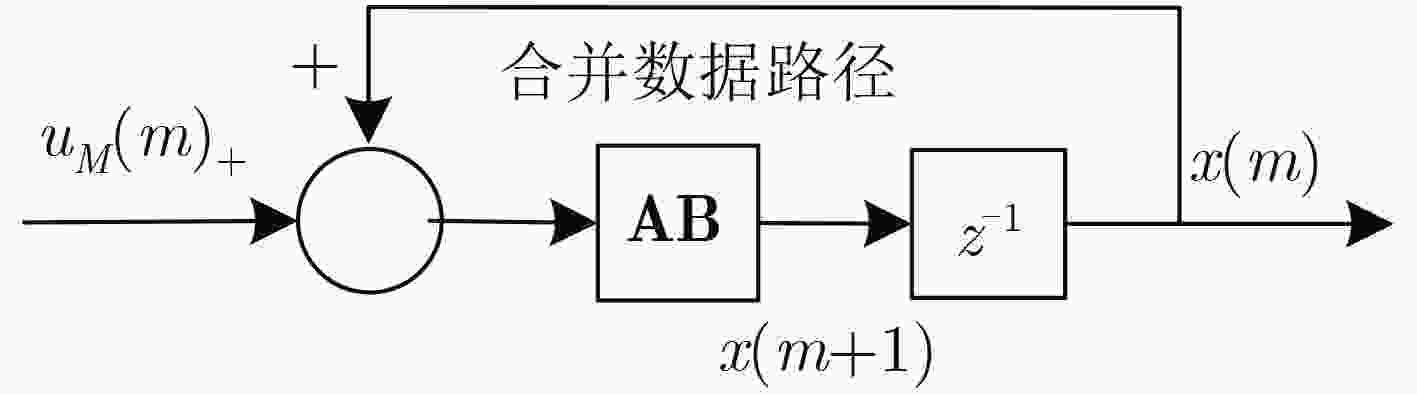

图 5 M位固定位宽合并计算

Figure 5.

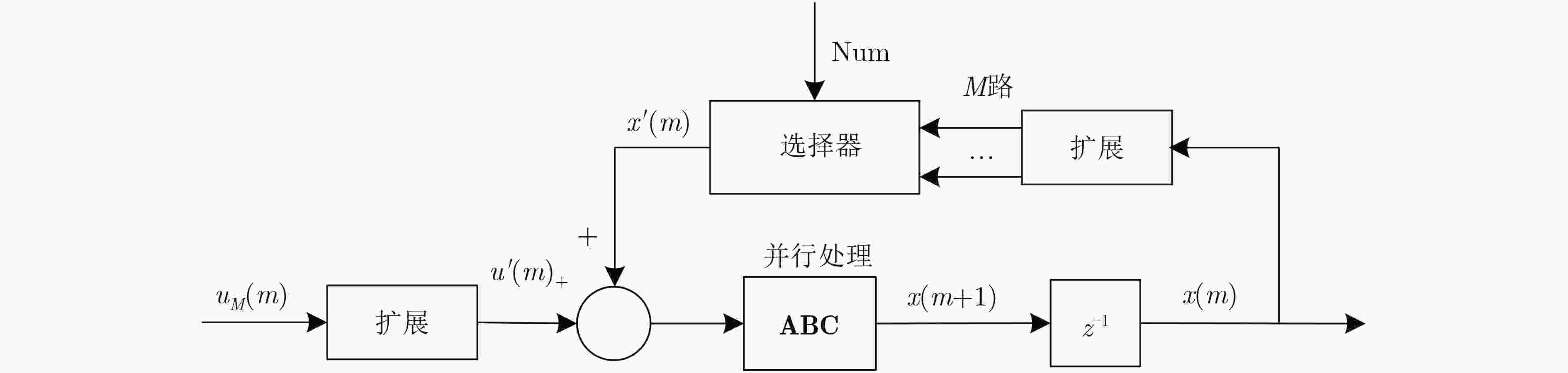

-

图 6 1~M位计算位宽可变的CRC计算

Figure 6.

-

图 7 1~32位并行度可变的CRC编码RTL实现

Figure 7.

-

项目 值 顶层实体名 crc_24 芯片 EP3C5E144C7(Cyclone III) 逻辑器件数 434/5136(8%) 寄存器数 26 管脚数 68/95(72%) 表 1 硬件资源开销

-

总长度

(bit)Num Matlab结果 仿真结果 数据1 60 7, 24, 29 001111010110111111110110 24’h3d6ff6 数据2 65 23, 32, 10 001110000010011011010001 24’h3826d1 数据3 70 24, 15, 31 011111100000011111011011 24’h7e07db 表 2 仿真测试结果

-

CRC 生成多项式 CRC-12 ${x^{12}} + {x^{11}} + {x^3} + {x^2} + x + 1$ CRC-16 ${x^{16}} + {x^{15}} + {x^2} + 1$ CRC-32 $\begin{array}{l}{x^{32}} + {x^{26}} + {x^{23}} + {x^{22}} + {x^{16}} + {x^{12}} + {x^{11}} + \\{x^{10}} + {x^8} + {x^7} + {x^5} + {x^4} + {x^2} + x + 1\end{array}$ 表 3 选用的生成多项式

-

CRC式子(M=r) 算法 总计 1 异或 关键路径 CRC-12(12) 文献[7] 136 112 9 文献[8] 120 66 8 文献[10] – 103 8 文献[9] 77 53 8 固定 52 43 5 可变 64 78 9 CRC-16(16) 文献[7] 218 186 10 文献[8] 188 98 10 文献[10] – 94 10 文献[9] 100 60 9 固定 72 54 5 可变 88 101 9 CRC-32(32) 文献[7] 1031 967 12 文献[8] 928 518 12 文献[10] – 675 10 文献[9] 888 461 12 固定 452 313 6 可变 484 408 11 表 4 电路资源和关键路径长度比较

图共

7 个 表共

4 个