# Nov. 2013

# FPGA 开关矩阵中基于通道结构的漏电流优化方法

王

一<sup>①2</sup>

杨海钢\*<sup>①</sup>

余

乐 <sup>①2</sup>

孙嘉斌<sup>①</sup>

①(中国科学院电子学研究所

北京

100190)

<sup>②</sup>(中国科学院大学

北京

100049)

摘 要:从通道互连结构角度考虑,该文提出一种降低 FPGA 中开关矩阵漏电流的方法。根据漏电流与电路输入、输出状态有关的结论,利用连线开关盒(SWB)对信号的传输特性,将 FPGA 中开关矩阵的漏电优化等效在小规模的矩阵单元中实现。因为能够在有限的输出状态组合中搜寻最小漏电状态,相比仅通过电平恢复器确定 SWB 输出状态的方法,该算法能有效地降低漏电流,并且兼容电路级的漏电流优化方法。

关键词: FPGA; 互连结构; 开关矩阵; 开关盒; 漏电流

中图分类号: TN47 文献标识码: A

**DOI**: 10.3724/SP.J.1146.2013.00242

# Leakage Current Optimization for FPGA Switch Matrixes Based on Routing Architecture

Wang Yi<sup>©®</sup> Yang Hai-gang<sup>©</sup> Yu Le<sup>©®</sup> Sun Jia-bin<sup>©</sup>

<sup>©</sup>(Institute of Electronics, Chinese Academy of Sciences, Beijing 100190, China)

<sup>®</sup>(University of Chinese Academy of Sciences, Beijing 100049, China)

Abstract: From the perspective of routing architecture, a leakage reduction method of switch matrixes in FPGA is proposed. Based on the conclusion of state-dependent leakage, the lowest leakage current of switch matrixes in FPGA is equivalently computed in a small size of matrix cell using the transition property of SWitch Box (SWB). Because the presented algorithm could research the lowest leakage state in finite SWB output state combinations, rather than confirming SWB output state by level-restoring circuit, the algorithm is used for efficient reduction of leakage in switch matrixes and is compatible with the optimization of leakage at the circuit-level.

Key words: FPGA; Routing architecture; Switch matrixes; SWitch Box (SWB); Leakage current

#### 1 引言

随着 FPGA 性能和密度的提高,功耗逐渐成为 FPGA 应用的瓶颈。尤其是当工艺进入深亚微米后,漏电(静态)功耗在总功耗中的比例逐渐提高,当工艺达到 65 nm 以下时,漏电功耗将超过总功耗的 50%[1],而互连结构占有 60~90%的漏电功耗[2-4],因此,研究如何降低 FPGA 互连结构的漏电功耗意义重大。文献[5]研究了如何降低互连结构中选择器在使用状态下的漏电流,考虑到初始上电时 FPGA 所有互连资源均处于空闲状态[6],即使在工作条件下,FPGA 电路中 90%的互连选择器仍处于未使用状态[3],因此,仅考虑使用状态下互连选择器的漏电流优化是不够的;文献[3]通过控制互连开关盒(SWB)输入端信号的 0,1 状态,减小未使用选择器

的漏电流,但只是考虑了输出驱动为2级缓冲器的SWB最小漏电设置,对于复杂的驱动设计考虑不足,因此该方法的通用性不强;文献[7]设计了一种可以工作在睡眠模式下的开关电路,虽然可以降低60%以上的静态功耗,但需要以面积作为代价。

文章编号: 1009-5896(2013)11-2784-06

本文从通道互连结构角度考虑,提出一种降低未使用状态下开关矩阵漏电流的方法。根据通道跳转位置数目,将 FPGA 开关矩阵的漏电优化等效在小规模的矩阵单元中实现,找到具有最小漏电状态的输出设置。并且该方法与 SWB 电路级的漏电优化方法不相冲突。

# 2 SWB的漏电状态

#### 2.1 FPGA 的互连结构

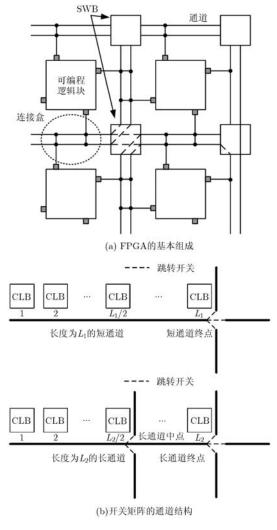

由于现有商用 FPGA 普遍采用基于静态随机存储器(SRAM)的岛型结构,本文选择这种类型的FPGA 作为研究对象。如图 1(a)所示,FPGA 由可编程逻辑单元(Configurable Logic Block, CLB)组

图1 FPGA的基本组成

成,它们之间通过开关矩阵和连接盒(Connection Box, CB)通信。其中开关矩阵包括 SWB 和不同长度的通道<sup>[8-10]</sup>,通道的长度是指横跨 CLB 的数目,一般认为长度小于 6 的通道属于短通道<sup>[5]</sup>。如图 1(b) 所示,短通道为了连接的灵活性,跳转位置通常只有终点,长通道权衡考虑芯片面积和灵活性,一般在通道中点和终点位置选择跳转<sup>[11]</sup>。另外,由于单驱动通道形式在面积、延时方面比多驱动结构具有优势,现代商用 FPGA 芯片已经摒弃了多驱动模式的通道结构<sup>[12]</sup>。

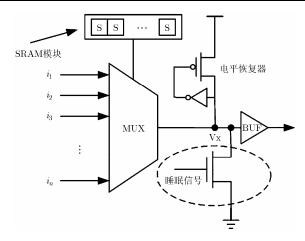

在 FPGA 中,基于 NMOS 传输管的可编程多路选择器是实现 SWB 的关键电路,SWB 的输入源于不同方向和位置上的通道信号,通过配置 SRAM 模块,多路选择器选通一路信号输出至不同方向的通道。如图 2 所示,典型选择器的基本组成为:一个基于 NMOS 传输管的选择阵列,输出驱动电路和 SRAM 配置模块。在图 2 中,MUX 代表传输管阵列,通常由译码或编码电路构成,BUF 代表输出驱

图2 一个典型选择器[7]

动电路。除上述基本组成外,选择器还有一些外围 电路,作用是抑制后级驱动电路产生漏电流,如图 2 中的电平恢复器和虚线框里栅极受控的 NMOS 晶 体管。

#### 2.2 选择器的漏电状态

因为不使用选择器时,所有 SRAM 值都是 0 并且保持不变,另外可以使用高阈值或长沟道的晶体管以降低 SRAM 速度为代价来减少漏电流<sup>[5]</sup>。故本文的 SWB 漏电流优化不考虑消耗在 SRAM 上的漏电流,只讨论 MUX 和 BUF 的漏电优化。

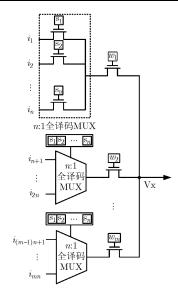

图 3 所示的 MUX 能够权衡考虑延时和面 积[13,14](包括 SRAM 面积), FPGA 中普遍使用这种 两级传输管结构的 MUX。选择器中使用电平恢复器 是为了解决 NMOS 传输管引入的阈值损失, 另外, 当不使用选择器时, 电平恢复器可将浮空点 Vx 上 拉至一个稳定的 1 状态,避免后面的驱动电路产生 漏电流。然而在文献[7]中,为了抑制电平恢复器工 作以获得未使用状态下更小的漏电功耗, Vx 必须设 置为 0 状态,方法是加入一个由睡眠信号控制的最 小尺寸 NMOS 管(如图 2 中虚线框所示)。综上所述, 中间节点 Vx 可以根据需要被设置成固定状态,或 被电平恢复电路上拉到 1; 或被 NMOS 管下拉至 0。 根据电路漏电流与输入状态有关的结论[5,7],因为输 入信号根据 0, 1 状态不同有  $2^{mn}$  种组合,输出有 0, 1 两种状态选择, 所以图 3 中的 MUX 有  $2^{(mn+1)}$  种漏 电状态[5]。

除 MUX 外,选择器的另一重要组成是 BUF。它由多级缓冲器<sup>[5,15]</sup>或在此基础上的改进结构组成<sup>[7]</sup>,缓冲器的输入状态决定了每级反相器中NMOS 和 PMOS 晶体管的导通或截止,每种晶体管在不同开关状态下存在特定的漏电机制,并且两种晶体管的载流子属性不同,以上这些因素皆导致缓冲器的漏电流与其输入状态密切相关<sup>[5]</sup>,缓冲器的输入即选择器中 Vx 节点的状态。

图3 FPGA中使用的MUX结构

## 3 基于通道结构的漏电流优化算法

通过 SPICE 仿真,可以得到 SWB 的漏电流与输入、输出状态关系的查找表。根据漏电流查找表易于使一个 SWB 处于最小漏电状态,但是由于 SWB 对信号的传递性,难于确定整个 FPGA 中开关矩阵的最小漏电状态。在本节中,从通道结构的角度考虑,根据漏电流查找表,在一个小规模的 SWB矩阵单元中实现 FPGA 全部 SWB 的漏电流优化。

#### 3.1 优化漏电流查找表规模

在基于通道结构的漏电流优化算法中,首先优化查找表的规模,以减少查找漏电流的时间和空间复杂度。对于文中的 MUX,当输出状态确定后,随着输入向量中 1 的个数增加,低阈值漏电的路径增多,平均漏电流变大。查找表中的漏电流可以简化为仅与输入向量中 1 的个数有关,漏电状态由 $2^{(mn+1)}$  降低到 $2\times(mn+1)$ ,故查找表的规模由 $2^{(mn+1)}$  优化为 $2\times(mn+1)$ 。

#### 3.2 矩阵单元可变颗粒度的线性扩展

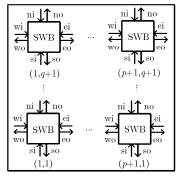

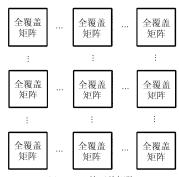

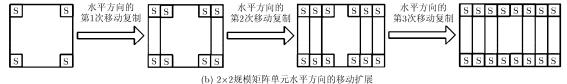

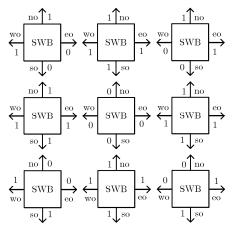

本文的漏电流优化算法研究基于相同长度通道可实现跳转的单驱动模式的开关矩阵,该算法适用于跳转位置处于终点和跳转位置等间距分布在通道上的情况。对于通道长度为 L 的开关矩阵,首先根据通道在水平和垂直方向上的跳转位置的数目 p , q , 定义由  $(p+1) \cdot (q+1)$  个 SWB 组成的矩阵单元,矩阵单元结构如图 4(a) 所示,n , s , e , w 分别代表矩阵中每个 SWB 4 个方向的信号,i 表示输入,o 表示输出。FPGA 的开关矩阵可通过对矩阵单元的线性扩展得到。

首先将矩阵单元扩展为全覆盖矩阵。当 L>p 或

q时,通道在一些位置上不会进行跳转选择。此时,得到全覆盖矩阵的过程为:将矩阵单元进行移动复制,每次移动一个 SWB 位置,直至将这些不进行跳转选择位置处的 SWB 全部覆盖。其中,水平方向移动的次数由式(1)得到,垂直方向移动的次数由式(2)得到,全覆盖矩阵的规模用式(3)求得。

$$R_m = (L - p) / p \tag{1}$$

$$C_m = (L - q) / q \tag{2}$$

$$M = (L/p + L) \cdot (L/q + L) \tag{3}$$

若 L=p=q,矩阵单元也即全覆盖矩阵。图 4(b) 给出 p=1, q=1, L=4 时, $2\times 2$  规模矩阵单元水平方向的移动扩展过程,垂直方向以此类推,当水平和垂直方向各 3 次移动后,即可得到  $8\times 8$  规模的全覆盖矩阵。在图 4(c)中,将全覆盖矩阵进行复制扩展即可得到 FPGA 的开关矩阵。由上述分析可知,FPGA 的开关矩阵可通过对矩阵单元的线性扩展得到,故求解 FPGA 开关矩阵的最小漏电流等价于求解矩阵单元的最小漏电流,以下介绍如何求解矩阵单元的最小漏电流。

#### 3.3 输入信号选择算法

矩阵单元的漏电流和其中每个 SWB 在不同跳转位置的输入、输出状态相关,有些输入状态决定于相邻矩阵单元的 SWB 输出。因为所有矩阵单元的最小漏电状态相同,这些输入状态可根据本矩阵单元的输出等效得到,无需依赖相邻矩阵单元中SWB 的输出,输入信号选择算法具体实现的伪代码如表 1 所示。

#### 3.4 矩阵单元的漏电流优化

当完成SWB选择器的设计后,可以通过SPICE 仿真得到所有可能的输入、输出状态与漏电流关系 的查找表。首先优化漏电流查找表的规模,然后根 据跳转位置数目得到矩阵单元。对于矩阵单元中 SWB的每一种输出状态组合,根据 3.3 节提出的基 于输出的输入选择算法,可以确定单元中所有 SWB 的输入状态,根据输入、输出状态通过查找表求出 漏电流。当穷尽所有输出状态的组合时,即可得到 矩阵单元的最小漏电流和对应的输出设置。

### 4 实验及结果分析

因商用 FPGA 中相同长度的通道在水平和垂直方向的跳转位置一般相同,实验选择两种具有代表性的矩阵单元:分别是在短通道终点跳转的规模为2×2 的矩阵单元和在长通道中点和终点位置跳转的规模为3×3 的矩阵单元。选取商用 FPGA 中常用规模为24选1和16选1的选择器分别对2×2和3×3规模的矩阵单元进行实验。其中,24选1选择

(c) FPGA的开关矩阵

S 代表矩阵中跳转位置处的SWB

图4 矩阵单元的定义和扩展过程

#### 表 1 输入信号选择算法实现的伪代码

- (1)for(矩阵单元中坐标(x,y)位置 SWB 的 ei 信号){

- (2) for(跳转位置 h){

- (3) if  $(x + h \le p + 1)$

- (4) 跳转位置 h 的 ei 等于坐标 (x + h, y) 位置 SWB 的 wo

- (5) else

- (6) 跳转位置 h 的 ei 等于坐标 (x + h p 1, y) 位置 SWB 的 wo}}

- (7)for(矩阵单元中坐标(x,y)位置 SWB 的 wi 信号){

- (8) for(跳转位置 h){

- (9) if (x h > 0)

- (10) 跳转位置 h 的 wi 等于坐标 (x h, y) 位置 SWB 的 eo

- (11) else

- (12) 跳转位置 h 的 wi 等于坐标 (p+1+x-h, y) 位置 SWB 的 eo}}

- (13)for(矩阵单元中坐标(x,y)位置 SWB 的 ni 信号){

- (14) for(跳转位置 h){

- (15) if  $(y + h \le q + 1)$

- (16) 跳转位置 h 的 ni 等于坐标 (x, y + h) 位置 SWB 的 so

- (17) else

- (18) 跳转位置 h 的 ni 等于坐标 (x, y + h q 1) 位置 SWB 的 so}}

- (19)for(矩阵单元中坐标(x,y)位置 SWB 的 si 信号){

- (20) for(跳转位置 h){

- (21) if (y h > 0)

- (22) 跳转位置 h 的 si 等于坐标 (x, y h) 位置 SWB 的 no

- (23) else

- (24) 跳转位置 h 的 si 等于坐标 (x, q + 1 + y h) 位置 SWB 的 no}}

器的 MUX 由 4 个 6 选 1 译码电路构成,16 选 1 的 MUX 采用 4 个 4 选 1 译码器实现。两种 MUX 电路 的 NMOS 晶体管为最小尺寸,缓冲器采用 FPGA 中常用的 2 级或 3 级反相器结构<sup>[5,15]</sup>,缓冲器中晶体管尺寸设置为可以达到相等的上升、下降时间,其中第 1 级是最小尺寸的反相器,第 2 级反相器尺寸是第 1 级的 4 倍,第 3 级反相器尺寸是第 2 级的 4 倍。24 选 1 和 16 选 1 MUX 的漏电流查找表如表 2 和表 3 所示,缓冲器漏电流的 SPICE 仿真结果如表 4 所示。漏电流仿真基于 0.13 µm 的 CMOS 工艺。

2×2规模的矩阵单元跳转规则为:在通道终点, SWB 选取任意 3 个方向各 8 路信号作为输入,另一方向为输出。表 2 是该矩阵单元的漏电极值和对应输出状态,根据 3.3 节提出的基于输出的输入选择算法,即可得到 SWB 的输入值。由表 5 可知,对于 2 级缓冲器,若要获得最小漏电流,图 2 中的 Vx 节点必须下拉至 0 电平,此时需要一个最小尺寸的 NMOS 管。若用晶体管宽度来估算面积<sup>[7]</sup>,选择器的面积增加约 2.33%,但漏电流减小了 81.11%,而传统的选择器设计是通过电平恢复器上拉 Vx 至 1 电平,此时对应最大漏电状态;而对于 3 级缓冲器,最小漏电状态仅需电平恢复器即可完成设置。

3×3 规模的矩阵单元跳转规则为:在第1个跳转位置,SWB每个输入方向有4路信号向与其传输方向垂直的两个方向跳转;在第2个跳转位置,输入信号可以向传输方向跳转4路信号。表6是该矩阵单元的漏电极值和对应输出状态。对于2级缓冲器,若要获得最小漏电流,仍需一个最小尺寸的

#### 表 2 24 选 1 的 MUX 漏电流查找表

| 输入端 1 | 输出 | 漏电流值  | 输入端1 | 输出 | 漏电流值  |

|-------|----|-------|------|----|-------|

| 的个数   | 状态 | (pA)  | 的个数  | 状态 | (pA)  |

| 0     | 0  | 0     | 0    | 1  | 17.43 |

| 1     | 0  | 4.36  | 1    | 1  | 19.84 |

| 2     | 0  | 8.92  | 2    | 1  | 22.22 |

| 3     | 0  | 11.99 | 3    | 1  | 24.58 |

| 4     | 0  | 15.19 | 4    | 1  | 26.96 |

| 5     | 0  | 18.29 | 5    | 1  | 29.32 |

| 6     | 0  | 21.28 | 6    | 1  | 31.69 |

| 7     | 0  | 23.90 | 7    | 1  | 34.05 |

| 8     | 0  | 26.51 | 8    | 1  | 36.41 |

| 9     | 0  | 29.13 | 9    | 1  | 38.77 |

| 10    | 0  | 31.59 | 10   | 1  | 40.10 |

| 11    | 0  | 34.03 | 11   | 1  | 43.41 |

| 12    | 0  | 36.39 | 12   | 1  | 45.66 |

| 13    | 0  | 38.74 | 13   | 1  | 47.91 |

| 14    | 0  | 41.08 | 14   | 1  | 50.09 |

| 15    | 0  | 43.38 | 15   | 1  | 52.13 |

| 16    | 0  | 45.66 | 16   | 1  | 54.14 |

| 17    | 0  | 47.92 | 17   | 1  | 56.10 |

| 18    | 0  | 50.16 | 18   | 1  | 57.97 |

| 19    | 0  | 52.31 | 19   | 1  | 59.71 |

| 20    | 0  | 54.41 | 20   | 1  | 61.33 |

| 21    | 0  | 56.48 | 21   | 1  | 62.92 |

| 22    | 0  | 58.41 | 22   | 1  | 64.29 |

| 23    | 0  | 60.29 | 23   | 1  | 65.59 |

| 24    | 0  | 62.08 | 24   | 1  | 66.75 |

#### 表 3 16 选 1 的 MUX 漏电流查找表

| 输入端 1 | 输出 | 漏电流值  | 输入端 1 | 输出 | 漏电流值  |

|-------|----|-------|-------|----|-------|

| 的个数   | 状态 | (pA)  | 的个数   | 状态 | (pA)  |

| 0     | 0  | 0     | 0     | 1  | 15.40 |

| 1     | 0  | 3.85  | 1     | 1  | 17.68 |

| 2     | 0  | 7.39  | 2     | 1  | 19.98 |

| 3     | 0  | 10.72 | 3     | 1  | 22.32 |

| 4     | 0  | 13.72 | 4     | 1  | 24.64 |

| 5     | 0  | 16.74 | 5     | 1  | 26.98 |

| 6     | 0  | 19.38 | 6     | 1  | 29.36 |

| 7     | 0  | 21.91 | 7     | 1  | 31.52 |

| 8     | 0  | 24.52 | 8     | 1  | 33.75 |

| 9     | 0  | 26.89 | 9     | 1  | 35.82 |

| 10    | 0  | 29.30 | 10    | 1  | 37.90 |

| 11    | 0  | 31.60 | 11    | 1  | 39.80 |

| 12    | 0  | 33.87 | 12    | 1  | 41.63 |

| 13    | 0  | 36.12 | 13    | 1  | 43.39 |

| 14    | 0  | 38.30 | 14    | 1  | 44.93 |

| 15    | 0  | 40.44 | 15    | 1  | 46.38 |

| 16    | 0  | 42.49 | 16    | 1  | 47.67 |

表 4 缓冲器在不同输入状态下的漏电流(pA)

| 缓冲器    | 输入为0  | 输入为1  |

|--------|-------|-------|

| 2 级缓冲器 | 16.82 | 22.33 |

| 3 级缓冲器 | 30.22 | 45.06 |

NMOS 管。此时,选择器的面积增加约 2.86%。而 SWB 选择 3 级缓冲器时的最小漏电输出设置如图 5 所示。

图5 SWB采用3级缓冲器的Vx最小漏电输出设置

对于2×2和3×3规模的矩阵单元,当采用3级缓冲器时,本文方法与文献[3],文献[7]的最小漏电流比较结果如表7所示。与文献[3]的方法相比,本文方法进一步降低8.82%和1.23%的漏电流。因为本文方法与SWB电路级的漏电流优化技术不相冲突,在2×2规模矩阵单元的实验中,若将3级缓冲器改为文献[7]提出的输出驱动电路,本文方法比文献[7]进一步降低11.78%的漏电流。对于3×3规模的矩阵单元3级缓冲器的情况,本文方法的最小漏电流和文献[7]相同。

通过对FPGA中两种常用规模矩阵单元应用本文方法进行漏电流优化,对于不同输出驱动的SWB,均可得到矩阵单元的最小漏电状态。但有时需通过一个最小尺寸的NMOS管,将SWB选择器的中间节点下拉至0电平,增加了芯片面积。求得矩阵单元的最小漏电状态后,根据可变颗粒度的线性扩展规则,即可得到FPGA中开关矩阵的最小漏电流和相应输出设置。在FPGA设计初期,当完成SWB电路和通道结构设计后,即可应用本方法求解出FPGA开关矩阵的最小漏电流,对器件的静态功耗进行前期评估;在FPGA使用过程中,应用本方法设定SWB的输出状态降低未使用开关矩阵的漏电流。

#### 表 5 2×2 规模的矩阵单元漏电极值和对应输出状态

| SWB 采用<br>缓冲器种类 | 最小漏电流(pA) | 最小漏电流 Vx<br>对应输出 | 最大漏电流(pA) | 最大漏电流 Vx 对应输出 | 漏电流减小比例(%) |

|-----------------|-----------|------------------|-----------|---------------|------------|

| 2级缓冲器           | 269.12    | 全部为0             | 1425.28   | 全部为1          | 81.11      |

| 3级缓冲器           | 999.84    | 全部为1             | 1476.80   | 全部为0          | 32.30      |

#### 表 6 3×3 规模的矩阵单元漏电极值和对应输出状态

| SWB 采用<br>缓冲器种类 | 最小漏电流(pA) | 最小漏电流 Vx<br>对应输出 | 最大漏电流(pA) | 最大漏电流 Vx 对应输出 | 漏电流减小比例(%) |

|-----------------|-----------|------------------|-----------|---------------|------------|

| 2 级缓冲器          | 605.52    | 全部为0             | 2302.56   | 全部为1          | 73.70      |

| 3级缓冲器           | 2139.84   | 见图 5             | 2307.24   | 全部为0          | 7.26       |

#### 表 7 最小漏电流优化比较

| 矩阵单元<br>规模   | 文献[3]<br>(pA) | 本文漏电<br>流减小比<br>例(%) | 文献[7]<br>(pA) | 本文漏电<br>流减小比<br>例(%) |

|--------------|---------------|----------------------|---------------|----------------------|

| $2\times2$   | 1096.60       | 8.82                 | 1147.20       | 11.78                |

| $3 \times 3$ | 2166.48       | 1.23                 | 2139.84       | 0                    |

#### 5 结束语

本文提出一种基于通道结构降低 FPGA 中开关矩阵漏电流的方法。首先基于漏电流与电路输入、输出状态有关的结论,将 SWB 选择器的漏电属性转化为输入、输出状态与漏电关系的查找表。然后根据水平和垂直方向通道上的跳转位置数目得到最小可重复的矩阵单元,将 FPGA 中开关矩阵的漏电优化等效为在矩阵单元中求解最小漏电流。实验结果表明,本文方法可以求解得到开关矩阵最小漏电流和相应的 SWB 输出设置,有效地降低了漏电流,并且本文算法可以兼容电路级的漏电优化方法。

#### 参考文献

- Nakha A, Palicot J, Leray P, et al. Leakage power consumption in FPGAs: thermal analysis[C]. 2012 International Symposium on Wireless Communication Systems (ISWCS), Paris, 2012: 606-610.

- [2] Salami B and Zamani M S. A prediction model for estimating leakage power consumption of routing resources in FPGAs[C]. 2011 3rd Asia Symposium on Quality Electronic Design (ASQED), Kuala Lumpur, 2011: 140–145.

- [3] Srinivasan S, Gayasen A, Vijaykrishnan N, et al. Leakage control in FPGA routing fabric[C]. Proceedings of the Asia and South Pacific Design Automation Conference (ASP-DAC), Shanghai, 2005, 1: 661–664.

- [4] Bagheri A and Masoumi N. A comprehensive smart and stochastic methodology for optimum wire segmentation in nano scale FPGAs[C]. 2011 International Conference on Microelectronics (ICM), Hammamet, 2011: 1–6.

- [5] Anderson J H and Najm F N. Active leakage power optimization for FPGAs[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006, 25(3): 423–437.

- [6] Huang K T, Hu Y, Li X W, et al.. Off-path leakage power aware routing for SRAM-based FPGAs[C]. 2012 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, 2012: 87–92.

- [7] Anderson J H and Najm F N. Low-power programmable FPGA routing circuitry [J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2009, 17(8): 1048-1060.

- [8] 李威, 杨海钢, 黄娟. 基于单驱动和多驱动通道形式组合的 FPGA 互连结构研究[J]. 电子与信息学报, 2010, 32(8): 2023-2027.

- [9] Bagheri A and Masoumi N. A stochastic evaluation methodology for wire segmentation in FPGAs for optimum performance[C]. 2011 19th Iranian Conference on Electrical Engineering (ICEE), Tehran, 2011: 1–6.

- [10] Schafer C, Stojilovic M, and Saranovac L. Analysis of impact of FPGA routing architecture parameters on area and delay[C]. 2011 19th Telecommunications Forum (TELFOR), Belgrade, 2011: 924–927.

- [11] Betz V and Rose J. FPGA routing architecture: segmentation and Buffering to optimize speed and density[C]. Proceedings of the 7th International ACM/SIGDA Symposium on FPGA, Monterey, CA, 1999: 140–149.

- [12] Lemieux G, Lee E, Tom M, et al. Directional and singledriver wires in FPGA interconnect[C]. 2004 IEEE International Conference on Field-Programmable Technology, Australia, 2004: 41–48.

- [13] Kuon I and Rose J. Exploring area and delay tradeoffs in FPGAs with architecture and automated transistor design[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2011, 19(1): 71–84.

- [14] Nair P S, Koppa S, John E B, et al. Topology selection of FPGA look-up tables for low-leakage operation[C]. 2009 European Conference on Circuit Theory and Design, Antalya, 2009: 73–76.

- [15] Lemieux G and Lewis D. Circuit design of routing switches[C]. Proceedings of the 10th International ACM/SIGDA Symposium on FPGA, Monterey, CA, 2002: 19–28.

- 王 一: 女,1984年生,博士生,研究方向为可编程逻辑芯片低功耗设计、电源/地线网络设计.

- 杨海钢: 男,1960年生,研究员,博士生导师,研究方向为高速 可编程逻辑芯片设计技术、数模混合信号SOC设计技术.

- 余 乐: 男,1983年生,博士后,研究方向为3维可编程逻辑芯 片架构及关键技术.