## 嵌入式可编程存储器设计中的"选择性寄存"方法

蔡

刚 <sup>①②</sup>

杨海钢 <sup>①</sup>

①(中国科学院电子学研究所

北京

100190)

②(中国科学院研究生院

北京

100049)

摘 要:该文提出一种"选择性寄存"的方法用于解决同步双端口存储器 IP 同时对同一地址进行读写操作时造成 的读出数据丢失的问题。利用该方法,通过使用同步双端口存储器 IP 和标准单元来设计嵌入式可编程存储器,可 减小设计的复杂度、增强设计的可移植性,从而大大缩短嵌入式可编程存储器的开发周期。该文设计的嵌入式可编 程存储器采用 SMIC 0.18 μm 1P6M CMOS 工艺流片。测试结果表明,与相近工艺尺寸、相同存储容量的全定制 嵌入式可编程存储器相比,它们在功能上兼容,在性能上相当。

关键词:嵌入式可编程存储器;选择性寄存;存储器 IP;标准单元

中图分类号: TN402

文献标识码: A

文章编号: 1009-5896(2009)11-2762-05

# A "Selective Registering" Technique for Design of an Embedded Programmable Memory

Cai  $\operatorname{Gang}^{^{\scriptsize{\textcircled{\tiny{1}}}\textcircled{\tiny{2}}}}$ Yang Hai-gang<sup>①</sup>

$^{\odot}($  The Institute of Electronics, Chinese Academy of Sciences, Beijing 100190, China)

<sup>2</sup>(Graduate University of the Chinese Academy of Sciences, Beijing 100049, China)

Abstract: A "selective registering" method is proposed to solve the problem of data loss in readout caused by simultaneously accessing both the read and write ports at the same address of a synchronous dual-port memory IP. Using this method to design an embedded programmable memory with the synchronous dual-port memory IP gives rise to reducing the implementing complexity and further improving the design's migration capabilities. Thus the research and development time can be shortened dramatically. According to the measurement results, such an embedded programmable memory fabricated in SMIC  $0.18~\mu m$  1P6M CMOS process has achieved some comparable performance for the compatible functions with the reference to those full custom embedded programmable memories based on the close processes.

Key words: Embedded programmable memory; Selective registering; Memory IP; Standard cell

### 引言

随着超大规模集成电路和系统芯片的发展,嵌 入式存储器已经广泛应用于各种设计之中[1]。然而, 随着市场趋势和应用需求的改变,存储器系统设计 者的主要目标也在发生着改变。不仅仅是性能,存 储器配置的灵活性、低功耗等设计目标也变得同等 重要[2-5]。在系统芯片,尤其是现场可编程门阵列 (FPGA)中,存储器配置的灵活性显得格外重要,因 为它直接影响到 FPGA 的应用范围和资源利用率。 当前,存储器配置灵活性的研究主要集中在 FPGA 中的嵌入式可编程存储器方面[3,4,6-9]。这些研究使得 商用 FPGA 中的嵌入式可编程存储器的灵活性得到 了很大的提高[10,11]。然而,从嵌入式可编程存储器 设计的角度来看,它们往往采用全定制的方法进行

设计,设计的复杂度高,开发周期长且设计不能在 不同的工艺上进行移植。为了在兼顾性能和灵活性 的基础上提高设计的可移植性、减小设计的复杂度, 本文提出了一种基于存储器 IP 和标准单元的嵌入 式可编程存储器的实现方案。

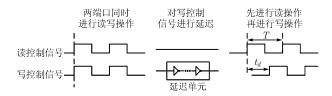

对于双端口存储器,当两端口同时对同一地址 进行读写操作时会存在读写冲突, 存储器中原有的 数据会被覆盖掉,从而造成读出数据的丢失。传统 的解决方法如图 1 所示,它通过延迟单元来延迟写 控制信号, 使读操作完成后再进行写操作, 通过实 现先读后写来避免读出数据的丢失。该方法的关键 是必须保证在 ta 时间内完成读操作, 因此延迟单元 的延时ta要足够大以保证在各个工艺角都满足要 求。存储器时钟的最小周期 T直接受限于 $t_a$ ,而 $t_a$ 会 大于存储器实际的读出时间,这样就会带来存储器 性能方面的损失。另外,不同工艺下延迟单元的延

图 1 通过延迟写控制信号来实现先读后写功能

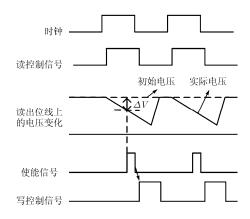

图 2 通过监测读出信号的变化来实现先读后写功能

时情况也不一样,每次设计都要重新考虑延迟单元 的延时是否满足要求,从而带来大量的额外工作。 文献[9]通过监测灵敏放大器读出位线上电压的变化 产生写控制信号来实现先读后写功能。如图 2 所示, 当读出位线上的电压变化幅度达到一定的数值  $\Delta V$ 时,就会产生一个使能信号,该使能信号再去控制 产生写控制信号,从而实现先读后写的功能。该方 法克服了传统方法的缺点,但不适用于使用存储器 IP 的情形,利用该方法进行的设计也不易于在不同 工艺上进行快速移植。为了克服这些困难,本文提 出了一种"选择性寄存"方法。该方法通过寄存有 读写冲突的写操作解决了同步双端口存储器 IP 同 时对同一地址进行读写操作时造成的读出数据丢失 的问题。利用该方法,通过使用同步双端口存储器 IP 和标准单元来设计嵌入式可编程存储器,可大大 减小设计的复杂度、缩短开发的周期。另外、由于

整个设计全部采用存储器 IP 和标准单元,可采用 ASIC 的设计流程。因此只要嵌入式可编程存储器的 基本结构确定,当采用不同的工艺进行设计时,设计的代码基本不需要改变或者改变很少,从而实现设计的快速移植。

### 2 基于"选择性寄存"方法的嵌入式可编程 存储器

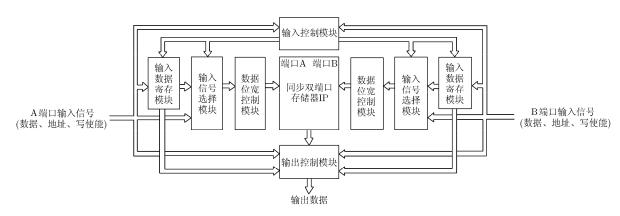

本文提出的基于"选择性寄存"方法的嵌入式 可编程存储器的基本结构如图 3 所示,通过使用同 步双端口存储器 IP 和标准单元来实现可进行多种 工作模式配置的嵌入式可编程存储器。由于同步双 端口存储器 IP 的两个端口同时对同一地址进行读 写操作时会引起读写冲突,写入的数据会覆盖掉存 储器中的原有数据,从而造成读出数据的丢失。为 了避免读出数据的丢失,本文提出了"选择性寄存" 的方法。该方法的基本思想是通过寄存有读写冲突 的写操作来避免同步双端口存储器 IP 出现读写冲 突以保证读出正确的数据。由于写操作被寄存到寄 存器中,从整体上看,整个嵌入式可编程存储器在 一个周期内完成了同一地址的读和写,并避免了读 出数据的丢失。图 3 中的数据位宽控制模块用于实 现不同数据位宽的配置,从而增强嵌入式存储器在 位宽配置方面的灵活性。其它模块用于实现"选择 性寄存"以防止读出数据的丢失。

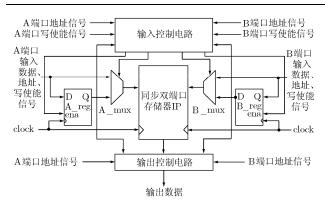

"选择性寄存"方法的实现结构如图 4 所示。 其基本结构主要由 5 部分组成,同步双端口存储器 IP,两组寄存器,两组选择器,输入控制电路以及 输出控制电路。寄存器通过输入控制电路给出的使 能信号选择性地寄存输入端的信号。选择器通过输 入控制电路给出的选择控制信号来决定将端口信号 或寄存器中的信号送给同步双端口存储器 IP。输入 控制电路根据输入信号的寄存和选择策略来产生 A,B端口寄存器的使能信号和选择器的控制信号。 输出控制电路根据输出数据控制策略来决定是输出

图 3 嵌入式可编程存储器的基本结构

图 4 "选择性寄存"方法的实现结构

寄存器中的数据还是输出同步双端口存储器 IP 的输出数据。A 端口进行读操作时的输出数据选择策略如表 1 所示。A 端口输入信号的寄存和选择策略如表 2 所示。依次类推,可得到 B 端口的输出数据选择策略及输入信号的寄存和选择策略。

由于写入的数据有可能寄存在寄存器中而并没有写入同步双端口存储器 IP,因此需要读出的数据有可能存在于 A\_reg 或 B\_reg 中,也有可能是同步双端口存储器 IP 的输出数据。要保证读出数据的正确性,输出控制电路必须按照一定的策略来输出读出数据。以 A 端口进行读操作为例,输出数据选择策略优先判断另一端口寄存器 B\_reg 中是否寄存有需要输出的数据。如果有,则输出该数据。如果没有,则判断本端口寄存器 A\_reg 中是否寄存有需要输出的数据。如果有,则输出该数据。如果没有,则输出同步双端口存储器 IP 的输出数据。如果没有,则输出同步双端口存储器 IP 的输出数据。输出数据选择策略成立的条件是 A\_reg 和 B\_reg 中寄存的必须是最新写入的数据,否则会造成读出的错误。

输入信号寄存策略采取的是一种选择性的寄存方法,它主要实现两大功能:寄存有读写冲突的写操作和更新寄存器中的写操作。当 A,B 端口存在读写冲突时,必须将写操作进行寄存以保证同步双端口存储器 IP 的两个端口不存在读写冲突,从而确保能读出 IP 中的原有数据,此时应按照表 2 的情形 1 进行处理。寄存器中写操作的更新发生在 3 种情况下:本端口在寄存地址处进行新的写操作,此时应按表 2 情形 2 中的(1)进行处理;另一端口在寄存地址处进行新的写操作,此时应按表 2 情形 4 中的(1)进行处理;寄存的数据已被写入存储器 IP,此时应按表 2 情形 3 中的(1)进行处理。寄存器中写操作的更新主要是为了满足输出数据选择策略成立的条件以保证读出数据的正确性。输入信号选择策略的原则是在保证同步双端口存储器 IP 不出现读写冲

表1A端口进行读操作时的输出数据选择策略

|       | 判断条件                                                                          | 输出结果                 |

|-------|-------------------------------------------------------------------------------|----------------------|

|       | A 端口与 B_reg 中地址相同<br>and B_reg 为写操作                                           | B_reg 中的数据           |

| A 端口读 | (A端口与B_reg 中地址不同<br>or B_reg 为读操作) and<br>(A端口与A_reg 中地址相同<br>and A_reg 为写操作) | A_reg 中的数据           |

|       | 其它情况                                                                          | 同步双端口存储器<br>IP 的输出数据 |

表 2 A 端口输入信号的寄存策略和选择策略

|       | A, B 端口地址相同              | A,B 端口地址不同                                                   |  |

|-------|--------------------------|--------------------------------------------------------------|--|

|       | 情形 1                     | 情形 2                                                         |  |

| A 端口写 | A reg 寄存                 | (1)A 端口与 A_reg 中地<br>址相同且 A_reg 为写操<br>作时<br>A reg 寄存 A 端口信号 |  |

|       | A 端口信号<br>A_mux 选择       | A_mux 选择 A_reg 中原<br>有信号                                     |  |

|       | A_reg 中原有信号              | (2)其它情况时                                                     |  |

|       |                          | A_reg 保持原有信号                                                 |  |

|       |                          | A_mux 选择 A 端口中信                                              |  |

|       |                          | 号                                                            |  |

|       | 情形 3                     | 情形 4                                                         |  |

|       | (1)A 端口与 A_reg 中         | (1)B 端口与 A_reg 中地                                            |  |

|       | 地址相同且 A_reg 为            | 址相同且都为写操作时                                                   |  |

| A 端口读 | 写操作时                     | A_reg 寄存 A 端口信号                                              |  |

|       | A_reg 寄存 A 端口信<br>号      | A_mux 选择 A 端口信号                                              |  |

|       | A_mux 选择 A_reg 中<br>原有信号 |                                                              |  |

|       | (2)其它情况时                 | (2)其它情况时                                                     |  |

|       | A_reg 保持原有信号             | A_reg 保持原有信号                                                 |  |

|       | A_mux 选择 A 端口信<br>号      | A_mux 选择 A 端口信号                                              |  |

突的情况下优先将寄存器中的写操作送到同步双端口存储器 IP,其具体的内容如表 2 所示。

"选择性寄存"方法处理过的同步双端口存储器 IP,具有了同时读写同一地址时能读出存储器中原有数据的功能,从而保证没有读出数据的丢失。

"选择性寄存"方法并不处理两端口同时对同一地 址进行写操作时造成的冲突问题。当出现这种情况, 写入该地址的数据是一个未知值。

### 3 芯片原型及测试结果

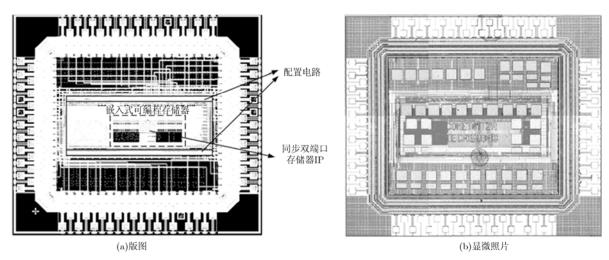

为了验证本文提出的"选择性寄存"方法的有效性,采用这种方法实现的嵌入式可编程存储器在 SMIC 0.18 μm 1P6M CMOS 工艺线上流片。芯片 的版图及显微照片如图 5 所示,中间黑色实线方框包围的部分为嵌入式可编程存储器,虚线框包围的部分为同步双端口存储器 IP,上下两个黑色方框包围的部分为配置电路。配置电路的作用是将嵌入式可编程存储器配置成不同的工作模式。同步双端口存储器 IP 使用的是 VeriSilicon 0.18 μm SMIC G process dual-port SRAM。整个芯片的存储容量为4608 bit,最高工作频率为 213 MHz。由于需要引出足够的信号以对嵌入式可编程存储器的功能和性能进行测试,因此引出的管脚比较多。该设计属于一种 PAD Limited 的设计,嵌入式可编程存储器只占整个芯片面积的 34.8%。

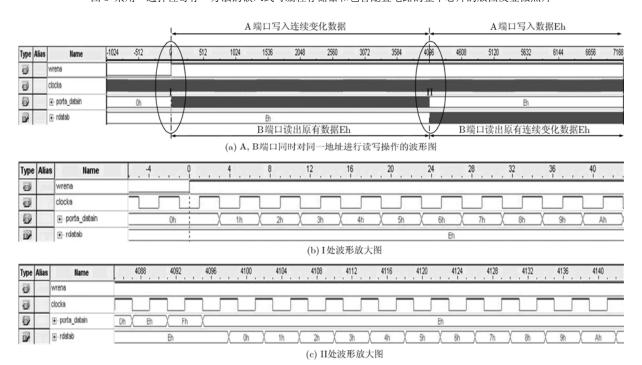

为了验证"选择性寄存"方法的有效性,对嵌入式可编程存储器两端口同时对同一地址进行读写

操作的工作模式进行了功能测试,测试得到的波形如图 6 所示。此时 A 端口进行写操作,B 端口进行读操作,A,B 两端口的地址始终相同且连续循环变化,地址在图中的 0 处开始第 1 次循环,在 4096处开始第 2 次循环。从图中可以看出 B 端口读出的数据始终是 A 端口在上次地址循环时写入的数据,从而说明"选择性寄存"方法实现了同时对同一地址进行读写操作时读出存储器中原有数据的功能。

从工艺尺寸和存储容量的角度来看,在所有的商用嵌入式可编程存储器当中,文献[10]中的嵌入式可编程存储器与本文设计的嵌入式可编程存储器的情形最为接近。因此,我们将两者进行了比较。表3给出了文献[10]、本文使用的同步双端口存储器 IP

图 5 采用"选择性寄存"方法的嵌入式可编程存储器和包含配置电路的整个芯片的版图及显微照片

图 6 两端口对同一地址同时进行读写操作时的波形图

表 3 配置灵活性方面的对比

|                           | 文献[10] | 本文使用的同步<br>双端口存储器 IP | 本文的嵌入式<br>可编程存储器 |

|---------------------------|--------|----------------------|------------------|

| 端口模式                      | 3      | 1                    | 3                |

| 数据宽度模式                    | 9      | 1                    | 9                |

| 简单双端口混<br>合宽度模式           | 45     | 0                    | 45               |

| 真双端口混合<br>宽度模式            | 29     | 1                    | 29               |

| 奇偶校验位                     | 1      | 0                    | 1                |

| 字节使能模式                    | 16     | 0                    | 16               |

| 时钟模式                      | 4      | 1                    | 4                |

| 对同一地址同<br>时进行读写时<br>的读出模式 | 2      | 1                    | 2                |

以及本文设计的嵌入式可编程存储器在配置灵活性方面的对比结果。表中的数值为三者在各个功能下可配置模式的数量,数值越大,说明配置的灵活性越强。从表中的对比结果可以看出,本文使用的同步双端口存储器 IP 的工作模式单一,配置的灵活性差。但经过设计得到的嵌入式可编程存储器达到了与文献[10]相同的配置灵活性。由于读出时间是存储器性能的瓶颈,因此读出时间直接决定了存储器的性能。本文与文献[10]在性能方面的对比结果如表4所示。文献[10]给出了-6,-7和-8三种速度等级下的FPGA芯片中的嵌入式可编程存储器的读出时间。从读出时间这个角度来说,本文设计的嵌入式可编程存储器的性能和文献[10]的性能相当。

表 4 与相近工艺尺寸及相同存储容量的 商用嵌入式可编程存储器性能的对比

|           | 文献[10]                   |       |                                    | 本文        |

|-----------|--------------------------|-------|------------------------------------|-----------|

|           | -6                       | -7    | -8                                 | 4.        |

| 工艺尺寸      | 0.13 μm all-layer copper |       | $0.18~\mu\mathrm{m}~\mathrm{SMIC}$ |           |

| 工乙/(1     | SRAM process             |       |                                    | G process |

| 存储容量(bit) | 4608                     |       | 4608                               |           |

| 读出时间(ns)  | 4.351                    | 5.003 | 5.656                              | 4.688     |

测试结果表明,本文设计的嵌入式可编程存储器在功能上与文献[10]中的商用嵌入式可编程存储器兼容,在性能上与其相当。如果考虑工艺因素造成的影响,假如采用和文献[10]一样的工艺,本文设计的嵌入式可编程存储器的性能还会进一步提高。

### 4 结论

本文提出了一种"选择性寄存"方法用于解决 同步双端口存储器 IP 同时对同一地址进行读写操 作时造成的读出数据丢失的问题。根据测试结果可知,利用该方法设计的嵌入式可编程存储器与相近工艺尺寸、相同存储容量的采用全定制方法设计的商用嵌入式可编程存储器相比,在功能上兼容,在性能上相当。本文利用同步双端口存储器 IP 和基本单元来实现嵌入式可编程存储器,减小了设计的复杂性、增强了设计的可移植性,可大大缩短嵌入式可编程存储器的开发周期。

### 参考文献

- [1] Sharma A K 著, 曾莹, 伍冬, 孙磊等译. 先进半导体存储器——结构、设计与应用[M]. 北京: 电子工业出版社, 2005: 355-356.

- [2] Chheda S, Chittamuru J K, and Moritz C A. Memory systems: overview and trends. http://www-unix.ecs.umass. edu/~ jchittam /memorysys.pdf, 2008, 10.

- [3] Ngai T, Rose J, and Wilton S J E. An SRAM-programmable field-configurable memory[C]. IEEE Custom Integrated Circuits Conference, May 1995: 499–502.

- [4] Wilton S J E, Rose J, and Vranesic Z G, et al.. Architecture of centralized field-configurable memory[C]. Proceedings of the Third International ACM Symposium, 1995: 97–103.

- [5] Chin S Y L, Lee C S P, and Wilton S J E. On the power dissipation of embedded memory blocks used to implement logic in field-programmable gate arrays[J]. *International Journal of Reconfigurable Computing*, 2008, Article ID 751863, 13 pages.

- [6] Yu H M and Jose S, et al.. Divisible true dual port memory system supporting simple dual port memory subsystems[P]. US 7,269,089 B1, Sep. 11, 2007.

- [7] Lytle C S and View M, et al. Programmable logic array integrated circuit with general-purpose memory configurable as a random access or FIFO memory[P]. US 6,340,897 B1, Jan. 22, 2002.

- [8] Leblance M A. Memory implementations of shift registers[P]. US 7,093,084 B1, Aug. 15, 2006.

- [9] Yu H M and Jose S. Dual port PLD embedded memory block to support read-before-write in one clock cycle[P]. US 7,206,251 B1, Apr.17, 2007.

- [10] Altera Corporation. Cyclone Device Handbook, Vol. 1. January 2007: 99–189.

- [11] Xilinx Corporation. Virtex-5 FPGA User Guide. May 2008: 111–170.

- 蔡 刚: 男,1980年生,博士生,从事嵌入式可编程存储器设计方面的研究工作.

- 杨海钢: 男,1960 年生,研究员,博士生导师,中国科学院"百人计划"引进国外杰出人才,主要从事数模混合信号 SoC设计和大规模集成电路设计等方面的研究工作.