# 适用于准循环 LDPC 码译码器的新型循环移位置换结构设计

苑津莎 陈智雄

(华北电力大学电气与电子工程学院 保定 071003)

摘 要:循环移位置换单元是准循环 LDPC 码的部分并行译码器的重要组成部分。该文研究并证明了 Reverse Banyan 交换结构在实现信息循环移位时各个基本交换单元的连接规律。基于该规律设计了基于可预置选路算法的 无阻塞循环移位置换结构。相比 Benes 交换结构和 Reverse Banyan 交换结构,提高了信息循环移位交换的速率,且占用较少的硬件资源和面积。最后设计了一个出线转换单元,该单元适用于各种循环移位交换结构。

关键词:准循环 LDPC 码;置换结构; Banyan 网络;循环移位

中图分类号: TN911.22

文献标识码: A

文章编号: 1009-5896(2009)09-2148-04

# Design of Novel Cyclic Shift Permutation Structure for Quasi-Cyclic LDPC Codes Decoder

Yuan Jin-sha Chen Zhi-xiong

(School of Electrical & Electronic Engineering, North China Electric Power University, Baoding 071003, China)

Abstract: Cyclic shift permutation structure is an important part of partial parallel decoder for quasi-cyclic LDPC codes. When the information is exchanged, a connecting law of basic switch units in Reverse Banyan network is researched and proved. Then a nonblocking permutation structure based on presetting routing algorithm for cyclic shift is designed. Compared with Benes exchange structure and Reverse Banyan exchange structure, the novel structure increases the exchange speed for information cyclic shift and occupies less hardware resource and area. Finally, an output converting unit is designed, which is adaptable for all kinds of switch structures.

Key words: Quasi-cyclic LDPC codes; Permutation structure; Banyan network; Cyclic shift

### 1 引言

准循环 LDPC 码<sup>II</sup>是结构化的 LDPC 码,具有较好译码性能,其结构化的校验矩阵便于实现 LDPC 码的有效编码和快速并行译码。准循环 LDPC 码已经被 WiFi (IEEE 802.11n)和 WiMax (IEEE 802.16e)等标准所采纳。目前准循环 LDPC 码译码器的研究是一个热点,人们期望在降低硬件实现复杂度的同时仍能保持较好的译码性能。

针对不同的应用环境,准循环 LDPC 码的译码器分为 3 种不同的硬件结构:全并行结构<sup>[2]</sup>、串行结构和部分并行结构<sup>[3-8]</sup>。部分并行结构是为每个非零子矩阵分配一个独立的存储区域,每块存储区串行的复用同一组节点计算单元和选路交换单元,从而实现部分并行的迭代译码。部分并行结构克服了全并行结构资源消耗过大、硬件实现难度大的缺点,同时译码速率比串行结构快,十分适合实际应用。

部分并行译码器使用循环移位置换网络 (permutation network)来实现信息分组在校验节点 运算单元分组和变量节点运算单元分组之间的循环 移位,简化了并行译码器内部的线路连接。信息交换结构的统一与复用,减少了译码器面积,也降低了硬件复杂度;而模块化的互连结构使得译码器便于扩展,更具灵活性。已有的准循环 LDPC 码的译码器主要采用 Barrel Shifter 交换结构<sup>[3]</sup>,Banyan交换结构<sup>[4]</sup>和 Benes 交换结构<sup>[5,6]</sup>等来实现信息的循环移位。

本文主要贡献在于:研究并证明了 Reverse Banyan 交换结构实现信息循环移位时,各个基本交换单元的内部连接规律;根据该规律设计了基于可预置选路算法的新型无阻塞循环移位交换结构,相比 Benes 和 Banyan 交换结构是更优的选择;设计了一个线转换结构,可普遍适用于 Benes 交换结构等各种交换结构。

## 2 部分并行译码器中的循环移位交换结构

部分并行译码器主要采用 TDMP(Turbo Decoding Message Passing)译码算法<sup>[9]</sup>(又称分层译码算法),其译码结构主要由节点计算单元、存储控制单元和交换单元等构成<sup>[8]</sup>。节点计算单元主要负责节点上信息的迭代计算;存储控制单元用于存储初始化信息、节点处理信息和控制信息;交换单元负

责信息在节点间的迭代交换。交换单元的交换速率 关系到译码器的译码速率,而交换单元消耗的硬件 资源也直接关系到译码器的实现复杂度。

$P \wedge P \sqcup ($ 以下简写为  $P \times P)$ 的循环移位交换结构的主要功能是对信息列向量进行循环移位后选路输出,Crossbar 交换结构,Clos 交换结构,Benes 交换结构和 Banyan 交换结构 $^{[10]}$ 都是可选择的交换形式。文献 $^{[5]}$ 列出 P=32 时,Crossbar,Clos 和 Benes 这 3 种交换结构的硬件资源消耗情况,无论是硬件复杂度还是占用面积,Benes 交换结构都是最佳的选择。

考虑  $P=2^t(t)$  为自然数)时的一般情况,实现相同的  $2^t \times 2^t$  交换功能,Banyan 交换结构仅需要  $2^{t-1}$  ×t 个  $2\times 2$  交换单元;Benes 交换结构需要  $(2^{t-1}\times (2t-1))$  个  $2\times 2$  交换单元,总的资源消耗和占用面积约为 Banyan 结构的两倍。但是 Benes 交换结构的优势在于:它是严格无阻塞的。一般情况下,Banyan 交换结构需要在前端增加排序结构(如Batcher 交换结构)来控制内部的阻塞。因此实际应用更多选择的是 Benes 交换结构。

对于 Benes 交换结构来说,根据给定的循化移位值来实时寻找信息的交换路由,硬件实现起来有一定的难度。一般都是针对特定的 LDPC 码,将提前计算好的路由控制信息比特存放在译码器的专门存储区域中,用于控制译码过程的信息选路交换[5,6],增加了硬件复杂度和占用面积。文献[8]中,准循环LDPC 码译码器采用自选路由的 96×96 交换网络,节点信息通过多级交换网络时,根据嵌入的路由信息来实现无阻塞交换。由于信息是分级交换的,如果交换网络的级数较多将直接影响信息交换的速率和译码器的译码速率。

# 3 基于可预置选路算法的无阻塞循环移位 交换结构

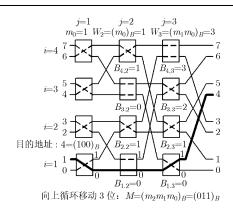

实现信息的循环移位,特殊形式的 Banyan 交换结构(又称 Reverse Banyan 网络或间接二进制 n 维立方体网络)是严格无阻塞的[11],因此相比 Benes 交换结构,Reverse Banyan 交换结构实际上是更好的选择。Reverse Banyan 交换结构采用递归式方法构造。 $2^t \times 2^t$  Reverse Banyan 交换结构的具体构造过程如下:将两个 $2^{t-1} \times 2^{t-1}$  Reverse Banyan 交换结构的逆均匀洗牌的出线方式都去掉后与 $2^{t-1}$ 个  $2\times 2$  交换单元采用蝶式互连,最后将总的  $2^t$ 条出线采用逆均匀洗牌方式选路输出。图 1 为  $2^3 \times 2^3$  Reverse Banyan 的交换结构图,它由两个  $4\times 4$  Reverse Banyan 交换结构和 4 个  $2\times 2$  交换单元构成。

图 1 M=3 时, $2^t \times 2^t$  Reverse Banyan 交换结构的内部连接规律

下面对 Reverse Banyan 交换结构的选路方式进行分析与设计。若没有特殊说明,文中均按从下到上的顺序进行编号。

#### 3.1 自选路由算法

$2^t \times 2^t$  Banyan 交换结构具有自选路由的特性<sup>[10]</sup>。若信息从第 x 条入线输入,当要求将信息向上循环移动 M 位时,信息的出线地址为[(x+M)模2<sup>¶</sup>,该地址的二进制形式共 t 位。信息经过第 j 列  $2\times 2$  交换单元时,交换单元可根据该目的地址由低位到高位的第 j 位上的数值来决定单元入线和出线的连接关系,以实现信息的选路交换。图 1 中的粗黑线表示:当 M=3 即将信息向上循环移动 3 位时, $2^3 \times 2^3$  Reverse Banyan 交换结构的入线 1 上的信息根据目的地址  $4=(100)_B$  进行自选路由的过程。硬件实现自选路由方法时共需  $2^{t-1} \times t$  个控制单元;信息选路置换的整个过程至少需 t 个时钟脉冲。

#### 3.2 可预置选路算法

$2^t \times 2^t$  Banyan 交换结构共包含  $2^{t-1} \times t$  个  $2 \times 2$  交换单元,它们被分为  $2^{t-1}$  行,t 列。研究发现,当 M 值从 0 到( $2^t$  -1)依次变化时,Reverse Banyan 结构中各列  $2 \times 2$  交换单元的内部连接状态(平行状态或交叉状态)具有一定的规律性(见引理)。因此可以根据 M 值来控制各个  $2 \times 2$  交换单元的内部连接状态,实现信息的循环移位选路。

引理 将第  $i(1 \le i \le 2^{t-1})$ 行、第  $j(1 \le j \le t)$ 列的  $2 \times 2$  交换单元编号为  $B_{i,j} = (i-1) \pmod{2^{j-1}}$ 。再用  $S_{i,j}$  表示该  $2 \times 2$  交换单元所对应的状态(控制信息比特): 当  $S_{i,j} = 0$  时为平行状态;当  $S_{i,j} = 1$  时为交叉状态。将  $M(M < 2^t)$ 表示成二进制  $(m_{t-1}, \cdots, m_1, m_0)_B$  的形式,则第  $j(1 \le j \le t)$ 列的每个  $2 \times 2$  交换单元按以下规律设置状态:

(1) 当 j=1 时, $S_{i,j}=m_0$ ;

$$(2) \stackrel{i.j}{=} 2 \stackrel{i.j}{\leqslant} t \, \text{时}, \, \stackrel{i.j}{\Leftrightarrow} \, W_j = \, (m_{j-2}, \cdots, m_1, m_0)_B \,,$$

$$S_{i,j} = \begin{cases} m_{j-1}, & W_j \leq B_{i,j} \\ 1 - m_{j-1}, & W_j > B_{i,j} \end{cases}$$

证明略。

信息循环移位时,Reverse Banyan 结构中各列 2×2 交换单元的内部连接状态的规律性,也就间接证明了 Reverse Banyan 结构实现信息循环移位时的严格无阻塞特性。

根据引理, $2\times 2$  交换单元的状态值  $S_{i,j}$  是列数 j,M 值和编号  $B_{i,j}$  的函数。第 1 列  $2\times 2$  交换单元的状态值仅取决于  $m_0$  值;第 j(j>1) 列的状态取决于  $m_{j-1}$  值和  $W_j$ 与  $B_{i,j}$  的比值关系。实时选路交换时,第 i行,第 j(j>1) 列  $2\times 2$  交换单元所对应的控制单元仅由一个(j-1) 位数值比较器和一个异或门构成即可。图 1 为当  $P=2^3$ ,M=3 时,各列  $2\times 2$  交换单元按引理设置的连接状态。

当同一列的  $2\times 2$  交换单元的编号值相等时,它们可共用一个控制单元(或控制信息比特)。第 j 列的编号  $B_{i,j}$  以  $2^{j-1}$  为周期,那么第 j 列只需  $2^{j-1}$  个选路控制单元(或控制信息比特), $2^t\times 2^t$  交换结构采用可预置选路算法时共需( $2^{t-1}$ ) 个控制单元(或控制信息比特),而自选路由算法需要( $2^{t-1}\times t$ ) 个控制单元(或控制信息比特)。例如当 P=64 即 t=6 时,可预置选路算法需要 63 个控制单元(或控制信息比特),比自选路由算法的 192 个要少得多。相比自选路由算法的 t 个时钟脉冲,可预置选路算法仅需 1 个时钟将 M 值送入各个控制单元进行逻辑运算来控制每个  $2\times 2$  交换单元的连接状态,从而使信息循环移位置换的速率得以提高。

#### 3.3 基于预置选路算法的改进循环移位置换单元

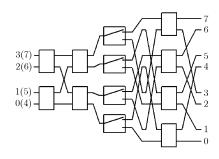

已知  $2^{t} \times 2^{t}$ 的 Reverse Banyan 交换单元由两个  $2^{t-1} \times 2^{t-1}$  的 Reverse Banyan 交换单元和  $2^{t-1}$  个  $2 \times 2$  交换单元构成。由引理,第 j 列  $2 \times 2$  交换单元的状态  $S_{i,j}$  的周期是  $2^{j-1}$  。因此 M 值一定,这两个  $2^{t-1} \times 2^{t-1}$  Reverse Banyan 交换单元对应位置上的  $2 \times 2$  交换单元的状态是一样的,可通过添加一个简单的两路复用器将它们合并,复用器由  $2^{t-1}$  个逻辑数字开关构成。合并后,可节省  $(2^{t-2} \times (t-1))$  个  $2 \times 2$  交换单元,也能减少交换单元硬件实现时的占用面积。

图 2 为 P=2³时,通过两路复用器合并后的循环移位置换结构。信息的循环移位分为两个时钟完成,在第 1 个时钟设置 2×2 交换单元的状态,同时控制复用器的开关与下路相连接,完成第 0 条入线至第 3 条入线上信息的循环移位;第 2 个时钟保持 2×2 交换单元的状态不变,控制复用器的开关与上路相连接,完成第 4 条入线至第 7 条入线上信息的循环移位。表 1 将新型的置换单元与 Benes,Reverse Banyan 结构进行了对比。

图 2 合并后的 23×23 循环移位置换结构

表 1 128×128(*t*=7)本文的置换单元与 Benes, Reverse Banyan 交换结构的对比情况

| 类型      | 2×2 交换 | 1×2 复用 | 实时选路  | 控制信息  |

|---------|--------|--------|-------|-------|

|         | 单元     | 单元     | 时钟    | 比特    |

| Benes 交 | 832 个  | 0 个    | 自选路由: | 832 个 |

| 换结构     |        |        | 13 个  |       |

| Reverse | 448 个  | 0 个    | 自选路由: | 127 个 |

| Banyan  |        |        | 7个    |       |

| 本文的置    | 256 个  | 64 个   | 预置选路: | 127 个 |

| 换结构     |        |        | 2 个   |       |

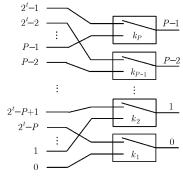

#### 3.4 出线转换单元设计

实际出线数 P不一定等于  $2^t$  (设 P满足:  $2^{t-1} < P$  < $2^t$ ),例如 802.16e 标准中 P=96,因此需要在  $2^t \times 2^t$  交换结构的出线处接一个出线转换单元。如图 3 所示,出线转换单元由 P 个逻辑开关组成,每个开关的上支路按从上到下的顺序依次与  $2^t \times 2^t$  交换单元的第( $2^{t-1}$ )至第( $2^{t-P}$ )条出线相连,每个开关的下支路按从下到上的顺序依次与交换单元的第 0 至第(P-1)条出线相连。由于  $2^{t-1} < P$ ,第  $i(2^{t-P} \leqslant i \leqslant P$ -1)条出线同时连接一个开关的上支路和另一个开关的下支路。

图 3 出线转换单元的结构

当要求将信息向上循环移 M 位时,控制开关  $K_1,K_2,\cdots,K_M$  与下支路相连,其它(P-M)个开关与上 支路相连,从而实现  $2^t \times 2^t$  交换到  $P \times P$  交换的转换。信息交换时,从  $2^t \times 2^t$  交换单元的第  $2^t$ -P+1 到第  $2^t$  条入线输入,经过循环移位后从出线转换单元输出。

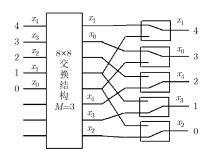

图 4 为当 P=5,M=3 时出线单元的连接方式和开关状态示意图,其中  $x_i$ 为第  $i(i=0,1,\cdots,4)$ 条入线上的信息。本文设计的出线转换单元不仅适用于 Reverse Banyan 交换结构,也适用于 Omega,Benes 等交换结构。

图 4 当 P=5,M=3 时出线转换单元的连接方式和开关状态

## 4 结束语

准循环LDPC码的译码器主要采用基于循环移位置换网络的部分并行译码结构。信息交换结构的统一与复用,减少了译码器面积,也降低了硬件复杂度;而模块化的互连结构使得译码器便于扩展,更具灵活性。置换单元的设计直接关系到译码器的译码速率和硬件复杂度。

本文主要研究并证明了Reverse Banyan交换结构实现信息循环移位时的内部连接规律,设计了基于可预置选路算法的无阻塞循环移位置换结构,设计了一个普遍适用的出线转换结构。相比Benes和Reverse Banyan交换结构,设计的新型循环移位置换结构提高了信息循环移位交换的速率,且占用较少的硬件资源和面积,具有重要的实际应用价值。

#### 参考文献

- Fossorier M P C. Quasi-cyclic low-density parity-check codes from circulant permutation matrices[J]. *IEEE Transactions on Information Theory*, 2004, 50(4): 1788-1793.

- [2] Darabiha A, Carusone A C, and Kschischang F R. Block-interlaced LDPC decoders with reduced interconnect complexity[J]. IEEE Transactions on Circuits System II: Express Briefs, 2008, 55(1): 74-78.

- [3] Yang S, Marjan K, and Joseph R C. VLSI decoder architecture for high throughput, variable block-size and multi-rate LDPC codes[C]. IEEE ISCAS 2007, New Orleans, USA, May 27–30, 2007: 2104–2107.

- [4] Mansour M M and Shanbhag N R. A 640-Mb/s 2048-bit programmable LDPC decoder chip[J]. IEEE Journal of Solid-State Circuits, 2006, 41(3): 634-698.

- [5] Masera G, Quaglio F, and Vacca F. Implementation of a flexible LDPC decoder[J]. IEEE Transactions on Circuits System II: Express Briefs, 2007, 54(6): 542-546.

- [6] Quaglio F, Vacca F, Castellano C, Tarable A, and Masera G. Interconnection framework for high-throughput, flexible LDPC decoders[C]. Proceedings Design Automation and Test in Europe, Munich, Germany, 2006, 2: 6-10.

- [7] Liu C H, Lin C C, Chang H C, Lee C Y, and Hsu Y S. An LDPC decoder chip based on self-routing network for IEEE 802.16e applications[J]. *IEEE Journal of Solid-State* Circuits, 2008, 43(3): 684–694.

- [8] Brack T, Alles M, and Lehnigk-Emden T, et al.. A survey on LDPC codes and decoders for OFDM-based UWB systems[C]. IEEE VTC-spring 2007, Dublin, Ireland, April 22–25, 2007: 1549–1553.

- [9] Mansour M M. A Turbo-decoding message-passing algorithm for sparse parity-check matrix codes[J]. IEEE Transactions on Signal Proceeding, 2006, 54(11): 4376-4392.

- [10] Goke L and Lipovski G. Banyan network for partitioning multiprocessor systems[C]. Proceedings of 1st annual symposium Computer architecture, New York, USA, 1973: 21–30.

- [11] Lee T H and Liu S J. Banyan network nonblocking with respect to cyclic shifts[J]. *Electronics Letters*, 1991, 27(16): 1474–1476.

苑津莎: 男,1957年生,教授,博士生导师,研究方向为信号与信息处理、电力系统通信.

陈智雄: 男,1983年生,博士生,研究方向为信道编码和协作通信.