# 一种高效的混合 Test-Per-Clock 测试方法

刘铁桥\* 牛小燕 杨 洁 毛 峰 (杭州电子科技大学 杭州 310018)

摘 要:该文提出了一种基于内建自测试(BIST)的 Test-Per-Clock 混合模式向量产生方法。测试由两个部分组成:自由线性反馈移位寄存器(LFSR)伪随机测试模式和受控 LFSR 确定型测试模式。伪随机测试模式用于快速地检测伪随机易测故障,减少确定型数据存储。受控 LFSR 测试模式采用直接存储在 ROM 中的控制位流对剩余故障产生确定型测试。通过对提出的 BIST 混合模式测试结构理论分析,提出了伪随机向量的选取方法以及基于受控线性移位确定型测试生成方法。基准电路的仿真结果表明,该方法可以获得完全单固定型故障覆盖率,其测试产生器设计简单且具有良好的稳定性,与其他方法相比,具有较低的测试开销和较短的测试应用时间。

关键词: IC 测试;内建自测试; Test-Per-Clock 测试;测试生成

中图分类号: TN407 文献标识码: A 文章编号: 1009-5896(2017)09-2266-06

**DOI**: 10.11999/JEIT161202

# An Efficient Mixed-mode Test-Per-Clock Scheme

LIU Tieqiao NIU Xiaoyan YANG Jie MAO Feng

(Hangzhou Dianzi University, Hangzhou 310018, China)

Abstract: A mixed-mode Test-Per-Clock Built In Self Test (BIST) scheme is proposed. The test consists of two parts: the free Linear Feedback Shift Register (LFSR) pseudo-random test mode and the deterministic test pattern based on controlled LFSR. Pseudo random test mode is used to quickly detect pseudo-random susceptible faults and reduce the deterministic data storage. Controlled LFSR test mode uses the control bits directly stored in the ROM to generate a deterministic test of the remaining faults. Based on the theoretical analysis of the proposed mixed-mode BIST test structure, a pseudo-random test sequence selection method and a deterministic test generation method based on controlled linear shifter are proposed. Simulation results on benchmark circuits show that the proposed method can obtain the complete single stuck-at fault coverage and has good stability in test generation. Compared with other methods, it has simpler Test Pattern Generator (TPG) design and lower test cost as well as shorter test application time.

Key words: IC test; Built In Self Test (BIST); Test-Per-Clock test; Test generation

#### 1 引言

随着超大规模集成电路的设计复杂性不断增加,芯片测试所需的引脚数越来越多,导致测试所需的自动测试设备(Automatic Test Equipment, ATE)变得越来越复杂和昂贵,所需的测试数据量越来越大,测试应用时间也越来越长。为了减轻这些测试问题,内建自测试(BIST)通过将测试向量生成和测试响应压缩设计在芯片内部,从而大大降低了测试代价,被工业和学术界广泛采用[1]。高效的BIST结构应具备的3个属性,包括高故障覆盖率,低硬

件开销,以及较短的测试应用时间。

许多 BIST 方法被提出来用于找到上述 BIST 3 个属性的最优化。其中 LFSR-ROM 方法以低存储、高效率获得广泛关注。在 LFSR-ROM 的测试方法中<sup>[2]</sup>,线性反馈移位寄存器(Linear Feedback Shift Register, LFSR)以伪随机向量生成的模式用于检测易测的故障,而 ROM 用于提供确定型测试生成,以保证故障覆盖率。文献[3]提出了一种新的混合BIST 技术,采用组合电路模块来产生确定型测试向量,从而不需要存储元件开销。加权伪随机测试<sup>[4]</sup>也是一种被广泛采用的用于同时减少测试应用时间和测试存储开销的方法,它通过设定的权值改变LFSR 输出引脚 0 和 1 的比率。然而,这些方法的主要缺点是它们只适合小规模电路测试,且附加的过多逻辑门加大了电路的延迟。随着电路规模的增

收稿日期: 2016-11-08; 改回日期: 2017-04-10; 网络出版: 2017-05-11 \*通信作者: 刘铁桥 tieqiao120@163.com

基金项目: 浙江省自然科学基金(LQ15F040005)

Foundation Item: Zhejiang Provincial Natural Science Foundation (LQ15F040005)

大,伪随机测试过长的测试应用时间和过大的额外逻辑块开销将无法被接受。另一种实现高故障覆盖而减少 ROM 存储的技术是 LFSR 重播种方法<sup>[5,6]</sup>。在 LFSR 重播种技术中,LFSR 种子被储存在 ROM,测试时,种子被连续装入 LFSR 作为不同的初始状态,通过 LFSR 解压缩以产生确定型测试向量序列。文献[7]使用了控制比特位来跳过无关的伪随机测试向量,文献[8]提出了一种扫描阻塞技术来控制伪随机扫描切片的装载。他们通过存储控制信号,而不是测试集实现了较高的测试数据压缩率。文献[9]从测试集出发构建 LFSR,从而有效减少了 LFSR 的级数并提高了编码成功率。

通过将电路中原始的功能触发器修改成扫描触 发器,在测试模式时将时序电路转化为组合模块, 扫描测试技术是一种最为流行的可测性测试 (Design For Testability, DFT)方法<sup>[10]</sup>。扫描测试有 效提高了芯片的可测性,大大降低测试生成的复杂 度。Test-Per-Scan 测试具有低功耗(低频下进行移 位)、实现代价低等优点。然而,在 Test-Per-Scan 测试方案中,每次施加新的测试向量时需将扫描链 的前一状态全部移出,随着测试数据规模的增大, 过长的扫描移位时间而导致的高额测试费用将无法 被接受。具有测试时间优势的 Test-Per-Clock 测试 越来越受到关注。然而, 传统 Test-Per-Clock 测试 大都采用了(类)伪随机测试生成,由于存在大量抗 伪随机故障, 在短时间里很难得到满意的故障覆盖 率,使得测试应用时间优势不能在 Test-Per-Clock 测试上得到很好的体现[11]。文献[12]结合了 LFSR 重 播种和测试点插入技术有效降低了测试时间和测试 数据, 文献[13]和文献[14]通过动态重构扫描链和

分块测试有效降低了 Test-Per-Clock 结构的实现代价,但这些方法布线开销大,实现较为复杂。本文考虑了布线费用和布线约束,提出了一种 LFSR-ROM 混合结构的高效 Test-Per-Clock 测试生成方案。首先基于故障统计,采用 LFSR 产生合适长度的伪随机测试向量,然后在测试结构的理论分析基础上,提出了一种受控的线性移位方法产生确定型测试向量来完成剩余故障的高效检测,其中线性移位器的控制位被存储于 ROM 中。实验结果表明,本文方法只需较少的测试数据存储和较短的测试应用时间能够达到单固定型故障的完全检测。

本文其余章节安排如下:第2节介绍了本文提出的测试结构;第3节介绍了伪随机测试序列长度的确定和确定型测试生成算法;第4节给出了基准电路的仿真结果;第5节总结全文。

# 2 LFSR-ROM 模式 BIST 结构

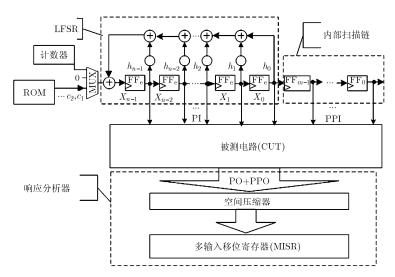

本文提出的 BIST 测试结构图如图 1 所示,测试结构由测试向量产生器(Test Pattern Generator, TPG)和响应分析器(Response Analyzer, RA)组成。其中,TPG 由线性反馈移位寄存器(LFSR)和存储控制位流的 ROM 组成。考虑到布线费用和布线约束,LFSR 只采用原始输入端(PI)附加的触发器构建。LFSR 在测试时有两种模式:自由伪随机模式和受控移位模式。首先,LFSR 自由地生成伪随机测试向量检测易于检测的故障(MUX 的 0 输入被选择),其中计数器记录伪随机测试序列的长度。然后,MUX 选择存储于 ROM 中受控位流,LFSR 处于受控模式,产生确定型测试向量以检测剩余故障。被测电路中所有的内部触发器构成串行扫描链,连接在 LFSR 的尾部。在每一个测试时钟下,TPG 产生

图 1 LFSR-ROM 混合模式 Test-Per-Clock 测试结构图

一个测试向量并施加到被测电路(CUT)中。空间压缩器 (Space Compactor) 和多输入移位寄存器 (MISR)通过电路原始输出和伪原始输出接收电路响应并进行响应压缩。其中空间压缩器和 MISR 的结构设计可参照文献[15],在这里不再叙述。

从上述内容可以看出,伪随机测试时间和确定型测试时间的总和决定了电路的总测试时间。在确定型测试序列生成中,存储在 ROM 中的每一位控制位决定了下一个测试向量的状态,从而决定了测试数据存储的硬件开销以及确定型测试生成的效率。因此,解决测试方案的关键在于找到有效的折中方案,确定合适的伪随机测试序列长度以减少确定型数据存储,寻找最优的控制位流以较低的测试存储高效地完成测试生成。下一节将详细介绍这些内容。

#### 3 测试生成

本文提出的测试生成包括两个部分:自由的 LFSR 伪随机测试生成和受控 LFSR 确定型测试生 成。自由 LFSR 测试序列长度和确定型测试生成算 法将在本节依次给出。

### 3.1 伪随机测试向量长度确定

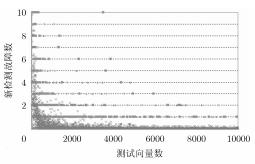

伪随机测试序列的长度将影响总的测试应用时间和随后的确定型测试生成。我们通过对多个伪随机故障检测情况进行统计,注意到新被检测的故障数量随着伪随机测试产生而急剧下降,且使用不同初始值的 LFSR 具有相似的特性。图 2 给出了电路 S5378 的 50 次伪随机故障检测散点图,每次检测分别在不同的初始状态下产生 10000 个伪随机向量。图中给出了 3 个随机样本和平均值的散点,横坐标表示向量个数,纵坐标表示单个向量新检测到的故障数大于 10 的部分没有显示)。由图 2 可以看出,每一个向量新检测到的故障数在向量数为 5000 后平均值趋于 0。因此,我们拟利用这一现象来确定伪随机测试序列的长度,如在本案中,可将 S5378 随机测试序列长度定为 5000。

随机测试1

随机测试2

植机测试3

※ 平均值

图 2 S5378 电路故障监测统计图

#### 3.2 确定型测试生成算法

在讨论确定型测试生成算法之前,首先分析测试结构。

定义 1 如图 1 所示,n 级 LFSR 和m 级内部扫描链组成了L 级移位寄存器(L=n+m)。

定理 1 对于 L 级移位寄存器,一定能够通过施加  $L'(L' \le L)$  位控制位,使得移位寄存器从当前状态 跳转到任一目标状态。

证明 假定移位寄存器当前的向量状态为

$$\boldsymbol{A} = \left\{ x_{n-1}, x_{n-2}, \cdots, x_1, x_0, a_{m-1}, a_{m-2}, \cdots, a_1, a_0 \right\}$$

目标向量为

在第 1 个测试时钟下,控制位  $c_1$  被移入到移位 寄存器,移位寄存器中的状态变为

$$\mathbf{A}^{1} = \left\{ c_{1} + \sum_{i=0}^{n-1} h_{i} x_{i}, x_{n-1}, x_{n-2}, \dots, x_{1}, x_{0}, a_{m-1}, a_{m-2}, \dots, a_{1} \right\}$$

$$(1)$$

其中, $c_1 + \sum_{i=0}^{n-1} h_i x_i$  是模 2 运算, $h_i$  表示反馈网络。由于 $c_1$  在 $c_1 + \sum_{i=0}^{n-1} h_i x_i$  中为唯一未知变量,因此, $c_1 + \sum_{i=0}^{n-1} h_i x_i$  用  $f(c_1)$  表示。

同理, 当第 2 个测试时钟到来时, 控制位  $c_2$  移入到移位寄存器中,移位寄存器中的向量状态变为

$$\mathbf{A}^{2} = \left\{ c_{2} + \sum_{i=0}^{n-2} h_{i} x_{i+1} + h_{n-1} f(c_{1}), f(c_{1}), x_{n-1}, \cdots, x_{1}, x_{0}, a_{m-1}, a_{m-2}, \cdots, a_{2} \right\}$$

$$(2)$$

我们同样用  $f(c_1,c_2)$ 来表示  $c_2+\sum_{i=0}^{n-2}h_ix_{i+1}+h_{n-1}f(c_1)$ 。 依次类推,当  $c_L$  被移入到移位寄存器中时,向量状态变为

$$\mathbf{A}^{L} = \{ f(c_{1}, c_{2}, \dots, c_{L}), f(c_{1}, c_{2}, \dots, c_{L-1}), \dots, f(c_{1}, c_{2}), f(c_{1}) \}$$

(3)

因此,对控制位流的求解等价于求解如式(4)所示的 线性方程组问题:

$$y_{n-1} = f(c_1, c_2, \dots, c_{L-1}, c_L)$$

$$y_{n-2} = f(c_1, c_2, \dots, c_{L-1})$$

$$b_1 = f(c_1, c_2)$$

$$b_0 = f(c_1)$$

$$(4)$$

这是一个模 2 运算方程,它具有唯一的解。在第 i 个  $(i \le L)$  时钟周期时,当前的向量就可能等于目标向量。也就是说,通过施加  $L'(L' \le L)$  位控制位,移位

寄存器中的现有向量可转变成任何其它目标向量。

现在,让我们从另一个角度来分析这个问题。 假设移位寄存器中的当前向量 A 为完全确定型向量 (向量中的每位是 0 或 1),目标向量 B 的每一位为无 关位 X 的概率为  $\lambda(0 \le \lambda \le 1)$ 。向量 A 与 B 匹配的 概率为

$$p_0 = \left(\lambda \times 1 + (1 - \lambda) \times \frac{1}{2}\right)^L = \left(\frac{1 + \lambda}{2}\right)^L \tag{5}$$

每个测试时钟移入的控制位可视为一个无关位 X,经过 L' 个时钟周期后,移位寄存器中的向量状态为  $\{X_{L'},\cdots,X_1,a_{n-1},a_{n-2},\cdots,a_{L'}\}$ 。此时,该向量与目标向量 B 匹配的概率为

$$P_{L'} = (1+\lambda)/2^{L-L'} \tag{6}$$

我们知道, $P_{L'}$ 和 $\lambda$ 的值呈正向增长,和L-L'的值呈反向增长。换句话说,为了得到一个较短的移位时间L',我们需要一个高的 $\lambda$ 值。

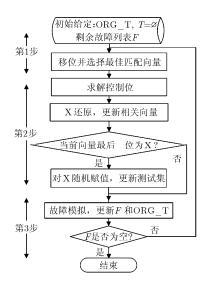

本文提出的确定型测试生成算法的流程如图 3 所示。伪随机测试生成后得到剩余故障列表 F。为了获得较高的 $\lambda$ 值,对每个剩余故障,我们都产生一个相应的测试向量,以最大化其无关位比率(即 $\lambda$ 值)。这些向量构成原始测试库 ORG\_T。我们使用改进的 ATPG 工具 ATALANTA [16]作为向量生成工具。如图 3 所示,算法主要分为 3 个步骤。

第 1 步 寻找具有最小移位的匹配向量过程: 每移入一位控制位都看成是一个临时的 X,称为临时向量,加入到测试集 T并和原始测试库  $ORG_T$ 中的向量进行匹配。当  $ORG_T$ 中不存在可匹配向量时,继续进行移位;当存在一个以上的匹配向量,选择策略是具有最小的 $\lambda$ 值优先。如前文所述,具

图 3 确定型测试生成流程图

有更高 $\lambda$ 值的向量将更容易被匹配,故优先选择更难匹配的向量可提高后续向量匹配的概率。

第2步 解方程的过程:方程的求解如式(4)所示,当控制位流 X 被求解后,进行向量还原,更新与其相关的向量。为了加速故障检测,当移位寄存器中当前向量的最后一位为 X 时,需要对该 X 进行随机赋值,并更新其相关向量。

第 3 步 故障模拟过程: 对测试集T中的新向量进行故障模拟。当某一故障被检测时,将其从故障列表F中删除,并将其对应的向量从测试库ORG\_T中删除。当故障列表F为空时,算法结束;否则,继续寻找下一个最佳目标向量。

测试生成算法的时间复杂度是 $O(L^2 \cdot \text{NoF}^2)$ ,其中 L 和 NoF 分别表示向量的位数和初始剩余故障数。

# 4 实验结果

本节选取了较大的 ISCAS'89 基准电路进行了实验仿真。实验平台为 Intel 酷睿 i3550, 2.0 GB RAM,测试生成算法采用 C 语言实现。故障仿真工具采用的是  $HOPE^{[17]}$ 。

表 1 给出了本文方法的测试生成结果。前 3 列 分别表示电路名称,电路原始输入数(LFSR 的大小) 和冗余故障的数目。第4列"GE"给出了实现本文 方法 TPG 的逻辑硬件开销,采用了文献[18]的等价 门(Gate Equivalent, GE)统计方法。其中一个2选 1的 MUX 代价为 1.5GE, 一个 2输入异或门的代价 为 2.5GE,一个 n 位计数器的代价为 4n GE。本文 LFSR 的特征多项式采用的是本原多项式,针对有 多个本原多项式的 LFSR, 随机选择反馈逻辑较少 的以降低 LFSR 硬件开销。第5列"Ran TL"给 出了 LFSR 的伪随机测试序列长度,采用了 3.1 节 中描述的方法来确定。列"Min Store"和 "Ave Store"给出了确定型测试生成中的最小和 平均控制位流(即存储位)大小,TAT 为测试周期数。 计算结果取自20次的运行结果。从实验结果可以发 现,最小存储位和平均存储位数相差不大,从而说 明了本文方法具有良好的相对稳定性,即总测试序 列不受制于伪随机测试的影响。最后两列给出了平 均总的测试应用时间和 CPU 运行时间(s)。其中, CPU 时间包括伪随机测试生成和确定型测试生成 时间。对每一个电路,故障效率都达到了 100%

$$\left($$

故障效率 =  $\frac{$ 检测到的故障数}{总故障数 - 冗余故障数} \times 100\% \right)。

表 2 给出了本文方法和其他方法的比较,包括基于 Test-Per-Scan 的 LFSR 重播种方法<sup>[5]</sup> (variation

| 丰 1 | 本文方法测试生成结果 |  |

|-----|------------|--|

| 75  | <b>本女刀</b> |  |

| 电路     | PΙ | #Red | GE   | Ran_TL | Min_Store(bit) | Ave_Store(bit) | TAT   | CPU(s)  |

|--------|----|------|------|--------|----------------|----------------|-------|---------|

| S5378  | 35 | 40   | 63.5 | 5000   | 711            | 754            | 5754  | 1.35    |

| S9234  | 36 | 452  | 67.5 | 10000  | 6942           | 7159           | 17159 | 42.87   |

| S13207 | 31 | 151  | 63.5 | 5000   | 2899           | 3033           | 8033  | 31.04   |

| S15850 | 14 | 389  | 63.5 | 5000   | 3525           | 3719           | 8719  | 23.45   |

| S35932 | 35 | 3984 | 55.5 | 1500   | 202            | 204            | 1704  | 15.67   |

| S38417 | 28 | 165  | 67.5 | 10000  | 15385          | 15737          | 25737 | 2233.28 |

| S38584 | 12 | 1506 | 63.5 | 5000   | 3985           | 4047           | 9047  | 225.25  |

表 2 本文方法和其它方法的对比

| 电路                     | 本文方法  |       | 文献[5]  |       | 文献[6] |       | 文献[8] |       | 文献[18] | 文献[19] |

|------------------------|-------|-------|--------|-------|-------|-------|-------|-------|--------|--------|

| <b>七</b> 斑             | TAT   | Store | TAT    | Store | TAT   | Store | TAT   | Store | Store  | Store  |

| S5378                  | 5754  | 754   | 13182  | 5040  | 23112 | 11440 | 11014 | 11014 | 10523  | 4107   |

| S9234                  | 17159 | 7159  | 19957  | 7931  | 11808 | 1935  | 20543 | 20543 | 17708  | 6492   |

| S13207                 | 8033  | 3033  | 47600  | 7723  | 21731 | 6696  | 16472 | 16472 | 23376  | 6724   |

| S15850                 | 8719  | 3719  | 45947  | 9423  | 8550  | 3505  | 17739 | 17739 | 21310  | 6567   |

| S35932                 | 1704  | 204   | N/A    | N/A   | 12180 | 5508  | 1295  | 1295  | 4211   | 1549   |

| S38417                 | 25737 | 15737 | 210329 | 36884 | 34510 | 34965 | 96645 | 96645 | 55977  | 24892  |

| S38584                 | 9047  | 4047  | 139372 | 15622 | 8052  | 8790  | 25685 | 25685 | 61304  | 21145  |

| $\mathrm{Ave.Red}(\%)$ |       |       | 69.3   | 57.9  | 27.1  | 11.1  | 39.0  | 81.6  | 83.2   | 53.4   |

-R 模式), 基于 Test-Per-Clock 的 LFSR 重播种方 法[6], 基于多扫描链的扫描切片阻塞方法[8]以及基于 编码的确定型压缩方法(自适应 EFDR 编码[18]和基 于 Hadamard 变换的 VIHC 编码<sup>[19]</sup>)。列 "TAT"和 列"Store"给出了每一种方法的测试应用时间(测试 周期数)和测试数据存储量(bit)。表中最后一行给出 了本文方法与其它方法相比测试应用时间和测试数 据存储量的平均减少率。从表 2 中的数据对比可以 看到,与伪随机方法[5,6,8]相比,由于本文方法能更有 效地利用受控位流构建测试向量, 使得当前向量能 更快地到达目标向量,本文方法在测试应用时间和 测试存储的减少上都具有较高的优势。与基于编码 的方法相比,测试储存减少更为明显,由于文献[18] 和文献[19]是基于 Test-Per-Scan 的测试方法,输入 的数据位在解码后还需要经过若干个时钟周期(扫 描链长度)才能被施加到被测电路,因此,本文方法 甚至在测试应用时间上都优于确定型算法。同时, 相比其它混合测试将整个电路扫描链都作为 LFSR 的引脚输出,本文方法的 LFSR 只采用了原始输入 端的触发器构建,测试向量产生器结构简单,控制 逻辑也仅需一个计数器实现,需要的控制逻辑和布 线开销小, 且不需要额外的解码逻辑。

#### 5 结束语

在本文中, 我们提出了一种基于全扫描电路的 LFSR-ROM 混合 BIST 测试方案。测试分为两部分: 自由 LFSR 伪随机测试模式和基于受控 LFSR 的确 定型测试模式。通过对提出的测试架构进行理论分 析,提出了一种有效的受控线性移位反馈测试生成 方法。实验结果表明,与其它方法相比,该方案在 测试应用时间和测试数据存储上都具有较强的优 势。由于采取了统计的方法来确定伪随机测试序列 的长度,本文的实验结果具有良好的稳定性,总测 试序列长度不受制于伪随机测试过程的影响。另外, 本文的 LFSR 只采用原始输入端附加的触发器构 建,并且控制位被直接存储于 ROM 中,不需额外 的解码逻辑,使得 TPG 的面积开销更少,实现更为 简单。本文提出的测试方法还可扩展到其它类型的 故障测试,如针对延时故障的全速 LOS(Latch-On-Shift)测试。下一步工作拟从电路拓扑结构出发, 构建扫描链,使其支持多扫描链测试,从而进一步 减少测试应用时间和测试存储。综上所述,本文方 法在低成本测试应用中具有良好的应用前景。

## 参考文献

- CHATTERJEE M and PRADHAN D K. A BIST pattern generator design for near-perfect fault coverage[J]. *IEEE Transactions on Computers*, 2003, 52(12): 1543–1558. doi: 10.1109/TC.2003.1252851.

- [2] LI L and MIN Y. An efficient BIST design using LFSR- ROM architecture[C]. 9th Asian Test Symposium, Taipei, 2000: 386–390.

- [3] FISER P and KUBATOVA H. An efficient mixed-mode BIST technique[C]. 7th IEEE Design and Diagnostics of Electronic Circuits and Systems Workshop 2004, Tatranská Lomnica, SK, 2004: 227–230.

- [4] JAS A, KRISHANA C V, and TOUBA N A. Weighted pseudo-random hybrid BIST[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2004, 12(12): 1277–1283. doi: 10.1109/TVLSI.2004.837985.

- [5] WANG Seongmoon, WEI Wenlong, and WANG Zhanglei. A low overhead high test compression technique using pattern clustering with n-detection test support[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2010, 18(12): 1672–1685. doi: 10.1109/TVLSI.2009.2026420.

- [6] KALLIGEROUS E, BAKALIS D, KAVOUSIANOS X, et al. Reseeding-based test set embedding with reduced test sequences[C]. International Symposium on Quality Electronic Design, San Jose, 2005: 226–231.

- [7] 胡晨, 许舸夫, 张哲. 一种基于受控 LFSR 的内建自测试结构 及其测试矢量生成[J]. 电路与系统学报, 2002, 7(3): 13–16. HU Chen, XU Gefu, and ZHANG Zhe. A BIST structure and test pattern generation method based on controlled LFSR[J]. *Journal of Circuits and Systems*, 2002, 7(3): 13–16.

- [8] YOU Zhiqiang, WANG Weizheng, DOU Zhiping, et al. A scan disabling-based BAST scheme for test cost reduction[J]. IEICE Electronics Express, 2011, 8(16): 1367–1373.

- [9] ACEVEDO O and KAGARIS D. On the computation of LFSR characteristic polynomials for built-in deterministic test pattern generation[J]. *IEEE Transactions on Computers*, 2016, 65(2): 664–669. doi: 10.1109/TC.2015.2428697.

- [10] CHEN L, CUI Aijiao, and CHANG C H. Design of optimal scan tree based on compact test patterns for test time reduction[J]. *IEEE Transactions on Computers*, 64(12), 2015: 3417–3492. doi: 10.1109/TC.2015.2401019.

- [11] LIU T, KUANG J, YOU Z, et al. An effective deterministic test generation for test-per-clock testing[J]. IEEE Aerospace & Electronic Systems Magazine, 2014, 29(5): 25–33. doi: 10.1109/MAES.2014.130192.

- [12] MRUGALSKI G, RAJSKI J, SOLECKI J, et al. Test express -new time-effective scan-based deterministic test paradigm[C]. 2015 IEEE 24th Asian Test Symposium(ATS), Mumbai, 2015: 19–24.

- [13] RAJSKI J, SOLECKI J, TYSZER J, et al. Scan chain configuration for test-per-clock based on circuit topology[P]. US9009553, 2015.

- [14] SHIAO C M, LIEN W C, and LEE K J. A test-per-cycle BIST architecture with low area overhead and no storage requirement[C]. 2016 International Symposium on VLSI Design, Automation and Test (VLSI-DAT), Hsinchu, 2016:

- [15] NOVAK O and NOSEK J. Test-per-clock testing of the circuits with scan[C]. Proceedings Seventh International On-Line Testing Workshop, Giardini Naxos, Taormina, Italy, 2001: 90–92.

- [16] LEE H K and HA D S. Atalanta: An efficient ATPG for combinational circuits[R]. Technical Report, 93–12, Department of Electrical Engineering, Virginia Polytechnic Institute and State University, Blacksburg, Virginia, 1993.

- [17] LEE H K and HA D S. HOPE: An efficient parallel fault simulator for synchronous sequential circuits[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 1996, 15(9): 1048–1058. doi: 10.1109/ 43.536711.

- [19] KUANG J, ZHANG L, YOU Z, et al. Improve the compression ratios for code-based test vector compressions by decomposing[C]. 20th IEEE European Test Symposium (ETS), Cluj-Napoca, 2015: 1–6.

- 刘铁桥: 男,1983 年生,讲师,主要研究方向为 IC 可测性设计与大数据研究.

- 牛小燕: 女,1978年生,助理研究员,主要研究方向为IC测试.

- 杨 洁: 女,1986年生,讲师,主要研究方向为数据挖掘和大数据研究.

- 毛 峰: 男,1986年生,讲师,主要研究方向为数据挖掘和容错 计算.