## 基于混合电压 - 电流表示的 ECL 电路综合方法 1

吴训威 Q. Qiu\* M. Pedram\*

(浙江大学电子工程系 杭州 310028) \*(美国南加州大学 电气工程与系统系 加州 CA 990189-2562)

摘 要 基于混合电压 - 电流的信号表示及对电流、电压信号定义的运算,本文提出了一种 ECL 电路的混合综合技术。所提出的方法已用一位全加器的设计实例予以演示。本文最后提出 了一个适用于电流信号表示和电流运算的代数系统。

关键词 电流信号, 电路综合, ECL, 代数系统

中图号 TN791

#### 1 ECL 电路中的混合电压-电流表示

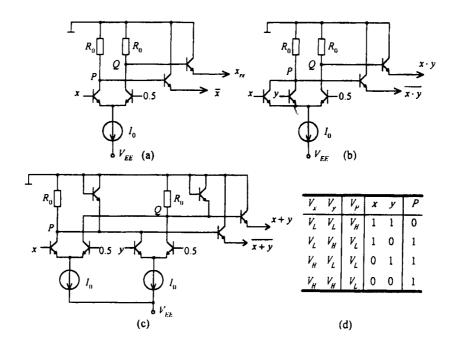

在传统的数字电路设计中,电压常被用来表示逻辑信号。例如,如果采用正逻辑,则一个变量的两个值 (1,0) 将用两个电平级 (高电平,低电平)来予以表示。 (对于负逻辑,则取值相反)。然而,在 ECL 电路中信号是用电压和电流二者来表示的  $^{[1]}$ 。以如图 1(a) 所示的 ECL 为例,其用 0.5 表示的参考电平取为 -1.2V,即设置在高电平 (-0.8V) 和低电平 (-1.6V)中间。假如输入电压信号为  $V_x = -0.8$ V (高电平),则单位电流  $I_0$  将流过输入端的晶体管,而流过参考侧晶体管的电流为 0。通过集电极电阻  $R_0$  的电流信号将转换成相应的电压信号。如果取  $(I_0R_0)$  为单位电压 0.8V,则结点 P 和 Q 的两个电平分别为 -0.8V 和 0V。考虑到两个输出射极跟随器 b-e 结的导通压降 (本文中将省画输出负载),输出电平将会下移 0.8V,因此我们得到  $V_{re} = -0.8$ V 和  $V_{\overline{x}} = -1.6$ V。如果输入信号为  $V_x = -1.6$  V(低电平),讨论可类似进行。我们已看到在 ECL 电路中电流信号是另一种信号形式,这样,通过引入可应用于电流信号的运算便可能得到一种综合 ECL 电路的混合方法。

在上面的讨论中我们也注意到: 如果电流信号 ( $I_0$ ,0) 对应的逻辑值为 (I,0),则由电流信号转换产生,后又经射极跟随器移位而得的输出电压信号 (I,0),也应对应于 (I,0)。因此,在 ECL 电路中电压信号以其本质应该采用负逻辑表示。本文中我们将采用负逻辑表示,这样,与用正逻辑时的传统名称不同,图 I(b), I(c) 所示的电路应被重新命名为 "与 /与非"门及 "或 / 或非"门。例如,图 I(b) 中结点 I 对输入的电压关系和使用负逻辑时的真值表如图 I(d) 所示,真值表中表示的是 "与非"运算而不再是 "或非"运算。

<sup>&</sup>lt;sup>1</sup> 1997-11-11 收到, 1998-09-10 定稿 国家自然科学基金资助的项目 (No.69573008)

图 1 基本 ECL 门 (a) 整形器 / 反相器, (b) "与 / 与非" 门 (负逻辑), (c) "或 / 或非"门 (负逻辑), (d) 在"与 / 与非"门中 P 点的真值表

### 2 电压信号和电流信号的物理运算

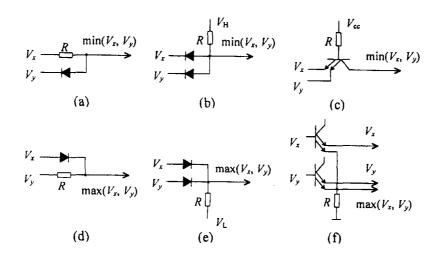

电压信号的特点是它们之间易于比较. 以双极性晶体管为例, p-n 结的单向导通特性就可用以比较和选择电压信号, 如图 2 所示 (在此我们忽略了 p-n 结的压降)<sup>[2]</sup>. 显然, 在使用负逻辑时图 2(a), 2(b), 2(c) 中的电路均实现 "或"运算, 而图 2(d), 2(e), 2(f) 中的电路均实现 "与"运算. (用正逻辑时, 两者实现的运算正好互换). 在 ECL 电路中, 图 2(f) 中的电路用于实现多个输入之间的 "与"运算, 如同图 1(b) 所示. 这种线 "与"运算亦可用联结两个晶体管的发射极输出来实现.

对于电流信号情况有所不同,因为它们之间是难以进行比较的. 现在我们理解了为何在使用布尔运算时在传统设计中很少讨论电流信号. 然而,电流之间容易通过简单的导线连结来实现相加或相减。这暗示了如果引入加减为辅助运算,则将会增强对 ECL 电路的综合技术. 在图 1(c) 所示的电路中,我们发现当  $V_x = V_y = -0.8V$  时,两个晶体管对中的输入管将导通,并且将有一个相加后的电流  $2I_0$  流过结点 P. 在 ECL 电路中这实际上反映了一次加法运算。但是,  $2I_0$  的电流对应的逻辑值为 2,因此这种加法运算导致了高逻辑值,它超出了允许的逻辑值范围 (1,0). 通常的解决方法是截去它以避免出现高逻辑值. 在图 1(c) 中用一个箝位二极管与电阻  $R_0$  并联以截去超量的电压 (注:如无箝位二极管,该超量的电流将会产生超量的电压)。它的作用亦可用图 2(d) 中的取小比较运算来解释。事实上图 1(c) 中的"或"运算是通过如下的公式实现的:

图 2 利用 p-n 结实现电压信号之间的比较和布尔运算

#### 3 利用电流信号的超量值设计 ECL 电路

上节我们讨论了如何抑制信号以免产生超量逻辑电平。然而,该超量电平却能显著增加导线携带的信息量和晶体管处理的信息量。因此,我们期望利用超量信号可以导出简单的电路结构。在本节我们将考虑这一由电流信号相加而产生的超量信号。该超量信号可作用于晶体管对的信号侧和参考侧。以下我们将把该综合技术用于 ECL 全加器的设计。

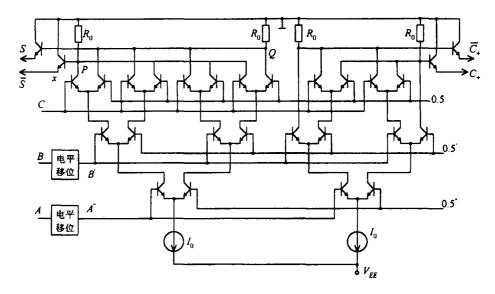

传统设计的 ECL 全加器如图 3 所示  $^{[3]}$ , 这种最简单的结构是靠利用串联门电路来获得的. 与使用 ECL 分立门电路组成的全加器相比,图 3 设计的优点是结构简单,级联数与所用电流源较少. 我们应该指出,为了防止较低级的晶体管进入饱和,它们的输入信号和参考信号必需进行电平下移. 对第二级,结点 B'(1,0) 相应的电平为 (-2.4V, -3.2V),而参考源 0.5' 相应的电平为 -2.8V,这表示输入信号和参考源都相应地下移 1.6V . 对于最低级,输入信号 A'' 和参考源 0.5'' 都下移了  $3.2V^{[4]}$  .图 3 中我们发现结点 P(或 Q) 在任何情况下仅连通一个电流源  $I_0$ ,因此在结点 P(或 Q) 的电流相加就不会产生超量信号。

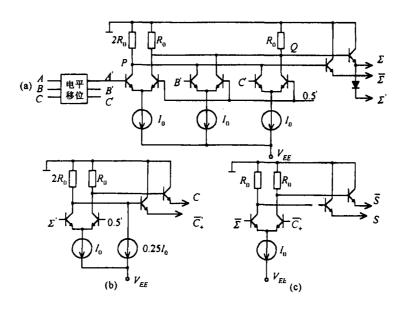

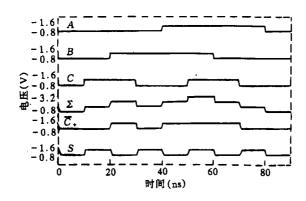

A, B, C 相加将会导致一个四值的信号 (0,1,2,3) 。该求和信号可容易地用电流信号实现,如图 4(a) 所示。对应于四值电流信号  $(0,I_0,2I_0,3I_0)$ ,在图中结点 P 转换的电压信号也是一个四值信号  $(0,-0.8\mathrm{V},-1.6\mathrm{V},-2.4\mathrm{V})^{[5]}$  。为防止晶体管进入饱和状态,输入信号 A,B,C 和参考源 0.5' 的电平必须下移  $1.6~\mathrm{V}$  。由于射极跟随器中的 b-e 结,输出信号  $\Sigma$  的四个电平分别为  $(-0.8\mathrm{V},-1.6\mathrm{V},-2.4\mathrm{V},-3.2\mathrm{V})$  。同理,我们可以导出它的补信号  $\Sigma$ ,它相应的四个输出电平为  $(-3.2\mathrm{V},-2.4\mathrm{V},-1.6\mathrm{V},-0.8\mathrm{V})$  。如果将电平移位后的  $\Sigma'$   $(-1.6\mathrm{V},-2.4\mathrm{V},-3.2\mathrm{V},-4.0\mathrm{V})$  和参考源  $0.5'(-2.8\mathrm{V})$  加到一个晶体管对的两端,这样就可以得到进位输出信号  $C_+$ ,如图 4(b) 所示。在该电路中,我们还可产生一个附加信号  $\overline{C}'_+$ , $\Sigma$  信号对应的四种电平为  $(-0.8\mathrm{V},-1.6\mathrm{V},-2.4\mathrm{V},-3.2\mathrm{V})$ ,而输出信号  $\overline{C}'_+$  对应的电平为  $(-2.8\mathrm{V},-2.8\mathrm{V},-1.2\mathrm{V},-1.2\mathrm{V})$ ,这是因为集电极电阻为  $2R_0$ ,并且有一个  $0.25I_0$  的偏置恒流源。显然,如果将信号  $\overline{C}'_+$  作为一个可变的参考源,并且将互补的求和信号  $\Sigma$  作为输入,则我们就可以得到求和信号 S 及其互补信号  $\overline{S}$  ,如图 4(c) 所示。

图 3 应用串联门的 ECL 全加器传统设计

图 4 利用超值加法信号的 ECL 全加器设计

图 5 利用超值加法信号的 ECL 全加器的 SPICE 模拟

比较图 3 和图 4 的两种设计,我们发现图 4 设计的电路比较小,在整个电路中仅需 5 个晶体管对,而在图 3 中需要 12 个晶体管对。此外,整个电路中仅有一个参考源,而在图 3 中需要三个。然而该电路有较多的恒流源和级联。图 4 的电路已由 PSPICE 模拟证明具有理想的逻辑功能,如图 5 所示。应该指出,利用中间信号  $\Sigma$  可以达到以较简单的电路结构来实现其它对称函数  $f_S(A,B,C)$ 。因此,图 4(a) 中产生该中间超量信号  $\Sigma$  的电路在其它相关的电路设计中可以被利用。

#### 4 适合用电流表示信号的代数系统

对于任何一种新运算,它在一个代数系统中的恰当地位如同在电路中相应的物理实现一样,必须被澄清。因此,通过参考适用于电压信号的布尔代数,我们需要建立一个适用于电流信号的代数系统。

正如前文所指出,传统的布尔运算是与比较相联系的。三种基本运算"与"、"或"、 "非"可以通过比较运算重新定义如下<sup>[2]</sup>:

"与"(取小运算)

$$x \cdot y = \min(x, y),\tag{1}$$

"或"(取大运算)

$$x + y = \max(x, y),\tag{2}$$

"非"(阈比较)

$$\overline{x} = \begin{cases} 0. & \forall \Pi x > 0.5; \\ 1, & \forall \Pi x < 0.5. \end{cases}$$

(3)

众所周知, "与"、"或"、"非"组成完备集以表示任意函数、例如,表 1(表中  $c_i \in \{0,1\})$  给出的二输入函数可用规范的最小项展开式表示如下:

$$f(x,y) = c_0 \cdot (\overline{x} \cdot \overline{y}) + c_1 \cdot (\overline{x} \cdot y) + c_2 \cdot (x \cdot \overline{y}) + c_3 \cdot (x \cdot y). \tag{4}$$

实际上,上述等式是用一种代数语言描述了对表 1 的查表过程. 例如 (4) 式的第一项  $c_0(\bar{x}\cdot\bar{y})$  表示了当 x=0 和 y=0 时,函数值检出为  $c_0$ ,等等.

由于电压信号之间容易比较,基于比较格的布尔代数适用于以电压表示信号的电路设计,然而,如果用电流表示信号,则算术运算,如加法和减法运算,可以容易地利用简单的

| 表 1 二输入逻辑函数    |   |                |

|----------------|---|----------------|

| $\overline{x}$ | y | f(x,y)         |

| 0              | 0 | c <sub>0</sub> |

| 0              | 1 | $c_1$          |

| 1              | 0 | $c_2$          |

| 1              | 1 | c <sub>3</sub> |

连线来实现,为了限制信号为二值的,可以引入如下两个有界算术运算来避免 1&1 = 2 和 0-1=-1 这两种情况:

有界加法

$$x \uplus y = \min(1, x \& y) = \begin{cases} 1, & \text{如x&} y > 1; \\ x \& y, & \text{其它}. \end{cases}$$

(5)

有界减法

$$x \ominus y = \max(0, x - y) = \begin{cases} 0, & \text{如} x - y < 0; \\ x - y, & \text{其它}. \end{cases}$$

(6)

以上两种有界运算可以用传统的"与"、"或"、"非"布尔运算表示如下:

$$x \uplus y = x + y,\tag{7}$$

$$x \ominus y = x \cdot \overline{y}. \tag{8}$$

如果 (8) 式中 x=1 ,我们可以得到非运算

$$1 \ominus y = \overline{y}. \tag{9}$$

由于"或"运算和"非"运算组成完备集,因此上述两种有界运算同样也组成完备集,利用有 界运算,表1所示的二输入函数现可表示成如下规范展开式:

$$f(x,y) = [c_0 \ominus (x \uplus y)] \uplus [c_1 \ominus (x \uplus \overline{y})] \uplus [c_2 \ominus (\overline{x} \uplus y)] \uplus [c_3 \ominus (\overline{x} \uplus \overline{y})]. \tag{10}$$

上式利用另一种代数语言同样描述了表 1 的查表过程。例如, 当 x = 0 和 y = 0 时, 只有  $(x \uplus y)$  这一项为 0, 在 (10) 式中仅第一项  $c_0 \ominus (x \uplus y)$  被保留。于是函数值  $c_0$  被检出,等 等. 上式特别适用于全部信号用电流表示的电流型电路. 但是, 在 ECL 电路的综合中我们 通常需要使用混合电压 - 电流运算. 作为例子, 在 (10) 式中, 若  $c_0 = 1$  和  $c_1 = c_2 = c_3 = 0$ , 我们可得到:

$$f(x,y) = 1 - (x \uplus y) = \overline{\min(x \& y, 1)},$$

式中求和 x&y 是通过电流信号实现的,而取小运算则是通过电压信号实现。对 ECL 电路的 讨论表明确实存在另一种适用于电流信号的代数系统、它为电流信号的应用提供了理论基 础。然而,它特别适用于纯电流型的电路,如电流型 CMOS 电路 [6]。

最后, 我们应该指出, 利用 (7) 式与 (8) 式, (10) 式可以返回到 (4) 式:

$$f(x,y) = [c_0 \cdot \overline{x+y}] + [c_1 \cdot \overline{x+\overline{y}}] + [c_2 \cdot \overline{x+y}] + [c_3 \cdot \overline{x+\overline{y}}].$$

以上讨论表明, 电流信号表示不仅有其物理基础, 而且有其代数基础. 所导出的代数系 统可以用来设计电流型电路,但是,在 ECL 电路中电压信号仍是主要信号形式,布尔代数 在设计 ECL 电路中仍起着主要的作用。我们相信、利用混合电流-电压表示、尤其是利用 中间超量信号,对于 ECL 电路将可发展一个更加灵活,并且功能更强的综合方法 [7]

#### 参考 文献

- [1] Elmasry M I. Digital Bipolar Integrated Circuits. New York: John Wiley & Sons Inc., 1982, Chap. 6.

- [2] 吴训威, 杭国强. Comparison operation of voltage signal and high-speed switching circuits based on multiple beta transistor. Science in China(Series E), 1997, 40(4): 339-448.

- [3] Muroga S. VLSI System Design. New York: John Wiley & Sons Inc., 1982, Chap. 3.

- [4] 吴训威,陈偕雄. Algebra system for ECL logic circuits. IEE Proc.-G, 1991, 138(6): 679-682.

- [5] Dunderdale H. Current mode circuits for ternary logic realizations. Electron. Lett., 1969, 5(23): 575-577.

- [6] Current K W. Current-mode CMOS multiple-valued logic circuits. IEEE J. of Solid-State Circuits, 1994, 29(2): 95-107.

- [7] 吴训威. 多值逻辑电路设计原理. 杭州: 杭州大学出版社, 1994, 第十章.

# A SYNTHESIS METHODOLOGY FOR ECL CIRCUITS BASED ON MIXED VOLTAGE-CURRENT REPRESENTATION

Wu Xunwei Q. Qiu\* M. Pedram\*

(Department of Electronic Engineering, Zhejiang University, Hangzhou 310028)

\*(Department of Electrical Engineering-Systems, University of Southern California, USA)

Abstract This paper presents a synthesis methodology for ECL circuits based on a mixed voltage-current signal representation and operation defined on the voltage and current signals. The ideas presented in this paper are then demonstrated on the design of an ECL 1-bit full adder. The paper concludes by presenting an algebra system which is suitable for current signal representation and operation on currents.

Key words Current signal, Circuit synthesis, ECL, Algebraic system

吴训威: 男, 1940 年生, 教授, 博士生导师, IEEE 高级会员, 中国电子学会会士, 中国通信学会会士, 现从事数字电子学方面的研究工作, 研究内容包括多值逻辑、数字电路开关级设计、低功耗数字集成电路设计等.

Qinru 女, 1972 年生, 博士, 研究助理, 现从事大规模集成电路的功耗估计和低功耗设计. Qiu:

Massoud 男, 1960年生, 教授, 现从事大规模集成电路方面的研究, 研究内容包括大规模集成电路综合 Pedram: CAD, 低功耗分析与设计等。他曾于 1996年荣获美国总统奖 (Presidential Faculty Awards).