# 一种应用于 GNSS 接收机的新型低功耗高速预分频

于云丰®马成炎®叶甜春®®(中国科学院徽电子研究所北京100029)(杭州中科徽电子有限公司杭州310053)

摘 要:该文设计了一款应用于全球卫星导航系统(GNSS)接收机射频芯片的基于新型源耦合锁存器结构的预分频,用于产生接收机所需要的本振信号。与传统的静态源耦合逻辑锁存器相比,新结构引入一个钟控晶体管,可实现在采样期间减小锁存器的时间常数,有效地提高了最高工作频率,并且扩展了工作频率范围。通过建立一个简单但有效的小信号模型,新结构的优点被详细阐述。实验结果显示,该预分频最高频率可达 6.9 GHz,消耗电流仅为 1.2 mA。该预分频在 0.18 µm CMOS 工艺上实现,已成功应用于 GNSS 接收机射频芯片中。

关键词: 全球卫星导航系统; 源耦合逻辑; 预分频; 本振

中图分类号: TN772 文献标识码: A 文章编号: 1009-5896(2010)07-1752-04

**DOI**: 10.3724/SP.J.1146.2009.00842

# A New Low-Power High-Speed Prescaler in GNSS Receivers

Yu Yun-feng<sup>©</sup> Ma Cheng-yan<sup>®</sup> Ye Tian-chun<sup>©</sup>

<sup>®</sup>(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

<sup>®</sup>(Hangzhou Zhongke Microelectronics Co., Ltd, Hangzhou 310053, China)

Abstract: A new prescaler based on new Source Coupled Logic(SCL) latch is proposed in this paper, supplying Local Oscillator (LO) for receivers. Compared to traditional static SCL latch, a clock-controlling transistor is added to reduce the time constant at sensing time, and as a result, the maximum operating frequency increases and the operating range is enlarged. A simple but to some extent accurate small signal model for this new architecture is developed, and the advantages of new design are described in detail. This prescaler's maximum operating frequency can reach to 6.9 GHz when its current is only 1.2 mA. The prescaler is manufactured in 0.18  $\mu$ m CMOS process, and it has been successfully applied to GPS receivers.

Key words : Global Navigation Satellite System (GNSS); Source Coupled Logic(SCL); prescaler; Local Oscillator (LO)

### 1 引言

近年来,无线通信系统发展迅速,尤其是宽带、高频无线通信标准的出现,对系统中一些关键模块,如锁相环中的 VCO、预分频等,提出了更高的要求:工作频率高、相噪低、功耗更小。随着工艺的不断进步,近些年来基于 CMOS 工艺的数 GHz 甚至数十 GHz 的高速器件不断被报道。通常来说,在 GHz 以上的系统中,预分频和 VCO 消耗大部分的功耗,成为决定系统功耗的关键模块 [1-3]。预分频主要有 3种类型:基于单相时钟(True Single Phase Clock, TSPC)结构的预分频、基于源耦合(Source Coupled Logic, SCL)锁存器的预分频、锁定注入预分频。源

耦合逻辑预分频器以其合适的功耗、较高的工作频率、宽的工作频率范围,较小的面积,能够提供正交信号等优势,在目前的无线产品中得到了广泛的应用[4-7]。

源耦合逻辑分频电路是由双极电路的 ECL 结构演变而来,由于电路的摆幅小,因而电路的工作速度得以提高。对于源耦合电路的设计,其速度的关键限制是负载电阻,小的负载电阻有利于减小时间常数,大的电阻则有利于信号的放大。但静态源耦合逻辑锁存器致命的缺点是随着工作频率的增加,功耗增加得非常迅速。Razavi<sup>[8]</sup>,Wang<sup>[9]</sup>等人在此基础上,对电路结构进行了改进,采用动态电阻负载(Dynamic Load, DL),从而使分频器能够工作在 10 GHz 以上,使电路的速度得以进一步提高。然而,态负载结构本身有致命的问题:因为改变负载电阻会改变电路的静态偏置点,这样会导致电路

<sup>2009-06-03</sup> 收到, 2010-01-18 改回

<sup>&</sup>quot;核高基"重大专项(2009ZX01031-002-008)和国家 863 计划项目 (2007AA12Z344)资助课题

通信作者: 于云丰 yunfeng82511@yahoo.com.cn

不能在所有的工艺角下都能稳定地工作。因此,本 文对静态负载结构进行改进,提出一种低功耗高速 源耦合逻辑预分频器。

## 2 低功耗高速预分频原理及电路设计

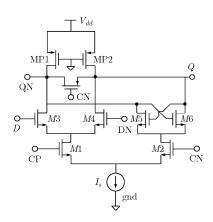

本文提出的锁存器的改进结构如图 1 所示。这种结构可以实现动态负载在采样时间期间减小负载电阻从而提高工作频率的优点,却改进了动态负载结构会改变电路的静态偏置点的缺点。如图 1 所示,本改进结构用一个钟控晶体管连接两个输出端,采用反向时钟信号控制:在采样阶段,负载电阻减小,充放电时间减小,转换速度得到提高;在保持阶段,电阻仍然保持大的阻值来提供足够的增益。

图 1 所提出的新的锁存器结构

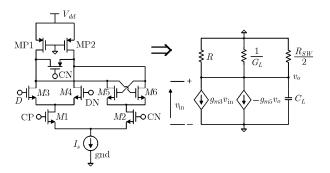

为了充分说明所提出的结构的优势,下面将介绍一种简单有效的小信号模型,从小信号的角度来分析新结构在提高速度、扩展工作范围方面的优势。所提出的源耦合锁存器结构的等效小信号模型如图2 所示。通常来说,源耦合锁存器的速度决定于采样电路的速度,所以,锁存器被设定于采样状态,小信号等效电路可只分析半边电路<sup>[10]</sup>。由图2可以得到小信号模型的传输函数为

$$\begin{split} A_{V}(s) &= \frac{v_{o}(s)}{v_{\text{in}}(s)} = -\frac{g_{m3}}{sC_{L} - g_{m5} + G_{L} + \frac{1}{R} + \frac{2}{R_{SW}}} \\ G_{L} &= g_{ds3} + g_{ds5} \end{split} \right\} (1)$$

图 2 所提出的锁存器的等效小信号模型

式(1)中  $g_{m3}$  为采样对管 M3, M4 的跨导,  $g_{m5}$  为锁存对管 M5, M6 的跨导,  $G_L$  为采样对管的沟道电导与锁存对管的沟道电导之和, R 为作为负载电阻的 MP1,MP2 的直流等效电阻,  $R_{SW}$  为增加的钟控晶体管的直流等效电阻,  $C_L$  是输出节点总的寄生电容以及负载电容之和。

当小信号传输函数的增益为 1,锁存器输出节 点最高工作频率为

$$f_{\text{out,max}} = \frac{\sqrt{g_{m3}^2 - \left(g_{m5} - G_L - \frac{1}{R} - \frac{2}{R_{SW}}\right)^2}}{2\pi C_L} \tag{2}$$

从式(2)中,很明显可以看出 M5、M6 组成的负阻结构产生的负跨导  $g_{m5}$  用来抵消负载电阻 R、钟控管等效电阻  $R_{SW}$ 、采样管的沟道电导与锁存对管的沟道电导。如果式(2)中分子中第 2 项恰好为 0,输出信号为输入信号的二分频信号,那么锁存器能够工作的最高频率,就是输入信号的最高频率为

$$f_{\text{max}} = 2f_{\text{out,max}} = 2 \times \frac{g_{m3}}{2\pi C_L} = \frac{g_{m3}}{\pi C_L}$$

(3)

在传统的源耦合锁存器中,采样管和锁存管采用相同的尺寸,那么  $g_{m3}$  和负跨导  $g_{m5}$  相等,锁存器的最高频率受到限制 $^{[11]}$ 。为了提高工作频率,可以减小锁存管 M5,M6 的尺寸,但是 M5,M6 的尺寸的减小会影响锁存状态下电路的工作情况,即如果 M5,M6 的尺寸太小,那么电路将不能正常工作,并且随着 M5,M6 尺寸的减小,锁存器的最低工作频率逐渐提高,压缩锁存器的工作范围 $^{[12]}$ 。

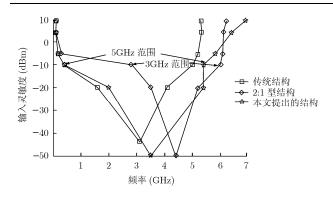

所提出的锁存器,在设计上增加了一个维度,使得可控参数不仅仅局限在 M3-M6 的尺寸上,通过在输出端加入一个晶体管,可以得到最优化的 M3-M6 的尺寸,满足高的工作频率和较宽的工作范围。传统锁存器,采样管与锁存管的比例为 2:1 的锁存器以及本文提出的新型的锁存器在输入灵敏度方面的比较如图 3 所示。在输入信号幅度为-10 dBm时,所提出的新型结构的工作范围可达 5 GHz,而 2:1 型仅为 3 GHz,并且所提出的结构的最高频率分别比传统结构, 2:1 型结构的最高频率提高 30%, 13%。实际上,如果把 M5,M6 管的尺寸减小一半,锁存器的最高频率会继续提高,但是这样也会提高最低工作频率,压缩工作范围。

如果输入时钟信号的频率较低,信号的周期较长,信号的高电平和低电平的持续时间比较长,这样也就意味着节点的充放电时间也较长。在输入信号的过零点附近的持续时间过长,导致预分频自振荡。而新结构预分频却可以把这种情况下的工作频

图 3 本文提出的锁存器与 2:1 型以及传统锁存器的灵敏度比较

率降低到更低的频率,即使输入时钟信号频率降低到 0.1 GHz,新结构预分频仍然可以正常分频。

由模拟结果,结合文献[9-12]中实用的经验规则,可得到如下结论:

- (1)负载电阻和输出节点的总电容值的乘积决定了节点充放电的时间,即 $\tau \propto RC_L$ ,也决定预分频的最高工作频率;

- (2)预分频的最高工作频率与尾电流源的电流 和采样差分对的宽长比有关。尾电流和采样差分对 的宽长比越大,工作频率也越高;

- (3)采样差分对管与锁存差分对管宽长比之比 影响预分频的自振荡频率。如果这个比值越大,预 分频的自振荡频率越高,最高工作频率也越高,但 是工作范围也会受到压缩,因为比值越大,预分频 的最低工作频率将迅速抬高,反之,如果锁存差分 对管宽长比接近采样差分对管宽长比,预分频的工 作范围就越大;

- (4)采样差分对管与锁存差分对管宽长比之比 越接近 1,那么预分频越容易振荡,并且振荡频率 的 2 倍越接近于工作范围的中心点;这个比值越大, 振荡频率的 2 倍越接近最高工作频率。

## 3 测试结果

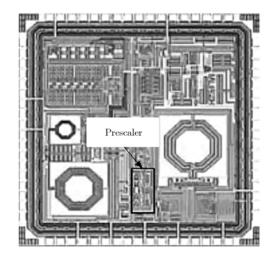

本文所提出的预分频在  $0.18~\mu m$  RFCMOS 工艺上实现,预分频核心版图大小约  $95~\mu m \times 58~\mu m$ 。 预分频在整个 GPS 接收机芯片中的位置如图 4~ 所

示。

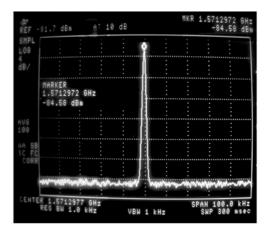

结果显示,所提出的预分频在 1.8 V 的供电情况下,核心电路功耗仅为 2.16 mW,工作范围为 0.1 GHz-6.9 GHz,比 2:1 型预分频工作频率提高约 13%,比传统型预分频性能提高约 30%。表 1 列出了基于所提出的锁存器的预分频与近年来发表的论文中的预分频测试结果的比较。当预分频的输入信号频率为 3.142 GHz 时,预分频的输出频谱如图 5 所示。

图 4 GPS 接收机射频芯片概貌图

图 5 预分频输出频谱

表 1 与近年来发表的 CMOS 预分频性能比较

|                   | $\rm Razavi^{[8]}$ |                | $\mathrm{Wong}^{[10]}$ | ${ m Shinmyo}^{[11]}$ | $\mathrm{Lu}^{[13]}$ | 本文                 |

|-------------------|--------------------|----------------|------------------------|-----------------------|----------------------|--------------------|

| 工艺(µm)            | 0.1                |                | 0.35                   | 0.18                  | 0.35                 | 0.18               |

| 电压(V)             | 1.2                | 2.6            | 1                      | 1.8                   | 3.3                  | 1.8                |

| 最低频率              | N/A                | N/A            | $1\mathrm{GHz}$        | N/A                   | N/A                  | $0.1~\mathrm{GHz}$ |

| 最高频率(GHz)         | 5                  | 13.4           | 5.2                    | 10                    | 8.5                  | 6.9                |

| 电流(mA)            | 2.17               | 10.77          | 2.5                    | 3.4                   | 3.3                  | 1.2                |

| 面积(μm²)           | $70 \times 50$     | $70 \times 50$ | $75\times80$           | $40 \times 50$        | $35 \times 50$       | $95{\times}58$     |

| $\mathrm{GHz/mW}$ | 1.92               | 0.48           | 2.08                   | 1.63                  | 0.77                 | 3.19               |

#### 4 结论

本文提出了一种新型锁存器结构。与基于传统锁存器的预分频、基于2:1型锁存器的预分频结果比较表明,基于新结构实现的预分频提高了最高工作频率(比基于传统型锁存器的预分频最高工作频率提高约30%),还能保持较宽的工作范围。在0.18 μm CMOS工艺中实现,工作电流仅为1.2 mA(1.8 V电压),已成功应用于GNSS接收机射频芯片中。该新型锁存器结构可用于其它高速数据传输系统。

### 参考文献

- [1] Henzler S and Koeppe S. Design and application of power optimized high-speed CMOS frequency dividers[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2008, 16(11): 1513–1520.

- [2] Kim D D, Cho Choong-yeun, and Kim Jong-hae. Scalable statistical measurement and estimation of a mmwave CML static divider sensitivity in 65nm SOI CMOS[C]. 2008 IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, Georgia, June 15–17, 2008: 625–628.

- [3] Park D M and Cho S H. A 1.8 V 900 μW 4.5 GHz VCO and prescaler in 0.18 μm CMOS using charge-recycling technique[J]. IEEE MicroWave and Wireless Components Letters, 2009, 19(2): 104–106.

- [4] Jang Sheng-Lyang, Lin Chi-Wen, and Liu Cheng-Chen, et al.. An active-inductor injection locked frequency divider with variable division ratio[J]. IEEE MicroWave and Wireless Components Letters, 2009, 19(1): 39–41.

- [5] Mohanavelu R and Heydari P. A novel 40-GHz flip-flop-based frequency divider in 0.18μm CMOS[C]. 31st European Solid-State Circuits Conference(ESSCIRC 2005), Grenoble, France, Sept. 12–16, 2005: 185–188.

- [6] Farazian M, Gudem P S, and Larson L E. A CMOS multi-phase injection-locked frequency divider for V-band operation[J]. IEEE Microwave and Wireless Components

- Letters, 2009, 19(4): 239-241.

- [7] Mo Yuan, Skafidas E, and Evans R, et al.. Analysis and design of a 50-GHz 2:1 CMOS CML static frequency divider based on LC-tank[C]. European Microwave Integrated Circuit Conference, Amsterdam, Netherlands, Oct. 27–28, 2008: 64–67.

- [8] Razavi B, Lee K F, and Yan R H. A 13.4-GHz CMOS frequency divider[C]. IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, Feb. 16–18, 1994: 176–177.

- [9] Wang Hong-mo. A 1.8V 3mW 16.8GHz frequency divider in 0.25μm CMOS[C]. IEEE International Solid-state circuits Conference, San Francisco, CA, USA, Feb.7–9, 2000: 196–197.

- [10] Wong M C, Cheung S L, Luong H C. A 1-V 2.5-mW 5.2-GHz frequency divider in a 0.35-μm CMOS process[J]. IEEE Journal of Solid-State Circuits, 2003, 38(10): 1643–1648.

- [11] Shinmyo A, Hashimoto M, and Onodera H. Design and optimization of CMOS current mode logic dividers[C]. IEEE Asia-Pacific Conference on Advanced System Integrated Circuits (AP-ASIC2004), Fukuoka, Japan, Aug. 4–5, 2004: 434–435.

- [12] Singh U and Green M. Dynamics of high-frequency CMOS dividers[C]. 2002 IEEE International Symposium on Circuits and Systems, Scottsdale, Arizona, USA, May 26–29, 2002: 421–424.

- [13] Lu Jian-hua, Wang Zhi-gong, and Tian Lei, et al.. An 8.5GHz

1:8 frequency divider in 0.35μm CMOS technology[J].

Chinese Journal of Semiconductors, 2003, 24(4): 366–369.

- 于云丰: 男,1982 年生,博士生,研究方向为 CMOS 低功耗高性能频率合成器的研究与设计.

- 马成炎: 男,1963年生,研究员,博士生导师,长期从事模拟射频集成电路设计及研究工作.

- 叶甜春: 男,1965 年生,研究员,博士生导师,从事模拟集成电路设计、纳米微细加工技术、下一代光刻掩模技术、新结构 MEMS 及纳米传感器技术等研究.